Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HCS12                                                       |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 25MHz                                                       |

| Connectivity               | EBI/EMI, SCI, SPI                                           |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 31                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-LQFP                                                     |

| Supplier Device Package    | 48-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12gc32mfae |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.2 **Memory Map and Registers**

#### 1.2.1 **Device Memory Map**

Table 1-1 shows the device register map after reset. Figure 1-2 through Figure 1-6 illustrate the full device memory map.

| Address       | Module                                                  | Size |

|---------------|---------------------------------------------------------|------|

| 0x0000-0x0017 | Core (ports A, B, E, modes, inits, test)                | 24   |

| 0x0018        | Reserved                                                | 1    |

| 0x0019        | Voltage regulator (VREG)                                | 1    |

| 0x001A-0x001B | Device ID register                                      | 2    |

| 0x001C-0x001F | Core (MEMSIZ, IRQ, HPRIO)                               | 4    |

| 0x0020-0x002F | Core (DBG)                                              | 16   |

| 0x0030–0x0033 | Core (PPAGE <sup>(1)</sup> )                            | 4    |

| 0x0034-0x003F | Clock and reset generator (CRG)                         | 12   |

| 0x0040-0x006F | Standard timer module (TIM)                             | 48   |

| 0x0070–0x007F | Reserved                                                | 16   |

| 0x0080-0x009F | Analog-to-digital converter (ATD)                       | 32   |

| 0x00A0-0x00C7 | Reserved                                                | 40   |

| 0x00C8-0x00CF | Serial communications interface (SCI)                   | 8    |

| 0x00D0-0x00D7 | Reserved                                                | 8    |

| 0x00D8-0x00DF | Serial peripheral interface (SPI)                       | 8    |

| 0x00E0-0x00FF | Pulse width modulator (PWM)                             | 32   |

| 0x0100-0x010F | Flash control register                                  | 16   |

| 0x0110-0x013F | Reserved                                                | 48   |

| 0x0140-0x017F | Scalable controller area network (MSCAN) <sup>(2)</sup> | 64   |

| 0x0180-0x023F | Reserved                                                | 192  |

| 0x0240-0x027F | Port integration module (PIM)                           | 64   |

| 0x0280-0x03FF | Reserved                                                | 384  |

#### Table 1-1. Device Register Map Overview

External memory paging is not supported on this device (Section 1.7.1, "PPAGE").

Not available on MC9S12GC Family devices

# 1.3.4.13 PE2 / R/W — Port E I/O Pin [2] / Read/Write

In all modes this pin can be used as a general-purpose I/O and is an input with an active pull-up out of reset. If the read/write function is required it should be enabled by setting the RDWE bit in the PEAR register. External writes will not be possible until enabled. This pin is not available in the 48- / 52-pin package versions.

# 1.3.4.14 PE1 / IRQ — Port E Input Pin [1] / Maskable Interrupt Pin

The  $\overline{\text{IRQ}}$  input provides a means of applying asynchronous interrupt requests to the MCU. Either falling edge-sensitive triggering or level-sensitive triggering is program selectable (INTCR register).  $\overline{\text{IRQ}}$  is always enabled and configured to level-sensitive triggering out of reset. It can be disabled by clearing IRQEN bit (INTCR register). When the MCU is reset the  $\overline{\text{IRQ}}$  function is masked in the condition code register. This pin is always an input and can always be read. There is an active pull-up on this pin while in reset and immediately out of reset. The pull-up can be turned off by clearing PUPEE in the PUCR register.

# 1.3.4.15 PE0 / XIRQ — Port E input Pin [0] / Non Maskable Interrupt Pin

The  $\overline{\text{XIRQ}}$  input provides a means of requesting a non-maskable interrupt after reset initialization. During reset, the X bit in the condition code register (CCR) is set and any interrupt is masked until MCU software enables it. Because the  $\overline{\text{XIRQ}}$  input is level sensitive, it can be connected to a multiple-source wired-OR network. This pin is always an input and can always be read. There is an active pull-up on this pin while in reset and immediately out of reset. The pull-up can be turned off by clearing PUPEE in the PUCR register.

# 1.3.4.16 PAD[7:0] / AN[7:0] — Port AD I/O Pins [7:0]

PAD7–PAD0 are general purpose I/O pins and also analog inputs for the analog to digital converter. In order to use a PAD pin as a standard input, the corresponding ATDDIEN register bit must be set. These bits are cleared out of reset to configure the PAD pins for A/D operation.

When the A/D converter is active in multi-channel mode, port inputs are scanned and converted irrespective of Port AD configuration. Thus Port AD pins that are configured as digital inputs or digital outputs are also converted in the A/D conversion sequence.

# 1.3.4.17 PP[7] / KWP[7] — Port P I/O Pin [7]

PP7 is a general purpose input or output pin, shared with the keypad interrupt function. When configured as an input, it can generate interrupts causing the MCU to exit stop or wait mode. This pin is not available in the 48- / 52-pin package versions.

# 1.3.4.18 PP[6] / KWP[6]/ROMCTL — Port P I/O Pin [6]

PP6 is a general purpose input or output pin, shared with the keypad interrupt function. When configured as an input, it can generate interrupts causing the MCU to exit stop or wait mode. This pin is not available in the 48-/52-pin package versions. During MCU expanded modes of operation, this pin is used to enable

Chapter 2 Port Integration Module (PIM9C32) Block Description

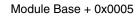

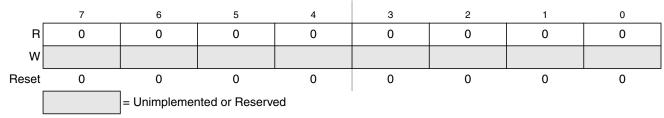

## 2.3.2.1.6 Port T Polarity Select Register (PTTST)

Figure 2-8. Port T Polarity Select Register (PPST)

Read: Anytime.

Write: Anytime.

### Table 2-8. PPST Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>PPST[7:0] | <ul> <li>Pull Select Port T — This register selects whether a pull-down or a pull-up device is connected to the pin.</li> <li>A pull-up device is connected to the associated port T pin, if enabled by the associated bit in register PERT and if the port is used as input.</li> <li>A pull-down device is connected to the associated port T pin, if enabled by the associated bit in register PERT and if the port is used as input.</li> </ul> |

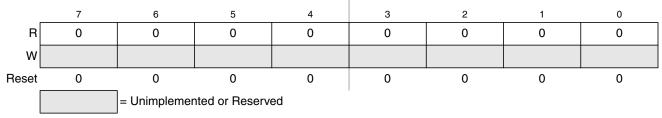

### 2.3.2.1.7 Port T Module Routing Register (MODRR)

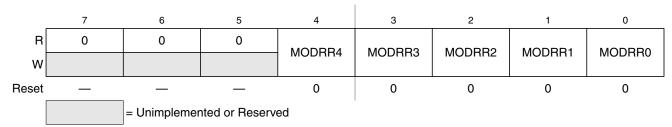

### Figure 2-9. Port T Module Routing Register (MODRR)

Read: Anytime.

Write: Anytime.

### NOTE

MODRR[4] must be kept clear on devices featuring a 4 channel PWM.

### Table 2-9. MODRR Field Descriptions

|   | Field      | Description                                                                            |  |  |  |  |  |  |

|---|------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|

|   | 4–0        | Module Routing Register Port T — This register selects the module connected to port T. |  |  |  |  |  |  |

| N | 10DRR[4:0] | 0 Associated pin is connected to TIM module                                            |  |  |  |  |  |  |

|   |            | 1 Associated pin is connected to PWM module                                            |  |  |  |  |  |  |

#### Chapter 6 Background Debug Module (BDMV4) Block Description

The commands are described as follows:

- ACK\_ENABLE enables the hardware handshake protocol. The target will issue the ACK pulse when a CPU command is executed by the CPU. The ACK\_ENABLE command itself also has the ACK pulse as a response.

- ACK\_DISABLE disables the ACK pulse protocol. In this case, the host needs to use the worst case delay time at the appropriate places in the protocol.

The default state of the BDM after reset is hardware handshake protocol disabled.

All the read commands will ACK (if enabled) when the data bus cycle has completed and the data is then ready for reading out by the BKGD serial pin. All the write commands will ACK (if enabled) after the data has been received by the BDM through the BKGD serial pin and when the data bus cycle is complete. See Section 6.4.3, "BDM Hardware Commands," and Section 6.4.4, "Standard BDM Firmware Commands," for more information on the BDM commands.

The ACK\_ENABLE sends an ACK pulse when the command has been completed. This feature could be used by the host to evaluate if the target supports the hardware handshake protocol. If an ACK pulse is issued in response to this command, the host knows that the target supports the hardware handshake protocol. If the target does not support the hardware handshake protocol the ACK pulse is not issued. In this case, the ACK\_ENABLE command is ignored by the target because it is not recognized as a valid command.

The BACKGROUND command will issue an ACK pulse when the CPU changes from normal to background mode. The ACK pulse related to this command could be aborted using the SYNC command.

The GO command will issue an ACK pulse when the CPU exits from background mode. The ACK pulse related to this command could be aborted using the SYNC command.

The GO\_UNTIL command is equivalent to a GO command with exception that the ACK pulse, in this case, is issued when the CPU enters into background mode. This command is an alternative to the GO command and should be used when the host wants to trace if a breakpoint match occurs and causes the CPU to enter active background mode. Note that the ACK is issued whenever the CPU enters BDM, which could be caused by a breakpoint match or by a BGND instruction being executed. The ACK pulse related to this command could be aborted using the SYNC command.

The TRACE1 command has the related ACK pulse issued when the CPU enters background active mode after one instruction of the application program is executed. The ACK pulse related to this command could be aborted using the SYNC command.

The TAGGO command will not issue an ACK pulse because this would interfere with the tagging function shared on the same pin.

#### Chapter 7 Debug Module (DBGV1) Block Description

#### Table 7-12. DBGCC Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0  | <ul> <li>Comparator C Compare Bits — The comparator C compare bits control whether comparator C will compare the address bus bits [15:0] to a logic 1 or logic 0. See Table 7-13.</li> <li>0 Compare corresponding address bit to a logic 0</li> <li>1 Compare corresponding address bit to a logic 1</li> <li>Note: This register will be cleared automatically when the DBG module is armed in LOOP1 mode.</li> </ul> |

#### Table 7-13. Comparator C Compares

| PAGSEL | EXTCMP Compare           | High-Byte Compare                 |

|--------|--------------------------|-----------------------------------|

| x0     | No compare               | DBGCCH[7:0] = AB[15:8]            |

| x1     | EXTCMP[5:0] = XAB[21:16] | DBGCCH[7:0] = XAB[15:14],AB[13:8] |

### 7.3.2.7 Debug Control Register 2 (DBGC2)

Module Base + 0x0028

Starting address location affected by INITRG register setting.

|        | 7                     | 6    | 5   | 4     | 3                    | 2                 | 1                  | 0                |

|--------|-----------------------|------|-----|-------|----------------------|-------------------|--------------------|------------------|

| R<br>W | BKABEN <sup>(1)</sup> | FULL | BDM | TAGAB | BKCEN <sup>(2)</sup> | TAGC <sup>2</sup> | RWCEN <sup>2</sup> | RWC <sup>2</sup> |

| Reset  | 0                     | 0    | 0   | 0     | 0                    | 0                 | 0                  | 0                |

1. When BKABEN is set (BKP mode), all bits in DBGC2 are available. When BKABEN is cleared and DBG is used in DBG mode, bits FULL and TAGAB have no meaning.

2. These bits can be used in BKP mode and DBG mode (when capture mode is not set in LOOP1) to provide a third breakpoint.

#### Figure 7-13. Debug Control Register 2 (DBGC2)

#### Table 7-14. DBGC2 Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>BKABEN | <ul> <li>Breakpoint Using Comparator A and B Enable — This bit enables the breakpoint capability using comparator A and B, when set (BKP mode) the DBGEN bit in DBGC1 cannot be set.</li> <li>0 Breakpoint module off</li> <li>1 Breakpoint module on</li> </ul>                                                                                                                |

| 6<br>FULL   | <ul> <li>Full Breakpoint Mode Enable — This bit controls whether the breakpoint module is in dual mode or full mode.<br/>In full mode, comparator A is used to match address and comparator B is used to match data. See<br/>Section 7.4.1.2, "Full Breakpoint Mode," for more details.</li> <li>0 Dual address mode enabled</li> <li>1 Full breakpoint mode enabled</li> </ul> |

| 5<br>BDM    | <ul> <li>Background Debug Mode Enable — This bit determines if the breakpoint causes the system to enter background debug mode (BDM) or initiate a software interrupt (SWI).</li> <li>0 Go to software interrupt on a break request</li> <li>1 Go to BDM on a break request</li> </ul>                                                                                          |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>AUTO | Automatic Bandwidth Control Bit — AUTO selects either the high bandwidth (acquisition) mode or the low bandwidth (tracking) mode depending on how close to the desired frequency the VCO is running. Write anytime except when PLLWAI=1, because PLLWAI sets the AUTO bit to 1.<br>0 Automatic mode control is disabled and the PLL is under software control, using ACQ bit.<br>1 Automatic mode control is enabled and ACQ bit has no effect. |

| 4<br>ACQ  | <ul> <li>Acquisition Bit — Write anytime. If AUTO=1 this bit has no effect.</li> <li>0 Low bandwidth filter is selected.</li> <li>1 High bandwidth filter is selected.</li> </ul>                                                                                                                                                                                                                                                               |

| 2<br>PRE  | <ul> <li>RTI Enable during Pseudo-Stop Bit — PRE enables the RTI during pseudo-stop mode. Write anytime.</li> <li>0 RTI stops running during pseudo-stop mode.</li> <li>1 RTI continues running during pseudo-stop mode.</li> <li>Note: If the PRE bit is cleared the RTI dividers will go static while pseudo-stop mode is active. The RTI dividers will not initialize like in wait mode with RTIWAI bit set.</li> </ul>                      |

| 1<br>PCE  | <ul> <li>COP Enable during Pseudo-Stop Bit — PCE enables the COP during pseudo-stop mode. Write anytime.</li> <li>0 COP stops running during pseudo-stop mode</li> <li>1 COP continues running during pseudo-stop mode</li> <li>Note: If the PCE bit is cleared the COP dividers will go static while pseudo-stop mode is active. The COP dividers will <i>not</i> initialize like in wait mode with COPWAI bit set.</li> </ul>                 |

| 0<br>SCME | <ul> <li>Self-Clock Mode Enable Bit — Normal modes: Write once — Special modes: Write anytime — SCME can not be cleared while operating in self-clock mode (SCM=1).</li> <li>0 Detection of crystal clock failure causes clock monitor reset (see Section 9.5.1, "Clock Monitor Reset").</li> <li>1 Detection of crystal clock failure forces the MCU in self-clock mode (see Section 9.4.7.2, "Self-Clock Mode").</li> </ul>                   |

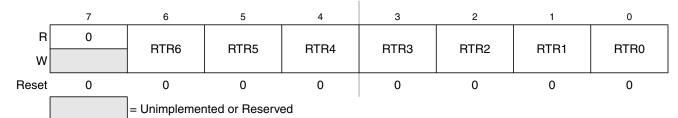

# 9.3.2.8 CRG RTI Control Register (RTICTL)

This register selects the timeout period for the real-time interrupt.

Module Base + 0x0007

### Figure 9-11. CRG RTI Control Register (RTICTL)

Read: anytime

Write: anytime

### NOTE

A write to this register initializes the RTI counter.

# 9.4.2 System Clocks Generator

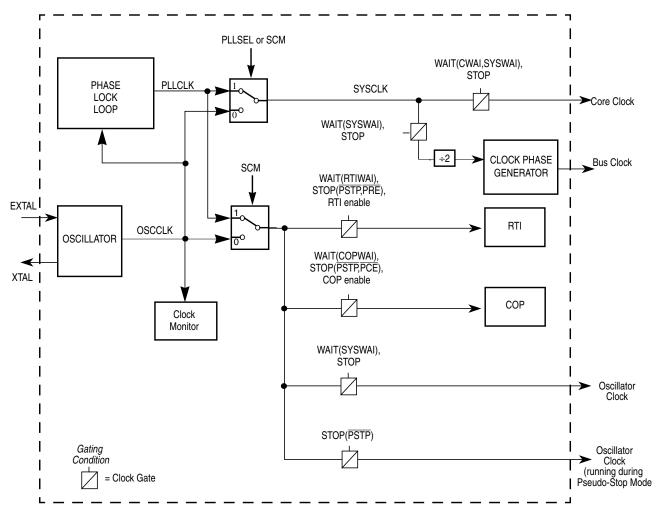

Figure 9-17. System Clocks Generator

The clock generator creates the clocks used in the MCU (see Figure 9-17). The gating condition placed on top of the individual clock gates indicates the dependencies of different modes (stop, wait) and the setting of the respective configuration bits.

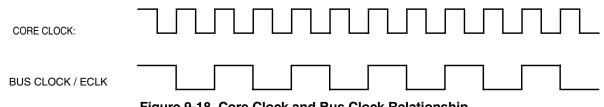

The peripheral modules use the bus clock. Some peripheral modules also use the oscillator clock. The memory blocks use the bus clock. If the MCU enters self-clock mode (see Section 9.4.7.2, "Self-Clock Mode"), oscillator clock source is switched to PLLCLK running at its minimum frequency  $f_{SCM}$ . The bus clock is used to generate the clock visible at the ECLK pin. The core clock signal is the clock for the CPU. The core clock is twice the bus clock as shown in Figure 9-18. But note that a CPU cycle corresponds to one bus clock.

PLL clock mode is selected with PLLSEL bit in the CLKSEL register. When selected, the PLL output clock drives SYSCLK for the main system including the CPU and peripherals. The PLL cannot be turned off by clearing the PLLON bit, if the PLL clock is selected. When PLLSEL is changed, it takes a maximum

#### Chapter 9 Clocks and Reset Generator (CRGV4) Block Description

of 4 OSCCLK plus 4 PLLCLK cycles to make the transition. During the transition, all clocks freeze and CPU activity ceases.

Figure 9-18. Core Clock and Bus Clock Relationship

# 9.4.3 Clock Monitor (CM)

If no OSCCLK edges are detected within a certain time, the clock monitor within the oscillator block generates a clock monitor fail event. The CRGV4 then asserts self-clock mode or generates a system reset depending on the state of SCME bit. If the clock monitor is disabled or the presence of clocks is detected no failure is indicated by the oscillator block. The clock monitor function is enabled/disabled by the CME control bit.

# 9.4.4 Clock Quality Checker

The clock monitor performs a coarse check on the incoming clock signal. The clock quality checker provides a more accurate check in addition to the clock monitor.

A clock quality check is triggered by any of the following events:

- Power-on reset (POR)

- Low voltage reset (LVR)

- Wake-up from full stop mode (exit full stop)

- Clock monitor fail indication (CM fail)

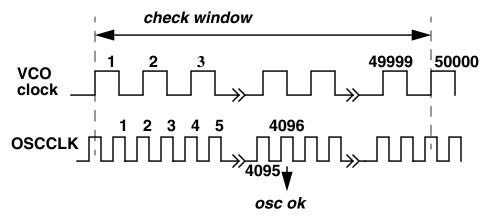

A time window of 50000 VCO clock cycles<sup>1</sup> is called *check window*.

A number greater equal than 4096 rising OSCCLK edges within a *check window* is called *osc ok*. Note that *osc ok* immediately terminates the current *check window*. See Figure 9-19 as an example.

Figure 9-19. Check Window Example

1. VCO clock cycles are generated by the PLL when running at minimum frequency  $\mathrm{f}_{\mathrm{SCM}}$

#### Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

| Register<br>Name          |        | Bit 7  | 6          | 5            | 4       | 3       | 2            | 1      | Bit 0  |

|---------------------------|--------|--------|------------|--------------|---------|---------|--------------|--------|--------|

| 0x0000<br>CANCTL0         | R<br>W | RXFRM  | RXACT      | CSWAI        | SYNCH   | TIME    | WUPE         | SLPRQ  | INITRQ |

| 0x0001<br>CANCTL1         | R<br>W | CANE   | CLKSRC     | LOOPB        | LISTEN  |         | WUPM         | SLPAK  | INITAK |

| 0x0002<br>CANBTR0         | R<br>W | SJW1   | SJW0       | BRP5         | BRP4    | BRP3    | BRP2         | BRP1   | BRP0   |

| 0x0003<br>CANBTR1         | R<br>W | SAMP   | TSEG22     | TSEG21       | TSEG20  | TSEG13  | TSEG12       | TSEG11 | TSEG10 |

| 0x0004<br>CANRFLG         | R<br>W | WUPIF  | CSCIF      | RSTAT1       | RSTAT0  | TSTAT1  | TSTAT0       | OVRIF  | RXF    |

| 0x0005<br>CANRIER         | R<br>W | WUPIE  | CSCIE      | RSTATE1      | RSTATE0 | TSTATE1 | TSTATE0      | OVRIE  | RXFIE  |

| 0x0006<br>CANTFLG         | R<br>W | 0      | 0          | 0            | 0       | 0       | TXE2         | TXE1   | TXE0   |

| 0x0007<br>CANTIER         | R<br>W | 0      | 0          | 0            | 0       | 0       | TXEIE2       | TXEIE1 | TXEIE0 |

| 0x0008<br>CANTARQ         | R<br>W | 0      | 0          | 0            | 0       | 0       | ABTRQ2       | ABTRQ1 | ABTRQ0 |

| 0x0009<br>CANTAAK         | R<br>W | 0      | 0          | 0            | 0       | 0       | ABTAK2       | ABTAK1 | ABTAK0 |

| 0x000A<br>CANTBSEL        | R<br>W | 0      | 0          | 0            | 0       | 0       | TX2          | TX1    | TX0    |

| 0x000B<br>CANIDAC         | R<br>W | 0      | 0          | IDAM1        | IDAM0   | 0       | IDHIT2       | IDHIT1 | IDHIT0 |

| 0x000C–0x000D<br>Reserved | R<br>W | 0      | 0          | 0            | 0       | 0       | 0            | 0      | 0      |

| 0x000E<br>CANRXERR        | R<br>W | RXERR7 | RXERR6     | RXERR5       | RXERR4  | RXERR3  | RXERR2       | RXERR1 | RXERR0 |

| 0x000F<br>CANTXERR        | R<br>W | TXERR7 | TXERR6     | TXERR5       | TXERR4  | TXERR3  | TXERR2       | TXERR1 | TXERR0 |

|                           |        |        | = Unimplen | nented or Re | served  |         | u = Unaffect | ted    |        |

Figure 10-3. MSCAN Register Summary

#### Chapter 10 Freescale's Scalable Controller Area Network (S12MSCANV2)

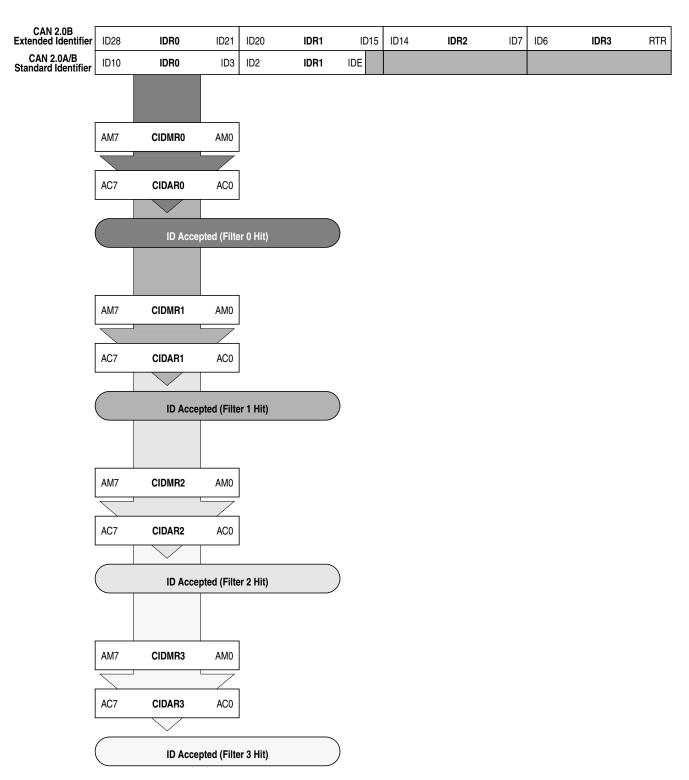

### Figure 10-41. 8-bit Maskable Identifier Acceptance Filters

### Table 12-3. PWMPOL Field Descriptions (continued)

| Field      | Description                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PPOL3 | Pulse Width Channel 3 Polarity0PWM channel 3 output is low at the beginning of the period, then goes high when the duty count is reached.1PWM channel 3 output is high at the beginning of the period, then goes low when the duty count is reached.                                           |

| 2<br>PPOL2 | Pulse Width Channel 2 Polarity0PWM channel 2 output is low at the beginning of the period, then goes high when the duty count is reached.1PWM channel 2 output is high at the beginning of the period, then goes low when the duty count is reached.                                           |

| 1<br>PPOL1 | <ul> <li>Pulse Width Channel 1 Polarity</li> <li>0 PWM channel 1 output is low at the beginning of the period, then goes high when the duty count is reached.</li> <li>1 PWM channel 1 output is high at the beginning of the period, then goes low when the duty count is reached.</li> </ul> |

| 0<br>PPOL0 | Pulse Width Channel 0 Polarity0PWM channel 0 output is low at the beginning of the period, then goes high when the duty count is reached1PWM channel 0 output is high at the beginning of the period, then goes low when the duty count is reached.                                            |

## 12.3.2.3 PWM Clock Select Register (PWMCLK)

Each PWM channel has a choice of two clocks to use as the clock source for that channel as described below.

Module Base + 0x0002

|       | 7                           | 6 | 5      | 4      | 3      | 2     | 1     | 0       |

|-------|-----------------------------|---|--------|--------|--------|-------|-------|---------|

| R     | 0                           | 0 | PCLK5  | PCLK4  | PCLK3  | PCLK2 | PCLK1 | PCLK0   |

| w     |                             |   | I OEKS | T OLN4 | I OLKO | TOLKZ | TOLKI | I OLIKO |

| Reset | 0                           | 0 | 0      | 0      | 0      | 0     | 0     | 0       |

|       | = Unimplemented or Reserved |   |        |        |        |       |       |         |

### Figure 12-5. PWM Clock Select Register (PWMCLK)

Read: anytime

Write: anytime

### NOTE

Register bits PCLK0 to PCLK5 can be written anytime. If a clock select is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

## 12.3.2.7 Reserved Register (PWMTST)

This register is reserved for factory testing of the PWM module and is not available in normal modes.

Module Base + 0x0006

Figure 12-9. Reserved Register (PWMTST)

Read: always read 0x0000 in normal modes

Write: unimplemented in normal modes

### NOTE

Writing to this register when in special modes can alter the PWM functionality.

### 12.3.2.8 Reserved Register (PWMPRSC)

This register is reserved for factory testing of the PWM module and is not available in normal modes.

Module Base + 0x0007

### Figure 12-10. Reserved Register (PWMPRSC)

Read: always read 0x0000 in normal modes

Write: unimplemented in normal modes

### NOTE

Writing to this register when in special modes can alter the PWM functionality.

Chapter 12 Pulse-Width Modulator (PWM8B6CV1) Block Description

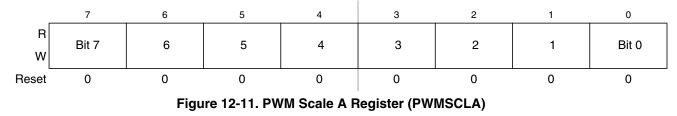

# 12.3.2.9 PWM Scale A Register (PWMSCLA)

PWMSCLA is the programmable scale value used in scaling clock A to generate clock SA. Clock SA is generated by taking clock A, dividing it by the value in the PWMSCLA register and dividing that by two.

Clock SA = Clock A / (2 \* PWMSCLA)

### NOTE

When PWMSCLA = 0x0000, PWMSCLA value is considered a full scale value of 256. Clock A is thus divided by 512.

Any value written to this register will cause the scale counter to load the new scale value (PWMSCLA).

Module Base + 0x0008

Read: anytime

Write: anytime (causes the scale counter to load the PWMSCLA value)

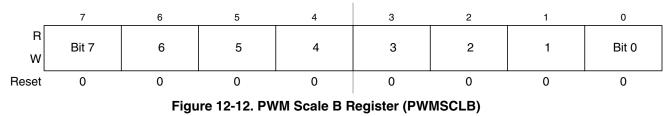

# 12.3.2.10 PWM Scale B Register (PWMSCLB)

PWMSCLB is the programmable scale value used in scaling clock B to generate clock SB. Clock SB is generated by taking clock B, dividing it by the value in the PWMSCLB register and dividing that by two.

Clock SB = Clock B / (2 \* PWMSCLB)

### NOTE

When PWMSCLB = 0x0000, PWMSCLB value is considered a full scale value of 256. Clock B is thus divided by 512.

Any value written to this register will cause the scale counter to load the new scale value (PWMSCLB).

Module Base + 0x0009

Read: anytime

Write: anytime (causes the scale counter to load the PWMSCLB value).

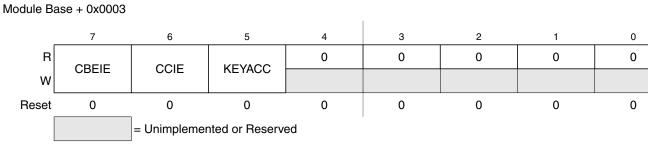

# 18.3.2.4 Flash Configuration Register (FCNFG)

The FCNFG register enables the Flash interrupts and gates the security backdoor key writes.

### Figure 18-7. Flash Configuration Register (FCNFG)

CBEIE, CCIE, and KEYACC are readable and writable while remaining bits read 0 and are not writable. KEYACC is only writable if the KEYEN bit in the FSEC register is set to the enabled state (see Section 18.3.2.2).

| Field       | Description                                                                                                                                                                                                                                                                                                  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CBEIE  | <ul> <li>Command Buffer Empty Interrupt Enable — The CBEIE bit enables the interrupts in case of an empty command buffer in the Flash module.</li> <li>0 Command Buffer Empty interrupts disabled</li> <li>1 An interrupt will be requested whenever the CBEIF flag is set (see Section 18.3.2.6)</li> </ul> |

| 6<br>CCIE   | <ul> <li>Command Complete Interrupt Enable — The CCIE bit enables the interrupts in case of all commands being completed in the Flash module.</li> <li>0 Command Complete interrupts disabled</li> <li>1 An interrupt will be requested whenever the CCIF flag is set (see Section 18.3.2.6)</li> </ul>      |

| 5<br>KEYACC | <ul> <li>Enable Security Key Writing.</li> <li>0 Flash writes are interpreted as the start of a command write sequence</li> <li>1 Writes to the Flash array are interpreted as a backdoor key while reads of the Flash array return invalid data</li> </ul>                                                  |

### Table 18-7. FCNFG Field Descriptions

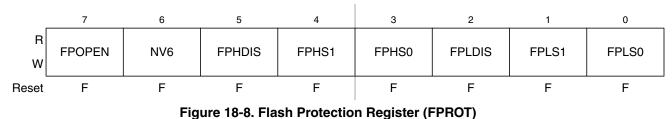

### 18.3.2.5 Flash Protection Register (FPROT)

The FPROT register defines which Flash sectors are protected against program or erase.

Module Base + 0x0004

The FPROT register is readable in normal and special modes. FPOPEN can only be written from a 1 to a 0. FPLS[1:0] can be written anytime until FPLDIS is cleared. FPHS[1:0] can be written anytime until

```

NP

```

```

Chapter 18 32 Kbyte Flash Module (S12FTS32KV1)

```

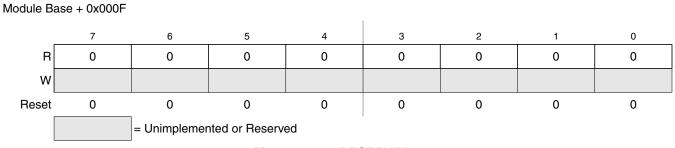

Figure 18-20. RESERVED6

All bits read 0 and are not writable.

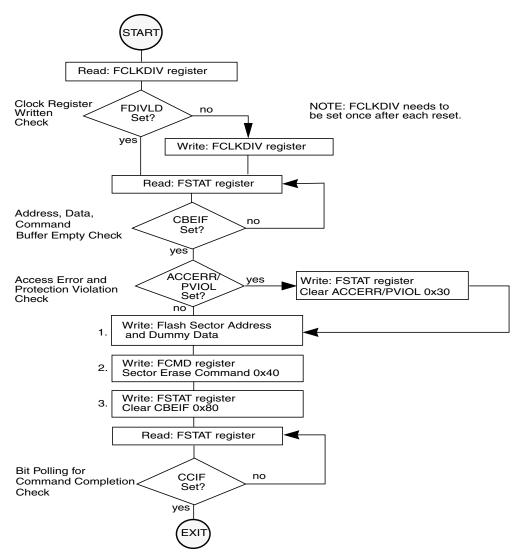

# 18.4 Functional Description

# 18.4.1 Flash Command Operations

Write operations are used for the program, erase, and erase verify algorithms described in this section. The program and erase algorithms are controlled by a state machine whose timebase FCLK is derived from the oscillator clock via a programmable divider. The FCMD register as well as the associated FADDR and FDATA registers operate as a buffer and a register (2-stage FIFO) so that a new command along with the necessary data and address can be stored to the buffer while the previous command is still in progress. This pipelined operation allows a time optimization when programming more than one word on a specific row, as the high voltage generation can be kept active in between two programming commands. The pipelined operation allows a simplification of command launching. Buffer empty as well as command completion are signalled by flags in the FSTAT register with corresponding interrupts generated, if enabled.

The next sections describe:

- How to write the FCLKDIV register

- Command write sequence used to program, erase or erase verify the Flash array

- Valid Flash commands

- Errors resulting from illegal Flash operations

# 18.4.1.1 Writing the FCLKDIV Register

Prior to issuing any Flash command after a reset, it is first necessary to write the FCLKDIV register to divide the oscillator clock down to within the 150-kHz to 200-kHz range. Since the program and erase timings are also a function of the bus clock, the FCLKDIV determination must take this information into account.

If we define:

- FCLK as the clock of the Flash timing control block

- Tbus as the period of the bus clock

- INT(x) as taking the integer part of x (e.g., INT(4.323) = 4),

| FPOPEN | FPHDIS | FPHS[1] | FPHS[0] | FPLDIS | FPLS[1] | FPLS[0] | Function <sup>(1)</sup>         |

|--------|--------|---------|---------|--------|---------|---------|---------------------------------|

| 1      | 1      | х       | х       | 1      | х       | х       | No protection                   |

| 1      | 1      | х       | х       | 0      | х       | х       | Protect low range               |

| 1      | 0      | х       | х       | 1      | х       | х       | Protect high range              |

| 1      | 0      | х       | х       | 0      | х       | х       | Protect high and low ranges     |

| 0      | 1      | х       | х       | 1      | х       | х       | Full Flash array protected      |

| 0      | 0      | х       | х       | 1      | х       | х       | Unprotected high range          |

| 0      | 1      | х       | х       | 0      | х       | х       | Unprotected low range           |

| 0      | 0      | х       | х       | 0      | х       | х       | Unprotected high and low ranges |

#### Table 20-10. Flash Protection Function

1. For range sizes refer to Table 20-11 and Table 20-12 or .

| Table 20-11. | Flash | Protection | Hiaher | Address | Range |

|--------------|-------|------------|--------|---------|-------|

|              |       |            |        |         |       |

| FPHS[1:0] | Address Range | Range Size |

|-----------|---------------|------------|

| 00        | 0xF800-0xFFFF | 2 Kbytes   |

| 01        | 0xF000-0xFFFF | 4 Kbytes   |

| 10        | 0xE000-0xFFFF | 8 Kbytes   |

| 11        | 0xC000-0xFFFF | 16 Kbytes  |

### Table 20-12. Flash Protection Lower Address Range

| FPLS[1:0] | Address Range | Range Size |

|-----------|---------------|------------|

| 00        | 0x4000-0x43FF | 1 Kbyte    |

| 01        | 0x4000-0x47FF | 2 Kbytes   |

| 10        | 0x4000-0x4FFF | 4 Kbytes   |

| 11        | 0x4000-0x5FFF | 8 Kbytes   |

Figure 20-11 illustrates all possible protection scenarios. Although the protection scheme is loaded from the Flash array after reset, it is allowed to change in normal modes. This protection scheme can be used by applications requiring re-programming in single chip mode while providing as much protection as possible if no re-programming is required.

### 21.4.1.4 Illegal Flash Operations

### 21.4.1.4.1 Access Error

The ACCERR flag in the FSTAT register will be set during the command write sequence if any of the following illegal Flash operations are performed causing the command write sequence to immediately abort:

- 1. Writing to the Flash address space before initializing the FCLKDIV register

- 2. Writing a misaligned word or a byte to the valid Flash address space

- 3. Writing to the Flash address space while CBEIF is not set

- 4. Writing a second word to the Flash address space before executing a program or erase command on the previously written word

- 5. Writing to any Flash register other than FCMD after writing a word to the Flash address space

- 6. Writing a second command to the FCMD register before executing the previously written command

- 7. Writing an invalid command to the FCMD register

- 8. Writing to any Flash register other than FSTAT (to clear CBEIF) after writing to the FCMD register

- 9. The part enters stop mode and a program or erase command is in progress. The command is aborted and any pending command is killed

- 10. When security is enabled, a command other than mass erase originating from a non-secure memory or from the background debug mode is written to the FCMD register

- 11. A 0 is written to the CBEIF bit in the FSTAT register to abort a command write sequence.

The ACCERR flag will not be set if any Flash register is read during the command write sequence. If the Flash array is read during execution of an algorithm (CCIF=0), the Flash module will return invalid data and the ACCERR flag will not be set. If an ACCERR flag is set in the FSTAT register, the Flash command controller is locked. It is not possible to launch another command until the ACCERR flag is cleared.

### 21.4.1.4.2 Protection Violation

The PVIOL flag in the FSTAT register will be set during the command write sequence after the word write to the Flash address space if any of the following illegal Flash operations are performed, causing the command write sequence to immediately abort:

- 1. Writing a Flash address to program in a protected area of the Flash array (see Section 21.3.2.5).

- 2. Writing a Flash address to erase in a protected area of the Flash array.

- 3. Writing the mass erase command to the FCMD register while any protection is enabled.

If the PVIOL flag is set, the Flash command controller is locked. It is not possible to launch another command until the PVIOL flag is cleared.

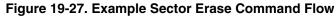

In Figure A-9 the timing diagram for slave mode with transmission format CPHA=1 is depicted.

### Figure A-9. SPI Slave Timing (CPHA=1)

In Table A-22 the timing characteristics for slave mode are listed.

| Num | С | Characteristic                          | Symbol            | Min | Тур | Max                                | Unit             |

|-----|---|-----------------------------------------|-------------------|-----|-----|------------------------------------|------------------|

| 1   | D | SCK Frequency                           | f <sub>sck</sub>  | DC  | —   | 1/4                                | f <sub>bus</sub> |

| 1   | Р | SCK Period                              | t <sub>sck</sub>  | 4   | —   | ∞                                  | t <sub>bus</sub> |

| 2   | D | Enable Lead Time                        | t <sub>lead</sub> | 4   | —   | —                                  | t <sub>bus</sub> |

| 3   | D | Enable Lag Time                         | t <sub>lag</sub>  | 4   | —   | —                                  | t <sub>bus</sub> |

| 4   | D | Clock (SCK) High or Low Time            | t <sub>wsck</sub> | 4   | —   | —                                  | t <sub>bus</sub> |

| 5   | D | Data Setup Time (Inputs)                | t <sub>su</sub>   | 8   | —   | —                                  | ns               |

| 6   | D | Data Hold Time (Inputs)                 | t <sub>hi</sub>   | 8   | —   | —                                  | ns               |

| 7   | D | Slave Access Time (time to data active) | t <sub>a</sub>    |     | —   | 20                                 | ns               |

| 8   | D | Slave MISO Disable Time                 | t <sub>dis</sub>  | _   | —   | 22                                 | ns               |

| 9   | D | Data Valid after SCK Edge               | t <sub>vsck</sub> | —   | _   | 30 + t <sub>bus</sub><br>(1)       | ns               |

| 10  | D | Data Valid after SS fall                | t <sub>vss</sub>  |     | —   | 30 + t <sub>bus</sub> <sup>1</sup> | ns               |

| 11  | D | Data Hold Time (Outputs)                | t <sub>ho</sub>   | 20  | —   | —                                  | ns               |

| 12  | D | Rise and Fall Time Inputs               | t <sub>rfi</sub>  |     | —   | 8                                  | ns               |

| 13  | D | Rise and Fall Time Outputs              | t <sub>rfo</sub>  |     | —   | 8                                  | ns               |

Table A-22. SPI Slave Mode Timing Characteristics

1. t<sub>bus</sub> added due to internal synchronization delay

Appendix A Electrical Characteristics

# A.7.3 Output Loads

### A.7.3.1 Resistive Loads

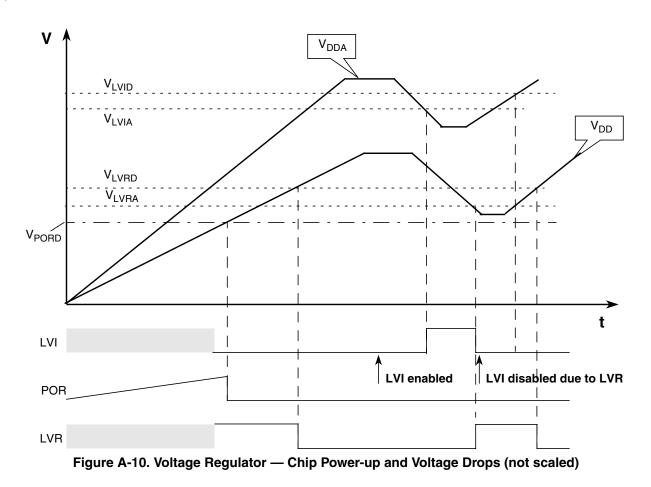

The on-chip voltage regulator is intended to supply the internal logic and oscillator circuits allows no external DC loads.

### A.7.3.2 Capacitive Loads

The capacitive loads are specified in Table A-24. Ceramic capacitors with X7R dielectricum are required.

| Table A-24. Voltage Regulator — | Capacitive Loads |

|---------------------------------|------------------|

|---------------------------------|------------------|

| Num | Characteristic                              | Symbol                | Min | Typical | Max   | Unit |

|-----|---------------------------------------------|-----------------------|-----|---------|-------|------|

| 1   | V <sub>DD</sub> external capacitive load    | C <sub>DDext</sub>    | 400 | 440     | 12000 | nF   |

| 2   | V <sub>DDPLL</sub> external capacitive load | C <sub>DDPLLext</sub> | 90  | 220     | 5000  | nF   |