Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | EBI/EMI, SCI, SPI                                                      |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 31                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12gc64mfae |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

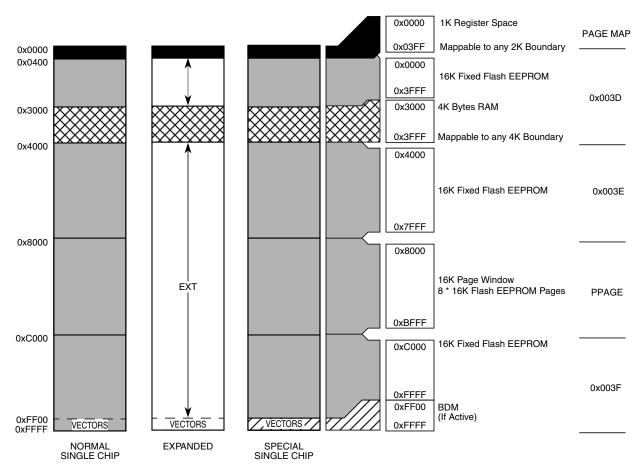

The figure shows a useful map, which is not the map out of reset. After reset the map is: 0x0000–0x03FF: Register Space

0x0000-0x0FFF: 4K RAM (only 3K visible 0x0400-0x0FFF)

Flash erase sector size is 1024 bytes

#### Figure 1-2. MC9S12C128 and MC9S12GC128 User Configurable Memory Map

| Address | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0180- | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x023F  | neserveu | Write: |       |       |       |       |       |       |       |       |

#### 0x0180–0x023F Reserved

### 0x0240–0x027F PIM (Port Interface Module) (Sheet 1 of 3)

| Address | Name     |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  |

|---------|----------|-----------------|-------|-------|-------|--------|--------|--------|---------|--------|

| 0x0240  | PTT      | Read:<br>Write: | PTT7  | PTT6  | PTT5  | PTT4   | PTT3   | PTT2   | PTT1    | PTT0   |

| 0.0041  | DTIT     | Read:           | PTIT7 | PTIT6 | PTIT5 | PTIT4  | PTIT3  | PTIT2  | PTIT1   | PTIT0  |

| 0x0241  | PTIT     | Write:          |       |       |       |        |        |        |         |        |

| 0x0242  | DDRT     | Read:<br>Write: | DDRT7 | DDRT7 | DDRT5 | DDRT4  | DDRT3  | DDRT2  | DDRT1   | DDRT0  |

| 0x0243  | RDRT     | Read:<br>Write: | RDRT7 | RDRT6 | RDRT5 | RDRT4  | RDRT3  | RDRT2  | RDRT1   | RDRT0  |

| 0x0244  | PERT     | Read:<br>Write: | PERT7 | PERT6 | PERT5 | PERT4  | PERT3  | PERT2  | PERT1   | PERT0  |

| 0x0245  | PPST     | Read:<br>Write: | PPST7 | PPST6 | PPST5 | PPST4  | PPST3  | PPST2  | PPST1   | PPST0  |

| 0x0246  | Reserved | Read:           | 0     | 0     | 0     | 0      | 0      | 0      | 0       | 0      |

| OXOL 10 |          | Write:          |       |       |       |        |        |        |         |        |

| 0x0247  | MODRR    | Read:           | 0     | 0     | 0     | MODRR4 | MODRR3 | MODRR2 | MODRR1  | MODRR0 |

|         |          | Write:<br>Read: | 0     | 0     | 0     | 0      |        | PTS2   | PTS1    | PTS0   |

| 0x0248  | PTS      | Write:          | 0     | 0     | 0     | 0      | PTS3   |        |         |        |

|         |          | Read:           | 0     | 0     | 0     | 0      | PTIS3  | PTIS2  | PTIS1   | PTIS0  |

| 0x0249  | PTIS     | Write:          |       |       |       |        |        |        |         |        |

| 0x024A  | DDRS     | Read:           | 0     | 0     | 0     | 0      | DDRS3  | DDRS2  | DDRS1   | DDRS0  |

| 070244  | DDI10    | Write:          |       |       |       |        | DDI100 |        | DDITIOT |        |

| 0x024B  | RDRS     | Read:           | 0     | 0     | 0     | 0      | RDRS3  | RDRS2  | RDRS1   | RDRS0  |

|         |          | Write:          |       |       |       |        |        |        |         |        |

| 0x024C  | PERS     | Read:           | 0     | 0     | 0     | 0      | PERS3  | PERS2  | PERS1   | PERS0  |

|         |          | Write:<br>Read: | 0     | 0     | 0     | 0      |        |        |         |        |

| 0x024D  | PPSS     | Write:          | 0     | 0     | 0     | 0      | PPSS3  | PPSS2  | PPSS1   | PPSS0  |

|         |          | Read:           | 0     | 0     | 0     | 0      |        |        |         |        |

| 0x024E  | WOMS     | Write:          |       |       |       |        | WOMS3  | WOMS2  | WOMS1   | WOMS0  |

| 0.0045  | Decerved | Read:           | 0     | 0     | 0     | 0      | 0      | 0      | 0       | 0      |

| 0x024F  | Reserved | Write:          |       |       |       |        |        |        |         |        |

| 0x0250  | PTM      | Read:           | 0     | 0     | PTM5  | PTM4   | PTM3   | PTM2   | PTM1    | PTM0   |

| 0.0200  |          | Write:          |       |       |       |        |        |        |         |        |

| 0x0251  | PTIM     | Read:           | 0     | 0     | PTIM5 | PTIM4  | PTIM3  | PTIM2  | PTIM1   | PTIM0  |

| -       |          | Write:          |       | -     |       |        |        |        |         |        |

| 0x0252  | DDRM     | Read:           | 0     | 0     | DDRM5 | DDRM4  | DDRM3  | DDRM2  | DDRM1   | DDRM0  |

|         |          | Write:          |       |       |       |        |        |        |         |        |

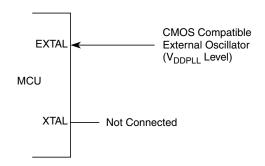

Figure 1-13. External Clock Connections (PE7 = 0)

### 1.3.4.9 PE6 / MODB / IPIPE1 — Port E I/O Pin 6

PE6 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODB bit at the rising edge of  $\overline{\text{RESET}}$ . This pin is shared with the instruction queue tracking signal IPIPE1. This pin is an input with a pull-down device which is only active when  $\overline{\text{RESET}}$  is low. PE[6] is not available in the 48- / 52-pin package versions.

## 1.3.4.10 PE5 / MODA / IPIPE0 — Port E I/O Pin 5

PE5 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODA bit at the rising edge of  $\overline{\text{RESET}}$ . This pin is shared with the instruction queue tracking signal IPIPE0. This pin is an input with a pull-down device which is only active when  $\overline{\text{RESET}}$  is low. This pin is not available in the 48- / 52-pin package versions.

## 1.3.4.11 PE4 / ECLK— Port E I/O Pin [4] / E-Clock Output

ECLK is the output connection for the internal bus clock. It is used to demultiplex the address and data in expanded modes and is used as a timing reference. ECLK frequency is equal to 1/2 the crystal frequency out of reset. The ECLK pin is initially configured as ECLK output with stretch in all expanded modes. The E clock output function depends upon the settings of the NECLK bit in the PEAR register, the IVIS bit in the MODE register and the ESTR bit in the EBICTL register. All clocks, including the E clock, are halted when the MCU is in stop mode. It is possible to configure the MCU to interface to slow external memory. ECLK can be stretched for such accesses. Reference the MISC register (EXSTR[1:0] bits) for more information. In normal expanded narrow mode, the E clock is available for use in external select decode logic or as a constant speed clock for use in the external application system. Alternatively PE4 can be used as a general purpose input or output pin.

## 1.3.4.12 PE3 / LSTRB — Port E I/O Pin [3] / Low-Byte Strobe (LSTRB)

In all modes this pin can be used as a general-purpose I/O and is an input with an active pull-up out of reset. If the strobe function is required, it should be enabled by setting the LSTRE bit in the PEAR register. This signal is used in write operations. Therefore external low byte writes will not be possible until this function is enabled. This pin is also used as TAGLO in special expanded modes and is multiplexed with the LSTRB function. This pin is not available in the 48- / 52-pin package versions.

the Flash EEPROM memory in the memory map (ROMCTL). At the rising edge of  $\overline{\text{RESET}}$ , the state of this pin is latched to the ROMON bit.

- PP6 = 1 in emulation modes equates to ROMON = 0 (ROM space externally mapped)

- PP6 = 0 in expanded modes equates to ROMON = 0 (ROM space externally mapped)

## 1.3.4.19 PP[5:0] / KWP[5:0] / PW[5:0] — Port P I/O Pins [5:0]

PP[5:0] are general purpose input or output pins, shared with the keypad interrupt function. When configured as inputs, they can generate interrupts causing the MCU to exit stop or wait mode.

PP[5:0] are also shared with the PWM output signals, PW[5:0]. Pins PP[2:0] are only available in the 80-pin package version. Pins PP[4:3] are not available in the 48-pin package version.

## 1.3.4.20 PJ[7:6] / KWJ[7:6] — Port J I/O Pins [7:6]

PJ[7:6] are general purpose input or output pins, shared with the keypad interrupt function. When configured as inputs, they can generate interrupts causing the MCU to exit stop or wait mode. These pins are not available in the 48-pin package version nor in the 52-pin package version.

### 1.3.4.21 PM5 / SCK — Port M I/O Pin 5

PM5 is a general purpose input or output pin and also the serial clock pin SCK for the serial peripheral interface (SPI).

### 1.3.4.22 PM4 / MOSI — Port M I/O Pin 4

PM4 is a general purpose input or output pin and also the master output (during master mode) or slave input (during slave mode) pin for the serial peripheral interface (SPI).

### 1.3.4.23 PM3 / SS — Port M I/O Pin 3

PM3 is a general purpose input or output pin and also the slave select pin  $\overline{SS}$  for the serial peripheral interface (SPI).

### 1.3.4.24 PM2 / MISO — Port M I/O Pin 2

PM2 is a general purpose input or output pin and also the master input (during master mode) or slave output (during slave mode) pin for the serial peripheral interface (SPI).

### 1.3.4.25 PM1 / TXCAN — Port M I/O Pin 1

PM1 is a general purpose input or output pin and the transmit pin, TXCAN, of the CAN module if available.

### 1.3.4.26 PM0 / RXCAN — Port M I/O Pin 0

PM0 is a general purpose input or output pin and the receive pin, RXCAN, of the CAN module if available.

Chapter 2 Port Integration Module (PIM9C32) Block Description

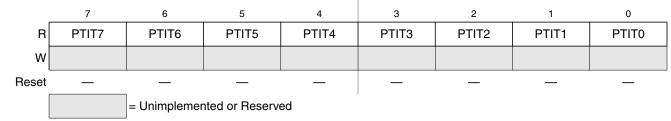

## 2.3.2.1.2 Port T Input Register (PTIT)

Module Base + 0x0001

#### Figure 2-4. Port T Input Register (PTIT)

#### Read: Anytime.

Write: Never, writes to this register have no effect.

| Table 2-4 | PTIT | Field | Descriptions |

|-----------|------|-------|--------------|

|-----------|------|-------|--------------|

| Field            | Description                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>PTIT[7:0] | <b>Port T Input Register</b> — This register always reads back the status of the associated pins. This can also be used to detect overload or short circuit conditions on output pins. |

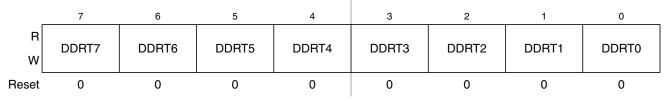

### 2.3.2.1.3 Port T Data Direction Register (DDRT)

Module Base + 0x0002

Figure 2-5. Port T Data Direction Register (DDRT)

Read: Anytime.

Write: Anytime.

### Table 2-5. DDRT Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7–0       | Data Direction Port T — This register configures each port T pin as either input or output.                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| DDRT[7:0] | The standard TIM / PWM modules forces the I/O state to be an output for each standard TIM / PWM module port associated with an enabled output compare. In these cases the data direction bits will not change.                                                                                                                                                        |  |  |  |  |  |  |

|           | The DDRT bits revert to controlling the I/O direction of a pin when the associated timer output compare is disabled.                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|           | <ul> <li>The timer input capture always monitors the state of the pin.</li> <li>Associated pin is configured as input.</li> <li>Associated pin is configured as output.</li> <li>Note: Due to internal synchronization circuits, it can take up to 2 bus cycles until the correct value is read on PTT or PTIT registers, when changing the DDRT register.</li> </ul> |  |  |  |  |  |  |

Chapter 7 Debug Module (DBGV1) Block Description

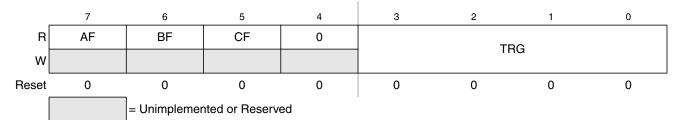

## 7.3.2.2 Debug Status and Control Register (DBGSC)

Module Base + 0x0021

Starting address location affected by INITRG register setting.

### Figure 7-5. Debug Status and Control Register (DBGSC)

| Field      | Description                                                                                                                                                                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>AF    | <ul> <li>Trigger A Match Flag — The AF bit indicates if trigger A match condition was met since arming. This bit is cleared when ARM in DBGC1 is written to a 1 or on any write to this register.</li> <li>0 Trigger A did not match</li> <li>1 Trigger A match</li> </ul>             |

| 6<br>BF    | <ul> <li>Trigger B Match Flag — The BF bit indicates if trigger B match condition was met since arming. This bit is cleared when ARM in DBGC1 is written to a 1 or on any write to this register.</li> <li>0 Trigger B did not match</li> <li>1 Trigger B match</li> </ul>             |

| 5<br>CF    | <ul> <li>Comparator C Match Flag — The CF bit indicates if comparator C match condition was met since arming. This bit is cleared when ARM in DBGC1 is written to a 1 or on any write to this register.</li> <li>0 Comparator C did not match</li> <li>1 Comparator C match</li> </ul> |

| 3:0<br>TRG | <b>Trigger Mode Bits</b> — The TRG bits select the trigger mode of the DBG module as shown Table 7-6. See Section 7.4.2.5, "Trigger Modes," for more detail.                                                                                                                           |

### Table 7-5. DBGSC Field Descriptions

#### Table 7-6. Trigger Mode Encoding

| TRG Value         | Meaning                          |

|-------------------|----------------------------------|

| 0000              | A only                           |

| 0001              | A or B                           |

| 0010              | A then B                         |

| 0011              | Event only B                     |

| 0100              | A then event only B              |

| 0101              | A and B (full mode)              |

| 0110              | A and Not B (full mode)          |

| 0111              | Inside range                     |

| 1000              | Outside range                    |

| 1001<br>↓<br>1111 | Reserved<br>(Defaults to A only) |

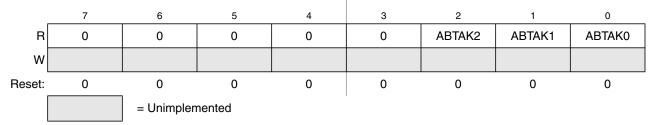

### 10.3.2.10 MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

The CANTAAK register indicates the successful abort of a queued message, if requested by the appropriate bits in the CANTARQ register.

Module Base + 0x0009

Figure 10-13. MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

### NOTE

The CANTAAK register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1).

Read: Anytime Write: Unimplemented for ABTAKx flags

#### Table 10-14. CANTAAK Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0<br>ABTAK[2:0] | <ul> <li>Abort Acknowledge — This flag acknowledges that a message was aborted due to a pending abort request from the CPU. After a particular message buffer is flagged empty, this flag can be used by the application software to identify whether the message was aborted successfully or was sent anyway. The ABTAKx flag is cleared whenever the corresponding TXE flag is cleared.</li> <li>0 The message was not aborted.</li> <li>1 The message was aborted.</li> </ul> |

### NOTE

Reading this register when in any other mode other than sleep or initialization mode may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

## 10.3.2.15 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

7 6 5 4 з 2 1 0 R TXERR7 **TXERR6** TXERR5 TXERR4 **TXERR3** TXERR2 TXERR1 TXERR0 W Reset: 0 0 0 0 0 0 0 0 = Unimplemented

Module Base + 0x000F

### Figure 10-18. MSCAN Transmit Error Counter (CANTXERR)

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1)

Write: Unimplemented

### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

| (          | 0x0018 (CAN<br>0x0019 (CAN<br>0x001A (CAN<br>0x001B (CAN | IIDAR5)<br>IIDAR6) |     |     |     |     |     |     |

|------------|----------------------------------------------------------|--------------------|-----|-----|-----|-----|-----|-----|

|            | 7                                                        | 6                  | 5   | 4   | 3   | 2   | 1   | 0   |

| R<br>W     | AC7                                                      | AC6                | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset      | 0                                                        | 0                  | 0   | 0   | 0   | 0   | 0   | 0   |

| F          | 7                                                        | 6                  | 5   | 4   | 3   | 2   | 1   | 0   |

| R<br>W     | AC7                                                      | AC6                | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset      | 0                                                        | 0                  | 0   | 0   | 0   | 0   | 0   | 0   |

|            | 7                                                        | 6                  | 5   | 4   | 3   | 2   | 1   | 0   |

| R<br>W     | AC7                                                      | AC6                | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset      | 0                                                        | 0                  | 0   | 0   | 0   | 0   | 0   | 0   |

| _ <b>Г</b> | 7                                                        | 6                  | 5   | 4   | 3   | 2   | 1   | 0   |

| R<br>W     | AC7                                                      | AC6                | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset      | 0                                                        | 0                  | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 10-20. MSCAN Identifier Acceptance Registers (Second Bank) — CANIDAR4–CANIDAR7

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 10-20. CANIDAR4–CANIDAR7 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>AC[7:0] | Acceptance Code Bits — AC[7:0] comprise a user-defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register. |

Chapter 15 Timer Module (TIM16B8CV1) Block Description

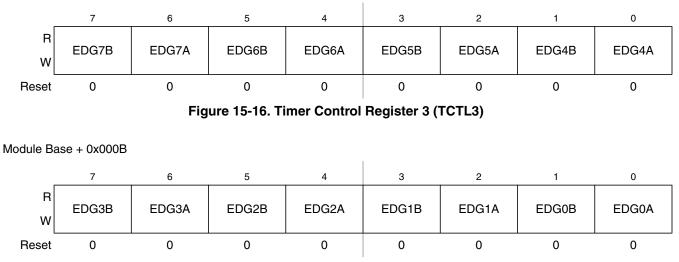

### 15.3.2.9 Timer Control Register 3/Timer Control Register 4 (TCTL3 and TCTL4)

Figure 15-17. Timer Control Register 4 (TCTL4)

### Read: Anytime

Module Base + 0x000A

Write: Anytime.

#### Table 15-12. TCTL3/TCTL4 Field Descriptions

| Field                 | Description                                                                                                               |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>EDGnB<br>EDGnA | <b>Input Capture Edge Control</b> — These eight pairs of control bits configure the input capture edge detector circuits. |

| Table 15-13 | . Edge | Detector | Circuit | Configuration |

|-------------|--------|----------|---------|---------------|

|-------------|--------|----------|---------|---------------|

| EDGnB | EDGnA | Configuration                           |

|-------|-------|-----------------------------------------|

| 0     | 0     | Capture disabled                        |

| 0     | 1     | Capture on rising edges only            |

| 1     | 0     | Capture on falling edges only           |

| 1     | 1     | Capture on any edge (rising or falling) |

## 15.4.2 Input Capture

Clearing the I/O (input/output) select bit, IOSx, configures channel x as an input capture channel. The input capture function captures the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the timer transfers the value in the timer counter into the timer channel registers, TCx.

The minimum pulse width for the input capture input is greater than two bus clocks.

An input capture on channel x sets the CxF flag. The CxI bit enables the CxF flag to generate interrupt requests. Timer module must stay enabled (TEN bit of TSCR1 must be set to one) while clearing CxF (writing one to CxF).

### 15.4.3 Output Compare

Setting the I/O select bit, IOSx, configures channel x as an output compare channel. The output compare function can generate a periodic pulse with a programmable polarity, duration, and frequency. When the timer counter reaches the value in the channel registers of an output compare channel, the timer can set, clear, or toggle the channel pin. An output compare on channel x sets the CxF flag. The CxI bit enables the CxF flag to generate interrupt requests. Timer module must stay enabled (TEN bit of TSCR1 register must be set to one) while clearing CxF (writing one to CxF).

The output mode and level bits, OMx and OLx, select set, clear, toggle on output compare. Clearing both OMx and OLx disconnects the pin from the output logic.

Setting a force output compare bit, FOCx, causes an output compare on channel x. A forced output compare does not set the channel flag.

A successful output compare on channel 7 overrides output compares on all other output compare channels. The output compare 7 mask register masks the bits in the output compare 7 data register. The timer counter reset enable bit, TCRE, enables channel 7 output compares to reset the timer counter. A channel 7 output compare can reset the timer counter even if the IOC7 pin is being used as the pulse accumulator input.

Writing to the timer port bit of an output compare pin does not affect the pin state. The value written is stored in an internal latch. When the pin becomes available for general-purpose output, the last value written to the bit appears at the pin.

When TCRE is set and TC7 is not equal to 0, then TCNT will cycle from 0 to TC7. When TCNT reaches TC7 value, it will last only one bus cycle then reset to 0.

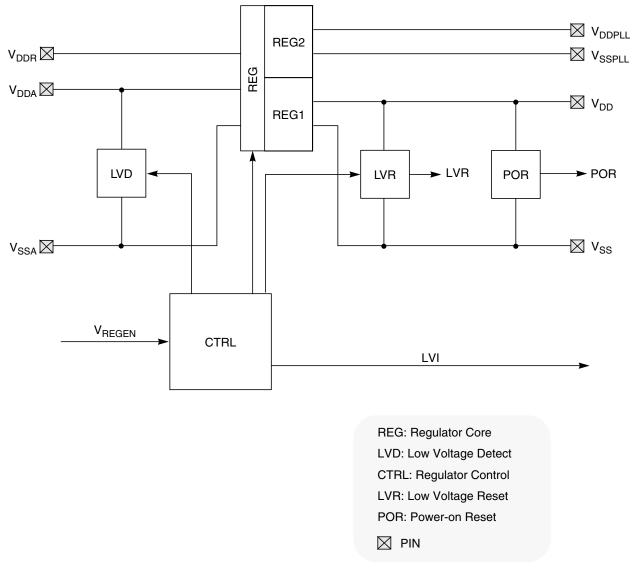

Chapter 16 Dual Output Voltage Regulator (VREG3V3V2) Block Description

# 16.1.3 Block Diagram

Figure 16-1 shows the function principle of VREG3V3V2 by means of a block diagram. The regulator core REG consists of two parallel sub-blocks, REG1 and REG2, providing two independent output voltages.

Figure 16-1. VREG3V3 Block Diagram

To change the Flash protection that will be loaded on reset, the upper sector of the Flash array must be unprotected, then the Flash protection byte located at Flash address 0xFF0D must be written to.

A protected Flash sector is disabled by FPHDIS while the size of the protected sector is defined by FPHS[1:0] in the FPROT register.

Trying to alter any of the protected areas will result in a protect violation error and the PVIOL flag will be set in the FSTAT register (see Section 17.3.2.6). A mass erase of the whole Flash array is only possible when protection is fully disabled by setting the FPOPEN and FPHDIS bits. An attempt to mass erase a Flash array while protection is enabled will set the PVIOL flag in the FSTAT register.

#### Table 17-8. FPROT Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FPOPEN      | <ul> <li>Protection Function for Program or Erase — The FPOPEN bit is used to either select an address range to be protected using the FPHDIS and FPHS[1:0] bits or to select the same address range to be unprotected as shown in Table 17-9.</li> <li>The FPHDIS bit allows a Flash address range to be unprotected</li> <li>The FPHDIS bit allows a Flash address range to be protected</li> </ul> |

| 6<br>NV6         | Nonvolatile Flag Bit — The NV6 bit should remain in the erased state for future enhancements.                                                                                                                                                                                                                                                                                                         |

| 5<br>FPHDIS      | Flash Protection Higher Address Range Disable — The FPHDIS bit determines whether there is a protected/unprotected area in the higher space of the Flash address map.         0       Protection/unprotection enabled         1       Protection/unprotection disabled                                                                                                                                |

| 4–3<br>FPHS[1:0] | Flash Protection Higher Address Size — The FPHS[1:0] bits determine the size of the protected/unprotected sector as shown in Table 17-10. The FPHS[1:0] bits can only be written to while the FPHDIS bit is set.                                                                                                                                                                                      |

| 2–0<br>NV[2:0]   | Nonvolatile Flag Bits — The NV[2:0] bits should remain in the erased state for future enhancements.                                                                                                                                                                                                                                                                                                   |

#### Table 17-9. Flash Protection Function

| FPOPEN      | FPHDIS      | FPHS1      | FPHS0 | Function <sup>(1)</sup>    |

|-------------|-------------|------------|-------|----------------------------|

| 1           | 1           | х          | х     | No protection              |

| 1           | 0           | х          | х     | Protect high range         |

| 0           | 1           | х          | х     | Full Flash array protected |

| 0           | 0           | х          | х     | Unprotected high range     |

| 1 For range | sizes refer | o Table 17 | -10   |                            |

1. For range sizes refer to Table 17-10.

#### Table 17-10. Flash Protection Higher Address Range

| FPHS[1:0] | Address Range | Range Size |

|-----------|---------------|------------|

| 00        | 0xF800–0xFFFF | 2 Kbytes   |

| 01        | 0xF000-0xFFFF | 4 Kbytes   |

| 10        | 0xE000-0xFFFF | 8 Kbytes   |

| 11        | 0xC000-0xFFFF | 16 Kbytes  |

Chapter 17 16 Kbyte Flash Module (S12FTS16KV1)

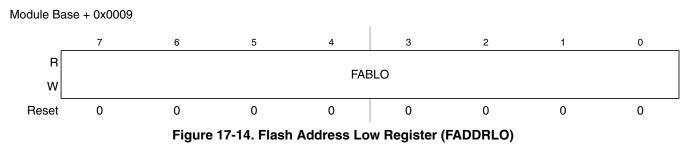

In normal modes, all FABHI and FABLO bits read 0 and are not writable. In special modes, the FABHI and FABLO bits are readable and writable. For sector erase, the MCU address bits [8:0] are ignored. For mass erase, any address within the Flash array is valid to start the command.

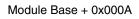

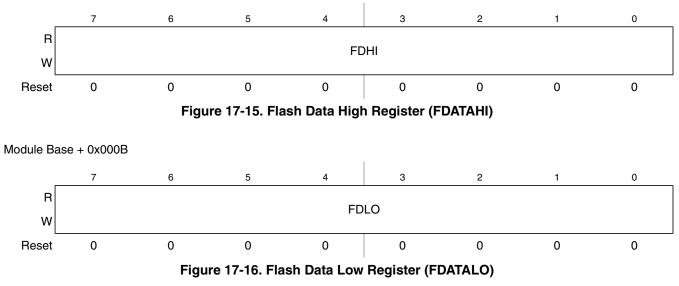

## 17.3.2.10 Flash Data Register (FDATA)

FDATAHI and FDATALO are the Flash data registers.

In normal modes, all FDATAHI and FDATALO bits read 0 and are not writable. In special modes, all FDATAHI and FDATALO bits are readable and writable when writing to an address within the Flash address range.

## 17.3.2.11 RESERVED3

This register is reserved for factory testing and is not accessible to the user.

### 18.4.1.3.2 Program Command

The program operation will program a previously erased word in the Flash array using an embedded algorithm.

An example flow to execute the program operation is shown in Figure 18-23. The program command write sequence is as follows:

- 1. Write to a Flash array address to start the command write sequence for the program command. The data written will be programmed to the Flash array address written.

- 2. Write the program command, 0x20, to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the program command.

If a word to be programmed is in a protected area of the Flash array, the PVIOL flag in the FSTAT register will set and the program command will not launch. Once the program command has successfully launched, the CCIF flag in the FSTAT register will set after the program operation has completed unless a new command write sequence has been buffered. By executing a new program command write sequence on sequential words after the CBEIF flag in the FSTAT register has been set, up to 55% faster programming time per word can be effectively achieved than by waiting for the CCIF flag to set after each program operation.

#### Chapter 19 64 Kbyte Flash Module (S12FTS64KV4)

| MCU Address<br>Range         | PPAGE             | Protectable<br>Low Range | Protectable<br>High Range | Array Relative<br>Address <sup>(1)</sup> |

|------------------------------|-------------------|--------------------------|---------------------------|------------------------------------------|

| 0x0000-0x3FFF <sup>(2)</sup> | Unpaged<br>(0x3D) | N.A.                     | N.A.                      | 0x14000-0x17FFF                          |

| 0x4000-0x7FFF                | Unpaged           | 0x4000-0x43FF            | N.A.                      | 0x18000-0x1BFFF                          |

|                              | (0x3E)            | 0x4000–0x47FF            |                           |                                          |

|                              |                   | 0x4000-0x4FFF            |                           |                                          |

|                              |                   | 0x4000-0x5FFF            |                           |                                          |

| 0x8000-0xBFFF                | 0x3C              | N.A.                     | N.A.                      | 0x10000-0x13FFF                          |

|                              | 0x3D              | N.A.                     | N.A.                      | 0x14000-0x17FFF                          |

|                              | 0x3E              | 0x8000-0x83FF            | N.A.                      | 0x18000-0x1BFFF                          |

|                              |                   | 0x8000-0x87FF            |                           |                                          |

|                              |                   | 0x8000-0x8FFF            |                           |                                          |

|                              |                   | 0x8000-0x9FFF            |                           |                                          |

|                              | 0x3F              | N.A.                     | 0xB800–0xBFFF             | 0x1C000-0x1FFFF                          |

|                              |                   |                          | 0xB000–0xBFFF             |                                          |

|                              |                   |                          | 0xA000–0xBFFF             |                                          |

|                              |                   |                          | 0x8000-0xBFFF             |                                          |

| 0xC000-0xFFFF                | Unpaged           | N.A.                     | 0xF800–0xFFFF             | 0x1C000-0x1FFFF                          |

|                              | (0x3F)            |                          | 0xF000–0xFFFF             |                                          |

|                              |                   |                          | 0xE000–0xFFFF             |                                          |

|                              |                   |                          | 0xC000–0xFFFF             |                                          |

Table 19-3. Flash Array Memory Map Summary

1. Inside Flash block.

2. If allowed by MCU.

Figure 21-17. RESERVED3

All bits read 0 and are not writable.

### 21.3.2.12 RESERVED4

This register is reserved for factory testing and is not accessible to the user.

Module Base + 0x000D

Figure 21-18. RESERVED4

All bits read 0 and are not writable.

### 21.3.2.13 RESERVED5

This register is reserved for factory testing and is not accessible to the user.

Module Base + 0x000E

All bits read 0 and are not writable.

### 21.3.2.14 RESERVED6

This register is reserved for factory testing and is not accessible to the user.

| Num | С | Rating                                                                            | Symbol          | Min | Тур | Max | Unit |

|-----|---|-----------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| 1   | Т | Thermal Resistance LQFP48, single layer PCB <sup>(2)</sup>                        | θ <sub>JA</sub> | —   |     | 69  | °C/W |

| 2   | т | Thermal Resistance LQFP48, double sided PCB with 2 internal planes <sup>(3)</sup> | θ <sub>JA</sub> |     | _   | 53  | °C/W |

| 3   | Т | Junction to Board LQFP48                                                          | θ <sub>JB</sub> | —   |     | 30  | °C/W |

| 4   | Т | Junction to Case LQFP48                                                           | θ <sub>JC</sub> | —   | _   | 20  | °C/W |

| 5   | Т | Junction to Package Top LQFP48                                                    | Ψ <sub>JT</sub> | —   | _   | 4   | °C/W |

| 6   | Т | Thermal Resistance LQFP52, single sided PCB                                       | θ <sub>JA</sub> | —   |     | 65  | °C/W |

| 7   | т | Thermal Resistance LQFP52, double sided PCB with 2 internal planes                | θ <sub>JA</sub> |     | _   | 49  | °C/W |

| 8   | Т | Junction to Board LQFP52                                                          | θ <sub>JB</sub> | —   |     | 31  | °C/W |

| 9   | Т | Junction to Case LQFP52                                                           | θ <sub>JC</sub> | —   | _   | 17  | °C/W |

| 10  | Т | Junction to Package Top LQFP52                                                    | Ψ <sub>JT</sub> | —   | _   | 3   | °C/W |

| 11  | Т | Thermal Resistance QFP 80, single sided PCB                                       | θ <sub>JA</sub> | —   |     | 52  | °C/W |

| 12  | т | Thermal Resistance QFP 80, double sided PCB with 2 internal planes                | θ <sub>JA</sub> |     | _   | 42  | °C/W |

| 13  | Т | Junction to Board QFP80                                                           | θ <sub>JB</sub> | —   | _   | 28  | °C/W |

| 14  | Т | Junction to Case QFP80                                                            | θ <sub>JC</sub> | —   | _   | 18  | °C/W |

| 15  | Т | Junction to Package Top QFP80                                                     | Ψ <sub>JT</sub> | _   | _   | 4   | °C/W |

| Table A-5. | Thermal | Package | Characteristics <sup>(1)</sup> |

|------------|---------|---------|--------------------------------|

|------------|---------|---------|--------------------------------|

1. The values for thermal resistance are achieved by package simulations

2. PC Board according to EIA/JEDEC Standard 51-2

3. PC Board according to EIA/JEDEC Standard 51-7

**Appendix A Electrical Characteristics**

## A.1.10.2 Additional Remarks

In expanded modes the currents flowing in the system are highly dependent on the load at the address, data and control signals as well as on the duty cycle of those signals. No generally applicable numbers can be given. A very good estimate is to take the single chip currents and add the currents due to the external loads.

| Conditions are shown in Table A-4 with internal regulator enabled unless otherwise noted |                                      |                                                                                                                                                                                 |                                  |     |                                                    |                                             |      |

|------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----|----------------------------------------------------|---------------------------------------------|------|

| Num                                                                                      | С                                    | Rating                                                                                                                                                                          | Symbol                           | Min | Тур                                                | Max                                         | Unit |

| 1                                                                                        | Р                                    | Run Supply Current Single Chip                                                                                                                                                  | I <sub>DD5</sub>                 | _   | —                                                  | 35                                          | mA   |

| 2                                                                                        | P<br>P<br>C                          | Wait Supply current<br>All modules enabled<br>V <sub>DDR</sub> <4.9V, only RTI enabled <sup>2</sup><br>V <sub>DDR</sub> >4.9V, only RTI enabled                                 | I <sub>DDW</sub>                 |     | 3.5<br>2.5                                         | 30<br>8                                     | mA   |

| 3                                                                                        | C<br>P<br>C<br>P<br>C<br>P<br>C<br>P | Pseudo Stop Current (RTI and COP disabled) <sup>2 3</sup><br>-40°C<br>27°C<br>85°C<br>"C" Temp Option 100°C<br>105°C<br>"V" Temp Option 120°C<br>125°C<br>"M" Temp Option 140°C | I <sub>DDPS</sub> <sup>(1)</sup> |     | 340<br>360<br>550<br>550<br>720<br>780<br>1100     | <br>450<br><br>1450<br><br>1900<br><br>4500 | μΑ   |

| 4                                                                                        | ССССС                                | Pseudo Stop Current (RTI and COP enabled) <sup>(2) (3)</sup><br>-40°C<br>27°C<br>85°C<br>105°C<br>125°C                                                                         | I <sub>DDPS</sub> <sup>1</sup>   |     | 540<br>700<br>750<br>880<br>1300                   |                                             | μΑ   |

| 5                                                                                        | C<br>P<br>C<br>P<br>C<br>P<br>C<br>P | Stop Current <sup>3</sup><br>-40°C<br>27°C<br>85°C<br>"C" Temp Option 100°C<br>105°C<br>"V" Temp Option 120°C<br>125°C<br>"M" Temp Option 140°C                                 | I <sub>DDS</sub> <sup>1</sup>    |     | 10<br>20<br>100<br>140<br>170<br>300<br>350<br>520 | <br>80<br><br>1000<br><br>1400<br><br>4000  | μΑ   |

Table A-8. Supply Current Characteristics for MC9S12CG16 MC9S12C32

1. STOP current measured in production test at increased junction temperature, hence for Temp Option "C" the test is carried out at 100°C although the Temperature specification is 85°C. Similarly for "v" and "M" options the temperature used in test lies 15°C above the temperature option specification.

2. PLL off

3. At those low power dissipation levels  $T_{\rm J}$  =  $T_{\rm A}$  can be assumed

# A.7 Voltage Regulator

# A.7.1 Voltage Regulator Operating Conditions

#### Table A-23. Voltage Regulator Electrical Parameters

| Num | С | Characteristic                                                                                                                                                                 | Symbol                                                                           | Min                          | Тур                          | Мах                          | Unit             |

|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------|

| 1   | Р | Input Voltages                                                                                                                                                                 | V <sub>VDDR, A</sub>                                                             | 2.97                         | —                            | 5.5                          | V                |

| 3   | Р | Output Voltage Core<br>Full Performance Mode                                                                                                                                   | V <sub>DD</sub>                                                                  | 2.35                         | 2.5                          | 2.75                         | V                |

| 4   | Р | Low Voltage Interrupt <sup>(1)</sup><br>Assert Level (xL45J mask set)<br>Assert Level (other mask sets)<br>Deassert Level (xL45J mask set)<br>Deassert Level (other mask sets) | V <sub>LVIA</sub><br>V <sub>LVIA</sub><br>V <sub>LVID</sub><br>V <sub>LVID</sub> | 4.30<br>4.00<br>4.42<br>4.15 | 4.53<br>4.37<br>4.65<br>4.52 | 4.77<br>4.66<br>4.89<br>4.77 | V<br>V<br>V<br>V |

| 5   | Р | Low Voltage Reset <sup>(2),(3)</sup><br>Assert Level (xL45J mask set)<br>Assert Level (other mask sets)                                                                        | V <sub>LVRA</sub>                                                                | 2.25<br>2.25                 | 2.3<br>2.35                  |                              | V                |

| 7   | С | Power-on Reset <sup>(4)</sup><br>Assert Level<br>Deassert Level                                                                                                                | V <sub>PORA</sub><br>V <sub>PORD</sub>                                           | 0.97                         |                              | 2.05                         | V<br>V           |

1. Monitors V<sub>DDA</sub>, active only in Full Performance Mode. Indicates I/O & ADC performance degradation due to low supply voltage.

2. Monitors V<sub>DD</sub>, active only in Full Performance Mode. MCU is monitored by the POR in RPM (see Figure A-10)

3. Digital functionality is guaranteed in the range between  $V_{DD}(min)$  and  $V_{LVRA}(min)$ .

4. Monitors V<sub>DD</sub>. Active in all modes.

# A.7.2 Chip Power-up and LVI/LVR Graphical Explanation

Voltage regulator sub modules LVI (low voltage interrupt), POR (power-on reset) and LVR (low voltage reset) handle chip power-up or drops of the supply voltage. Their function is described in Figure A-10.