Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | EBI/EMI, SCI, SPI                                                      |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 35                                                                     |

| Program Memory Size        | 96KB (96K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 52-LQFP                                                                |

| Supplier Device Package    | 52-TQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12gc96vpbe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.2.2 Detailed Register Map

The detailed register map of the MC9S12C128 is listed in address order below.

# 0x0000-0x000F MEBI Map 1 of 3 (HCS12 Multiplexed External Bus Interface)

| Address       | Name      |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1   | Bit 0 |

|---------------|-----------|-----------------|--------|-------|-------|---------|-------|-------|---------|-------|

| 0x0000        | PORTA     | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | 1       | Bit 0 |

| 0x0001        | PORTB     | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | 1       | Bit 0 |

| 0x0002        | DDRA      | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | 1       | Bit 0 |

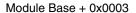

| 0x0003        | DDRB      | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | 1       | Bit 0 |

| 0x0004        | Reserved  | Read:           | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

|               |           | Write:          | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

| 0x0005        | Reserved  | Read:<br>Write: | 0      | U     | U     | 0       | U     | 0     | 0       | U     |

| 0.0000        | Б         | Read:           | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

| 0x0006        | Reserved  | Write:          |        |       |       |         |       |       |         |       |

| 0x0007        | Reserved  | Read:           | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

| 0,0007        | ricscrvca | Write:          |        |       |       |         |       |       |         |       |

| 0x0008        | PORTE     | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | 2     | Bit 1   | Bit 0 |

| 0x0009        | DDRE      | Read:<br>Write: | Bit 7  | 6     | 5     | 4       | 3     | Bit 2 | 0       | 0     |

| 0x000A        | PEAR      | Read:<br>Write: | NOACCE | 0     | PIPOE | NECLK   | LSTRE | RDWE  | 0       | 0     |

| 0x000B        | MODE      | Read:<br>Write: | MODC   | MODB  | MODA  | 0       | IVIS  | 0     | EMK     | EME   |

| 0x000C        | PUCR      | Read:           | PUPKE  | 0     | 0     | PUPEE   | 0     | 0     | PUPBE   | PUPAE |

| 0,0000        | 1 0011    | Write:          | TOTAL  |       |       | 1 01 LL |       |       | 1 OI DE | TOTAL |

| 0x000D        | RDRIV     | Read:<br>Write: | RDPK   | 0     | 0     | RDPE    | 0     | 0     | RDPB    | RDPA  |

| 0x000E EBICTL | EBICTL    | Read:           | 0      | 0     | 0     | 0       | 0     | 0     | 0       | ESTR  |

| 3,0000        | 22.0.2    | Write:          |        |       |       |         |       |       |         |       |

| 0x000F        | Reserved  | Read:<br>Write: | 0      | 0     | 0     | 0       | 0     | 0     | 0       | 0     |

# 1.3.4.6 PA[7:0] / ADDR[15:8] / DATA[15:8] — Port A I/O Pins

PA7–PA0 are general purpose input or output pins,. In MCU expanded modes of operation, these pins are used for the multiplexed external address and data bus. PA[7:1] pins are not available in the 48-pin package version. PA[7:3] are not available in the 52-pin package version.

# 1.3.4.7 PB[7:0] / ADDR[7:0] / DATA[7:0] — Port B I/O Pins

PB7–PB0 are general purpose input or output pins. In MCU expanded modes of operation, these pins are used for the multiplexed external address and data bus. PB[7:5] and PB[3:0] pins are not available in the 48-pin nor 52-pin package version.

## 1.3.4.8 PE7 / NOACC / XCLKS — Port E I/O Pin 7

PE7 is a general purpose input or output pin. During MCU expanded modes of operation, the NOACC signal, when enabled, is used to indicate that the current bus cycle is an unused or "free" cycle. This signal will assert when the CPU is not using the bus. The  $\overline{\text{XCLKS}}$  is an input signal which controls whether a crystal in combination with the internal Colpitts (low power) oscillator is used or whether Pierce oscillator/external clock circuitry is used. The state of this pin is latched at the rising edge of  $\overline{\text{RESET}}$ . If the input is a logic low the EXTAL pin is configured for an external clock drive or a Pierce oscillator. If input is a logic high a Colpitts oscillator circuit is configured on EXTAL and XTAL. Since this pin is an input with a pull-up device during reset, if the pin is left floating, the default configuration is a Colpitts oscillator circuit on EXTAL and XTAL.

Due to the nature of a translated ground Colpitts oscillator a DC voltage bias is applied to the crystal. Please contact the crystal manufacturer for crystal DC.

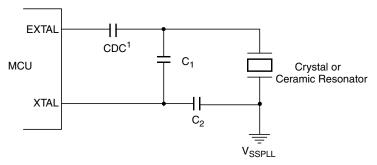

Figure 1-11. Colpitts Oscillator Connections (PE7 = 1)

RS can be zero (shorted) when used with higher frequency crystals, refer to manufacturer's data.

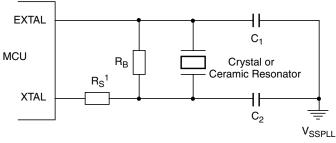

Figure 1-12. Pierce Oscillator Connections (PE7 = 0)

#### Chapter 1 MC9S12C and MC9S12GC Device Overview (MC9S12C128)

the Flash EEPROM memory in the memory map (ROMCTL). At the rising edge of  $\overline{RESET}$ , the state of this pin is latched to the ROMON bit.

- PP6 = 1 in emulation modes equates to ROMON = 0 (ROM space externally mapped)

- PP6 = 0 in expanded modes equates to ROMON = 0 (ROM space externally mapped)

# 1.3.4.19 PP[5:0] / KWP[5:0] / PW[5:0] — Port P I/O Pins [5:0]

PP[5:0] are general purpose input or output pins, shared with the keypad interrupt function. When configured as inputs, they can generate interrupts causing the MCU to exit stop or wait mode.

PP[5:0] are also shared with the PWM output signals, PW[5:0]. Pins PP[2:0] are only available in the 80-pin package version. Pins PP[4:3] are not available in the 48-pin package version.

# 1.3.4.20 PJ[7:6] / KWJ[7:6] — Port J I/O Pins [7:6]

PJ[7:6] are general purpose input or output pins, shared with the keypad interrupt function. When configured as inputs, they can generate interrupts causing the MCU to exit stop or wait mode. These pins are not available in the 48-pin package version nor in the 52-pin package version.

### 1.3.4.21 PM5 / SCK — Port M I/O Pin 5

PM5 is a general purpose input or output pin and also the serial clock pin SCK for the serial peripheral interface (SPI).

## 1.3.4.22 PM4 / MOSI — Port M I/O Pin 4

PM4 is a general purpose input or output pin and also the master output (during master mode) or slave input (during slave mode) pin for the serial peripheral interface (SPI).

## 1.3.4.23 PM3 / SS — Port M I/O Pin 3

PM3 is a general purpose input or output pin and also the slave select pin  $\overline{SS}$  for the serial peripheral interface (SPI).

### 1.3.4.24 PM2 / MISO — Port M I/O Pin 2

PM2 is a general purpose input or output pin and also the master input (during master mode) or slave output (during slave mode) pin for the serial peripheral interface (SPI).

### 1.3.4.25 PM1 / TXCAN — Port M I/O Pin 1

PM1 is a general purpose input or output pin and the transmit pin, TXCAN, of the CAN module if available.

### 1.3.4.26 PM0 / RXCAN — Port M I/O Pin 0

PM0 is a general purpose input or output pin and the receive pin, RXCAN, of the CAN module if available.

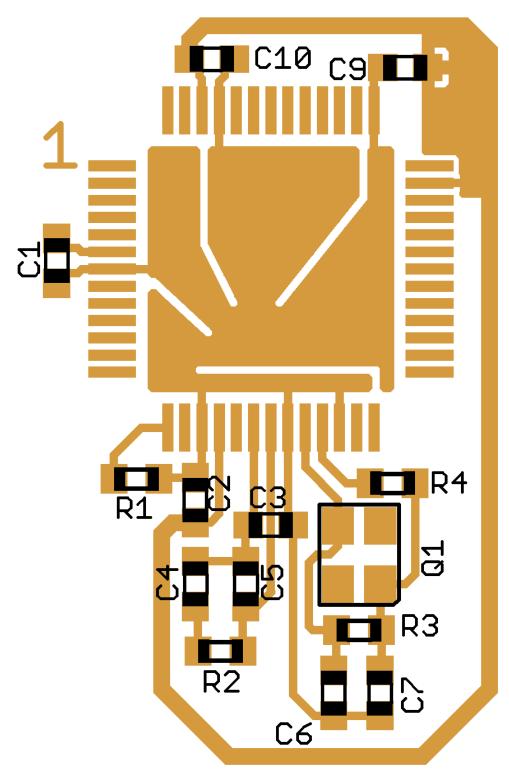

Figure 1-19. Recommended PCB Layout for 52 LQFP Pierce Oscillator

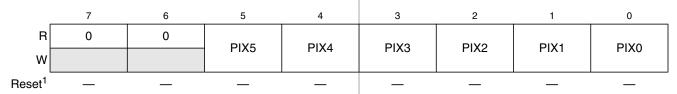

# 3.3.2.9 Program Page Index Register (PPAGE)

Module Base + 0x0030

Starting address location affected by INITRG register setting.

1. The reset state of this register is controlled at chip integration. Please refer to the device overview section to determine the actual reset state of this register.

= Unimplemented or Reserved

Figure 3-11. Program Page Index Register (PPAGE)

Read: Anytime

Write: Determined at chip integration. Generally it's: "write anytime in all modes;" on some devices it will be: "write only in special modes." Check specific device documentation to determine which applies.

Reset: Defined at chip integration as either 0x00 (paired with write in any mode) or 0x3C (paired with write only in special modes), see device overview chapter.

The HCS12 core architecture limits the physical address space available to 64K bytes. The program page index register allows for integrating up to 1M byte of FLASH or ROM into the system by using the six page index bits to page 16K byte blocks into the program page window located from 0x8000 to 0xBFFF as defined in Table 3-14. CALL and RTC instructions have special access to read and write this register without using the address bus.

### NOTE

Normal writes to this register take one cycle to go into effect. Writes to this register using the special access of the CALL and RTC instructions will be complete before the end of the associated instruction.

Table 3-13. MEMSIZ0 Field Descriptions

| Field | Description                                                                                                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Program Page Index Bits 5:0</b> — These page index bits are used to select which of the 64 FLASH or ROM array pages is to be accessed in the program page window as shown in Table 3-14. |

#### Chapter 3 Module Mapping Control (MMCV4) Block Description

unimplemented locations within the register space or to locations that are removed from the map (i.e., ports A and B in expanded modes) will not cause this signal to become active. When the EMK bit is clear, this pin is used for general purpose I/O.

# 3.4.3 Memory Expansion

The HCS12 core architecture limits the physical address space available to 64K bytes. The program page index register allows for integrating up to 1M byte of FLASH or ROM into the system by using the six page index bits to page 16K byte blocks into the program page window located from 0x8000 to 0xBFFF in the physical memory space. The paged memory space can consist of solely on-chip memory or a combination of on-chip and off-chip memory. This partitioning is configured at system integration through the use of the paging configuration switches ( $pag\_sw1:pag\_sw0$ ) at the core boundary. The options available to the integrator are as given in Table 3-16 (this table matches Table 3-12 but is repeated here for easy reference).

| pag_sw1:pag_sw0 | Off-Chip Space | On-Chip Space |

|-----------------|----------------|---------------|

| 00              | 876K bytes     | 128K bytes    |

| 01              | 768K bytes     | 256K bytes    |

| 10              | 512K bytes     | 512K bytes    |

| 11              | 0K byte        | 1M byte       |

Table 3-16. Allocated Off-Chip Memory Options

Based upon the system configuration, the program page window will consider its access to be either internal or external as defined in Table 3-17.

| pag_sw1:pag_sw0 | Partitioning                          | PIX5:0 Value  | Page Window<br>Access |

|-----------------|---------------------------------------|---------------|-----------------------|

| 00              | 876K off-Chip,                        | 0x0000-0x0037 | External              |

|                 | 128K on-Chip                          | 0x0038-0x003F | Internal              |

| 01              | 768K off-chip,                        | 0x0000-0x002F | External              |

|                 | 256K on-chip                          | 0x0030-0x003F | Internal              |

| 10              | · · · · · · · · · · · · · · · · · · · |               | External              |

|                 | 512K on-chip                          | 0x0020-0x003F | Internal              |

| 11              | 0K off-chip,                          | N/A           | External              |

|                 | 1M on-chip                            | 0x0000-0x003F | Internal              |

Table 3-17. External/Internal Page Window Access

## **NOTE**

The partitioning as defined in Table 3-17 applies only to the allocated memory space and the actual on-chip memory sizes implemented in the system may differ. Please refer to the device overview chapter for actual sizes.

Chapter 4 Multiplexed External Bus Interface (MEBIV3)

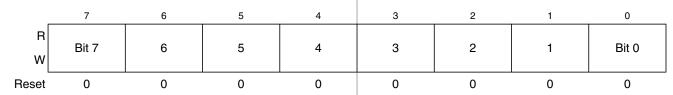

# 4.3.2.3 Data Direction Register A (DDRA)

Module Base + 0x0002

Starting address location affected by INITRG register setting.

Figure 4-4. Data Direction Register A (DDRA)

Read: Anytime when register is in the map

Write: Anytime when register is in the map

This register controls the data direction for port A. When port A is operating as a general-purpose I/O port, DDRA determines the primary direction for each port A pin. A 1 causes the associated port pin to be an output and a 0 causes the associated pin to be a high-impedance input. The value in a DDR bit also affects the source of data for reads of the corresponding PORTA register. If the DDR bit is 0 (input) the buffered pin input state is read. If the DDR bit is 1 (output) the associated port data register bit state is read.

This register is not in the on-chip memory map in expanded and special peripheral modes. Therefore, these accesses will be echoed externally. It is reset to 0x00 so the DDR does not override the three-state control signals.

**Table 4-3. DDRA Field Descriptions**

| Field       | Description                                                                                                                  |

|-------------|------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>DDRA | Data Direction Port A  0 Configure the corresponding I/O pin as an input  1 Configure the corresponding I/O pin as an output |

### Chapter 7 Debug Module (DBGV1) Block Description

## **Table 7-15. DBGC3 Field Descriptions (continued)**

| Field      | Description                                                                                                                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>RWBEN | Read/Write Comparator B Enable Bit — The RWBEN bit controls whether read or write comparison is enabled for comparator B. See Section 7.4.2.1.1, "Read or Write Comparison," for more information. This bit is not useful for tagged operations.  O Read/Write is not used in comparison  Read/Write is used in comparison |

| 0<br>RWB   | Read/Write Comparator B Value Bit — The RWB bit controls whether read or write is used in compare for comparator B. The RWB bit is not used if RWBEN = 0.  0 Write cycle will be matched  1 Read cycle will be matched  Note: RWB and RWBEN are not used in full mode.                                                     |

Table 7-16. Breakpoint Mask Bits for First Address

| BKAMBH:BKAMBL | Address Compare        | DBGCAX             | DBGCAH | DBGCAL |

|---------------|------------------------|--------------------|--------|--------|

| x:0           | Full address compare   | Yes <sup>(1)</sup> | Yes    | Yes    |

| 0:1           | 256 byte address range | Yes <sup>1</sup>   | Yes    | No     |

| 1:1           | 16K byte address range | Yes <sup>1</sup>   | No     | No     |

<sup>1.</sup> If PPAGE is selected.

Table 7-17. Breakpoint Mask Bits for Second Address (Dual Mode)

| ВКВМВН:ВКВМВL | Address Compare        | DBGCBX             | DBGCBH | DBGCBL |

|---------------|------------------------|--------------------|--------|--------|

| x:0           | Full address compare   | Yes <sup>(1)</sup> | Yes    | Yes    |

| 0:1           | 256 byte address range | Yes <sup>1</sup>   | Yes    | No     |

| 1:1           | 16K byte address range | Yes <sup>1</sup>   | No     | No     |

<sup>1.</sup> If PPAGE is selected.

Table 7-18. Breakpoint Mask Bits for Data Breakpoints (Full Mode)

| ВКВМВН:ВКВМВL | Data Compare              | DBGCBX            | DBGCBH | DBGCBL |

|---------------|---------------------------|-------------------|--------|--------|

| 0:0           | High and low byte compare | No <sup>(1)</sup> | Yes    | Yes    |

| 0:1           | High byte                 | No <sup>1</sup>   | Yes    | No     |

| 1:0           | Low byte                  | No <sup>1</sup>   | No     | Yes    |

| 1:1           | No compare                | No <sup>1</sup>   | No     | No     |

<sup>1.</sup> Expansion addresses for breakpoint B are not applicable in this mode.

#### Chapter 9 Clocks and Reset Generator (CRGV4) Block Description

of 4 OSCCLK plus 4 PLLCLK cycles to make the transition. During the transition, all clocks freeze and CPU activity ceases.

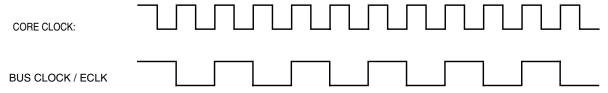

Figure 9-18. Core Clock and Bus Clock Relationship

# 9.4.3 Clock Monitor (CM)

If no OSCCLK edges are detected within a certain time, the clock monitor within the oscillator block generates a clock monitor fail event. The CRGV4 then asserts self-clock mode or generates a system reset depending on the state of SCME bit. If the clock monitor is disabled or the presence of clocks is detected no failure is indicated by the oscillator block. The clock monitor function is enabled/disabled by the CME control bit.

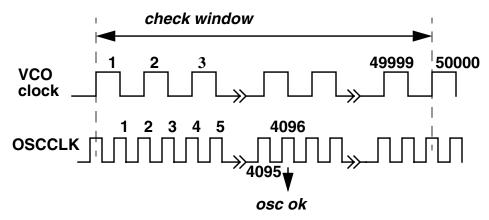

# 9.4.4 Clock Quality Checker

The clock monitor performs a coarse check on the incoming clock signal. The clock quality checker provides a more accurate check in addition to the clock monitor.

A clock quality check is triggered by any of the following events:

- Power-on reset (POR)

- Low voltage reset (LVR)

- Wake-up from full stop mode (exit full stop)

- Clock monitor fail indication (CM fail)

A time window of 50000 VCO clock cycles<sup>1</sup> is called *check window*.

A number greater equal than 4096 rising OSCCLK edges within a *check window* is called *osc ok*. Note that *osc ok* immediately terminates the current *check window*. See Figure 9-19 as an example.

Figure 9-19. Check Window Example

1. VCO clock cycles are generated by the PLL when running at minimum frequency  $f_{\text{SCM}}$ .

Module Base + 0x001C (CANIDMR4) 0x001D (CANIDMR5) 0x001E (CANIDMR6) 0x001F (CANIDMR7) 5 3 2 0 R AM7 AM6 AM5 AM4 АМЗ AM2 AM1 AM0 W 0 0 0 0 0 0 0 Reset 0 7 6 5 4 3 2 1 0 R AM6 AM4 АМ3 AM2 AM1 AM7 AM5 AM0 0 0 0 0 0 0 0 0 Reset 7 5 3 2 0 R AM7 AM6 AM5 AM4 АМ3 AM2 AM1 AM0 W Reset 0 0 0 0 0 0 0 0 5 4 3 0 R AM7 AM6 AM5 AM4 AM3 AM2 AM1 AM0 W 0 0 0 0 0 0 0 0 Reset

Figure 10-22. MSCAN Identifier Mask Registers (Second Bank) — CANIDMR4-CANIDMR7

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

Table 10-22. CANIDMR4-CANIDMR7 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>AM[7:0] | Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.  O Match corresponding acceptance code register and identifier bits  I Ignore corresponding acceptance code register bit |

### **Table 12-4. PWMCLK Field Descriptions**

| Field      | Description                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>PCLK5 | Pulse Width Channel 5 Clock Select  0 Clock A is the clock source for PWM channel 5.  1 Clock SA is the clock source for PWM channel 5. |

| 4<br>PCLK4 | Pulse Width Channel 4 Clock Select  0 Clock A is the clock source for PWM channel 4.  1 Clock SA is the clock source for PWM channel 4. |

| 3<br>PCLK3 | Pulse Width Channel 3 Clock Select  0 Clock B is the clock source for PWM channel 3.  1 Clock SB is the clock source for PWM channel 3. |

| 2<br>PCLK2 | Pulse Width Channel 2 Clock Select  0 Clock B is the clock source for PWM channel 2.  1 Clock SB is the clock source for PWM channel 2. |

| 1<br>PCLK1 | Pulse Width Channel 1 Clock Select  0 Clock A is the clock source for PWM channel 1.  1 Clock SA is the clock source for PWM channel 1. |

| 0<br>PCLK0 | Pulse Width Channel 0 Clock Select 0 Clock A is the clock source for PWM channel 0. 1 Clock SA is the clock source for PWM channel 0.   |

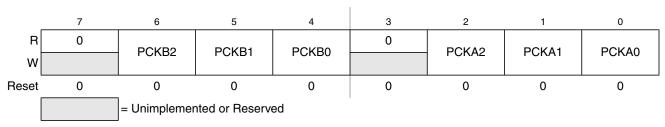

# 12.3.2.4 PWM Prescale Clock Select Register (PWMPRCLK)

This register selects the prescale clock source for clocks A and B independently.

Figure 12-6. PWM Prescaler Clock Select Register (PWMPRCLK)

Read: anytime Write: anytime

356

### NOTE

PCKB2–PCKB0 and PCKA2–PCKA0 register bits can be written anytime. If the clock prescale is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

#### Chapter 13 Serial Communications Interface (S12SCIV2) Block Description

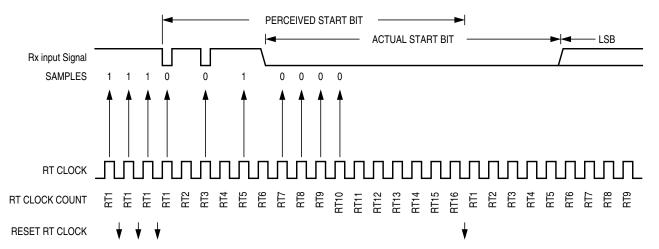

In Figure 13-16, a large burst of noise is perceived as the beginning of a start bit, although the test sample at RT5 is high. The RT5 sample sets the noise flag. Although this is a worst-case misalignment of perceived bit time, the data samples RT8, RT9, and RT10 are within the bit time and data recovery is successful.

Figure 13-16. Start Bit Search Example 3

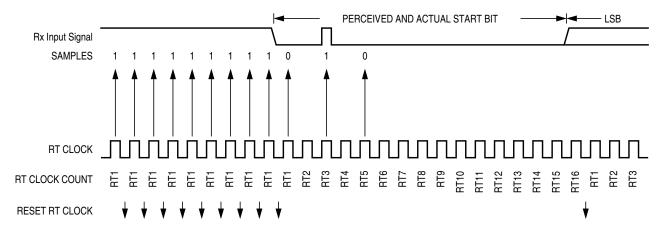

Figure 13-17 shows the effect of noise early in the start bit time. Although this noise does not affect proper synchronization with the start bit time, it does set the noise flag.

Figure 13-17. Start Bit Search Example 4

#### Chapter 14 Serial Peripheral Interface (SPIV3) Block Description

In master mode, with slave select output enabled the  $\overline{SS}$  line is always deasserted and reasserted between successive transfers for at least minimum idle time.

### 14.4.3.3 CPHA = 1 Transfer Format

Some peripherals require the first SCK edge before the first data bit becomes available at the data out pin, the second edge clocks data into the system. In this format, the first SCK edge is issued by setting the CPHA bit at the beginning of the 8-cycle transfer operation.

The first edge of SCK occurs immediately after the half SCK clock cycle synchronization delay. This first edge commands the slave to transfer its first data bit to the serial data input pin of the master.

A half SCK cycle later, the second edge appears on the SCK pin. This is the latching edge for both the master and slave.

When the third edge occurs, the value previously latched from the serial data input pin is shifted into the LSB or MSB of the SPI shift register, depending on LSBFE bit. After this edge, the next bit of the master data is coupled out of the serial data output pin of the master to the serial input pin on the slave.

This process continues for a total of 16 edges on the SCK line with data being latched on even numbered edges and shifting taking place on odd numbered edges.

Data reception is double buffered, data is serially shifted into the SPI shift register during the transfer and is transferred to the parallel SPI Data Register after the last bit is shifted in.

After the 16th SCK edge:

- Data that was previously in the SPI Data Register of the master is now in the data register of the slave, and data that was in the data register of the slave is in the master.

- The SPIF flag bit in SPISR is set indicating that the transfer is complete.

Figure 14-10 shows two clocking variations for CPHA = 1. The diagram may be interpreted as a master or slave timing diagram because the SCK, MISO, and MOSI pins are connected directly between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The  $\overline{SS}$  pin of the master must be either high or reconfigured as a general-purpose output not affecting the SPI.

The  $\overline{SS}$  line can remain active low between successive transfers (can be tied low at all times). This format is sometimes preferred in systems having a single fixed master and a single slave that drive the MISO data line.

Back-to-back transfers in master mode

In master mode, if a transmission has completed and a new data byte is available in the SPI Data Register, this byte is send out immediately without a trailing and minimum idle time.

The SPI interrupt request flag (SPIF) is common to both the master and slave modes. SPIF gets set one half SCK cycle after the last SCK edge.

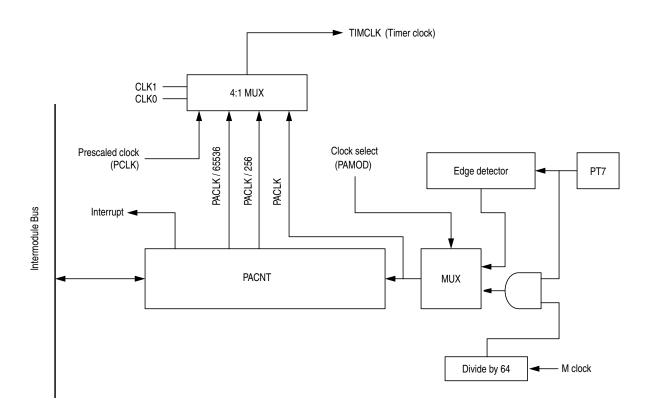

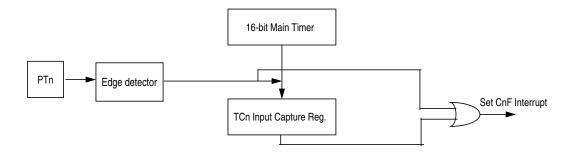

Figure 15-2. 16-Bit Pulse Accumulator Block Diagram

Figure 15-3. Interrupt Flag Setting

The 16-bit main timer is an up counter.

A full access for the counter register should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

Read: Anytime

Write: Has no meaning or effect in the normal mode; only writable in special modes (test\_mode = 1).

The period of the first count after a write to the TCNT registers may be a different size because the write is not synchronized with the prescaler clock.

# 15.3.2.6 Timer System Control Register 1 (TSCR1)

Module Base + 0x0006

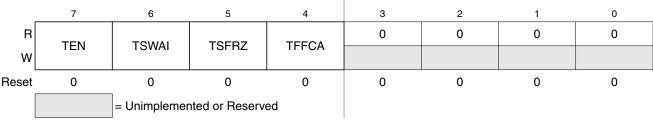

Figure 15-12. Timer System Control Register 1 (TSCR1)

Read: Anytime Write: Anytime

**Table 15-7. TSCR1 Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TEN   | Timer Enable  0 Disables the main timer, including the counter. Can be used for reducing power consumption.  1 Allows the timer to function normally.  If for any reason the timer is not active, there is no ÷64 clock for the pulse accumulator because the ÷64 is generated by the timer prescaler. |

| 6<br>TSWAI | Timer Module Stops While in Wait  O Allows the timer module to continue running during wait.  Disables the timer module when the MCU is in the wait mode. Timer interrupts cannot be used to get the MCU out of wait.  TSWAI also affects pulse accumulator.                                           |

# 17.3 Memory Map and Registers

This section describes the FTS16K memory map and registers.

# 17.3.1 Module Memory Map

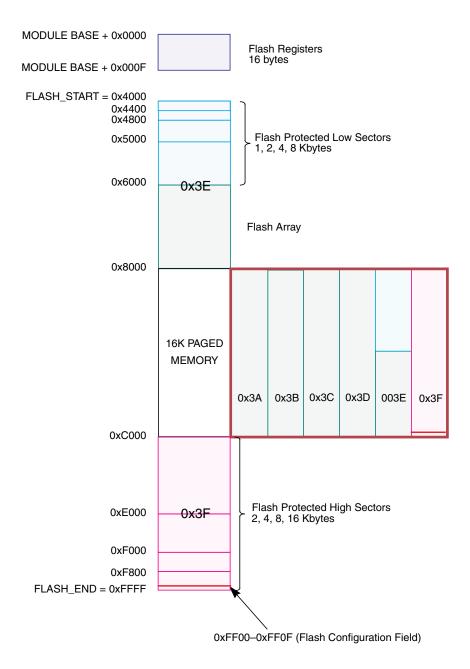

The FTS16K memory map is shown in Figure 17-2. The HCS12 architecture places the Flash array addresses between 0xC000 and 0xFFFF. The content of the HCS12 Core PPAGE register is used to map the logical page ranging from address 0x8000 to 0xBFFF to a physical 16K byte page in the Flash array memory. The FPROT register (see Section 17.3.2.5) can be set to globally protect the entire Flash array or one growing downward from the Flash array end address. The higher address area is mainly targeted to hold the boot loader code since it covers the vector space. Default protection settings as well as security information that allows the MCU to restrict access to the Flash module are stored in the Flash configuration field described in Table 17-1.

Table 17-1. Flash Configuration Field

| Flash Address | Size<br>(bytes) | Description                                                                             |

|---------------|-----------------|-----------------------------------------------------------------------------------------|

| 0xFF00-0xFF07 | 8               | Backdoor Key to unlock security                                                         |

| 0xFF08-0xFF0C | 5               | Reserved                                                                                |

| 0xFF0D        | 1               | Flash Protection byte Refer to Section 17.3.2.5, "Flash Protection Register (FPROT)"    |

| 0xFF0E        | 1               | Reserved                                                                                |

| 0xFF0F        | 1               | Flash Security/Options byte Refer to Section 17.3.2.2, "Flash Security Register (FSEC)" |

<sup>1.</sup> By placing 0x3F in the HCS12 Core PPAGE register, the 16 Kbyte page can be seen twice in the MCU memory map.

### Chapter 17 16 Kbyte Flash Module (S12FTS16KV1)

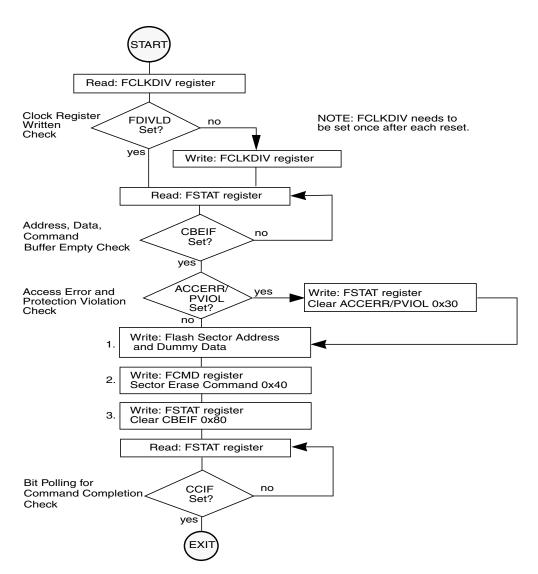

Figure 17-24. Example Sector Erase Command Flow

## 18.4.1.3.2 Program Command

The program operation will program a previously erased word in the Flash array using an embedded algorithm.

An example flow to execute the program operation is shown in Figure 18-23. The program command write sequence is as follows:

- 1. Write to a Flash array address to start the command write sequence for the program command. The data written will be programmed to the Flash array address written.

- 2. Write the program command, 0x20, to the FCMD register.

- 3. Clear the CBEIF flag in the FSTAT register by writing a 1 to CBEIF to launch the program command.

If a word to be programmed is in a protected area of the Flash array, the PVIOL flag in the FSTAT register will set and the program command will not launch. Once the program command has successfully launched, the CCIF flag in the FSTAT register will set after the program operation has completed unless a new command write sequence has been buffered. By executing a new program command write sequence on sequential words after the CBEIF flag in the FSTAT register has been set, up to 55% faster programming time per word can be effectively achieved than by waiting for the CCIF flag to set after each program operation.

# 19.4.4 Flash Reset Sequence

On each reset, the Flash module executes a reset sequence to hold CPU activity while loading the following registers from the Flash array memory according to Table 19-1:

- FPROT Flash Protection Register (see Section 19.3.2.5)

- FSEC Flash Security Register (see Section 19.3.2.2)

## 19.4.4.1 Reset While Flash Command Active

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/array being erased is not guaranteed.

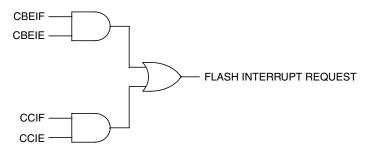

# 19.4.5 Interrupts

The Flash module can generate an interrupt when all Flash commands have completed execution or the Flash address, data, and command buffers are empty.

| Interrupt Source                                      | Interrupt Flag            | Local Enable | Global (CCR) Mask |

|-------------------------------------------------------|---------------------------|--------------|-------------------|

| Flash Address, Data, and Command<br>Buffers are empty | CBEIF<br>(FSTAT register) | CBEIE        | I Bit             |

| All Flash commands have completed execution           | CCIF<br>(FSTAT register)  | CCIE         | l Bit             |

**Table 19-18. Flash Interrupt Sources**

### NOTE

Vector addresses and their relative interrupt priority are determined at the MCU level.

# 19.4.5.1 Description of Interrupt Operation

Figure 19-29 shows the logic used for generating interrupts.

The Flash module uses the CBEIF and CCIF flags in combination with the enable bits CBIE and CCIE to discriminate for the generation of interrupts.

Figure 19-29. Flash Interrupt Implementation

For a detailed description of these register bits, refer to Section 19.3.2.4, "Flash Configuration Register (FCNFG)" and Section 19.3.2.6, "Flash Status Register (FSTAT)".

### Chapter 20 96 Kbyte Flash Module (S12FTS96KV1)

Note: 0x3A-0x3F correspond to the PPAGE register content

Figure 20-4. Flash Memory Map