Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 48                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f521ar9t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# WATCHDOG TIMER (Cont'd)

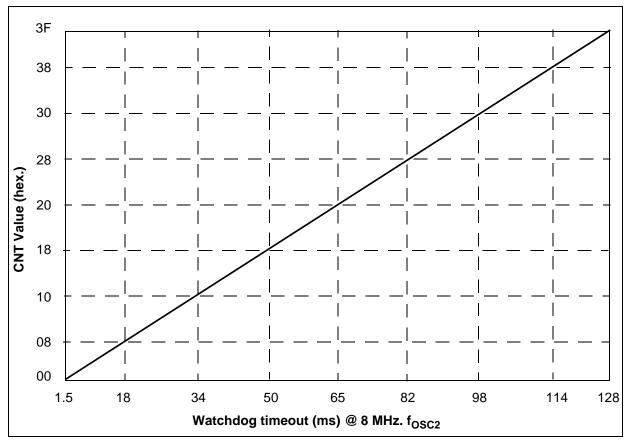

## **10.1.4 How to Program the Watchdog Timeout**

Figure 33 shows the linear relationship between the 6-bit value to be loaded in the Watchdog Counter (CNT) and the resulting timeout duration in milliseconds. This can be used for a quick calculation without taking the timing variations into account. If

Figure 33. Approximate Timeout Duration

more precision is needed, use the formulae in Figure 34.

**Caution:** When writing to the WDGCR register, always write 1 in the T6 bit to avoid generating an immediate reset.

**\$7**

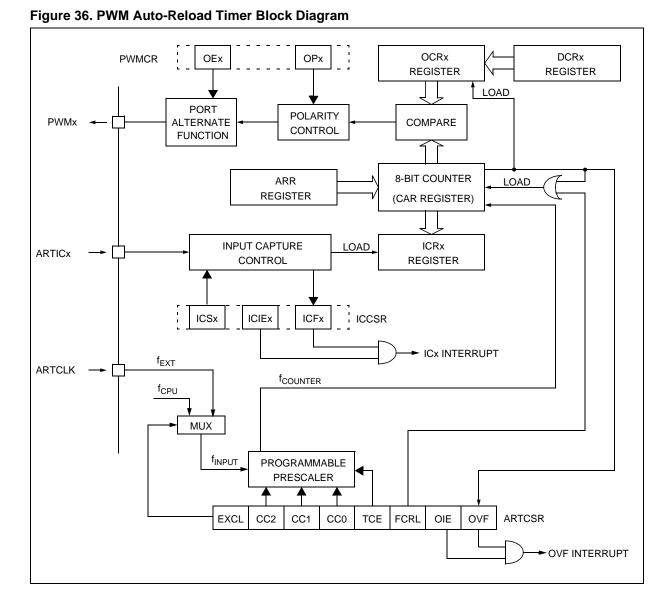

# 10.3 PWM AUTO-RELOAD TIMER (ART)

# 10.3.1 Introduction

47/

The Pulse Width Modulated Auto-Reload Timer on-chip peripheral consists of an 8-bit auto reload counter with compare/capture capabilities and of a 7-bit prescaler clock source.

These resources allow five possible operating modes:

- Generation of up to 4 independent PWM signals

- Output compare and Time base interrupt

- Up to two input capture functions

- External event detector

- Up to two external interrupt sources

The three first modes can be used together with a single counter frequency.

The timer can be used to wake up the MCU from WAIT and HALT modes.

# Table 33. ST7 Application Notes

| IDENTIFICATION      | DESCRIPTION                                                                          |  |  |

|---------------------|--------------------------------------------------------------------------------------|--|--|

| AN1106              | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                                           |  |  |

| AN1179              | PROGRAMMING ST7 FLASH MICROCONTROLLERS IN REMOTE ISP MODE (IN-SITU PRO-<br>GRAMMING) |  |  |

| AN1446              | USING THE ST72521 EMULATOR TO DEBUG A ST72324 TARGET APPLICATION                     |  |  |

| AN1477              | EMULATED DATA EEPROM WITH XFLASH MEMORY                                              |  |  |

| AN1478              | PORTING AN ST7 PANTA PROJECT TO CODEWARRIOR IDE                                      |  |  |

| AN1527              | DEVELOPING A USB SMARTCARD READER WITH ST7SCR                                        |  |  |

| AN1575              | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS                         |  |  |

| AN1576              | IN-APPLICATION PROGRAMMING (IAP) DRIVERS FOR ST7 HDFLASH OR XFLASH MCUS              |  |  |

| AN1577              | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION FOR ST7 USB APPLICATIONS                |  |  |

| AN1601              | SOFTWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |  |  |

| AN1603              | USING THE ST7 USB DEVICE FIRMWARE UPGRADE DEVELOPMENT KIT (DFU-DK)                   |  |  |

| AN1635              | ST7 CUSTOMER ROM CODE RELEASE INFORMATION                                            |  |  |

| AN1754              | DATA LOGGING PROGRAM FOR TESTING ST7 APPLICATIONS VIA ICC                            |  |  |

| AN1796              | FIELD UPDATES FOR FLASH BASED ST7 APPLICATIONS USING A PC COMM PORT                  |  |  |

| AN1900              | HARDWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |  |  |

| AN1904              | ST7MC THREE-PHASE AC INDUCTION MOTOR CONTROL SOFTWARE LIBRARY                        |  |  |

| AN1905              | ST7MC THREE-PHASE BLDC MOTOR CONTROL SOFTWARE LIBRARY                                |  |  |

| SYSTEM OPTIMIZATION |                                                                                      |  |  |

| AN1711              | SOFTWARE TECHNIQUES FOR COMPENSATING ST7 ADC ERRORS                                  |  |  |

| AN1827              | IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09                                 |  |  |

| AN2009              | PWM MANAGEMENT FOR 3-PHASE BLDC MOTOR DRIVES USING THE ST7FMC                        |  |  |

| AN2030              | BACK EMF DETECTION DURING PWM ON TIME BY ST7MC                                       |  |  |

# **15 KNOWN LIMITATIONS**

# **15.1 ALL FLASH AND ROM DEVICES**

## 15.1.1 External RC option

The External RC clock source option described in previous datasheet revisions is no longer supported and has been removed from this specification.

### 15.1.2 Safe Connection of OSC1/OSC2 Pins

The OSC1 and/or OSC2 pins must not be left unconnected otherwise the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. Refer to section 6.2 on page 25.

### 15.1.3 Reset pin protection with LVD Enabled

As mentioned in note 2 below Figure 103 on page 186, when the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

### 15.1.4 Unexpected Reset Fetch

If an interrupt request occurs while a "POP CC" instruction is executed, the interrupt controller does not recognise the source of the interrupt and, by default, passes the RESET vector address to the CPU.

### Workaround

57

To solve this issue, a "POP CC" instruction must always be preceded by a "SIM" instruction.

# 15.1.5 Clearing active interrupts outside interrupt routine

When an active interrupt request occurs at the same time as the related flag is being cleared, an unwanted reset may occur.

**Note:** clearing the related interrupt mask will not generate an unwanted reset

### Concurrent interrupt context

The symptom does not occur when the interrupts are handled normally, i.e.

when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

Perform SIM and RIM operation before and after resetting an active interrupt request.

Example:

SIM

reset interrupt flag

RIM

#### Nested interrupt context:

The symptom does not occur when the interrupts are handled normally, i.e.

when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine with higher or identical priority level

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

PUSH CC SIM reset interrupt flag POP CC

# KNOWN LIMITATIONS (Cont'd)

#### 15.1.6 SCI Wrong Break duration

#### Description

A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 20 bits instead of 10 bits if M=0

- 22 bits instead of 11 bits if M=1.

In the same way, as long as the SBK bit is set, break characters are sent to the TDO pin. This may lead to generate one break more than expected.

#### Occurrence

The occurrence of the problem is random and proportional to the baudrate. With a transmit frequency of 19200 baud ( $f_{CPU}=8MHz$  and SCI-BRR=0xC9), the wrong break duration occurrence is around 1%.

#### Workaround

If this wrong duration is not compliant with the communication protocol in the application, software can request that an Idle line be generated before the break character. In this case, the break duration is always correct assuming the application is not doing anything between the idle and the break. This can be ensured by temporarily disabling interrupts.

The exact sequence is:

- Disable interrupts

- Reset and Set TE (IDLE request)

- Set and Reset SBK (Break Request)

- Re-enable interrupts

#### 15.1.7 16-bit Timer PWM Mode

In PWM mode, the first PWM pulse is missed after writing the value FFFCh in the OC1R register (OC1HR, OC1LR). It leads to either full or no PWM during a period, depending on the OLVL1 and OLVL2 settings.

| 15.1.8 | CAN | Cell | Limitations |

|--------|-----|------|-------------|

|--------|-----|------|-------------|

| Limitation                                                      | Flash          | ROM            |

|-----------------------------------------------------------------|----------------|----------------|

| Omitted SOF bit                                                 | х              | х              |

| CPU write access<br>(more than one cycle)<br>corrupts CAN frame | х              | x              |

| Unexpected Mes-<br>sage transmission                            | x <sup>2</sup> |                |

| Bus Off State Not En-<br>tered                                  |                | x <sup>4</sup> |

| WKPS Functionality                                              |                | x <sup>3</sup> |

x=limitation present

<sup>1</sup>For details see section 10.8.5 on page 146

<sup>2</sup>Software workaround possible using modified WKPS bit.

<sup>3</sup>Functionality modified for Unexpected Message Transmission workaround in Flash.

<sup>4</sup>Limitation present on ROM Rev W and Rev Z. Not present in Flash and ROM Rev Y.

#### 15.1.9 I2C Multimaster

In multimaster configurations, if the ST7 I2C receives a START condition from another I2C master after the START bit is set in the I2CCR register and before the START condition is generated by the ST7 I2C, it may ignore the START condition from the other I2C master. In this case, the ST7 master will receive a NACK from the other device. On reception of the NACK, ST7 can send a re-start and Slave address to re-initiate communication