Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 64                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | · ·                                                                  |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 80-LQFP                                                              |

| Supplier Device Package    |                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f521m9t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

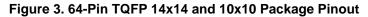

# PIN DESCRIPTION (Cont'd)

57

# INTERRUPTS (Cont'd)

57

| Instruction | New Description                 | Function/Example      | 11 | Н | 10 | Ν | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|---|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |   |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | 11 | Н | 10 | Ν | Z | С |

| JRM         | Jump if I1:0=11 (level 3)       | 11:0=11 ?             |    |   |    |   |   |   |

| JRNM        | Jump if I1:0<>11                | 11:0<>11 ?            |    |   |    |   |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | 11 | Н | 10 | Ν | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |   |   |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  |   |   |   |

| TRAP        | Software trap                   | Software NMI          | 1  |   | 1  |   |   |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  |   |   |   |

# Table 6. Dedicated Interrupt Instruction Set

**Note**: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

# INTERRUPTS (Cont'd)

# Table 7. Interrupt Mapping

| N° | Source<br>Block | Description                               | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT/<br>ACTIVE<br>HALT <sup>3)</sup> | Address<br>Vector |

|----|-----------------|-------------------------------------------|-------------------|-------------------|-------------------------------------------------------|-------------------|

|    | RESET           | Reset                                     | N/A               |                   | yes                                                   | FFFEh-FFFFh       |

|    | TRAP            | Software interrupt                        |                   |                   | no                                                    | FFFCh-FFFDh       |

| 0  | TLI             | External top level interrupt              | EICR              |                   | yes                                                   | FFFAh-FFFBh       |

| 1  | MCC/RTC         | Main clock controller time base interrupt | MCCSR             | Higher            | yes                                                   | FFF8h-FFF9h       |

| 2  | ei0             | External interrupt port A30               |                   | Priority          | yes                                                   | FFF6h-FFF7h       |

| 3  | ei1             | External interrupt port F20               | N/A               |                   | yes                                                   | FFF4h-FFF5h       |

| 4  | ei2             | External interrupt port B30               | IN/A              |                   | yes                                                   | FFF2h-FFF3h       |

| 5  | ei3             | External interrupt port B74               |                   |                   | yes                                                   | FFF0h-FFF1h       |

| 6  | CAN             | CAN peripheral interrupts                 | CANISR            |                   | yes                                                   | FFEEh-FFEFh       |

| 7  | SPI             | SPI peripheral interrupts                 | SPICSR            |                   | yes <sup>1</sup>                                      | FFECh-FFEDh       |

| 8  | TIMER A         | TIMER A peripheral interrupts             | TASR              | •                 | no                                                    | FFEAh-FFEBh       |

| 9  | TIMER B         | TIMER B peripheral interrupts             | TBSR              |                   | no                                                    | FFE8h-FFE9h       |

| 10 | SCI             | SCI Peripheral interrupts                 | SCISR             | Lower             | no                                                    | FFE6h-FFE7h       |

| 11 | AVD             | Auxiliary Voltage detector interrupt      | SICSR             | Priority          | no                                                    | FFE4h-FFE5h       |

| 12 | I2C             | I2C Peripheral interrupts                 | (see periph)      |                   | no                                                    | FFE2h-FFE3h       |

| 13 | PWM ART         | PWM ART interrupt                         | ARTCSR            |                   | yes <sup>2</sup>                                      | FFE0h-FFE1h       |

# Notes:

- 1. Exit from HALT possible when SPI is in slave mode.

- 2. Exit from HALT possible when PWM ART is in external clock mode.

- 3. In Flash devices only a RESET or MCC/RTC interrupt can be used to wake-up from Active Halt mode.

# **7.6 EXTERNAL INTERRUPTS**

# 7.6.1 I/O Port Interrupt Sensitivity

The external interrupt sensitivity is controlled by the IPA, IPB and ISxx bits of the EICR register (Figure 22). This control allows to have up to 4 fully independent external interrupt source sensitivities.

Each external interrupt source can be generated on four (or five) different events on the pin:

- Falling edge

- Rising edge

- Falling and rising edge

- Falling edge and low level

- Rising edge and high level (only for ei0 and ei2)

To guarantee correct functionality, the sensitivity bits in the EICR register can be modified only when the I1 and I0 bits of the CC register are both set to 1 (level 3). This means that interrupts must be disabled before changing sensitivity.

The pending interrupts are cleared by writing a different value in the ISx[1:0], IPA or IPB bits of the EICR.

# **10 ON-CHIP PERIPHERALS**

# **10.1 WATCHDOG TIMER (WDG)**

# 10.1.1 Introduction

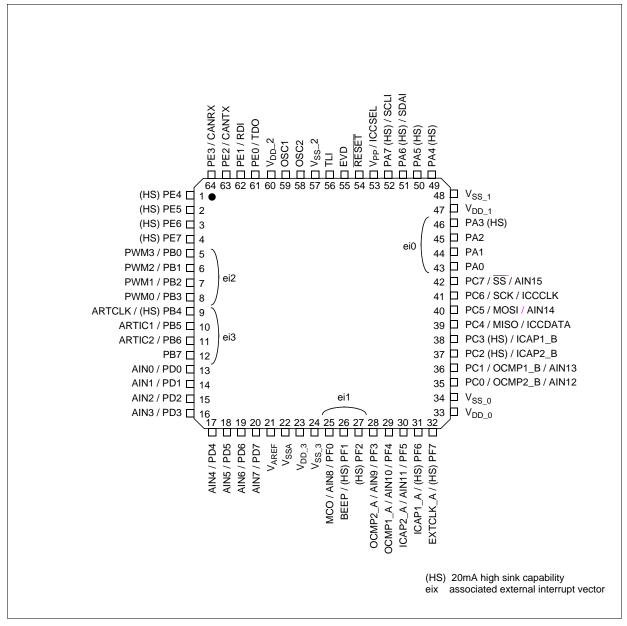

The Watchdog timer is used to detect the occurrence of a software fault, usually generated by external interference or by unforeseen logical conditions, which causes the application program to abandon its normal sequence. The Watchdog circuit generates an MCU reset on expiry of a programmed time period, unless the program refreshes the counter's contents before the T6 bit becomes cleared.

# 10.1.2 Main Features

- Programmable free-running downcounter

- Programmable reset

- Reset (if watchdog activated) when the T6 bit reaches zero

- HALT Optional reset on instruction (configurable by option byte)

- Hardware Watchdog selectable by option byte

# 10.1.3 Functional Description

The counter value stored in the Watchdog Control register (WDGCR bits T[6:0]), is decremented every 16384 f<sub>OSC2</sub> cycles (approx.), and the length of the timeout period can be programmed by the user in 64 increments.

If the watchdog is activated (the WDGA bit is set) and when the 7-bit timer (bits T[6:0]) rolls over from 40h to 3Fh (T6 becomes cleared), it initiates a reset cycle pulling low the reset pin for typically 500ns.

The application program must write in the WDGCR register at regular intervals during normal operation to prevent an MCU reset. This downcounter is free-running: it counts down even if the watchdog is disabled. The value to be stored in the WDGCR register must be between FFh and C0h:

- The WDGA bit is set (watchdog enabled)

- The T6 bit is set to prevent generating an immediate reset

- The T[5:0] bits contain the number of increments which represents the time delay before the watchdog produces a reset (see Figure 33. Approximate Timeout Duration). The timing varies between a minimum and a maximum value due to the unknown status of the prescaler when writing to the WDGCR register (see Figure 34).

Following a reset, the watchdog is disabled. Once activated it cannot be disabled, except by a reset.

The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is cleared).

If the watchdog is activated, the HALT instruction will generate a Reset.

# Figure 32. Watchdog Block Diagram

5/

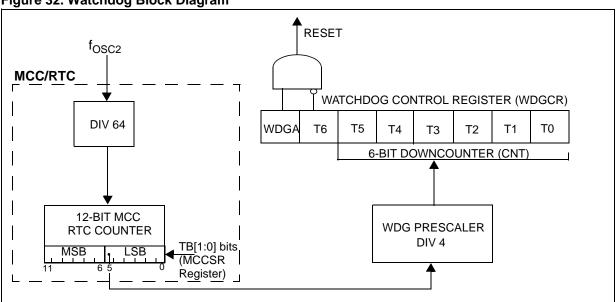

# **10.5 SERIAL PERIPHERAL INTERFACE (SPI)**

# **10.5.1 Introduction**

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves however the SPI interface can not be a master in a multi-master system.

# 10.5.2 Main Features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- Six master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

57

Write collision, Master Mode Fault and Overrun flags **Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

# 10.5.3 General Description

Figure 53 shows the serial peripheral interface (SPI) block diagram. There are 3 registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through 4 pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

### 10.6.4.7 Parity Control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in Table 20.

| M bit   | PCE bit                                 | SCI frame                  |  |  |  |  |  |

|---------|-----------------------------------------|----------------------------|--|--|--|--|--|

| 0       | 0                                       | SB   8 bit data   STB      |  |  |  |  |  |

| 0       | 1                                       | SB   7-bit data   PB   STB |  |  |  |  |  |

| 1       | 0                                       | SB   9-bit data   STB      |  |  |  |  |  |

| 1       | 1                                       | SB   8-bit data PB   STB   |  |  |  |  |  |

| Legend: | Legend: SB = Start Bit, STB = Stop Bit, |                            |  |  |  |  |  |

**Table 20. Frame Formats**

PB = Parity Bit Note: In case of wake up by an address mark

**Note**: In case of wake up by an address mark, the MSB bit of the data is taken into account and not the parity bit

**Even parity:** the parity bit is calculated to obtain an even number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Ex: data=00110101; 4 bits set => parity bit will be 0 if even parity is selected (PS bit = 0).

**Odd parity:** the parity bit is calculated to obtain an odd number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Ex: data=00110101; 4 bits set => parity bit will be 1 if odd parity is selected (PS bit = 1).

**Transmission mode:** If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

**Reception mode:** If the PCE bit is set then the interface checks if the received data byte has an

57

even number of "1s" if even parity is selected (PS=0) or an odd number of "1s" if odd parity is selected (PS=1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PIE is set in the SCICR1 register.

### 10.6.4.8 SCI Clock Tolerance

During reception, each bit is sampled 16 times. The majority of the 8th, 9th and 10th samples is considered as the bit value. For a valid bit detection, all the three samples should have the same value otherwise the noise flag (NF) is set. For example: if the 8th, 9th and 10th samples are 0, 1 and 1 respectively, then the bit value will be "1", but the Noise Flag bit is be set because the three samples values are not the same.

Consequently, the bit length must be long enough so that the 8th, 9th and 10th samples have the desired bit value. This means the clock frequency should not vary more than 6/16 (37.5%) within one bit. The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation must not exceed 3.75%.

**Note:** The internal sampling clock of the microcontroller samples the pin value on every falling edge. Therefore, the internal sampling clock and the time the application expects the sampling to take place may be out of sync. For example: If the baud rate is 15.625 kbaud (bit length is 64µs), then the 8th, 9th and 10th samples will be at 28µs, 32µs & 36µs respectively (the first sample starting ideally at 0µs). But if the falling edge of the internal clock occurs just before the pin value changes, the samples would then be out of sync by ~4us. This means the entire bit length must be at least 40µs (36µs for the 10th sample + 4µs for synchronization with the internal sampling clock).

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

# 10.6.7 Register Description STATUS REGISTER (SCISR)

Read Only Reset Value: 1100 0000 (C0h)

| 7    |    |      |      |    |    |    | 0  |

|------|----|------|------|----|----|----|----|

| TDRE | тс | RDRF | IDLE | OR | NF | FE | PE |

### Bit 7 = **TDRE** *Transmit data register empty.*

This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Data is not transferred to the shift register

1: Data is transferred to the shift register

**Note:** Data will not be transferred to the shift register unless the TDRE bit is cleared.

#### Bit 6 = **TC** Transmission complete.

This bit is set by hardware when transmission of a frame containing Data is complete. An interrupt is generated if TCIE=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

**Note:** TC is not set after the transmission of a Preamble or a Break.

#### Bit 5 = **RDRF** Received data ready flag.

This bit is set by hardware when the content of the RDR register has been transferred to the SCIDR register. An interrupt is generated if RIE=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: Data is not received

1: Received data is ready to be read

#### Bit 4 = **IDLE** *Idle line detect.*

This bit is set by hardware when a Idle Line is detected. An interrupt is generated if the ILIE=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Idle Line is detected

1: Idle Line is detected

**Note:** The IDLE bit will not be set again until the RDRF bit has been set itself (i.e. a new idle line occurs).

## Bit 3 = **OR** Overrun error.

This bit is set by hardware when the word currently being received in the shift register is ready to be transferred into the RDR register while RDRF=1. An interrupt is generated if RIE=1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Overrun error

1: Overrun error is detected

**Note:** When this bit is set RDR register content will not be lost but the shift register will be overwritten.

#### Bit 2 = NF Noise flag.

This bit is set by hardware when noise is detected on a received frame. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No noise is detected

1: Noise is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.

#### Bit 1 = **FE** Framing error.

This bit is set by hardware when a de-synchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Framing error is detected

1: Framing error or break character is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both frame error and overrun error, it will be transferred and only the OR bit will be set.

#### Bit 0 = **PE** Parity error.

This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE=1 in the SCICR1 register. 0: No parity error

1: Parity error

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) DATA REGISTER (SCIDR)

### Read/Write

#### Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 60).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 60).

# **BAUD RATE REGISTER (SCIBRR)**

Read/Write

Reset Value: 0000 0000 (00h)

7

0

SCP1

SCP0

SCT2

SCT1

SCT0

SCR2

SCR1

SCR0

# Bits 7:6= SCP[1:0] First SCI Prescaler

These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

| 1                    | 0    | 0    |

| 3                    | 0    | 1    |

| 4                    | 1    | 0    |

| 13                   | 1    | 1    |

Bits 5:3 = **SCT[2:0]** *SCI Transmitter rate divisor* These 3 bits, in conjunction with the SCP1 & SCP0 bits define the total division applied to the bus clock to yield the transmit rate clock in conventional Baud Rate Generator mode.

| TR dividing factor | SCT2 | SCT1 | SCT0 |

|--------------------|------|------|------|

| 1                  | 0    | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  | 0    | 1    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                | 1    | 1    | 1    |

Bits 2:0 = **SCR[2:0]** *SCI Receiver rate divisor.* These 3 bits, in conjunction with the SCP[1:0] bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| RR Dividing factor | SCR2 | SCR1 | SCR0 |

|--------------------|------|------|------|

| 1                  | 0    | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  | 0    | 1    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                | 1    | 1    | 1    |

# I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C CLOCK CONTROL REGISTER (CCR)

Read / Write Reset Value: 0000 0000 (00h)

| 7     |     |     |     |     |     |     | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|

| FM/SM | CC6 | CC5 | CC4 | CC3 | CC2 | CC1 | CC0 |

# Bit 7 = **FM/SM** Fast/Standard $l^2C$ mode.

This bit is set and cleared by software. It is not cleared when the interface is disabled (PE=0). 0: Standard  $I^2C$  mode

1: Fast I<sup>2</sup>C mode

Bit 6:0 = CC[6:0] 7-bit clock divider.

These bits select the speed of the bus ( $F_{SCL}$ ) depending on the I<sup>2</sup>C mode. They are not cleared when the interface is disabled (PE=0).

Refer to the Electrical Characteristics section for the table of values.

Note: The programmed  $\mathrm{F}_{\mathrm{SCL}}$  assumes no load on SCL and SDA lines.

# I<sup>2</sup>C DATA REGISTER (DR)

### Read / Write

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Bit 7:0 = D[7:0] 8-bit Data Register.

These bits contain the byte to be received or transmitted on the bus.

- Transmitter mode: Byte transmission start automatically when the software writes in the DR register.

- Receiver mode: the first data byte is received automatically in the DR register using the least significant bit of the address.

Then, the following data bytes are received one by one after reading the DR register.

# CONTROLLER AREA NETWORK (Cont'd) IDENTIFIER LOW REGISTERS (IDLRx)

Read/Write

Reset Value: Undefined

| 7   |     |     |     |      |      |      | 0    |

|-----|-----|-----|-----|------|------|------|------|

| ID2 | ID1 | ID0 | RTR | DLC3 | DLC2 | DLC1 | DLC0 |

**ID[2:0]** are the least significant 3 bits of the 11-bit message identifier.

**RTR** is the Remote Transmission Request bit. It is set to indicate a remote frame and reset to indicate a data frame.

**DLC[3:0]** is the Data Length Code. It gives the number of bytes in the data field of the message. The valid range is 0 to 8.

# DATA REGISTERS (DATA0-7x)

Read/Write

Reset Value: Undefined

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| DATA |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

**DATA**[7:0] is a message data byte. Up to eight such bytes may be part of a message. Writing to byte DATA7 initiates a transmit request and should always be done even when DATA7 is not part of the message.

# **BUFFER CONTROL/STATUS REGs. (BCSRx)**

Read/Write

Reset Value: 00h

| 7 |   |   |   |     |     |      | 0    |

|---|---|---|---|-----|-----|------|------|

| 0 | 0 | 0 | 0 | ACC | RDY | BUSY | LOCK |

# Bit 3 = **ACC** Acceptance Code

Read Only

Set by hardware with the id of the highest priority filter which accepted the message stored in the buffer.

ACC = 0: Match for Filter/Mask0. Possible match for Filter/Mask1.

ACC = 1: No match for Filter/Mask0 and match for Filter/Mask1.

Reset by hardware when either RDY or RXIF gets reset.

Bit 2 = **RDY** Message Ready

### - Read/Clear

Set by hardware to signal that a new error-free message is available (LOCK = 0) or that a transmission request is pending (LOCK = 1).

Cleared by software when LOCK = 0 to release the buffer and to clear the corresponding RXIF bit in the Interrupt Status Register.

Cleared by hardware when LOCK = 1 to indicate that the transmission request has been serviced or cancelled.

# Bit 1 = **BUSY** Busy Buffer

- Read Only

Set by hardware when the buffer is being filled (LOCK = 0) or emptied (LOCK = 1) and reset after the 2nd intermission bit.

Reset by hardware when the buffer is not accessed by the CAN core for transmission nor reception purposes.

# Bit 0 = **LOCK** *Lock Buffer*

- Read/Set/Clear

Set by software to lock a buffer. No more message can be received into the buffer thus preserving its content and making it available for transmission. Cleared by software to make the buffer available for reception. Cancels any pending transmission

request. Cleared by hardware once a message has been successfully transmitted provided the early transmit interrupt mode is on. Left untouched otherwise.

Note that in order to prevent any message corruption or loss of context, LOCK cannot be set nor reset while BUSY is set. Trying to do so will result in LOCK not changing state.

# CONTROLLER AREA NETWORK (Cont'd)

57

Table 24. CAN Register Map and Reset Values

| Address<br>(Hex.) | Page         | Register<br>Label | 7     | 6     | 5     | 4    | 3     | 2     | 1     | 0     |

|-------------------|--------------|-------------------|-------|-------|-------|------|-------|-------|-------|-------|

| 5A                | 1 /          | CANISR            | RXIF3 | RXIF2 | RXIF1 | TXIF | SCIF  | ORIF  | TEIF  | EPND  |

| ЪА                | $\backslash$ | Reset Value       | 0     | 0     | 0     | 0    | 0     | 0     | 0     | 0     |

| 5B                |              | CANICR            |       | ESCI  | RXIE  | TXIE | SCIE  | ORIE  | TEIE  | ETX   |

| 56                | $\setminus$  | Reset Value       | 0     | 0     | 0     | 0    | 0     | 0     | 0     | 0     |

| 5C                |              | CANCSR            |       | BOFF  | EPSV  | SRTE | NRTX  | FSYN  | WKPS  | RUN   |

| 50                | V            | Reset Value       | 0     | 0     | 0     | 0    | 0     | 0     | 0     | 0     |

| 5D                |              | CANBRPR           | RJW1  | RJW0  | BRP5  | BRP4 | BRP3  | BRP2  | BRP1  | BRP0  |

| 50                |              | Reset Value       | 0     | 0     | 0     | 0    | 0     | 0     | 0     | 0     |

| 5E                |              | CANBTR            |       | BS22  | BS21  | BS20 | BS13  | BS12  | BS11  | BS10  |

| JL                |              | Reset Value       | 0     | 0     | 1     | 0    | 0     | 0     | 1     | 1     |

| 5F                |              | CANPSR            |       |       |       |      |       | PAGE2 | PAGE1 | PAGE0 |

| 51                | / \          | Reset Value       | 0     | 0     | 0     | 0    | 0     | 0     | 0     | 0     |

|                   | 0            | CANLIDHR          | LID10 | LID9  | LID8  | LID7 | LID6  | LID5  | LID4  | LID3  |

| 60                | 0            | Reset Value       | х     | х     | Х     | х    | х     | х     | х     | х     |

| 00                | 1 to 3       | CANIDHRx          | ID10  | ID9   | ID8   | ID7  | ID6   | ID5   | ID4   | ID3   |

|                   | 1 10 3       | Reset Value       | х     | х     | х     | х    | х     | х     | х     | х     |

| 60, 64            | 4            | CANFHRx           | FIL11 | FIL10 | FIL9  | FIL8 | FIL7  | FIL6  | FIL5  | FIL4  |

| 00, 04            | -            | Reset Value       | х     | х     | Х     | х    | х     | х     | х     | х     |

|                   | 0            | CANLIDLR          | LID2  | LID1  | LID0  | LRTR | LDLC3 | LDLC2 | LDLC1 | LDLC0 |

| 61                | U            | Reset Value       | х     | х     | х     | х    | х     | х     | х     | х     |

| 01                | 1 to 3       | CANIDLRx          | ID2   | ID1   | ID0   | RTR  | DLC3  | DLC2  | DLC1  | DLC0  |

|                   | 1 10 0       | Reset Value       | х     | Х     | Х     | Х    | Х     | х     | х     | х     |

| 61, 65            | 4            | CANFLRx           | FIL3  | FIL2  | FIL1  | FIL0 |       |       |       |       |

| 01, 00            | -            | Reset Value       | х     | х     | Х     | х    | 0     | 0     | 0     | 0     |

| 62 to 69          | 1 to 3       | CANDRx            | MSB   |       |       |      |       |       |       | LSB   |

| 02 10 05          | 1 10 0       | Reset Value       | х     | х     | Х     | Х    | х     | Х     | Х     | х     |

| 62, 66            | 4            | CANMHRx           | MSK11 | MSK10 | MSK9  | MSK8 | MSK7  | MSK6  | MSK5  | MSK4  |

| 02,00             | -            | Reset Value       | х     | х     | х     | х    | х     | х     | х     | х     |

| 63, 67            | 4            | CANMLRx           | MSK3  | MSK2  | MSK1  | MSK0 |       |       |       |       |

| 00, 07            |              | Reset Value       | х     | х     | х     | х    | 0     | 0     | 0     | 0     |

| 6E                | 0            | CANTECR           | MSB   |       |       |      |       |       |       | LSB   |

|                   | Ŭ            | Reset Value       | 0     | 0     | 0     | 0    | 0     | 0     | 0     | 0     |

|                   |              | CANRECR           | MSB   |       |       |      |       |       |       | LSB   |

| 6F                |              | Reset Value       | 0     | 0     | 0     | 0    | 0     | 0     | 0     | 0     |

|                   | 1 to 3       | CANBCSRx          |       |       |       |      | ACC   | RDY   | BUSY  | LOCK  |

|                   | 1.00         | Reset Value       | 0     | 0     | 0     | 0    | 0     | 0     | 0     | 0     |

# CONTROLLER AREA NETWORK (Cont'd)

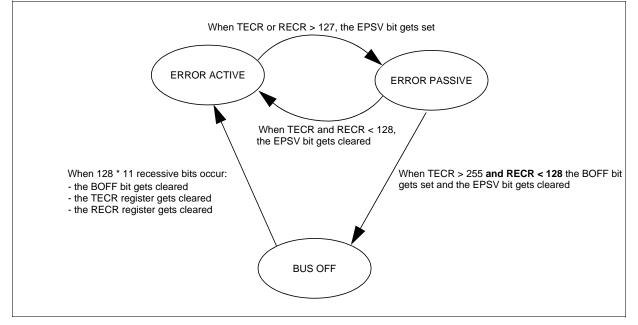

### 10.8.5.5 Bus-off state not entered

### Symptom:

pCAN does not enter bus-off state under certain conditions. This is fixed in FLASH version of ST72F521 starting from silicon Rev R and in ROM version ST72521B starting from silicon Rev Y.

### Details:

According to the CAN standard, pCAN is expected to enter bus-off state when TEC (Transmit Error Counter) is greater than 255.

But if RÉC (Receive Error Counter) is greater than 127 (Error Passive State) pCAN does not enter bus-off and the BOFF bit of the CSR register is not set. To enter bus-off, REC must decrease to a value lower than 128, this is the case with any correct reception even if the message is filtered out.

As bus-off state is not entered and pCAN still attempts to transmit its message, after the overflow the TEC register continues to increment as long as transmission errors occur.

#### Impact on the application:

The application will not stop attempting to transmit CAN messages, even when the bus-off conditions have been reached, until the transmission has been successful or the value of REC becomes lower than 128. However the application will not disturb the communication of the other nodes on the CAN network as pCAN is in Error Passive State.

### Figure 82. CAN Error State Diagram showing "BUSOFF not entered" limitation

# 10-BIT A/D CONVERTER (Cont'd)

# Table 25. ADC Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label     | 7        | 6          | 5         | 4       | 3        | 2        | 1        | 0        |

|-------------------|-----------------------|----------|------------|-----------|---------|----------|----------|----------|----------|

| 0070h             | ADCCSR<br>Reset Value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0       | CH3<br>0 | CH2<br>0 | CH1<br>0 | CH0<br>0 |

| 0071h             | ADCDRH<br>Reset Value | D9<br>0  | D8<br>0    | D7<br>0   | D6<br>0 | D5<br>0  | D4<br>0  | D3<br>0  | D2<br>0  |

| 0072h             | ADCDRL<br>Reset Value | 0        | 0          | 0         | 0       | 0        | 0        | D1<br>0  | D0<br>0  |

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

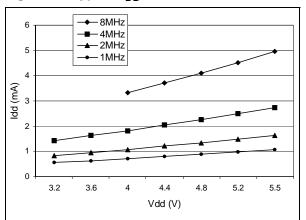

Figure 87. Typical  $I_{DD}$  in RUN mode

# 12.4.1.1 Power Consumption vs f<sub>CPU</sub>: Flash Devices

#### -8MHz • 9 – 4MHz . 8 – 2MHz --1MHz 7 6 (Am) bbl 5 4 3 2 1 0 3.2 3.6 4 4.4 4.8 5.2 5.5 Vdd (V)

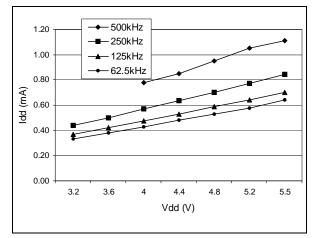

Figure 88. Typical I<sub>DD</sub> in SLOW mode

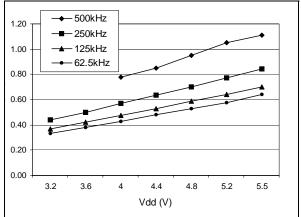

# Figure 89. Typical I<sub>DD</sub> in WAIT mode

Figure 90. Typ.  $I_{DD}$  in SLOW-WAIT mode

57

# CLOCK CHARACTERISTICS (Cont'd)

# 12.5.4 RC Oscillators

| Symbol       | Parameter                                         | Conditions                                | Min | Тур | Max | Unit |

|--------------|---------------------------------------------------|-------------------------------------------|-----|-----|-----|------|

| fosc (RCINT) | Internal RC oscillator frequency<br>See Figure 93 | T <sub>A</sub> =25°C, V <sub>DD</sub> =5V | 2   | 3.5 | 5.6 | MHz  |

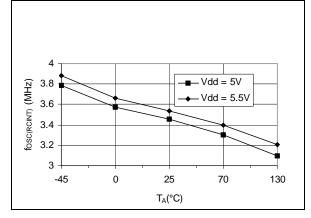

# Figure 93. Typical f<sub>OSC(RCINT)</sub> vs T<sub>A</sub>

Note: To reduce disturbance to the RC oscillator, it is recommended to place decoupling capacitors between  $V_{DD}$  and  $V_{SS}$  as shown in Figure 113

# ADC CHARACTERISTICS (Cont'd)

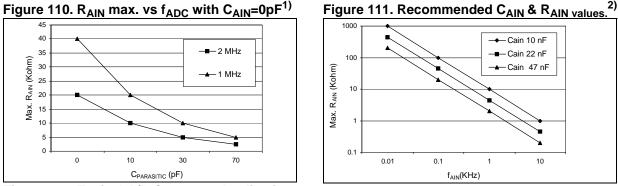

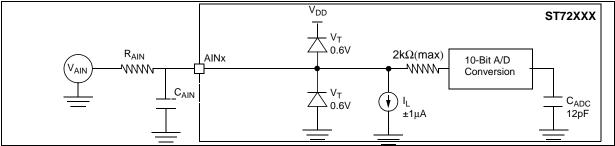

Figure 112. Typical A/D Converter Application

#### Notes:

1.  $C_{PARASITIC}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (3pF). A high  $C_{PARASITIC}$  value will downgrade conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2. This graph shows that depending on the input signal variation ( $f_{AIN}$ ),  $C_{AIN}$  can be increased for stabilization time and decreased to allow the use of a larger serial resistor ( $R_{AIN}$ ).

# 10-BIT ADC CHARACTERISTICS (Cont'd)

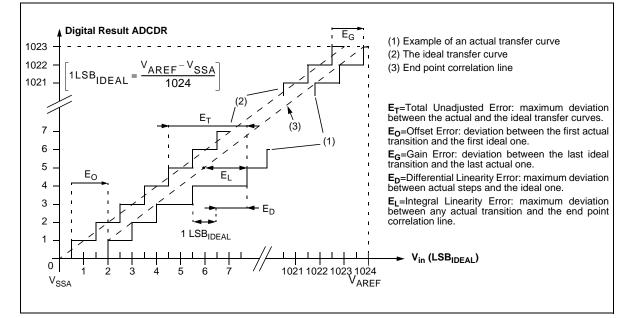

# 12.12.3 ADC Accuracy

Conditions: V<sub>DD</sub>=5V<sup>1)</sup>

| Symbol         | Parameter                            | Conditions                                | Тур | Max <sup>2)</sup> | Unit |

|----------------|--------------------------------------|-------------------------------------------|-----|-------------------|------|

| E <sub>T</sub> | Total unadjusted error <sup>1)</sup> |                                           | 3   | 4                 |      |

| E <sub>O</sub> | Offset error <sup>1)</sup>           |                                           | 2   | 3                 |      |

| E <sub>G</sub> | Gain Error <sup>1)</sup>             |                                           | 0.5 | 3                 | LSB  |

| E <sub>D</sub> | Differential linearity error 1)      | CPU in run mode @ f <sub>ADC</sub> 2 MHz. | 1   | 2                 |      |

| E <sub>L</sub> | Integral linearity error 1)          | CPU in run mode @ f <sub>ADC</sub> 2 MHz. | 1   | 2                 |      |

Notes:

1. ADC Accuracy vs. Negative Injection Current: Injecting negative current may reduce the accuracy of the conversion being performed on another analog input. The effect of negative injection current on robust pins is specified in Section 12.12.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 12.8 does not affect the ADC accuracy.

2. Data based on characterization results, monitored in production to guarantee 99.73% within  $\pm$  max value from -40°C to 125°C ( $\pm$  3 $\sigma$  distribution limits).

### Figure 114. ADC Accuracy Characteristics

# **13.2 THERMAL CHARACTERISTICS**

| Symbol            | Ratings                                                                                          | Value          | Unit |

|-------------------|--------------------------------------------------------------------------------------------------|----------------|------|

| R <sub>thJA</sub> | Package thermal resistance (junction to ambient)<br>TQFP80 14x14<br>TQFP64 14x14<br>TQFP64 10x10 | 55<br>47<br>50 | °C/W |

| P <sub>D</sub>    | Power dissipation <sup>1)</sup>                                                                  | 500            | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>                                                       | 150            | °C   |

#### Notes:

57

1. The power dissipation is obtained from the formula  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD}xV_{DD}$ ) and  $P_{PORT}$  is the port power dissipation determined by the user.

2. The average chip-junction temperature can be obtained from the formula  $T_J = T_A + P_D x RthJA$ .

# ST72521 DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

|                                                                                                                                               | ST72521B MICROCONT<br>(Last update: De                                                              |                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Customer:<br>Address:                                                                                                                         |                                                                                                     |                                                                                                                                                                        |

| Contact:<br>Phone No:<br>Reference/ROM Code*<br>*The ROM code name is                                                                         | s assigned by STMicroelectroni<br>t in .S19 formatHex extension                                     | cs.<br>cannot be processed.                                                                                                                                            |

|                                                                                                                                               | ze/Package (check only one op                                                                       | - /                                                                                                                                                                    |

|                                                                                                                                               |                                                                                                     | 32K                                                                                                                                                                    |

| TQFP64 14x14<br>TQFP64 10x10                                                                                                                  | [] ST72521BM9<br>::   [] ST72521BR9<br>::   [] ST72521BAR9                                          | <br>       [] ST72521BR6<br>      [] ST72521BAR6                                                                                                                       |

| DIE FORM:                                                                                                                                     | 60K                                                                                                 | 32K                                                                                                                                                                    |

| 80-pin:<br>64-pin:                                                                                                                            |                                                                                                     | <br> <br>  []                                                                                                                                                          |

| Conditioning (check only                                                                                                                      |                                                                                                     |                                                                                                                                                                        |

| Packa                                                                                                                                         | aged Product                                                                                        | Die Product (dice tested at 25°C only)                                                                                                                                 |

| [] Tape & Reel                                                                                                                                |                                                                                                     | <ul> <li>[] Tape &amp; Reel</li> <li>[] Inked wafer</li> <li>[] Sawn wafer on sticky foil</li> <li>Please refer to datasheet for specific sales conditions:</li> </ul> |

| <br>Standard                                                                                                                                  | Automotive                                                                                          | Temp. Range                                                                                                                                                            |

| []  <br>[]                                                                                                                                    | []<br>[]<br>[]                                                                                      | <pre></pre>                                                                                                                                                            |

|                                                                                                                                               | [ ] No<br>re letters, digits, '.', '-', '/' and sp                                                  | []Yes "" (10 char. max)<br>aces only.                                                                                                                                  |

| Clock Source Selection<br>[] Resona                                                                                                           | tor: [] LP: Low power rese<br>[] MP: Medium power<br>[] MS: Medium speed<br>[] HS: High speed res   | r resonator (2 to 4 MHz)<br>I resonator (4 to 8 MHz)                                                                                                                   |

| [] Internal<br>[] Externa<br>PLL<br>LVD Reset [] Disable<br>Reset Delay<br>Watchdog Selection:<br>Watchdog Reset on Ha<br>Readout Protection: | RC:<br>I Clock<br>[] Disabled<br>d [] High threshold [<br>[] 256 Cycles [<br>[] Software Activation | [] Enabled<br>] Med. threshold [] Low threshold<br>] 4096 Cycles                                                                                                       |

| 0: /                                                                                                                                          |                                                                                                     |                                                                                                                                                                        |

| ase download the latest p://www.st.com/mcu > c                                                                                                | version of this option list from:<br>downloads > ST7 microcontro                                    | ollers > Option list                                                                                                                                                   |

57

# DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

### Table 32. Suggested List of Socket Types

| Device         | Socket (supplied with ST7MDT20M-<br>EMU3) | Emulator Adapter (supplied with<br>ST7MDT20M-EMU3) |

|----------------|-------------------------------------------|----------------------------------------------------|

| TQFP64 14 x14  | CAB 3303262                               | CAB 3303351                                        |

| TQFP64 10 x10  | YAMAICHI IC149-064-*75-*5                 | YAMAICHI ICP-064-6                                 |

| TQFP80 14 X 14 | YAMAICHI IC149-080-*51-*5                 | YAMAICHI ICP-080-7                                 |

# 14.3.1 Socket and Emulator Adapter Information

For information on the type of socket that is supplied with the emulator, refer to the suggested list of sockets in Table 32.

**Note:** Before designing the board layout, it is recommended to check the overall dimensions of the socket as they may be greater than the dimensions of the device.

For footprint and other mechanical information about these sockets and adapters, refer to the manufacturer's datasheet (www.yamaichi.de for

57/

TQFP64 10 x 10 and TQFP80 14 x 14 and www.cabgmbh.com for TQFP64 14 x 14)

### **Related Documentation**

AN 978: ST7 Visual Develop Software Key Debugging Features

AN 1938: ST7 Visual Develop for ST7 Cosmic C toolset users

AN 1939: ST7 Visual Develop for ST7 Metroworks C toolset users

AN 1940: ST7 Visual Develop for ST7 Assembler Linker toolset users