# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48 MIPS                                                         |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART, USB                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 40                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | ·                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                    |

| Data Converters            | A/D 32x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f380-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 25.6. SPI Special Function Registers                                  | 256 |

|-----------------------------------------------------------------------|-----|

| 26. Timers                                                            |     |

| 26.1. Timer 0 and Timer 1                                             |     |

| 26.1.1. Mode 0: 13-bit Counter/Timer                                  |     |

| 26.1.2. Mode 1: 16-bit Counter/Timer                                  |     |

| 26.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload                  |     |

| 26.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)               |     |

| 26.2. Timer 2                                                         |     |

| 26.2.1. 16-bit Timer with Auto-Reload                                 |     |

| 26.2.2. 8-bit Timers with Auto-Reload                                 |     |

| 26.2.3. Timer 2 Capture Modes: USB Start-of-Frame or LFO Falling Edge |     |

| 26.3. Timer 3                                                         |     |

| 26.3.1. 16-bit Timer with Auto-Reload                                 |     |

| 26.3.2. 8-bit Timers with Auto-Reload                                 |     |

| 26.3.3. Timer 3 Capture Modes: USB Start-of-Frame or LFO Falling Edge |     |

| 26.4. Timer 4                                                         |     |

| 26.4.1. 16-bit Timer with Auto-Reload                                 |     |

| 26.4.2. 8-bit Timers with Auto-Reload                                 |     |

| 26.5. Timer 5                                                         |     |

| 26.5.1. 16-bit Timer with Auto-Reload                                 |     |

| 26.5.2. 8-bit Timers with Auto-Reload                                 | 294 |

| 27. Programmable Counter Array                                        | 298 |

| 27.1. PCA Counter/Timer                                               |     |

| 27.2. PCA0 Interrupt Sources                                          | 300 |

| 27.3. Capture/Compare Modules                                         | 301 |

| 27.3.1. Edge-triggered Capture Mode                                   | 302 |

| 27.3.2. Software Timer (Compare) Mode                                 | 303 |

| 27.3.3. High-Speed Output Mode                                        |     |

| 27.3.4. Frequency Output Mode                                         | 305 |

| 27.3.5. 8-bit Pulse Width Modulator Mode                              | 306 |

| 27.3.6. 16-Bit Pulse Width Modulator Mode                             | 307 |

| 27.4. Watchdog Timer Mode                                             | 308 |

| 27.4.1. Watchdog Timer Operation                                      |     |

| 27.4.2. Watchdog Timer Usage                                          |     |

| 27.5. Register Descriptions for PCA0                                  |     |

| 28. C2 Interface                                                      |     |

| 28.1. C2 Interface Registers                                          |     |

| 28.2. C2 Pin Sharing                                                  |     |

| Document Change List                                                  |     |

| Contact Information                                                   | 321 |

| Figure 14.9. Multiplexed 8-bit MOVX without Bank Select Timing                 | . 108 |

|--------------------------------------------------------------------------------|-------|

| Figure 14.10. Multiplexed 8-bit MOVX with Bank Select Timing                   |       |

| Figure 17.1. Reset Sources                                                     | . 129 |

| Figure 17.2. Power-On and VDD Monitor Reset Timing                             | . 130 |

| Figure 18.1. Flash Program Memory Map and Security Byte                        | . 137 |

| Figure 19.1. Oscillator Options                                                | . 142 |

| Figure 19.2. External Crystal Example                                          | . 150 |

| Figure 20.1. Port I/O Functional Block Diagram (Port 0 through Port 3)         | . 153 |

| Figure 20.2. Port I/O Cell Block Diagram                                       | . 154 |

| Figure 20.3. Peripheral Availability on Port I/O Pins                          | . 155 |

| Figure 20.4. Crossbar Priority Decoder in Example Configuration                |       |

|                                                                                | . 156 |

| Figure 20.5. Crossbar Priority Decoder in Example Configuration (3 Pins Skippe | d)    |

|                                                                                | . 157 |

| Figure 21.1. USB0 Block Diagram                                                |       |

| Figure 21.2. USB0 Register Access Scheme                                       | . 175 |

| Figure 21.3. USB FIFO Allocation                                               | . 181 |

| Figure 22.1. SMBus Block Diagram                                               | . 205 |

| Figure 22.2. Typical SMBus Configuration                                       | . 206 |

| Figure 22.3. SMBus Transaction                                                 |       |

| Figure 22.4. Typical SMBus SCL Generation                                      | . 209 |

| Figure 22.5. Typical Master Write Sequence                                     | . 223 |

| Figure 22.6. Typical Master Read Sequence                                      | . 224 |

| Figure 22.7. Typical Slave Write Sequence                                      | . 225 |

| Figure 22.8. Typical Slave Read Sequence                                       | . 226 |

| Figure 23.1. UARTO Block Diagram                                               | . 232 |

| Figure 23.2. UART0 Baud Rate Logic                                             | . 233 |

| Figure 23.3. UART Interconnect Diagram                                         | . 234 |

| Figure 23.4. 8-Bit UART Timing Diagram                                         | . 234 |

| Figure 23.5. 9-Bit UART Timing Diagram                                         | . 235 |

| Figure 23.6. UART Multi-Processor Mode Interconnect Diagram                    | . 236 |

| Figure 24.1. UART1 Block Diagram                                               | . 240 |

| Figure 24.2. UART1 Timing Without Parity or Extra Bit                          | . 242 |

| Figure 24.3. UART1 Timing With Parity                                          | . 242 |

| Figure 24.4. UART1 Timing With Extra Bit                                       | . 242 |

| Figure 24.5. Typical UART Interconnect Diagram                                 |       |

| Figure 24.6. UART Multi-Processor Mode Interconnect Diagram                    | . 244 |

| Figure 25.1. SPI Block Diagram                                                 |       |

| Figure 25.2. Multiple-Master Mode Connection Diagram                           |       |

| Figure 25.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diag | gram  |

|                                                                                |       |

| Figure 25.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diag   | gram  |

|                                                                                | -     |

| Figure 25.5. Master Mode Data/Clock Timing                                     |       |

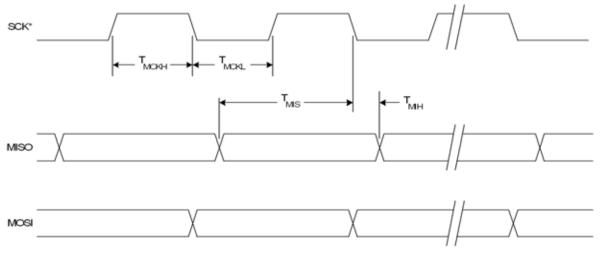

| Figure 25.6. Slave Mode Data/Clock Timing (CKPHA = 0)                          | . 255 |

|                                                                                |       |

| Name | Pin Nu        | umbers | Туре             | Description                                                    |

|------|---------------|--------|------------------|----------------------------------------------------------------|

|      | 48-pin 32-pin |        |                  |                                                                |

| P0.7 | 47            | 27     | D I/O or<br>A In | Port 0.7.                                                      |

| P1.0 | 46            | 26     | D I/O or<br>A In | Port 1.0. See Section 20 for a complete description of Port 1. |

| P1.1 | 45            | 25     | D I/O or<br>A In | Port 1.1.                                                      |

| P1.2 | 44            | 24     | D I/O or<br>A In | Port 1.2.                                                      |

| P1.3 | 43            | 23     | D I/O or<br>A In | Port 1.3.                                                      |

| P1.4 | 42            | 22     | D I/O or<br>A In | Port 1.4.                                                      |

| P1.5 | 41            | 21     | D I/O or<br>A In | Port 1.5.                                                      |

| P1.6 | 40            | 20     | D I/O or<br>A In | Port 1.6.                                                      |

| P1.7 | 39            | 19     | D I/O or<br>A In | Port 1.7.                                                      |

| P2.0 | 38            | 18     | D I/O or<br>A In | Port 2.0. See Section 20 for a complete description of Port 2. |

| P2.1 | 37            | 17     | D I/O or<br>A In | Port 2.1.                                                      |

| P2.2 | 36            | 16     | D I/O or<br>A In | Port 2.2.                                                      |

| P2.3 | 35            | 15     | D I/O or<br>A In | Port 2.3.                                                      |

| P2.4 | 34            | 14     | D I/O or<br>A In | Port 2.4.                                                      |

| P2.5 | 33            | 13     | D I/O or<br>A In | Port 2.5.                                                      |

| P2.6 | 32            | 12     | D I/O or<br>A In | Port 2.6.                                                      |

| P2.7 | 31            | 11     | D I/O or<br>A In | Port 2.7.                                                      |

| P3.0 | 30            | —      | D I/O or<br>A In | Port 3.0. See Section 20 for a complete description of Port 3. |

## Table 3.1. Pin Definitions for the C8051F380/1/2/3/4/5/6/7/C (Continued)

#### Table 5.10. ADC0 Electrical Characteristics

$V_{DD}$  = 3.0 V, VREF = 2.40 V (REFSL=0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                                  | Test Condition               | Min       | Тур       | Max             | Unit             |

|------------------------------------------------------------|------------------------------|-----------|-----------|-----------------|------------------|

| DC Accuracy                                                |                              |           |           |                 | ļ                |

| Resolution                                                 |                              |           | 10        |                 | bits             |

| Integral Nonlinearity                                      |                              | —         | ±0.5      | ±1              | LSB              |

| Differential Nonlinearity                                  | Guaranteed Monotonic         | _         | ±0.5      | ±1              | LSB              |

| Offset Error                                               |                              | -2        | 0         | 2               | LSB              |

| Full Scale Error                                           |                              | -5        | -2        | 0               | LSB              |

| Offset Temperature Coefficient                             |                              | _         | 0.005     | _               | LSB/°C           |

| Dynamic performance (10 kHz s                              | ine-wave single-ended input, | 1 dB belo | w Full So | ale, 500        | ksps)            |

| Signal-to-Noise Plus Distortion                            |                              | 55        | 58        | _               | dB               |

| Total Harmonic Distortion                                  | Up to the 5th harmonic       | _         | -73       | _               | dB               |

| Spurious-Free Dynamic Range                                |                              | _         | 78        | _               | dB               |

| Conversion Rate                                            |                              |           |           |                 |                  |

| SAR Conversion Clock                                       |                              | _         | _         | 8.33            | MHz              |

| Conversion Time in SAR Clocks                              | 10-bit Mode<br>8-bit Mode    | 13<br>11  | _         | _               | clocks<br>clocks |

| Track/Hold Acquisition Time                                |                              | 300       |           | _               | ns               |

| Throughput Rate                                            |                              | _         | _         | 500             | ksps             |

| Analog Inputs                                              |                              | 1         |           |                 |                  |

| ADC Input Voltage Range                                    | Single Ended (AIN+ – GND)    | 0         | _         | VREF            | V                |

|                                                            | Differential (AIN+ – AIN–)   | -VREF     | _         | VREF            | V                |

| Absolute Pin Voltage with respect to GND                   | Single Ended or Differential | 0         | _         | V <sub>DD</sub> | V                |

| Sampling Capacitance                                       |                              | _         | 30        | _               | pF               |

| Input Multiplexer Impedance                                |                              |           | 5         | _               | kΩ               |

| Power Specifications                                       |                              |           |           |                 |                  |

| Power Supply Current<br>(V <sub>DD</sub> supplied to ADC0) | Operating Mode, 500 ksps     | -         | 750       | 1000            | μA               |

| Power Supply Rejection                                     |                              |           | 1         |                 | mV/V             |

| Note: Represents one standard devia                        | tion from the mean.          | 1         |           | 1               | 1                |

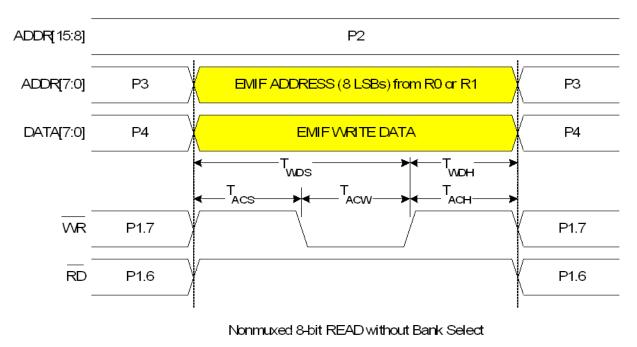

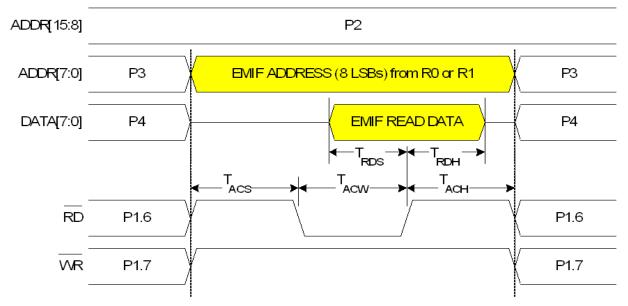

## 14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111

Nonmuxed 8-bit WRITE without Bank Select

## Table 15.2. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Page      | Description                     | Page |

|----------|---------|-----------|---------------------------------|------|

| TMR5RLL  | 0xCA    | F         | Timer/Counter 5 Reload Low      | 296  |

| USB0ADR  | 0x96    | All Pages | USB0 Indirect Address Register  | 176  |

| USB0DAT  | 0x97    | All Pages | USB0 Data Register              | 177  |

| USB0XCN  | 0xD7    | All Pages | USB0 Transceiver Control        | 174  |

| VDM0CN   | 0xFF    | All Pages | V <sub>DD</sub> Monitor Control | 132  |

| XBR0     | 0xE1    | All Pages | Port I/O Crossbar Control 0     | 159  |

| XBR1     | 0xE2    | All Pages | Port I/O Crossbar Control 1     | 160  |

| XBR2     | 0xE3    | All Pages | Port I/O Crossbar Control 2     | 161  |

## SFR Definition 16.4. EIP1: Extended Interrupt Priority 1

| Bit   | 7   | 6    | 5    | 4     | 3     | 2      | 1     | 0     |

|-------|-----|------|------|-------|-------|--------|-------|-------|

| Name  | PT3 | PCP1 | PCP0 | PPCA0 | PADC0 | PWADC0 | PUSB0 | PSMB0 |

| Туре  | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W   | R/W   |

| Reset | 0   | 0    | 0    | 0     | 0     | 0      | 0     | 0     |

#### SFR Address = 0xF6; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                     |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PT3    | Timer 3 Interrupt Priority Control.This bit sets the priority of the Timer 3 interrupt.0: Timer 3 interrupts set to low priority level.1: Timer 3 interrupts set to high priority level.                                                                                                                     |

| 6   | PCP1   | <ul> <li>Comparator1 (CP1) Interrupt Priority Control.</li> <li>This bit sets the priority of the CP1 interrupt.</li> <li>0: CP1 interrupt set to low priority level.</li> <li>1: CP1 interrupt set to high priority level.</li> </ul>                                                                       |

| 5   | PCP0   | <ul> <li>Comparator0 (CP0) Interrupt Priority Control.</li> <li>This bit sets the priority of the CP0 interrupt.</li> <li>0: CP0 interrupt set to low priority level.</li> <li>1: CP0 interrupt set to high priority level.</li> </ul>                                                                       |

| 4   | PPCA0  | <ul> <li>Programmable Counter Array (PCA0) Interrupt Priority Control.</li> <li>This bit sets the priority of the PCA0 interrupt.</li> <li>0: PCA0 interrupt set to low priority level.</li> <li>1: PCA0 interrupt set to high priority level.</li> </ul>                                                    |

| 3   | PADC0  | <ul> <li>ADC0 Conversion Complete Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 Conversion Complete interrupt.</li> <li>0: ADC0 Conversion Complete interrupt set to low priority level.</li> <li>1: ADC0 Conversion Complete interrupt set to high priority level.</li> </ul> |

| 2   | PWADC0 | <ul> <li>ADC0 Window Comparator Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 Window interrupt.</li> <li>0: ADC0 Window interrupt set to low priority level.</li> <li>1: ADC0 Window interrupt set to high priority level.</li> </ul>                                          |

| 1   | PUSB0  | USB (USB0) Interrupt Priority Control.<br>This bit sets the priority of the USB0 interrupt.<br>0: USB0 interrupt set to low priority level.<br>1: USB0 interrupt set to high priority level.                                                                                                                 |

| 0   | PSMB0  | <ul> <li>SMBus0 Interrupt Priority Control.</li> <li>This bit sets the priority of the SMB0 interrupt.</li> <li>0: SMB0 interrupt set to low priority level.</li> <li>1: SMB0 interrupt set to high priority level.</li> </ul>                                                                               |

## C8051F380/1/2/3/4/5/6/7/C

## SFR Definition 18.2. FLKEY: Flash Lock and Key

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|---|---|---|---|---|

| Name  |   | FLKEY[7:0]      |   |   |   |   |   |   |

| Туре  |   | R/W             |   |   |   |   |   |   |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

#### SFR Address = 0xB7; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FLKEY[7:0] | Flash Lock and Key Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | This register provides a lock and key function for Flash erasures and writes. Flash writes and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY register. Flash writes and erases are automatically disabled after the next write or erase is complete. If any writes to FLKEY are performed incorrectly, or if a Flash write or erase operation is attempted while these operations are disabled, the Flash will be permanently locked from writes or erasures until the next device reset. If an application never writes to Flash, it can intentionally lock the Flash by writing a non-0xA5 value to |

|     |            | FLKEY from software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |            | Read:<br>When read, bits 1–0 indicate the current Flash lock state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |            | 00: Flash is write/erase locked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | 01: The first key code has been written (0xA5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |            | 10: Flash is unlocked (writes/erases allowed).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | 11: Flash writes/erases disabled until the next reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## **19.5.** Programmable Internal Low-Frequency (L-F) Oscillator

All C8051F380/1/2/3/4/5/6/7/C devices include a programmable low-frequency internal oscillator, which is calibrated to a nominal frequency of 80 kHz. The low-frequency oscillator circuit includes a divider that can be changed to divide the clock by 1, 2, 4, or 8, using the OSCLD bits in the OSCLCN register (see SFR Definition 19.5). Additionally, the OSCLF[3:0] bits can be used to adjust the oscillator's output frequency.

#### 19.5.1. Calibrating the Internal L-F Oscillator

Timers 2 and 3 include capture functions that can be used to capture the oscillator frequency, when running from a known time base. When either Timer 2 or Timer 3 is configured for L-F Oscillator Capture Mode, a falling edge (Timer 2) or rising edge (Timer 3) of the low-frequency oscillator's output will cause a capture event on the corresponding timer. As a capture event occurs, the current timer value (TMRnH:TMRnL) is copied into the timer reload registers (TMRnRLH:TMRnRLL). By recording the difference between two successive timer capture values, the low-frequency oscillator's period can be calculated. The OSCLF bits can then be adjusted to produce the desired oscillator frequency.

#### SFR Definition 19.5. OSCLCN: Internal L-F Oscillator Control

| Bit   | 7      | 6       | 5          | 4      | 3      | 2      | 1          | 0 |  |

|-------|--------|---------|------------|--------|--------|--------|------------|---|--|

| Name  | OSCLEN | OSCLRDY | OSCLF[3:0] |        |        |        | OSCLD[1:0] |   |  |

| Туре  | R/W    | R       | R.W        |        |        |        | R/         | W |  |

| Reset | 0      | 0       | Varies     | Varies | Varies | Varies | 0          | 0 |  |

SFR Address = 0x86; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OSCLEN     | Internal L-F Oscillator Enable.                                                                                                                                                                                                                                                                                     |

|     |            | 0: Internal L-F Oscillator Disabled.                                                                                                                                                                                                                                                                                |

|     |            | 1: Internal L-F Oscillator Enabled.                                                                                                                                                                                                                                                                                 |

| 6   | OSCLRDY    | Internal L-F Oscillator Ready.                                                                                                                                                                                                                                                                                      |

|     |            | 0: Internal L-F Oscillator frequency not stabilized.                                                                                                                                                                                                                                                                |

|     |            | 1: Internal L-F Oscillator frequency stabilized.                                                                                                                                                                                                                                                                    |

|     |            | <b>Note:</b> OSCLRDY is only set back to 0 in the event of a device reset or a change to the OSCLD[1:0] bits.                                                                                                                                                                                                       |

| 5:2 | OSCLF[3:0] | Internal L-F Oscillator Frequency Control Bits.                                                                                                                                                                                                                                                                     |

|     |            | Fine-tune control bits for the Internal L-F oscillator frequency. When set to 0000b, the L-F oscillator operates at its fastest setting. When set to 1111b, the L-F oscillator operates at its slowest setting. The OSCLF bits should only be changed by firmware when the L-F oscillator is disabled (OSCLEN = 0). |

| 1:0 | OSCLD[1:0] | Internal L-F Oscillator Divider Select.                                                                                                                                                                                                                                                                             |

|     |            | 00: Divide by 8 selected.                                                                                                                                                                                                                                                                                           |

|     |            | 01: Divide by 4 selected.                                                                                                                                                                                                                                                                                           |

|     |            | 10: Divide by 2 selected.                                                                                                                                                                                                                                                                                           |

|     |            | 11: Divide by 1 selected.                                                                                                                                                                                                                                                                                           |

## SFR Definition 20.22. P4MDOUT: Port 4 Output Mode

| Bit   | 7                                        | 6            | 5 | 4 | 3        | 2 | 1 | 0 |  |  |  |

|-------|------------------------------------------|--------------|---|---|----------|---|---|---|--|--|--|

| Name  | •                                        | P4MDOUT[7:0] |   |   |          |   |   |   |  |  |  |

| Туре  |                                          | R/W          |   |   |          |   |   |   |  |  |  |

| Reset | t 0                                      | 0            | 0 | 0 | 0        | 0 | 0 | 0 |  |  |  |

| SFR A | SFR Address = 0xAE; SFR Page = All Pages |              |   |   |          |   |   |   |  |  |  |

| Bit   | Name                                     |              |   |   | Function |   |   |   |  |  |  |

| 7:0 | P4MDOUT[7:0] | Output Configuration Bits for P4.7–P4.0 (respectively).                                                                                                                     |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |              | These bits are ignored if the corresponding bit in register P4MDIN is logic 0.<br>0: Corresponding P4.n Output is open-drain.<br>1: Corresponding P4.n Output is push-pull. |

## USB Register Definition 21.25. EOUTCNTH: USB0 OUT Endpoint Count High

| Bit   | 7                           | 6 | 5        | 4 | 3 | 2 | 1    | 0      |  |  |

|-------|-----------------------------|---|----------|---|---|---|------|--------|--|--|

| Name  |                             |   |          |   |   |   | EOCI | H[1:0] |  |  |

| Туре  | R                           | R | R        | R | R | R | R    | R      |  |  |

| Rese  | t 0                         | 0 | 0        | 0 | 0 | 0 | 0    | 0      |  |  |

| USB R | USB Register Address = 0x17 |   |          |   |   |   |      |        |  |  |

| Bit   | Name                        |   | Function |   |   |   |      |        |  |  |

| Bit | Name      | Function                                                                                                                                                                |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused    | Read = 000000b. Write = don't care.                                                                                                                                     |

| 1:0 | EOCH[1:0] | OUT Endpoint Count High Byte.                                                                                                                                           |

|     |           | EOCH holds the upper 2-bits of the 10-bit number of data bytes in the last received packet in the current OUT endpoint FIFO. This number is only valid while OPRDY = 1. |

| SMBnCS1 | SMBnCS0 | SMBus0 Clock Source        | SMBus1 Clock Source        |

|---------|---------|----------------------------|----------------------------|

| 0       | 0       | Timer 0 Overflow           | Timer 0 Overflow           |

| 0       | 1       | Timer 1 Overflow           | Timer 5 Overflow           |

| 1       | 0       | Timer 2 High Byte Overflow | Timer 2 High Byte Overflow |

| 1       | 1       | Timer 2 Low Byte Overflow  | Timer 2 Low Byte Overflow  |

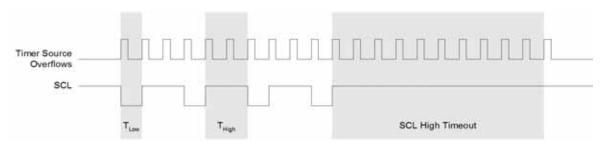

Table 22.1. SMBus Clock Source Selection

The SMBnCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 22.1.The selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus0 and SMBus1 clock rates simultaneously. Timer configuration is covered in Section "26. Timers" on page 263.

$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$

#### Equation 22.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 22.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 22.2.

BitRate =

$$\frac{f_{ClockSourceOverflow}}{3}$$

#### Equation 22.2. Typical SMBus Bit Rate

Figure 22.4 shows the typical SCL generation described by Equation 22.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 22.1.

Figure 22.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 22.2 shows the minimum setup.

## SFR Definition 22.7. SMB0ADM: SMBus0 Slave Address Mask

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|------------|---|---|---|---|---|---|--|--|--|

| Name  |   | SLVM0[6:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W        |   |   |   |   |   |   |  |  |  |

| Reset | 1 |            |   |   |   |   |   |   |  |  |  |

SFR Address = 0xCE; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                                                                                                             |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM0[6:0] | SMBus0 Slave Address Mask.                                                                                                                                                                                                                                                           |

|     |            | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM0[6:0] enables comparisons with the corresponding bit in SLV0[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK0     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                         |

|     |            | Enables hardware acknowledgement of slave address and received data bytes.<br>0: Firmware must manually acknowledge all incoming address and data bytes.<br>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.                                              |

#### SFR Definition 22.8. SMB1ADR: SMBus1 Slave Address

| Bit   | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------|---|---|---|---|---|---|--|--|--|

| Name  |   | SLV1[6:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W       |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0         | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

#### SFR Address = 0xCF; SFR Page = F

| Bit | Name      | Function                                                                                                                                                                                                                                                                    |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV1[6:0] | SMBus1 Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |           | Defines the SMBus1 Slave Address(es) for automatic hardware acknowledge-<br>ment. Only address bits which have a 1 in the corresponding bit position in<br>SLVM1[6:0] are checked against the incoming address. This allows multiple<br>addresses to be recognized.         |

| 0   | GC1       | General Call Address Enable.                                                                                                                                                                                                                                                |

|     |           | <ul> <li>When hardware address recognition is enabled (EHACK1 = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

## 24.3. Configuration and Operation

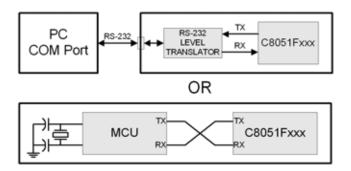

UART1 provides standard asynchronous, full duplex communication. It can operate in a point-to-point serial communications application, or as a node on a multi-processor serial interface. To operate in a point-to-point application, where there are only two devices on the serial bus, the MCE1 bit in SMOD1 should be cleared to 0. For operation as part of a multi-processor communications bus, the MCE1 and XBE1 bits should both be set to 1. In both types of applications, data is transmitted from the microcontroller on the TX1 pin, and received on the RX1 pin. The TX1 and RX1 pins are configured using the crossbar and the Port I/O registers, as detailed in Section "20. Port Input/Output" on page 153.

In typical UART communications, The transmit (TX) output of one device is connected to the receive (RX) input of the other device, either directly or through a bus transceiver, as shown in Figure 24.5.

Figure 24.5. Typical UART Interconnect Diagram

#### 24.3.1. Data Transmission

Data transmission is double-buffered, and begins when software writes a data byte to the SBUF1 register. Writing to SBUF1 places data in the Transmit Holding Register, and the Transmit Holding Register Empty flag (THRE1) will be cleared to 0. If the UARTs shift register is empty (i.e. no transmission is in progress) the data will be placed in the shift register, and the THRE1 bit will be set to 1. If a transmission is in progress, the data will remain in the Transmit Holding Register until the current transmission is complete. The TI1 Transmit Interrupt Flag (SCON1.1) will be set at the end of any transmission (the beginning of the stop-bit time). If enabled, an interrupt will occur when TI1 is set.

If the extra bit function is enabled (XBE1 = 1) and the parity function is disabled (PE1 = 0), the value of the TBX1 (SCON1.3) bit will be sent in the extra bit position. When the parity function is enabled (PE1 = 1), hardware will generate the parity bit according to the selected parity type (selected with S1PT[1:0]), and append it to the data field. Note: when parity is enabled, the extra bit function is not available.

#### 24.3.2. Data Reception

Data reception can begin any time after the REN1 Receive Enable bit (SCON1.4) is set to logic 1. After the stop bit is received, the data byte will be stored in the receive FIFO if the following conditions are met: the receive FIFO (3 bytes deep) must not be full, and the stop bit(s) must be logic 1. In the event that the receive FIFO is full, the incoming byte will be lost, and a Receive FIFO Overrun Error will be generated (OVR1 in register SCON1 will be set to logic 1). If the stop bit(s) were logic 0, the incoming data will not be stored in the receive FIFO. If the reception conditions are met, the data is stored in the receive FIFO, and the RI1 flag will be set. Note: when MCE1 = 1, RI1 will only be set if the extra bit was equal to 1. Data can be read from the receive FIFO by reading the SBUF1 register. The SBUF1 register represents the oldest byte in the FIFO. After SBUF1 is read, the next byte in the FIFO is immediately loaded into SBUF1, and space is made available in the FIFO for another incoming byte. If enabled, an interrupt will occur when RI1 is set. RI1 can only be cleared to '0' by software when there is no more information in the FIFO. The recommended procedure to empty the FIFO contents is:

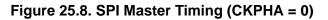

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

## Figure 25.9. SPI Master Timing (CKPHA = 1)

## SFR Definition 26.1. CKCON: Clock Control

| Bit   | 7    | 6    | 5    | 4    | 3   | 2   | 1        | 0 |

|-------|------|------|------|------|-----|-----|----------|---|

| Name  | ТЗМН | T3ML | T2MH | T2ML | T1M | ТОМ | SCA[1:0] |   |

| Туре  | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W      |   |

| Reset | 0    | 0    | 0    | 0    | 0   | 0   | 0        | 0 |

#### SFR Address = 0x8E; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ТЗМН     | Timer 3 High Byte Clock Select.                                                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).<br>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.<br>1: Timer 3 high byte uses the system clock.                                                                                                     |

| 6   | T3ML     | Timer 3 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 low byte uses the system clock.</li> </ul>                                    |

| 5   | T2MH     | Timer 2 High Byte Clock Select.                                                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).<br>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.<br>1: Timer 2 high byte uses the system clock.                                                                                                     |

| 4   | T2ML     | Timer 2 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |

| 3   | T1       | Timer 1 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                             |

| 2   | Т0       | Timer 0 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.<br>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].<br>1: Counter/Timer 0 uses the system clock.                                                                                                             |

|     | 00414.01 |                                                                                                                                                                                                                                                                                                                   |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.These bits control the Timer 0/1 Clock Prescaler:00: System clock divided by 1201: System clock divided by 410: System clock divided by 4811: External clock divided by 8 (synchronized with the system clock)                                                                            |

|     |          | 1                                                                                                                                                                                                                                                                                                                 |

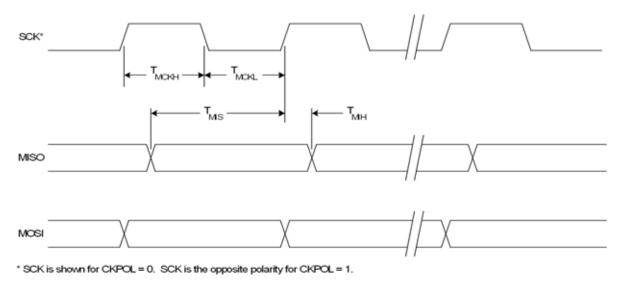

Figure 26.2. T0 Mode 2 Block Diagram

#### 26.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates or overflow conditions for other peripherals. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

## SFR Definition 26.18. TMR3H Timer 3 High Byte

| Bit    | 7            | 6          | 5   | 4 | 3        | 2 | 1 | 0 |  |  |  |  |

|--------|--------------|------------|-----|---|----------|---|---|---|--|--|--|--|

| Name   |              | TMR3H[7:0] |     |   |          |   |   |   |  |  |  |  |

| Туре   |              | R/W        |     |   |          |   |   |   |  |  |  |  |

| Reset  | 0            | 0          | 0   | 0 | 0        | 0 | 0 | 0 |  |  |  |  |

| SFR Ad | dress = 0x95 | ; SFR Page | = 0 |   |          |   |   |   |  |  |  |  |

| Dit    | Namo         |            |     |   | Eurotion |   |   |   |  |  |  |  |

| Bit | Name       | Function                                                                                                                                        |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3H[7:0] | Timer 3 High Byte.                                                                                                                              |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-bit mode, TMR3H contains the 8-bit high byte timer value. |

## SFR Definition 26.24. TMR5CN: Timer 5 Control

| Bit   | 7    | 6    | 5      | 4 | 3       | 2   | 1 | 0      |

|-------|------|------|--------|---|---------|-----|---|--------|

| Name  | TF5H | TF5L | TF5LEN |   | T5SPLIT | TR5 |   | T5XCLK |

| Туре  | R/W  | R/W  | R/W    | R | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0 | 0       | 0   | 0 | 0      |

#### SFR Address = 0xC8; SFR Page = F; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF5H    | Timer 5 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                            |

|     |         | Set by hardware when the Timer 5 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 5 overflows from 0xFFFF to 0x0000. When the Timer 5 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 5 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                         |

| 6   | TF5L    | Timer 5 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | Set by hardware when the Timer 5 low byte overflows from 0xFF to 0x00. TF5L will be set when the low byte overflows regardless of the Timer 5 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                      |

| 5   | TF5LEN  | Timer 5 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                          |

|     |         | When set to 1, this bit enables Timer 5 Low Byte interrupts. If Timer 5 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 5 overflows.                                                                                                                                                                                                                                                 |

| 4   | Unused  | Read = 0b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                              |

| 3   | T5SPLIT | Timer 5 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | When this bit is set, Timer 5 operates as two 8-bit timers with auto-reload.                                                                                                                                                                                                                                                                                                                                                |

|     |         | 0: Timer 5 operates in 16-bit auto-reload mode.<br>1: Timer 5 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                     |

|     | TDE     |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2   | TR5     | Timer 5 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |         | Timer 5 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR5H only; TMR5L is always enabled in split mode.                                                                                                                                                                                                                                                                                    |

| 1   | Unused  | Read = 0b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                              |

| 0   | T5XCLK  | Timer 5 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                              |

|     |         | <ul> <li>This bit selects the external clock source for Timer 5. However, the Timer 5 Clock</li> <li>Select bits (T5MH and T5ML in register CKCON1) may still be used to select</li> <li>between the external clock and the system clock for either timer.</li> <li>0: Timer 5 clock is the system clock divided by 12.</li> <li>1: Timer 5 clock is the external clock divided by 8 (synchronized with SYSCLK).</li> </ul> |

| System Clock (Hz)      | PCA0CPL4 | Timeout Interval (ms)<br>16.4 |  |

|------------------------|----------|-------------------------------|--|

| 48,000,000             | 255      |                               |  |

| 48,000,000             | 128      | 8.3                           |  |

| 48,000,000             | 32       | 2.1                           |  |

| 12,000,000             | 255      | 65.5                          |  |

| 12,000,000             | 128      | 33.0                          |  |

| 12,000,000             | 32       | 8.4                           |  |

| 1,500,000 <sup>2</sup> | 255      | 524.3                         |  |

| 1,500,000 <sup>2</sup> | 128      | 264.2                         |  |

| 1,500,000 <sup>2</sup> | 32       | 67.6                          |  |

| 32,768                 | 255      | 24,000                        |  |

| 32,768                 | 128      | 12,094                        |  |

| 32,768                 | 32       | 3,094                         |  |

## Table 27.3. Watchdog Timer Timeout Intervals<sup>1</sup>

Notes:

1. Assumes SYSCLK/12 as the PCA clock source, and a PCA0L value of 0x00 at the update time.

2. Internal SYSCLK reset frequency = Internal Oscillator divided by 8.