Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48 MIPS                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | A/D 21x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f381-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

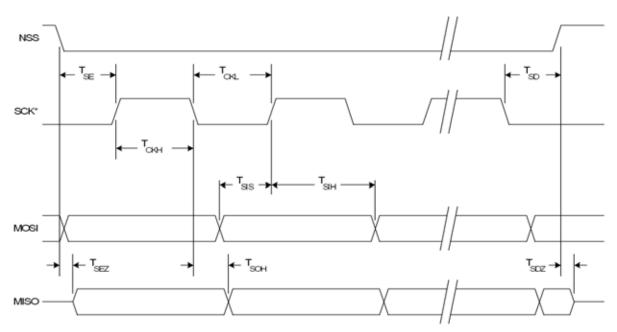

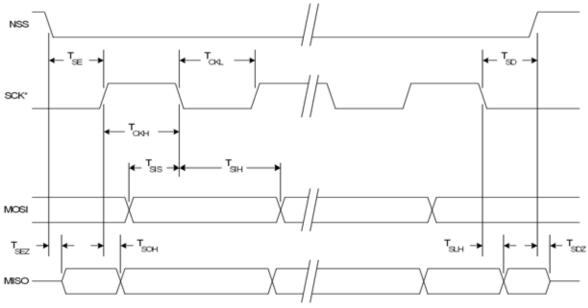

| Figure 25.7. Slave Mode Data/Clock Timing (CKPHA = 1)  | 256 |

|--------------------------------------------------------|-----|

| Figure 25.8. SPI Master Timing (CKPHA = 0)             | 260 |

| Figure 25.9. SPI Master Timing (CKPHA = 1)             |     |

| Figure 25.10. SPI Slave Timing (CKPHA = 0)             |     |

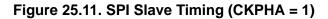

| Figure 25.11. SPI Slave Timing (CKPHA = 1)             | 261 |

| Figure 26.1. T0 Mode 0 Block Diagram                   | 267 |

| Figure 26.2. T0 Mode 2 Block Diagram                   |     |

| Figure 26.3. T0 Mode 3 Block Diagram                   | 269 |

| Figure 26.4. Timer 2 16-Bit Mode Block Diagram         | 274 |

| Figure 26.5. Timer 2 8-Bit Mode Block Diagram          |     |

| Figure 26.6. Timer 2 Capture Mode (T2SPLIT = 0)        |     |

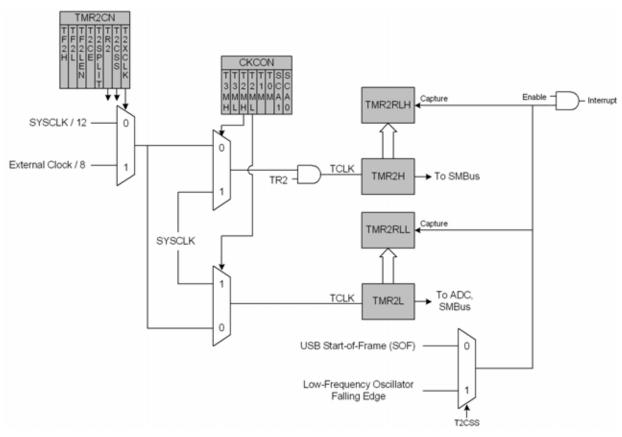

| Figure 26.7. Timer 2 Capture Mode (T2SPLIT = 0)        | 277 |

| Figure 26.8. Timer 3 16-Bit Mode Block Diagram         | 281 |

| Figure 26.9. Timer 3 8-Bit Mode Block Diagram          |     |

| Figure 26.10. Timer 3 Capture Mode (T3SPLIT = 0)       | 283 |

| Figure 26.11. Timer 3 Capture Mode (T3SPLIT = 0)       | 284 |

| Figure 26.12. Timer 4 16-Bit Mode Block Diagram        | 288 |

| Figure 26.13. Timer 4 8-Bit Mode Block Diagram         | 289 |

| Figure 26.14. Timer 5 16-Bit Mode Block Diagram        |     |

| Figure 26.15. Timer 5 8-Bit Mode Block Diagram         | 294 |

| Figure 27.1. PCA Block Diagram                         | 298 |

| Figure 27.2. PCA Counter/Timer Block Diagram           | 299 |

| Figure 27.3. PCA Interrupt Block Diagram               | 300 |

| Figure 27.4. PCA Capture Mode Diagram                  | 302 |

| Figure 27.5. PCA Software Timer Mode Diagram           |     |

| Figure 27.6. PCA High-Speed Output Mode Diagram        | 304 |

| Figure 27.7. PCA Frequency Output Mode                 |     |

| Figure 27.8. PCA 8-Bit PWM Mode Diagram                |     |

| Figure 27.9. PCA 16-Bit PWM Mode                       |     |

| Figure 27.10. PCA Module 4 with Watchdog Timer Enabled |     |

| Figure 28.1. Typical C2 Pin Sharing                    | 319 |

|                                                        |     |

Figure 3.9. QFN-32 Recommended PCB Land Pattern

| Table 3.7. QFN-32 PCB Land Pattern Dime | ensions |

|-----------------------------------------|---------|

|-----------------------------------------|---------|

| Dimension | Min      | Мах  | Dimension | Min  | Max  |

|-----------|----------|------|-----------|------|------|

| C1        | 4.80     | 4.90 | X2        | 3.20 | 3.40 |

| C2        | 4.80     | 4.90 | Y1        | 0.75 | 0.85 |

| E         | 0.50 BSC |      | Y2        | 3.20 | 3.40 |

| X1        | 0.20     | 0.30 |           |      | •    |

#### Notes:

#### General:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design:

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design:

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- 7. A 3x3 array of 1.0 mm openings on a 1.2mm pitch should be used for the center pad to assure the proper paste volume.

#### Card Assembly:

- **8.** A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### **Table 5.13. Comparator Electrical Characteristics**

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise noted.

| Parameter                                         | Test Condition          | Min   | Тур   | Max                    | Unit |

|---------------------------------------------------|-------------------------|-------|-------|------------------------|------|

| Response Time:                                    | CP0+ - CP0- = 100 mV    | _     | 100   | —                      | ns   |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | _     | 250   | _                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | _     | 175   | —                      | ns   |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | _     | 500   | —                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | _     | 320   | —                      | ns   |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | _     | 1100  | —                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV    | _     | 1050  | _                      | ns   |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV   | _     | 5200  | _                      | ns   |

| Common-Mode Rejection Ratio                       |                         | _     | 1.5   | 4                      | mV/V |

| Positive Hysteresis 1                             | CP0HYP1-0 = 00          | _     | 0     | 1                      | mV   |

| Positive Hysteresis 2                             | CP0HYP1-0 = 01          | 2     | 5     | 10                     | mV   |

| Positive Hysteresis 3                             | CP0HYP1-0 = 10          | 7     | 10    | 20                     | mV   |

| Positive Hysteresis 4                             | CP0HYP1-0 = 11          | 15    | 20    | 30                     | mV   |

| Negative Hysteresis 1                             | CP0HYN1-0 = 00          | _     | 0     | 1                      | mV   |

| Negative Hysteresis 2                             | CP0HYN1-0 = 01          | 2     | 5     | 10                     | mV   |

| Negative Hysteresis 3                             | CP0HYN1-0 = 10          | 7     | 10    | 20                     | mV   |

| Negative Hysteresis 4                             | CP0HYN1-0 = 11          | 15    | 20    | 30                     | mV   |

| Inverting or Non-Inverting Input<br>Voltage Range |                         | -0.25 | _     | V <sub>DD</sub> + 0.25 | V    |

| Input Capacitance                                 |                         | _     | 4     | _                      | pF   |

| Input Bias Current                                |                         | —     | 0.001 | —                      | nA   |

| Input Offset Voltage                              |                         | -10   |       | +10                    | mV   |

| Power Supply                                      |                         | •     |       |                        |      |

| Power Supply Rejection                            |                         | _     | 0.1   | _                      | mV/V |

| Power-up Time                                     |                         | _     | 10    | _                      | μs   |

| Supply Current at DC                              | Mode 0                  | _     | 20    | —                      | μA   |

|                                                   | Mode 1                  | —     | 10    | _                      | μA   |

|                                                   | Mode 2                  | -     | 4     | _                      | μA   |

|                                                   | Mode 3                  | —     | 1     | _                      | μA   |

| Note: Vcm is the common-mode vo                   | Itage on CP0+ and CP0–. | •     |       |                        |      |

### 6.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

### SFR Definition 6.5. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit                                      | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|--------------|---|---|---|---|---|---|---|

| Name                                     | ADC0GTH[7:0] |   |   |   |   |   |   |   |

| Туре                                     | R/W          |   |   |   |   |   |   |   |

| Reset                                    | 1            | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| SFR Address = 0xC4; SFR Page = All Pages |              |   |   |   |   |   |   |   |

| Bit | Name         | Function                                     |

|-----|--------------|----------------------------------------------|

| 7:0 | ADC0GTH[7:0] | ADC0 Greater-Than Data Word High-Order Bits. |

### SFR Definition 6.6. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit   | 7                                        | 6            | 5                                           | 4 | 2 | 2 | 1 | 0 |

|-------|------------------------------------------|--------------|---------------------------------------------|---|---|---|---|---|

| ы     | 1                                        | 0            | 5                                           | 4 | 3 | 2 | 1 | 0 |

| Nam   | e                                        | ADC0GTL[7:0] |                                             |   |   |   |   |   |

| Туре  | 9                                        | R/W          |                                             |   |   |   |   |   |

| Rese  | et 1                                     | 1            | 1                                           | 1 | 1 | 1 | 1 | 1 |

| SFR A | SFR Address = 0xC3; SFR Page = All Pages |              |                                             |   |   |   |   |   |

| Bit   | Name                                     |              | Function                                    |   |   |   |   |   |

| 7:0   | ADC0GTL[7:0                              | ] ADC0 GI    | ADC0 Greater-Than Data Word Low-Order Bits. |   |   |   |   |   |

## SFR Definition 8.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3    | 2       | 1    | 0       |

|-------|-------|--------|--------|--------|------|---------|------|---------|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0H | /P[1:0] | CP0H | YN[1:0] |

| Туре  | R/W   | R      | R/W    | R/W    | R/W  |         | R/   | W       |

| Reset | 0     | 0      | 0      | 0      | 0    | 0       | 0    | 0       |

### SFR Address = 0x9B; SFR Page = All Pages

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0                                                      |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## 12. Prefetch Engine

The C8051F380/1/2/3/4/5/6/7/C family of devices incorporate a 2-byte prefetch engine. Because the access time of the Flash memory is 40 ns, and the minimum instruction time is roughly 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from Flash memory two bytes at a time by the prefetch engine and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from Flash memory. It is recommended that the prefetch be used for optimal code execution timing.

**Note:** The prefetch engine can be disabled when the device is in suspend mode to save power.

### SFR Definition 12.1. PFE0CN: Prefetch Engine Control

| Bit   | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0     |

|-------|---|---|------|---|---|---|---|-------|

| Name  |   |   | PFEN |   |   |   |   | FLBWE |

| Туре  | R | R | R/W  | R | R | R | R | R/W   |

| Reset | 0 | 0 | 1    | 0 | 0 | 0 | 0 | 0     |

#### SFR Address = 0xAF; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                     |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b, Write = don't care.                                                                                                                                                                                                              |

| 5   | PFEN   | Prefetch Enable.This bit enables the prefetch engine.0: Prefetch engine is disabled.1: Prefetch engine is enabled.                                                                                                                           |

| 4:1 | Unused | Read = 0000b. Write = don't care.                                                                                                                                                                                                            |

| 0   | FLBWE  | <ul><li>Flash Block Write Enable.</li><li>This bit allows block writes to Flash memory from software.</li><li>0: Each byte of a software Flash write is written individually.</li><li>1: Flash bytes are written in groups of two.</li></ul> |

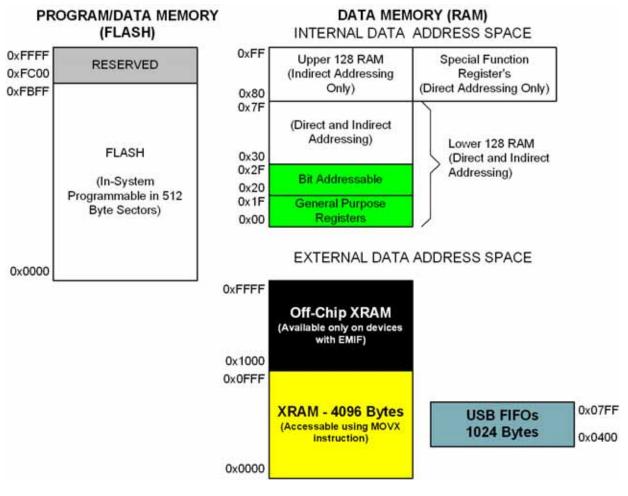

## **13. Memory Organization**

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The CIP-51 memory organization is shown in Figure 13.1 and Figure 13.2.

Figure 13.1. On-Chip Memory Map for 64 kB Devices (C8051F380/1/4/5)

## SFR Definition 16.5. EIE2: Extended Interrupt Enable 2

| Bit   | 7 | 6 | 5   | 4   | 3     | 2   | 1   | 0     |

|-------|---|---|-----|-----|-------|-----|-----|-------|

| Name  |   |   | ET5 | ET4 | ESMB1 |     | ES1 | EVBUS |

| Туре  | R | R | R/W | R/W | R/W   | R/W | R/W | R/W   |

| Reset | 0 | 0 | 0   | 0   | 0     | 0   | 0   | 0     |

### SFR Address = 0xE7; SFR Page = All Pages

| Bit | Name     | Function                                                                              |

|-----|----------|---------------------------------------------------------------------------------------|

| 7:6 | Unused   | Read = 00b, Write = Don't Care.                                                       |

| 5   | ET5      | Enable Timer 5 Interrupt.                                                             |

|     |          | This bit sets the masking of the Timer 5 interrupt.<br>0: Disable Timer 5 interrupts. |

|     |          | 1: Enable interrupt requests generated by the TF5L or TF5H flags.                     |

| 4   | ET4      | Enable Timer 4 Interrupt.                                                             |

|     |          | This bit sets the masking of the Timer 4 interrupt.                                   |

|     |          | 0: Disable Timer 4interrupts.                                                         |

|     |          | 1: Enable interrupt requests generated by the TF4L or TF4H flags.                     |

| 3   | ESMB1    | Enable SMBus1 Interrupt.                                                              |

|     |          | This bit sets the masking of the SMB1 interrupt.                                      |

|     |          | 0: Disable all SMB1 interrupts.                                                       |

|     |          | 1: Enable interrupt requests generated by SMB1.                                       |

| 2   | Reserved | Must Write 0b.                                                                        |

| 1   | ES1      | Enable UART1 Interrupt.                                                               |

|     |          | This bit sets the masking of the UART1 interrupt.                                     |

|     |          | 0: Disable UART1 interrupt.                                                           |

|     |          | 1: Enable UART1 interrupt.                                                            |

| 0   | EVBUS    | Enable VBUS Level Interrupt.                                                          |

|     |          | This bit sets the masking of the VBUS interrupt.                                      |

|     |          | 0: Disable all VBUS interrupts.                                                       |

|     |          | 1: Enable interrupt requests generated by VBUS level sense.                           |

## SFR Definition 19.3. OSCICN: Internal H-F Oscillator Control

| Bit   | 7      | 6     | 5       | 4 | 3 | 2 | 1         | 0 |

|-------|--------|-------|---------|---|---|---|-----------|---|

| Name  | IOSCEN | IFRDY | SUSPEND |   |   |   | IFCN[1:0] |   |

| Туре  | R/W    | R     | R/W     | R | R | R | R/W       |   |

| Reset | 1      | 1     | 0       | 0 | 0 | 0 | 0         | 0 |

### SFR Address = 0xB2; SFR Page = All Pages

| Bit | Name      | Function                                                                                                                                                                            |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IOSCEN    | Internal H-F Oscillator Enable Bit.                                                                                                                                                 |

|     |           | 0: Internal H-F Oscillator Disabled.                                                                                                                                                |

|     |           | 1: Internal H-F Oscillator Enabled.                                                                                                                                                 |

| 6   | IFRDY     | Internal H-F Oscillator Frequency Ready Flag.                                                                                                                                       |

|     |           | 0: Internal H-F Oscillator is not running at programmed frequency.                                                                                                                  |

|     |           | 1: Internal H-F Oscillator is running at programmed frequency.                                                                                                                      |

| 5   | SUSPEND   | Internal Oscillator Suspend Enable Bit.                                                                                                                                             |

|     |           | Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The inter-<br>nal oscillator resumes operation when one of the SUSPEND mode awakening<br>events occurs. |

| 4:2 | Unused    | Read = 000b; Write = don't care                                                                                                                                                     |

| 1:0 | IFCN[1:0] | Internal H-F Oscillator Frequency Divider Control Bits.                                                                                                                             |

|     |           | The Internal H-F Oscillator is divided by the IFCN bit setting after a divide-by-4 stage.                                                                                           |

|     |           | 00: SYSCLK can be derived from Internal H-F Oscillator divided by 8 (1.5 MHz).                                                                                                      |

|     |           | 01: SYSCLK can be derived from Internal H-F Oscillator divided by 4 (3 MHz).                                                                                                        |

|     |           | 10: SYSCLK can be derived from Internal H-F Oscillator divided by 2 (6 MHz).11: SYSCLK can be derived from Internal H-F Oscillator divided by 1 (12 MHz).                           |

### USB Register Definition 21.4. INDEX: USB0 Endpoint Index

| Bit   | 7 | 6 | 5 | 4 | 3          | 2 | 1 | 0 |  |

|-------|---|---|---|---|------------|---|---|---|--|

| Name  |   |   |   |   | EPSEL[3:0] |   |   |   |  |

| Туре  | R | R | R | R | R/W        |   |   |   |  |

| Reset | 0 | 0 | 0 | 0 | 0          | 0 | 0 | 0 |  |

#### USB Register Address = 0x0E

| Bit | Name       | Function                                                                                                                                                                                       |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused     | Read = 0000b. Write = don't care.                                                                                                                                                              |

| 3:0 | EPSEL[3:0] | Endpoint Select Bits.                                                                                                                                                                          |

|     |            | These bits select which endpoint is targeted when indexed USB0 registers are accessed.<br>0000: Endpoint 0<br>0001: Endpoint 1<br>0010: Endpoint 2<br>0011: Endpoint 3<br>0100-1111: Reserved. |

### 21.4. USB Clock Configuration

USB0 is capable of communication as a Full or Low Speed USB function. Communication speed is selected via the SPEED bit in SFR USB0XCN. When operating as a Low Speed function, the USB0 clock must be 6 MHz. When operating as a Full Speed function, the USB0 clock must be 48 MHz. Clock options are described in Section "19. Oscillators and Clock Selection" on page 142. The USB0 clock is selected via SFR CLKSEL (see SFR Definition 19.1).

Clock Recovery circuitry uses the incoming USB data stream to adjust the internal oscillator; this allows the internal oscillator to meet the requirements for USB clock tolerance. Clock Recovery should be used in the following configurations:

| Communication Speed | USB Clock               |

|---------------------|-------------------------|

| Full Speed          | Internal Oscillator     |

| Low Speed           | Internal Oscillator / 8 |

When operating USB0 as a Low Speed function with Clock Recovery, software must write 1 to the CRLOW bit to enable Low Speed Clock Recovery. Clock Recovery is typically not necessary in Low Speed mode.

Single Step Mode can be used to help the Clock Recovery circuitry to lock when high noise levels are present on the USB network. This mode is not required (or recommended) in typical USB environments.

## USB Register Definition 21.5. CLKREC: Clock Recovery Control

| Bit   | 7   | 6      | 5     | 4   | 3 | 2 | 1 | 0 |

|-------|-----|--------|-------|-----|---|---|---|---|

| Name  | CRE | CRSSEN | CRLOW |     |   |   |   |   |

| Туре  | R/W | R/W    | R/W   | R/W |   |   |   |   |

| Reset | 0   | 0      | 0     | 0   | 1 | 1 | 1 | 1 |

USB Register Address = 0x0F

| Bit | Name     | Function                                                                                                                                                                                                            |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CRE      | Clock Recovery Enable Bit.<br>This bit enables/disables the USB clock recovery feature.<br>0: Clock recovery disabled.<br>1: Clock recovery enabled.                                                                |

| 6   | CRSSEN   | <ul> <li>Clock Recovery Single Step.</li> <li>This bit forces the oscillator calibration into single-step mode during clock recovery.</li> <li>0: Normal calibration mode.</li> <li>1: Single step mode.</li> </ul> |

| 5   | CRLOW    | Low Speed Clock Recovery Mode.<br>This bit must be set to 1 if clock recovery is used when operating as a Low Speed USB device.<br>0: Full Speed Mode.<br>1: Low Speed Mode.                                        |

| 4:0 | Reserved | Must Write = 01111b.                                                                                                                                                                                                |

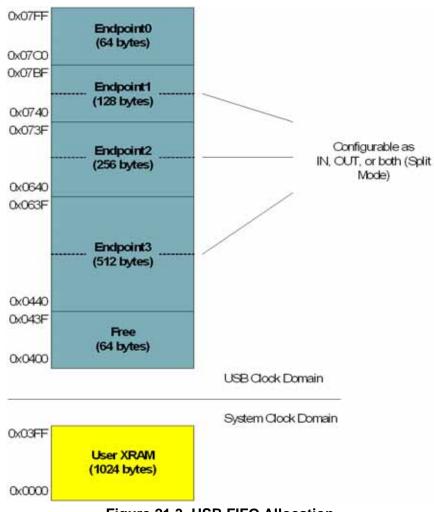

## 21.5. FIFO Management

1024 bytes of on-chip XRAM are used as FIFO space for USB0. This FIFO space is split between Endpoints0-3 as shown in Figure 21.3. FIFO space allocated for Endpoints1-3 is configurable as IN, OUT, or both (Split Mode: half IN, half OUT).

Figure 21.3. USB FIFO Allocation

### 21.5.1. FIFO Split Mode

The FIFO space for Endpoints1-3 can be split such that the upper half of the FIFO space is used by the IN endpoint, and the lower half is used by the OUT endpoint. For example: if the Endpoint3 FIFO is configured for Split Mode, the upper 256 bytes (0x0540 to 0x063F) are used by Endpoint3 IN and the lower 256 bytes (0x0440 to 0x053F) are used by Endpoint3 OUT.

If an endpoint FIFO is not configured for Split Mode, that endpoint IN/OUT pair's FIFOs are combined to form a single IN *or* OUT FIFO. In this case only one direction of the endpoint IN/OUT pair may be used at a time. The endpoint direction (IN/OUT) is determined by the DIRSEL bit in the corresponding endpoint's EINCSRH register (see SFR Definition 21.13).

## SFR Definition 22.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7      | 6    | 5     | 4        | 3       | 2       | 1           | 0 |

|-------|--------|------|-------|----------|---------|---------|-------------|---|

| Name  | ENSMB0 | INH0 | BUSY0 | EXTHOLD0 | SMB0TOE | SMB0FTE | SMB0CS[1:0] |   |

| Туре  | R/W    | R/W  | R     | R/W      | R/W     | R/W     | R/W         |   |

| Reset | 0      | 0    | 0     | 0        | 0       | 0       | 0           | 0 |

### SFR Address = 0xC1; SFR Page = 0

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB0      | SMBus0 Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |             | This bit enables the SMBus0 interface when set to 1. When enabled, the interface constantly monitors the SDA0 and SCL0 pins.                                                                                                                                                                                                                                                                                                                    |

| 6   | INH0        | SMBus0 Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |             | When this bit is set to logic 1, the SMBus0 does not generate an interrupt when slave events occur. This effectively removes the SMBus0 slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                            |

| 5   | BUSY0       | SMBus0 Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |             | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                          |

| 4   | EXTHOLD0    | SMBus0 Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |             | <ul><li>This bit controls the SDA0 setup and hold times according to Table 22.2.</li><li>0: SDA0 Extended Setup and Hold Times disabled.</li><li>1: SDA0 Extended Setup and Hold Times enabled.</li></ul>                                                                                                                                                                                                                                       |

| 3   | SMB0TOE     | SMBus0 SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   |             | This bit enables SCL low timeout detection. If set to logic 1, the SMBus0 forces<br>Timer 3 to reload while SCL0 is high and allows Timer 3 to count when SCL0 goes<br>low. If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in<br>reload while SCL0 is high. Timer 3 should be programmed to generate interrupts at<br>25 ms, and the Timer 3 interrupt service routine should reset SMBus0 communica-<br>tion. |

| 2   | SMB0FTE     | SMBus0 Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |             | When this bit is set to logic 1, the bus will be considered free if SCL0 and SDA0 remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                                      |

| 1:0 | SMB0CS[1:0] | SMBus0 Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |             | These two bits select the SMBus0 clock source, which is used to generate the<br>SMBus0 bit rate. The selected device should be configured according to<br>Equation 22.1.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow                                                                                                                                                     |

## SFR Definition 22.2. SMB1CF: SMBus Clock/Configuration

| Bit   | 7      | 6    | 5     | 4        | 3       | 2       | 1           | 0 |

|-------|--------|------|-------|----------|---------|---------|-------------|---|

| Name  | ENSMB1 | INH1 | BUSY1 | EXTHOLD1 | SMB1TOE | SMB1FTE | SMB1CS[1:0] |   |

| Туре  | R/W    | R/W  | R     | R/W      | R/W     | R/W     | R/W         |   |

| Reset | 0      | 0    | 0     | 0        | 0       | 0       | 0           | 0 |

## SFR Address = 0xC1; SFR Page = F

| SFR A | Address = 0xC1               | ; SFR Page = F                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|-------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Bit   | Name                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| 7     | ENSMB1                       | <b>SMBus1 Enable.</b><br>This bit enables the SMBus1 interface when set to 1. When enabled, the interface constantly monitors the SDA1 and SCL1 pins.                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 6     | INH1                         | SMBus1 Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|       |                              | When this bit is set to logic 1, the SMBus1 does not generate an interrupt when slave events occur. This effectively removes the SMBus1 slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| 5     | BUSY1                        | SMBus1 Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|       |                              | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| 4     | EXTHOLD1                     | SMBus1 Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|       |                              | This bit controls the SDA1 setup and hold times according to Table 22.2.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|       |                              | 0: SDA1 Extended Setup and Hold Times disabled.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|       |                              | 1: SDA1 Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| 3     | SMB1TOE                      | SMBus1 SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|       |                              | This bit enables SCL low timeout detection. If set to logic 1, the SMBus1 forces Timer 4 to reload while SCL1 is high and allows Timer 4 to count when SCL1 goes low. If Timer 4 is configured to Split Mode, only the High Byte of the timer is held in reload while SCL1 is high. Timer 4 should be programmed to generate interrupts at 25 ms, and the Timer 4 interrupt service routine should reset SMBus1 communication. |  |  |  |  |  |  |  |  |

| 2     | SMB1FTE                      | SMBus1 Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|       |                              | When this bit is set to logic 1, the bus will be considered free if SCL1 and SDA1 remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| 1:0   | SMB1CS[1:0]                  | SMBus1 Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|       |                              | These two bits select the SMBus1 clock source, which is used to generate the SMBus1 bit rate. The selected device should be configured according to Equation 22.1.                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|       |                              | 00: Timer 0 Overflow                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|       |                              | 01: Timer 5 Overflow                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|       |                              | 10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|       | TT: Timer 2 Low Byte Overnow |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

Table 22.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (Continued)

| Mode                       | Values Read      |       |         |                              |                             |                             | Values to<br>Write |     |     | Status<br>Expected     |

|----------------------------|------------------|-------|---------|------------------------------|-----------------------------|-----------------------------|--------------------|-----|-----|------------------------|

|                            | Status<br>Vector | ACKRQ | ARBLOST | ACK                          | Current SMbus State         | Typical Response Options    | STA                | STO | ACK | Next Sta<br>Vector Exp |

| <b>Bus Error Condition</b> | 0010             | 0     | 1       | x                            | is a serie at a d OTA DT    | Abort failed transfer.      | 0                  | 0   | Х   | —                      |

|                            | 0010             |       |         |                              |                             | Reschedule failed transfer. | 1                  | 0   | Х   | 1110                   |

|                            | 0001             | 0     | 1       | x                            |                             | Abort failed transfer.      | 0                  | 0   | Х   | —                      |

|                            | 0001             |       |         |                              |                             | Reschedule failed transfer. | 1                  | 0   | Х   | 1110                   |

|                            | 0000             | 1     | 1       | X tion a data buta as moster | Abort failed transfer.      | 0                           | 0                  | 0   | —   |                        |

|                            | 0000             |       |         |                              | ting a data byte as master. | Reschedule failed transfer. | 1                  | 0   | 0   | 1110                   |

### Table 22.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1)

| Mode               | Values Read |        |       |         | d   |                                                                    |                                                                                                                        | Values to<br>Write |     |     | Status<br>Expected           |

|--------------------|-------------|--------|-------|---------|-----|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|------------------------------|

|                    | Status      | Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                                | Typical Response Options                                                                                               | STA                | STO | ACK | Next Status<br>Vector Expect |

| Master Transmitter | 11'         | 10     | 0     | 0       | x   | A master START was gener-<br>ated.                                 | Load slave address + R/W into SMB0DAT.                                                                                 | 0                  | 0   | Х   | 1100                         |

|                    |             |        |       |         |     | was transmitted; NACK                                              | Set STA to restart transfer.                                                                                           | 1                  | 0   | Х   | 1110                         |

|                    | 1100        |        | 0     | 0       | 0   |                                                                    | Abort transfer.                                                                                                        | 0                  | 1   | Х   | —                            |

|                    |             |        |       |         |     | A master data or address byte<br>was transmitted; ACK<br>received. | Load next data byte into SMB0-<br>DAT.                                                                                 | 0                  | 0   | Х   | 1100                         |

|                    |             |        |       |         |     |                                                                    | End transfer with STOP.                                                                                                | 0                  | 1   | Х   | —                            |

|                    |             | 100    | 0     | 0       | 1   |                                                                    | End transfer with STOP and start another transfer.                                                                     | 1                  | 1   | Х   | —                            |

|                    |             |        | Ũ     | ľ       |     |                                                                    | Send repeated START.                                                                                                   | 1                  | 0   | Х   | 1110                         |

|                    |             |        |       |         |     |                                                                    | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT). Set ACK for initial<br>data byte. | 0                  | 0   | 1   | 1000                         |

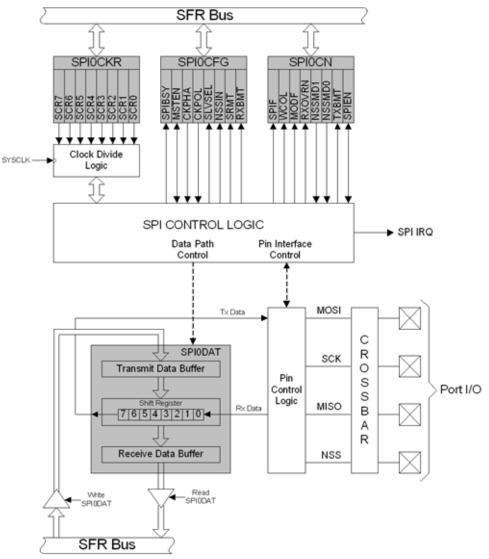

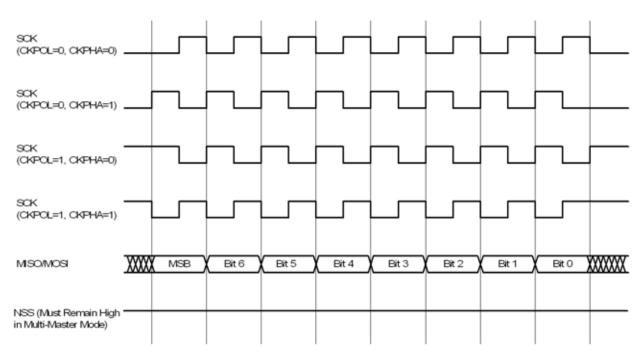

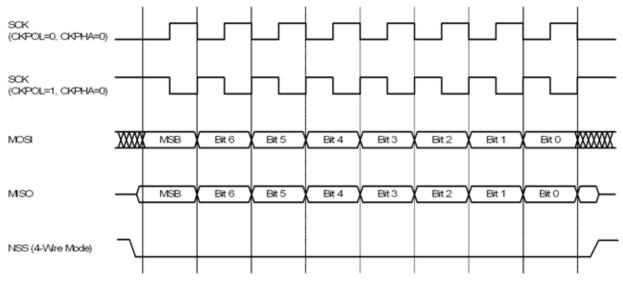

## 25. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 25.10. SPI Slave Timing (CKPHA = 0)

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 26.7. Timer 2 Capture Mode (T2SPLIT = 0)