# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48 MIPS                                                        |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART, USB                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | A/D 32x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f382-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 3.6. | <b>QFN-32</b> | Package  | Dimensions   |

|------------|---------------|----------|--------------|

|            |               | I uonugo | Difficitorio |

| Dimension | Min      | Тур      | Max  |   | Dimension | Min  | Тур  | Max  |

|-----------|----------|----------|------|---|-----------|------|------|------|

| A         | 0.80     | 0.85     | 0.90 |   | E2        | 3.20 | 3.30 | 3.40 |

| A1        | 0.00     | 0.02     | 0.05 | ĺ | L         | 0.35 | 0.40 | 0.45 |

| b         | 0.18     | 0.25     | 0.30 |   | aaa       | _    | _    | 0.10 |

| D         |          | 5.00 BSC |      |   | bbb       | _    |      | 0.10 |

| D2        | 3.20     | 3.30     | 3.40 |   | ddd       | _    |      | 0.05 |

| е         | 0.50 BSC |          |      |   | eee       | _    | _    | 0.08 |

| E         | 5.00 BSC |          |      |   |           |      |      |      |

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, and L which are toleranced per supplier designation.

- **4.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## SFR Definition 8.3. CPT1CN: Comparator1 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP1EN | CP1OUT | CP1RIF | CP1FIF | CP1HYP[1:0] |   | CP1HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

#### SFR Address = 0x9A; SFR Page = All Pages

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP1EN       | Comparator1 Enable Bit.                                                       |

|     |             | 0: Comparator1 Disabled.                                                      |

|     |             | 1: Comparator1 Enabled.                                                       |

| 6   | CP1OUT      | Comparator1 Output State Flag.                                                |

|     |             | 0: Voltage on CP1+ < CP1                                                      |

|     |             | 1: Voltage on CP1+ > CP1                                                      |

| 5   | CP1RIF      | Comparator1 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator1 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator1 Rising Edge has occurred.                                      |

| 4   | CP1FIF      | Comparator1 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator1 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator1 Falling-Edge has occurred.                                     |

| 3:2 | CP1HYP[1:0] | Comparator1 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP1HYN[1:0] | Comparator1 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

## SFR Definition 11.6. PSW: Program Status Word

| Bit   | 7          | 6                                    | 5                                                                                                           | 4              | 3               | 2                              | 1            | 0             |  |  |

|-------|------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------|-----------------|--------------------------------|--------------|---------------|--|--|

| Nam   | e CY       | AC                                   | F0                                                                                                          | RS             | [1:0]           | OV                             | F1           | PARITY        |  |  |

| Туре  | R/W        | R/W                                  | R/W                                                                                                         | R              | /W              | R/W                            | R/W          | R             |  |  |

| Rese  | et 0       | 0                                    | 0                                                                                                           | 0              | 0               | 0                              | 0            | 0             |  |  |

| SFR A | ddress = 0 | (D0; SFR Page                        | e = All Pages                                                                                               | ; Bit-Addres   | sable           | 4                              | 1            |               |  |  |

| Bit   | Name       |                                      |                                                                                                             |                | Function        |                                |              |               |  |  |

| 7     | CY         | Carry Flag.                          | rry Flag.                                                                                                   |                |                 |                                |              |               |  |  |

|       |            | This bit is set row (subtraction     |                                                                                                             |                |                 |                                |              | n) or a bor-  |  |  |

| 6     | AC         | Auxiliary Car                        | ry Flag.                                                                                                    |                |                 |                                |              |               |  |  |

|       |            | This bit is set                      |                                                                                                             |                |                 |                                |              |               |  |  |

|       |            | `                                    | prrow from (subtraction) the high order nibble. It is cleared to logic 0 by all other arithetic operations. |                |                 |                                |              |               |  |  |

| 5     | F0         | User Flag 0.                         |                                                                                                             |                |                 |                                |              |               |  |  |

|       |            | This is a bit-ad                     | ddressable,                                                                                                 | general purp   | ose flag for    | use under so                   | oftware cont | rol.          |  |  |

| 4:3   | RS[1:0]    | Register Ban                         | k Select.                                                                                                   |                |                 |                                |              |               |  |  |

|       |            | These bits sel                       |                                                                                                             | -              | s used durir    | ng register ac                 | cesses.      |               |  |  |

|       |            | 00: Bank 0, Ao<br>01: Bank 1, Ao     |                                                                                                             |                |                 |                                |              |               |  |  |

|       |            | 10: Bank 2, A                        |                                                                                                             |                |                 |                                |              |               |  |  |

|       |            | 11: Bank 3, Ac                       | dresses 0x                                                                                                  | 18-0x1F        |                 |                                |              |               |  |  |

| 2     | OV         | <b>Overflow Flag</b>                 | g.                                                                                                          |                |                 |                                |              |               |  |  |

|       |            | This bit is set                      |                                                                                                             | -              |                 |                                |              |               |  |  |

|       |            |                                      |                                                                                                             |                |                 | n-change ove<br>greater than 2 |              |               |  |  |

|       |            |                                      |                                                                                                             | es a divide-by | •               | •                              | 00).         |               |  |  |

|       |            | The OV bit is other cases.           | cleared to 0                                                                                                | by the ADD,    | ADDC, SU        | BB, MUL, and                   | d DIV instru | ctions in all |  |  |

| 1     | F1         | User Flag 1.                         |                                                                                                             |                |                 |                                |              |               |  |  |

|       |            | This is a bit-ad                     | ddressable,                                                                                                 | general purp   | ose flag for    | use under so                   | oftware cont | rol.          |  |  |

| 0     | PARITY     | Parity Flag.                         |                                                                                                             |                |                 |                                |              |               |  |  |

|       |            | This bit is set t<br>if the sum is e | -                                                                                                           | ne sum of the  | e eight bits ir | n the accumu                   | lator is odd | and cleared   |  |  |

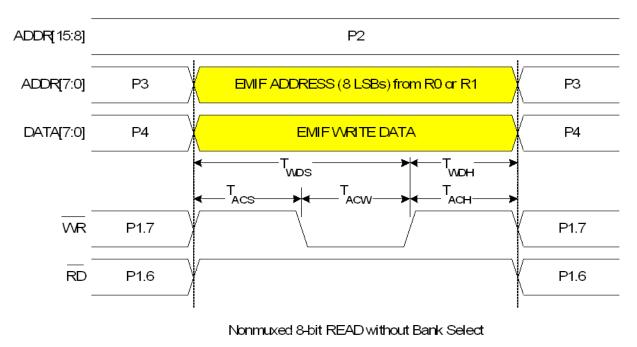

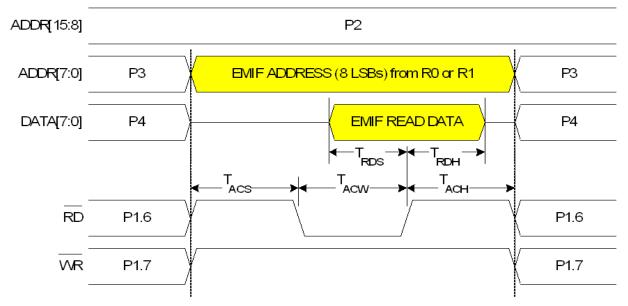

## 14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111

Nonmuxed 8-bit WRITE without Bank Select

| Address | Page   | 0(8)   | 1(9)     | 2(A)     | 3(B)            | 4(C)             | 5(D)     | 6(E)     | 7(F)           |

|---------|--------|--------|----------|----------|-----------------|------------------|----------|----------|----------------|

| F8      |        | SPI0CN | PCA0L    | PCA0H    | PCA0CPL0        | PCA0CPH0         | PCA0CPL4 | PCA0CPH4 | VDM0CN         |

| F0      |        | В      | P0MDIN   | P1MDIN   | P2MDIN          | P3MDIN           | P4MDIN   | EIP1     | EIP2           |

| E8      |        | ADC0CN | PCA0CPL1 | PCA0CPH1 | PCA0CPL2        | PCA0CPH2         | PCA0CPL3 | PCA0CPH3 | RSTSRC         |

| E0      | 0<br>F | ACC    | XBR0     | XBR1     | XBR2            | IT01CF<br>CKCON1 | SMOD1    | EIE1     | EIE2           |

| D8      |        | PCA0CN | PCA0MD   | PCA0CPM0 | PCA0CPM1        | PCA0CPM2         | PCA0CPM3 | PCA0CPM4 | P3SKIP         |

| D0      |        | PSW    | REF0CN   | SCON1    | SBUF1           | P0SKIP           | P1SKIP   | P2SKIP   | <b>USB0XCN</b> |

| C8      | 0      | TMR2CN | REG01CN  | TMR2RLL  | TMR2RLH         | TMR2L            | TMR2H    | SMB0ADM  | SMB0ADR        |

|         | F      | TMR5CN | REGUICIN | TMR5RLL  | TMR5RLH         | TMR5L            | TMR5H    | SMB1ADM  | SMB1ADR        |

| CO      | 0 S    | SMB0CN | SMB0CF   | SMB0DAT  | SMB0DAT ADC0GTL | ADC0GTH          | ADC0LTL  | ADC0LTH  | P4             |

|         | F      | SMB1CN | SMB1CF   | SMB1DAT  | ADCOUTL         | ADCOGIII         | ADCOLIL  | ADCOLITI | Γ4             |

| B8      | 0      | IP     | CLKMUL   | AMX0N    | AMX0P           | ADC0CF           | ADC0L    | ADC0H    | SFRPAGE        |

| Бо      | F      |        | SMBTC    |          |                 |                  | ADCOL    |          |                |

| B0      |        | P3     | OSCXCN   | OSCICN   | OSCICL          | SBRLL1           | SBRLH1   | FLSCL    | FLKEY          |

| A8      |        | IE     | CLKSEL   | EMIOCN   |                 | SBCON1           |          | P4MDOUT  | PFE0CN         |

| A0      |        | P2     | SPI0CFG  | SPI0CKR  | SPI0DAT         | POMDOUT          | P1MDOUT  | P2MDOUT  | P3MDOUT        |

| 98      |        | SCON0  | SBUF0    | CPT1CN   | CPT0CN          | CPT1MD           | CPT0MD   | CPT1MX   | CPT0MX         |

| 90      | 0      | P1     | TMR3CN   | TMR3RLL  | TMR3RLH         | TMR3L            | TMR3H    | USB0ADR  | USB0DAT        |

| 90      | F      |        | TMR4CN   | TMR4RLL  | TMR4RLH         | TMR4L            | TMR4H    | USBUADR  | USBUDAI        |

| 88      |        | TCON   | TMOD     | TL0      | TL1             | TH0              | TH1      | CKCON    | PSCTL          |

| 80      |        | P0     | SP       | DPL      | DPH             | EMI0TC           | EMI0CF   | OSCLCN   | PCON           |

|         |        | 0(8)   | 1(9)     | 2(A)     | 3(B)            | 4(C)             | 5(D)     | 6(E)     | 7(F)           |

| Note    |        |        |          |          | -               | -                |          |          |                |

#### Table 15.1. Special Function Register (SFR) Memory Map

Notes:

1. SFR Addresses ending in 0x0 or 0x8 are bit-addressable locations and can be used with bitwise instructions.

2. Unless indicated otherwise, SFRs are available on both page 0 and page F.

## SFR Definition 17.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|---------|--------|--------|--------|--------|--------|--------|

| Name  | VDMEN  | VDDSTAT |        |        |        |        |        |        |

| Туре  | R/W    | R       | R      | R      | R      | R      | R      | R      |

| Reset | Varies | Varies  | Varies | Varies | Varies | Varies | Varies | Varies |

#### SFR Address = 0xFF; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 17.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. See Table 5.4 for the minimum V <sub>DD</sub> Monitor turn-on time.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).<br>0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.<br>1: $V_{DD}$ is above the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5:0 | Unused  | Read = 000000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 17.3. External Reset

The external  $\overline{\text{RST}}$  pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the  $\overline{\text{RST}}$  pin generates a reset; an external pullup and/or decoupling of the  $\overline{\text{RST}}$  pin may be necessary to avoid erroneous noise-induced resets. See Table 5.4 for complete  $\overline{\text{RST}}$  pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 17.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the MCD time-out, a reset will be generated. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

### 17.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

## 17.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "27.4. Watchdog Timer Mode" on page 308; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

## 17.7. Flash Error Reset

If a Flash program read, write, or erase operation targets an illegal address, a system reset is generated. This may occur due to any of the following:

- Programming hardware attempts to write or erase a Flash location which is above the user code space address limit.

- A Flash read from firmware is attempted above user code space. This occurs when a MOVC operation is attempted above the user code space address limit.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the user code space address limit.

- A Flash read, write, or erase attempt is restricted due to a Flash security setting.

- A Flash write or erase is attempted when the V<sub>DD</sub> monitor is not enabled.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 17.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 17.9. USB Reset

Writing 1 to the USBRSF bit in register RSTSRC selects USB0 as a reset source. With USB0 selected as a reset source, a system reset will be generated when either of the following occur:

- 1. RESET signaling is detected on the USB network. The USB Function Controller (USB0) must be enabled for RESET signaling to be detected. See Section "21. Universal Serial Bus Controller (USB0)" on page 172 for information on the USB Function Controller.

- 2. A falling or rising voltage on the VBUS pin.

The USBRSF bit will read 1 following a USB reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

## SFR Definition 20.12. P2: Port 2

| Bit   | 7 | 6       | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|---------|---|---|---|---|---|---|--|--|

| Name  |   | P2[7:0] |   |   |   |   |   |   |  |  |

| Туре  |   | R/W     |   |   |   |   |   |   |  |  |

| Reset | 1 | 1       | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

SFR Address = 0xA0; SFR Page = All Pages; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P2[7:0] | <b>Port 2 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P2.n Port pin is logic<br>LOW.<br>1: P2.n Port pin is logic<br>HIGH. |

## SFR Definition 20.13. P2MDIN: Port 2 Input Mode

| Bit   | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|---------------|---|---|---|---|---|---|--|--|

| Name  |   | P2MDIN[7:0]   |   |   |   |   |   |   |  |  |

| Туре  |   | R/W           |   |   |   |   |   |   |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |

#### SFR Address = 0xF3; SFR Page = All Pages

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDIN[7:0] | Analog Configuration Bits for P2.7–P2.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P2.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P2.n pin is not configured for analog mode.                                                |

### USB Register Definition 21.4. INDEX: USB0 Endpoint Index

| Bit   | 7 | 6 | 5 | 4 | 3          | 2 | 1 | 0 |

|-------|---|---|---|---|------------|---|---|---|

| Name  |   |   |   |   | EPSEL[3:0] |   |   |   |

| Туре  | R | R | R | R | R/W        |   |   |   |

| Reset | 0 | 0 | 0 | 0 | 0          | 0 | 0 | 0 |

#### USB Register Address = 0x0E

| Bit | Name       | Function                                                                                                                                                                                       |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused     | Read = 0000b. Write = don't care.                                                                                                                                                              |

| 3:0 | EPSEL[3:0] | Endpoint Select Bits.                                                                                                                                                                          |

|     |            | These bits select which endpoint is targeted when indexed USB0 registers are accessed.<br>0000: Endpoint 0<br>0001: Endpoint 1<br>0010: Endpoint 2<br>0011: Endpoint 3<br>0100-1111: Reserved. |

### 21.4. USB Clock Configuration

USB0 is capable of communication as a Full or Low Speed USB function. Communication speed is selected via the SPEED bit in SFR USB0XCN. When operating as a Low Speed function, the USB0 clock must be 6 MHz. When operating as a Full Speed function, the USB0 clock must be 48 MHz. Clock options are described in Section "19. Oscillators and Clock Selection" on page 142. The USB0 clock is selected via SFR CLKSEL (see SFR Definition 19.1).

Clock Recovery circuitry uses the incoming USB data stream to adjust the internal oscillator; this allows the internal oscillator to meet the requirements for USB clock tolerance. Clock Recovery should be used in the following configurations:

| Communication Speed | USB Clock               |  |  |  |

|---------------------|-------------------------|--|--|--|

| Full Speed          | Internal Oscillator     |  |  |  |

| Low Speed           | Internal Oscillator / 8 |  |  |  |

When operating USB0 as a Low Speed function with Clock Recovery, software must write 1 to the CRLOW bit to enable Low Speed Clock Recovery. Clock Recovery is typically not necessary in Low Speed mode.

Single Step Mode can be used to help the Clock Recovery circuitry to lock when high noise levels are present on the USB network. This mode is not required (or recommended) in typical USB environments.

## USB Register Definition 21.13. CMINT: USB0 Common Interrupt

| Bit   | 7 | 6 | 5 | 4 | 3   | 2      | 1      | 0      |

|-------|---|---|---|---|-----|--------|--------|--------|

| Name  |   |   |   |   | SOF | RSTINT | RSUINT | SUSINT |

| Туре  | R | R | R | R | R   | R      | R      | R      |

| Reset | 0 | 0 | 0 | 0 | 0   | 0      | 0      | 0      |

#### USB Register Address = 0x06

| Bit | Name   | Function                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused | Read = 0000b. Write = don't care.                                                                                                                                                                       |

| 3   | SOF    | Start of Frame Interrupt Flag.                                                                                                                                                                          |

|     |        | Set by hardware when a SOF token is received. This interrupt event is synthesized by hardware: an interrupt will be generated when hardware expects to receive a SOF                                    |

|     |        | event, even if the actual SOF signal is missed or corrupted.                                                                                                                                            |

|     |        | This bit is cleared when software reads the CMINT register.                                                                                                                                             |

|     |        | 0: SOF interrupt inactive.                                                                                                                                                                              |

|     |        | 1: SOF interrupt active.                                                                                                                                                                                |

| 2   | RSTINT | Reset Interrupt-Pending Flag.                                                                                                                                                                           |

|     |        | Set by hardware when Reset signaling is detected on the bus.                                                                                                                                            |

|     |        | This bit is cleared when software reads the CMINT register.<br>0: Reset interrupt inactive.                                                                                                             |

|     |        | 1: Reset interrupt active.                                                                                                                                                                              |

| 1   | RSUINT | Resume Interrupt-Pending Flag.                                                                                                                                                                          |

|     |        | Set by hardware when Resume signaling is detected on the bus while USB0 is in suspend mode.                                                                                                             |

|     |        | This bit is cleared when software reads the CMINT register.                                                                                                                                             |

|     |        | 0: Resume interrupt inactive.                                                                                                                                                                           |

|     |        | 1: Resume interrupt active.                                                                                                                                                                             |

| 0   | SUSINT | Suspend Interrupt-Pending Flag.                                                                                                                                                                         |

|     |        | When Suspend detection is enabled (bit SUSEN in register POWER), this bit is set by hardware when Suspend signaling is detected on the bus. This bit is cleared when software reads the CMINT register. |

|     |        | 0: Suspend interrupt inactive.                                                                                                                                                                          |

|     |        | 1: Suspend interrupt active.                                                                                                                                                                            |

# USB Register Definition 21.23. EOUTCSRH: USB0 OUT Endpoint Control High Byte

| Bit   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------|-----|---|---|---|---|---|---|

| Name  | DBOEN | ISO |   |   |   |   |   |   |

| Туре  | R/W   | R/W | R | R | R | R | R | R |

| Reset | 0     | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

#### USB Register Address = 0x15

| Bit | Name   | Function                                                                                                                                                                              |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DBOEN  | Double-buffer Enable.                                                                                                                                                                 |

|     |        | <ul><li>0: Double-buffering disabled for the selected OUT endpoint.</li><li>1: Double-buffering enabled for the selected OUT endpoint.</li></ul>                                      |

| 6   | ISO    | Isochronous Transfer Enable.                                                                                                                                                          |

|     |        | This bit enables/disables isochronous transfers on the current endpoint.<br>0: Endpoint configured for bulk/interrupt transfers.<br>1: Endpoint configured for isochronous transfers. |

| 5:0 | Unused | Read = 000000b. Write = don't care.                                                                                                                                                   |

## USB Register Definition 21.24. EOUTCNTL: USB0 OUT Endpoint Count Low

| Bit                         | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------------|-----------|---|---|---|---|---|---|---|

| Name                        | EOCL[7:0] |   |   |   |   |   |   |   |

| Туре                        |           |   |   | F | २ |   |   |   |

| Reset                       | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| USB Register Address = 0x16 |           |   |   |   |   |   |   |   |

| Bit | Name      | Function                                                                                                                                                                   |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | EOCL[7:0] | OUT Endpoint Count Low Byte.                                                                                                                                               |

|     |           | EOCL holds the lower 8-bits of the 10-bit number of data bytes in the last received packet in the current OUT endpoint FIFO. This number is only valid while $OPRDY = 1$ . |

| SMBnCS1 | SMBnCS0 | SMBus0 Clock Source        | SMBus1 Clock Source        |  |  |

|---------|---------|----------------------------|----------------------------|--|--|

| 0       | 0       | Timer 0 Overflow           | Timer 0 Overflow           |  |  |

| 0       | 1       | Timer 1 Overflow           | Timer 5 Overflow           |  |  |

| 1       | 0       | Timer 2 High Byte Overflow | Timer 2 High Byte Overflow |  |  |

| 1       | 1       | Timer 2 Low Byte Overflow  | Timer 2 Low Byte Overflow  |  |  |

Table 22.1. SMBus Clock Source Selection

The SMBnCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 22.1.The selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus0 and SMBus1 clock rates simultaneously. Timer configuration is covered in Section "26. Timers" on page 263.

$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$

#### Equation 22.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 22.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 22.2.

BitRate =

$$\frac{f_{ClockSourceOverflow}}{3}$$

#### Equation 22.2. Typical SMBus Bit Rate

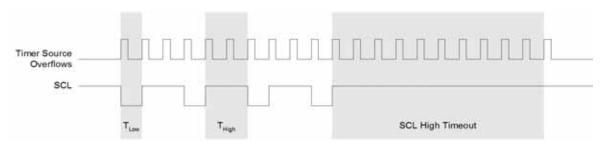

Figure 22.4 shows the typical SCL generation described by Equation 22.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 22.1.

Figure 22.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 22.2 shows the minimum setup.

## 22.5. SMBus Transfer Modes

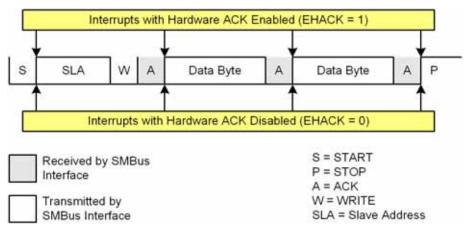

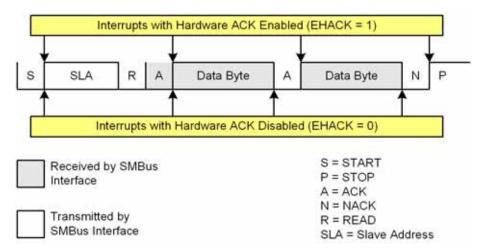

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames. The position of the ACK interrupt when operating as a receiver depends on whether hardware ACK generation is enabled. As a receiver, the interrupt for an ACK occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled. As a transmitter, interrupts occur **after** the ACK, regardless of whether hardware ACK generation is enabled or not.

#### 22.5.1. Write Sequence (Master)

During a write sequence, an SMBus master writes data to a slave device. The master in this transfer will be a transmitter during the address byte, and a transmitter during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 0 (WRITE). The master then transmits one or more bytes of serial data. After each byte is transmitted, an acknowledge bit is generated by the slave. The transfer is ended when the STO bit is set and a STOP is generated. The interface will switch to Master Receiver Mode if SMB0DAT is not written following a Master Transmitter interrupt. Figure 22.5 shows a typical master write sequence. Two transmit data bytes are shown, though any number of bytes may be transmitted. Notice that all of the "data byte transferred" interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

Figure 22.5. Typical Master Write Sequence

#### 22.5.2. Read Sequence (Master)

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

Writing a 1 to the ACK bit generates an ACK; writing a 0 generates a NACK. Software should write a 0 to the ACK bit for the last data transfer, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if SMB0-DAT is written while an active Master Receiver. Figure 22.6 shows a typical master read sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 22.6. Typical Master Read Sequence

## SFR Definition 24.2. SMOD1: UART1 Mode

| Bit   | 7                    | 6                                                                  | 5                             | 4                      | 3             | 2              | 1                | 0            |

|-------|----------------------|--------------------------------------------------------------------|-------------------------------|------------------------|---------------|----------------|------------------|--------------|

| Nam   | e MCE1               | S1P                                                                | [1:0]                         | PE1                    | S1D           | L[1:0]         | XBE1             | SBL1         |

| Туре  | Type R/W R/W R/W R/W |                                                                    | /W                            | R/W                    | R/W           |                |                  |              |

| Rese  | et 0                 | 0                                                                  | 0                             | 0                      | 1             | 1              | 0                | 0            |

| SFR A | Address = 0          | KE5; SFR Page                                                      | = All Pages                   | 5                      |               |                |                  |              |

| Bit   | Name                 |                                                                    |                               |                        | Function      |                |                  |              |

| 7     | MCE1                 | Multiprocess                                                       | or Commur                     | nication Ena           | able.         |                |                  |              |

|       |                      | 0: RI will be ad<br>1: RI will be ad<br>XBE1).<br>Note: This fun   | ctivated if sto               | op bit(s) and          | extra bit are |                |                  | bled using   |

| 6:5   | S1PT[1:0]            | Parity Type B                                                      | its.                          |                        |               |                |                  |              |

|       |                      | 00: Odd                                                            |                               |                        |               |                |                  |              |

|       |                      | 01: Even<br>10: Mark                                               |                               |                        |               |                |                  |              |

|       |                      | 11: Space                                                          |                               |                        |               |                |                  |              |

| 4     | PE1                  | Parity Enable                                                      | •                             |                        |               |                |                  |              |

|       |                      | This bit activa<br>by bits S1PT1<br>0: Hardware p<br>1: Hardware p | -0 when par<br>arity is disat | ity is enable<br>bled. |               | checking. The  | e parity type    | is selected  |

| 3:2   | S1DL[1:0]            | Data Length.                                                       |                               |                        |               |                |                  |              |

|       |                      | 00: 5-bit data                                                     |                               |                        |               |                |                  |              |

|       |                      | 01: 6-bit data<br>10: 7-bit data                                   |                               |                        |               |                |                  |              |

|       |                      | 11: 8-bit data                                                     |                               |                        |               |                |                  |              |

| 1     | XBE1                 | Extra Bit Ena                                                      | ble.                          |                        |               |                |                  |              |

|       |                      | When enabled                                                       |                               | of TBX1 will           | be appende    | d to the data  | field.           |              |

|       |                      | 0: Extra Bit Di<br>1: Extra Bit Er                                 |                               |                        |               |                |                  |              |

| 0     | SBL1                 | Stop Bit Leng                                                      |                               |                        |               |                |                  |              |

|       |                      | 0: Short—Stor                                                      | -                             | e for one bit          | time.         |                |                  |              |

|       |                      | 1: Long—Stop<br>(data length =                                     | bit is active                 |                        |               | ngth = 6, 7, o | or 8 bits), or 1 | .5 bit times |

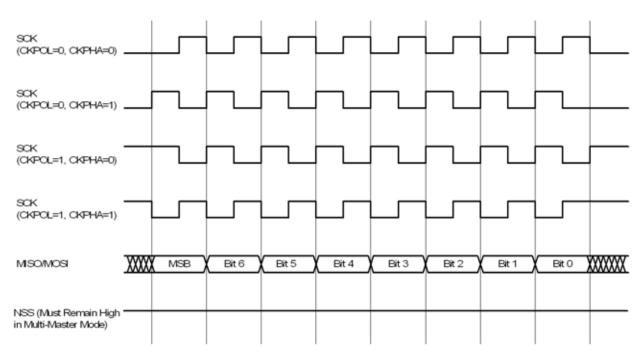

## SFR Definition 25.2. SPI0CN: SPI0 Control

| Bit   | 7    | 6    | 5    | 4      | 3    | 2       | 1     | 0     |

|-------|------|------|------|--------|------|---------|-------|-------|

| Name  | SPIF | WCOL | MODF | RXOVRN | NSSM | ID[1:0] | ТХВМТ | SPIEN |

| Туре  | R/W  | R/W  | R/W  | R/W    | R/W  |         | R     | R/W   |

| Reset | 0    | 0    | 0    | 0      | 0    | 1       | 1     | 0     |

#### SFR Address = 0xF8; SFR Page = All Pages; Bit-Addressable

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF       | <b>SPI0 Interrupt Flag.</b><br>This bit is set to logic 1 by hardware at the end of a data transfer. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                                                      |

| 6   | WCOL       | Write Collision Flag.                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | This bit is set to logic 1 if a write to SPI0DAT is attempted when TXBMT is 0. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                       |

| 5   | MODF       | Mode Fault Flag.                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                             |

| 4   | RXOVRN     | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI0 shift register. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                         |

| 3:2 | NSSMD[1:0] | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | Selects between the following NSS operation modes:<br>(See Section 25.2 and Section 25.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |

| 1   | TXBMT      | Transmit Buffer Empty.                                                                                                                                                                                                                                                                                                                                                                       |

|     |            | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                              |

| 0   | SPIEN      | SPI0 Enable.                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | 0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                                                                                                                                                          |

## SFR Definition 26.9. TMR2CN: Timer 2 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1     | 0      |

|-------|------|------|--------|--------|---------|-----|-------|--------|

| Name  | TF2H | TF2L | TF2LEN | TF2CEN | T2SPLIT | TR2 | T2CSS | T2XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/W   | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0     | 0      |

#### SFR Address = 0xC8; SFR Page = 0; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | TF2H    | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|     |         | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                            |  |  |  |  |

| 6   | TF2L    | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|     |         | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                         |  |  |  |  |

| 5   | TF2LEN  | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|     |         | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                                                                    |  |  |  |  |

| 4   | TF2CEN  | Timer 2 Low-Frequency Oscillator Capture Enable.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|     |         | When set to 1, this bit enables Timer 2 Low-Frequency Oscillator Capture Mode. If TF2CEN is set and Timer 2 interrupts are enabled, an interrupt will be generated on a falling edge of the low-frequency oscillator output, and the current 16-bit timer value in TMR2H:TMR2L will be copied to TMR2RLH:TMR2RLL.                                                              |  |  |  |  |

| 3   | T2SPLIT | Timer 2 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|     |         | When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 2   | TR2     | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|     |         | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                                                                    |  |  |  |  |

| 1   | T2CSS   | Timer 2 Capture Source Select.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|     |         | This bit selects the source of a capture event when bit T2CE is set to 1.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|     |         | 0: Capture source is USB SOF event.<br>1: Capture source is falling edge of Low-Frequency Oscillator.                                                                                                                                                                                                                                                                          |  |  |  |  |

| 0   | T2XCLK  | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|     |         | This bit selects the external clock source for Timer 2. However, the Timer 2 Clock<br>Select bits (T2MH and T2ML in register CKCON) may still be used to select between<br>the external clock and the system clock for either timer.<br>0: Timer 2 clock is the system clock divided by 12.<br>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK). |  |  |  |  |

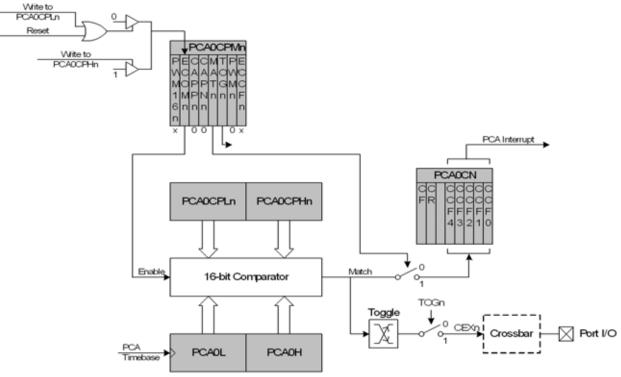

#### 27.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 27.6. PCA High-Speed Output Mode Diagram

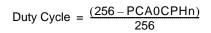

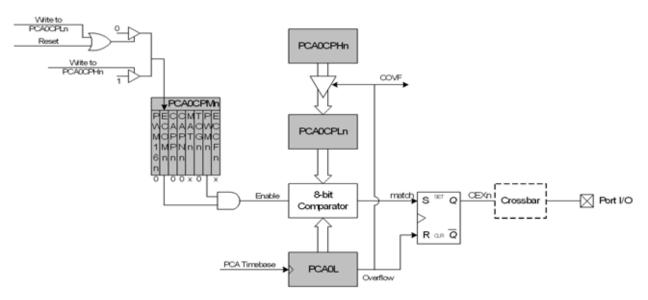

#### 27.3.5. 8-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 8-bit PWM mode is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 27.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register enables 8-Bit Pulse Width Modulator mode. If the MATn bit is set to 1, the CCFn flag for the module will be set each time an 8-bit comparator match (rising edge) occurs. The duty cycle for 8-Bit PWM Mode is given in Equation 27.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

#### Equation 27.2. 8-Bit PWM Duty Cycle

Using Equation 27.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 27.8. PCA 8-Bit PWM Mode Diagram