#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48 MIPS                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | A/D 21x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f383-gq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. System Overview

C8051F380/1/2/3/4/5/6/7/C devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 48 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Universal Serial Bus (USB) Function Controller with eight flexible endpoint pipes, integrated transceiver, and 1 kB FIFO RAM

- Supply Voltage Regulator

- True 10-bit 500 ksps differential / single-ended ADC with analog multiplexer

- On-chip Voltage Reference and Temperature Sensor

- On-chip Voltage Comparators (2)

- Precision internal calibrated 48 MHz internal oscillator

- Internal low-frequency oscillator for additional power savings

- Up to 64 kB of on-chip Flash memory

- Up to 4352 Bytes of on-chip RAM (256 + 4 kB)

- External Memory Interface (EMIF) available on 48-pin versions.

- 2 I<sup>2</sup>C/SMBus, 2 UARTs, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Missing Clock Detector

- Up to 40 Port I/O (5 V tolerant)

With on-chip Power-On Reset,  $V_{DD}$  monitor, Voltage Regulator, Watchdog Timer, and clock oscillator, C8051F380/1/2/3/4/5/6/7/C devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 2.7–5.25 V operation over the industrial temperature range (–40 to +85 °C). For voltages above 3.6 V, the on-chip Voltage Regulator must be used. A minimum of 3.0 V is required for USB communication. The Port I/O and RST pins are tolerant of input signals up to 5 V. C8051F380/1/2/3/ 4/5/6/7/C devices are available in 48-pin TQFP, 32-pin LQFP, or 32-pin QFN packages. See Table 1.1, "Product Selection Guide," on page 17 for feature and package choices.

USB is connected to a host device and is shown with a 100  $\Omega$  current-limiting resistor. This current-limiting resistor is recommended for systems that may experience electrostatic discharge (ESD), latch-up, and have a greater opportunity to share signals with systems that do not have the same ground potential. This is not a required component for most applications.

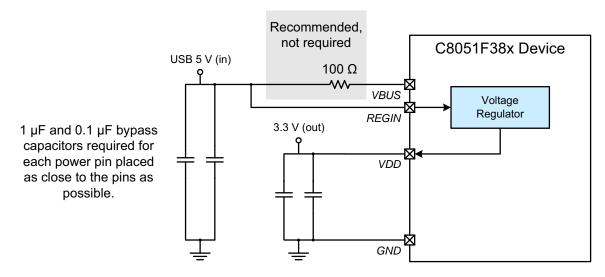

Figure 4.3. Connection Diagram with Voltage Regulator Used and USB Connected (Bus-Powered)

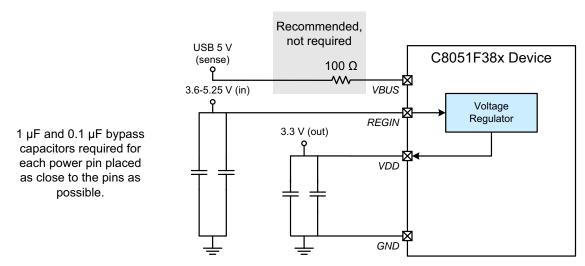

Figure 4.4 shows a typical connection diagram for the power pins of the C8051F38x devices when the internal regulator used and USB is connected (self-powered). The VBUS signal is used to detect when USB is connected to a host device and is shown with a 100  $\Omega$  current-limiting resistor. This current-limiting resistor is recommended for systems that may experience electrostatic discharge (ESD), latch-up, and have a greater opportunity to share signals with systems that do not have the same ground potential. This is not a required component for most applications.

# 5. Electrical Characteristics

# 5.1. Absolute Maximum Specifications

### Table 5.1. Absolute Maximum Ratings

| Parameter                                                                    | Conditions                                                             | Min          | Тур | Max                          | Units  |

|------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|-----|------------------------------|--------|

| Junction Temperature Under Bias                                              |                                                                        | -55          |     | 125                          | °C     |

| Storage Temperature                                                          |                                                                        | -65          |     | 150                          | °C     |

| Voltage on <del>RST</del> , VBUS, or any<br>Port I/O Pin with Respect to GND | V <sub>DD</sub> ≥ 2.2 V<br>V <sub>DD</sub> < 2.2 V                     | -0.3<br>-0.3 | _   | 5.8<br>V <sub>DD</sub> + 3.6 | V<br>V |

| Voltage on V <sub>DD</sub> with Respect to<br>GND                            | Regulator1 in Normal Mode<br>Regulator1 in Bypass Mode                 | -0.3<br>-0.3 |     | 4.2<br>1.98                  | V<br>V |

| Maximum Total Current through<br>V <sub>DD</sub> or GND                      |                                                                        | _            |     | 500                          | mA     |

| Maximum Output Current sunk by RST or any Port Pin                           |                                                                        |              |     | 100                          | mA     |

| Note: Stresses above those listed unc<br>This is a stress rating only and    | der "Absolute Maximum Ratings" i<br>functional operation of the device | -            | -   | -                            |        |

those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### Table 5.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 2.7 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter           | Test Condition                                                                                    | Min                                            | Тур                   | Max | Unit |

|---------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------|-----|------|

| Output High Voltage | $I_{OH} = -3 \text{ mA}$ , Port I/O push-pull<br>$I_{OH} = -10 \mu \text{A}$ , Port I/O push-pull | V <sub>DD</sub> – 0.7<br>V <sub>DD</sub> – 0.1 | _                     |     | V    |

|                     | $I_{OH} = -10$ mA, Port I/O push-pull                                                             |                                                | V <sub>DD</sub> – 0.8 | —   |      |

| Output Low Voltage  | I <sub>OL</sub> = 8.5 mA                                                                          | _                                              |                       | 0.6 | V    |

|                     | I <sub>OL</sub> = 10 μA                                                                           | _                                              | —                     | 0.1 |      |

|                     | I <sub>OL</sub> = 25 mA                                                                           | —                                              | 1.0                   | —   |      |

| Input High Voltage  |                                                                                                   | 2.0                                            | _                     | _   | V    |

| Input Low Voltage   |                                                                                                   | —                                              | _                     | 0.8 | V    |

| Input Leakage       | Weak Pullup Off                                                                                   | _                                              | _                     | ±1  | μA   |

| Current             | Weak Pullup On, V <sub>IN</sub> = 0 V                                                             | _                                              | 15                    | 50  |      |

#### **Table 5.4. Reset Electrical Characteristics**

-40 to +85 °C unless otherwise specified.

| Parameter                                                    | Test Condition                                                                        | Min                         | Тур  | Max                   | Unit |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|------|-----------------------|------|

| RST Output Low Voltage                                       | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 2.7 V to 3.6 V                         | _                           |      | 0.6                   | V    |

| RST Input High Voltage                                       |                                                                                       | $0.7 	ext{ x V}_{	ext{DD}}$ |      |                       | V    |

| RST Input Low Voltage                                        |                                                                                       | _                           | _    | 0.3 x V <sub>DD</sub> | V    |

| RST Input Pullup Current                                     | <del>RST</del> = 0.0 V                                                                | _                           | 15   | 40                    | μA   |

| $V_{DD}$ Monitor Threshold ( $V_{RST}$ )                     |                                                                                       | 2.60                        | 2.65 | 2.70                  | V    |

| Missing Clock Detector Time-<br>out                          | Time from last system clock rising edge to reset initiation                           | 80                          | 580  | 800                   | μs   |

| Reset Time Delay                                             | Delay between release of any<br>reset source and code<br>execution at location 0x0000 | _                           | _    | 250                   | μs   |

| Minimum $\overline{RST}$ Low Time to Generate a System Reset |                                                                                       | 15                          |      | —                     | μs   |

| V <sub>DD</sub> Monitor Turn-on Time                         |                                                                                       | _                           | —    | 100                   | μs   |

| V <sub>DD</sub> Monitor Supply Current                       |                                                                                       |                             | 15   | 50                    | μA   |

### 6.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

### SFR Definition 6.5. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit     | 7            | 6            | 5             | 4  | 3 | 2 | 1 | 0 |

|---------|--------------|--------------|---------------|----|---|---|---|---|

| Name    |              | ADC0GTH[7:0] |               |    |   |   |   |   |

| Туре    |              |              |               | R/ | W |   |   |   |

| Reset   | 1            | 1            | 1             | 1  | 1 | 1 | 1 | 1 |

| SFR Add | dress = 0xC4 | 4; SFR Page  | e = All Pages | 5  |   |   |   |   |

| Bit | Name         | Function                                     |

|-----|--------------|----------------------------------------------|

| 7:0 | ADC0GTH[7:0] | ADC0 Greater-Than Data Word High-Order Bits. |

### SFR Definition 6.6. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit   | 7                 | 6          | 5                                           | 4 | 2 | 2 | 1 | 0 |

|-------|-------------------|------------|---------------------------------------------|---|---|---|---|---|

| ы     | 1                 | 0          | 5                                           | 4 | 3 | 2 | 1 | 0 |

| Nam   | Name ADC0GTL[7:0] |            |                                             |   |   |   |   |   |

| Туре  | /pe R/W           |            |                                             |   |   |   |   |   |

| Rese  | et 1              | 1          | 1                                           | 1 | 1 | 1 | 1 | 1 |

| SFR A | Address = 0xC3    | ; SFR Page | e = All Pages                               | 5 |   |   |   |   |

| Bit   | Name              |            | Function                                    |   |   |   |   |   |

| 7:0   | ADC0GTL[7:0       | ] ADC0 GI  | ADC0 Greater-Than Data Word Low-Order Bits. |   |   |   |   |   |

# SFR Definition 8.4. CPT1MD: Comparator1 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1    | 0      |  |

|-------|---|---|--------|--------|---|---|------|--------|--|

| Name  |   |   | CP1RIE | CP1FIE |   |   | CP1M | D[1:0] |  |

| Туре  | R | R | R/W    | R/W    | R | R | R/   | R/W    |  |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1    | 0      |  |

#### SFR Address = 0x9C; SFR Page = All Pages

| Bit | Name       | Function                                                                   |

|-----|------------|----------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = don't care.                                            |

| 5   | CP1RIE     | Comparator1 Rising-Edge Interrupt Enable.                                  |

|     |            | 0: Comparator1 Rising-edge interrupt disabled.                             |

|     |            | 1: Comparator1 Rising-edge interrupt enabled.                              |

| 4   | CP1FIE     | Comparator1 Falling-Edge Interrupt Enable.                                 |

|     |            | 0: Comparator1 Falling-edge interrupt disabled.                            |

|     |            | 1: Comparator1 Falling-edge interrupt enabled.                             |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                            |

| 1:0 | CP1MD[1:0] | Comparator1 Mode Select.                                                   |

|     |            | These bits affect the response time and power consumption for Comparator1. |

|     |            | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)              |

|     |            | 01: Mode 1                                                                 |

|     |            | 10: Mode 2                                                                 |

|     |            | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)               |

# SFR Definition 8.5. CPT0MX: Comparator0 MUX Selection

| Bit   | 7              | 6           | 5           | 4              | 3          | 2        | 1          | 0 |  |  |

|-------|----------------|-------------|-------------|----------------|------------|----------|------------|---|--|--|

| Nam   | e              |             | CMX0N[2:0]  |                |            |          | CMX0P[2:0] |   |  |  |

| Туре  | e R            |             | R/W         |                | R          |          | R/W        |   |  |  |

| Rese  | et 0           | 0           | 0           | 0              | 0          | 0        | 0          | 0 |  |  |

| SFR / | Address = 0x9I | F; SFR Page | = All Page  | S              |            | 1        |            |   |  |  |

| Bit   | Name           |             |             |                | Function   |          |            |   |  |  |

| 7     | Unused         | Read = 0b;  | Write = dor | 't care.       |            |          |            |   |  |  |

| 6:4   | CMX0N[2:0]     | Comparato   | r0 Negativ  | e Input MUX    | Selection. |          |            |   |  |  |

|       |                | Selection   | 32          | -pin Package   | ;          | 48-pin l | Package    |   |  |  |

|       |                | 000: P1.1   |             |                |            |          | P2.1       |   |  |  |

|       |                | 001:        | P1          | .5             |            | P2.6     |            |   |  |  |

|       |                | 010:        | P2          | .1             |            | P3.5     |            |   |  |  |

|       |                | 011:        | P2          | P2.5           |            |          | P4.4       |   |  |  |

|       |                | 100:        | PO          | .1             |            | P0.4     | P0.4       |   |  |  |

|       |                | 101-111:    | Re          | served         |            | Reserv   | ed         |   |  |  |

| 3     | Unused         | Read = 0b;  | Write = dor | 't care.       |            |          |            |   |  |  |

| 2:0   | CMX0P[2:0]     | Comparato   | r0 Positive | Input MUX      | Selection. |          |            |   |  |  |

|       |                | Selection   | 32          | 32-pin Package |            |          | Package    |   |  |  |

|       |                | 000:        | P1          | P1.0           |            |          | P2.0       |   |  |  |

|       |                | 001:        | P1          | .4             |            | P2.5     | P2.5       |   |  |  |

|       |                | 010:        | P2          | .0             | P3.4       | P3.4     |            |   |  |  |

|       | 011:           |             | P2          | .4             |            | P4.3     |            |   |  |  |

|       |                | 100:        | PO          | .0             |            | P0.3     |            |   |  |  |

|       |                | 101-111:    | Re          | served         |            | Reserv   | ed         |   |  |  |

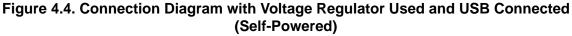

## 14.7.2. Multiplexed Mode 14.7.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011

Figure 14.8. Multiplexed 16-bit MOVX Timing

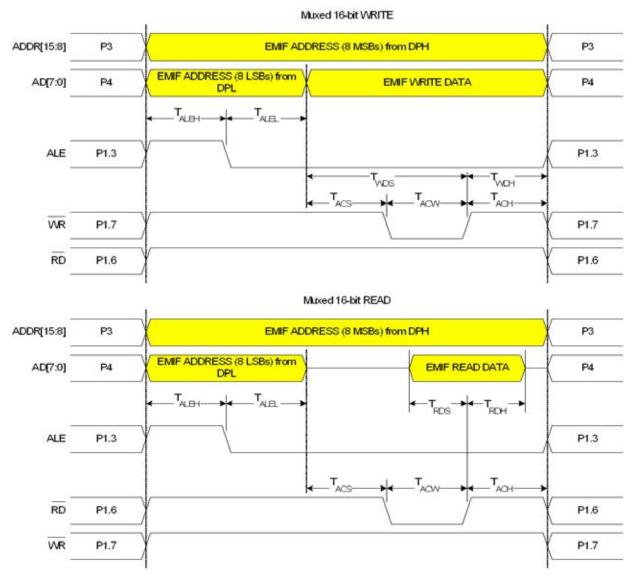

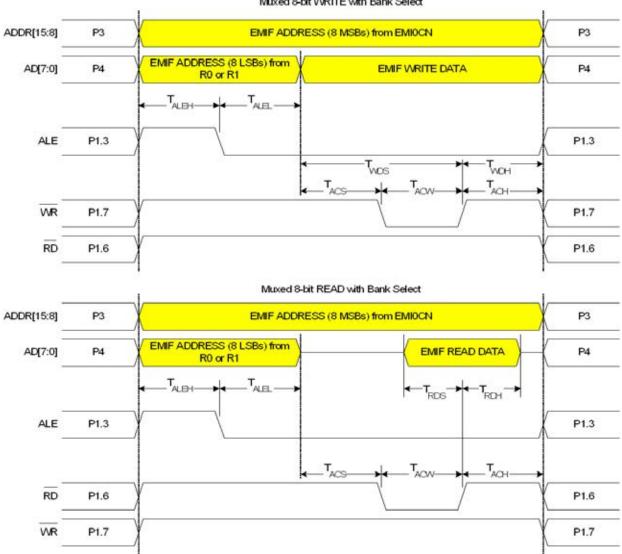

#### 14.7.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010

Muxed 8-bit WRITE with Bank Select

Figure 14.10. Multiplexed 8-bit MOVX with Bank Select Timing

# SFR Definition 16.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xA8; SFR Page = All Pages; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

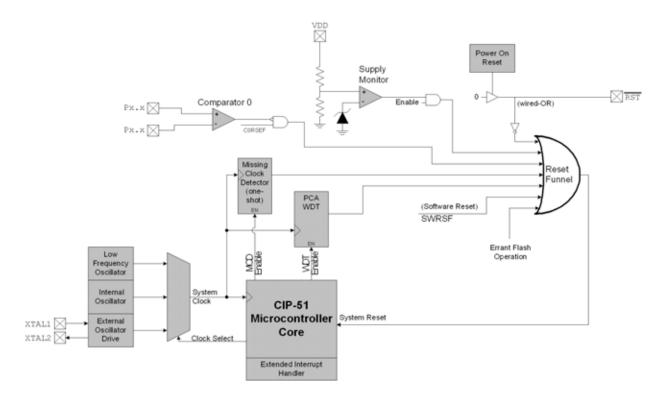

# 17. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overline{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 17.1. Reset Sources

# SFR Definition 20.4. P0: Port 0

| Bit   | 7 | 6       | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---------|---|---|---|---|---|---|

| Name  |   | P0[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W     |   |   |   |   |   |   |

| Reset | 1 | 1       | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0x80; SFR Page = All Pages; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P0.n Port pin is logic<br>LOW.<br>1: P0.n Port pin is logic<br>HIGH. |

## SFR Definition 20.5. P0MDIN: Port 0 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | POMDIN[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0xF1; SFR Page = All Pages

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P0.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P0.n pin is not configured for analog mode.                                                |

# USB Register Definition 21.21. EINCSRH: USB0 IN Endpoint Control High

| Bit   | 7     | 6   | 5      | 4 | 3    | 2     | 1 | 0 |

|-------|-------|-----|--------|---|------|-------|---|---|

| Name  | DBIEN | ISO | DIRSEL |   | FCDT | SPLIT |   |   |

| Туре  | R/W   | R/W | R/W    | R | R/W  | R/W   | R | R |

| Reset | 0     | 0   | 0      | 0 | 0    | 0     | 0 | 0 |

#### USB Register Address = 0x12

| Bit | Name   | Function                                                                                                                                                                                                                                                                       |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DBIEN  | IN Endpoint Double-buffer Enable.                                                                                                                                                                                                                                              |

|     |        | <ul><li>0: Double-buffering disabled for the selected IN endpoint.</li><li>1: Double-buffering enabled for the selected IN endpoint.</li></ul>                                                                                                                                 |

| 6   | ISO    | <ul> <li>Isochronous Transfer Enable.</li> <li>This bit enables/disables isochronous transfers on the current endpoint.</li> <li>0: Endpoint configured for bulk/interrupt transfers.</li> <li>1: Endpoint configured for isochronous transfers.</li> </ul>                    |

| 5   | DIRSEL | <ul> <li>Endpoint Direction Select.</li> <li>This bit is valid only when the selected FIFO is not split (SPLIT = 0).</li> <li>0: Endpoint direction selected as OUT.</li> <li>1: Endpoint direction selected as IN.</li> </ul>                                                 |

| 4   | Unused | Read = 0b. Write = don't care.                                                                                                                                                                                                                                                 |

| 3   | FCDT   | <ul> <li>Force Data Toggle Bit.</li> <li>0: Endpoint data toggle switches only when an ACK is received following a data packet transmission.</li> <li>1: Endpoint data toggle forced to switch after every data packet is transmitted, regardless of ACK reception.</li> </ul> |

| 2   | SPLIT  | <b>FIFO Split Enable.</b><br>When SPLIT = 1, the selected endpoint FIFO is split. The upper half of the selected FIFO is used by the IN endpoint; the lower half of the selected FIFO is used by the OUT endpoint.                                                             |

| 1:0 | Unused | Read = 00b. Write = don't care.                                                                                                                                                                                                                                                |

# SFR Definition 22.3. SMBTC: SMBus Timing Control

| Bit   | 7 | 6 | 5 | 4 | 3            | 2 | 1            | 0 |

|-------|---|---|---|---|--------------|---|--------------|---|

| Name  |   |   |   |   | SMB1SDD[1:0] |   | SMB0SDD[1:0] |   |

| Туре  | R | R | R | R | R/W          |   | R/           | W |

| Reset | 0 | 0 | 0 | 0 | 0            | 0 | 0            | 0 |

#### SFR Address = 0xB9; SFR Page = F

| Bit | Name         | Function                                                                                                    |

|-----|--------------|-------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused       | Read = 0000b; Write = don't care.                                                                           |

| 3:2 | SMB1SDD[1:0] | SMBus1 Start Detection Window                                                                               |

|     |              | These bits increase the hold time requirement between SDA falling and SCL fall-<br>ing for START detection. |

|     |              | 00: No additional hold time requirement (0-1 SYSCLK).                                                       |

|     |              | 01: Increase hold time window to 2-3 SYSCLKs.                                                               |

|     |              | 10: Increase hold time window to 4-5 SYSCLKs.                                                               |

|     |              | 11: Increase hold time window to 8-9 SYSCLKs.                                                               |

| 1:0 | SMB0SDD[1:0] | SMBus0 Start Detection Window                                                                               |

|     |              | These bits increase the hold time requirement between SDA falling and SCL fall-<br>ing for START detection. |

|     |              | 00: No additional hold time window (0-1 SYSCLK).                                                            |

|     |              | 01: Increase hold time window to 2-3 SYSCLKs.                                                               |

|     |              | 10: Increase hold time window to 4-5 SYSCLKs.                                                               |

|     |              | 11: Increase hold time window to 8-9 SYSCLKs.                                                               |

### SFR Definition 23.1. SCON0: Serial Port 0 Control

|       |             |                            | _                                    | 1            |              | 1             |            |     |

|-------|-------------|----------------------------|--------------------------------------|--------------|--------------|---------------|------------|-----|

| Bit   | 7           | 6                          | 5                                    | 4            | 3            | 2             | 1          | 0   |

| Nam   | e S0MOD     | E -                        | MCE0                                 | REN0         | TB80         | RB80          | TI0        | RI0 |

| Туре  | e R/W       | R                          | R/W                                  | R/W          | R/W          | R/W           | R/W        | R/W |

| Rese  | et 0        | 1                          | 0                                    | 0            | 0            | 0             | 0          | 0   |

| SFR A | Address = 0 | x98; SFR Page              | = All Pages                          | ; Bit-Addres | sable        |               |            |     |

| Bit   | Name        |                            | Function                             |              |              |               |            |     |

| 7     | SOMODE      | Serial Port 0              | Operation M                          | /lode.       |              |               |            |     |

|       |             | Selects the U              | ART0 Opera                           | tion Mode.   |              |               |            |     |

|       |             | 0: 8-bit UART              | with Variable                        | e Baud Rate  |              |               |            |     |

|       |             | 1: 9-bit UART              | with Variable                        | e Baud Rate  |              |               |            |     |

| 6     | Unused      | Read = 1b, W               | rite = don't c                       | are.         |              |               |            |     |

| 5     | MCE0        | Multiprocess               | Multiprocessor Communication Enable. |              |              |               |            |     |

|       |             | The function of            | of this bit is d                     | lependent or | the Serial F | Port 0 Operat | tion Mode: |     |

|       |             | Mode 0: Che                |                                      | •            |              |               |            |     |

|       |             | 0 <sup>.</sup> Logic level |                                      | -            |              |               |            |     |

| 1: RI0 will only be activated if stop bit is logic level 1. |

|-------------------------------------------------------------|

|  | Mode 1: Multiprocessor Communications Enable. |

|--|-----------------------------------------------|

|--|-----------------------------------------------|

| 0: Logic level of ninth bit is ignored.                                        |

|--------------------------------------------------------------------------------|

| 1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1 |

| REN0 | Receive Enable.                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------|

|      | 0: UART0 reception disabled.                                                                                                       |

|      | 1: UART0 reception enabled.                                                                                                        |

| TB80 | Ninth Transmission Bit.                                                                                                            |

|      | The logic level of this bit will be sent as the ninth transmission bit in 9-bit UART Mode (Mode 1). Unused in 8-bit mode (Mode 0). |

| RB80 | Ninth Receive Bit.                                                                                                                 |

|      | RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9th data bit in Mode 1.                      |

| TI0  | Transmit Interrupt Flag.                                                                                                           |

|      | Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bit                                               |

in 8-bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the UART0 interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software.

RI0Receive Interrupt Flag.Set to 1 by hardware when a byte of data has been received by UART0 (set at the<br/>STOP bit sampling time). When the UART0 interrupt is enabled, setting this bit to 1<br/>causes the CPU to vector to the UART0 interrupt service routine. This bit must be<br/>cleared manually by software.

4

3

2

1

0

### 25.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

### 25.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 25.5. For slave mode, the clock and data relationships are shown in Figure 25.6 and Figure 25.7. Note that CKPHA should be set to 0 on both the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 25.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

## 27.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high-speed output, frequency output, 8-bit pulse width modulator, or 16-bit pulse width modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 27.2 summarizes the bit settings in the PCA0CPMn register used to select the PCA capture/compare module's operating mode. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

| Operational Mode                                                                                                  |       | PCA0CPMn |   |   |   |   |   |   |

|-------------------------------------------------------------------------------------------------------------------|-------|----------|---|---|---|---|---|---|

| Bit Num                                                                                                           | ber 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

| Capture triggered by positive edge on CEXn                                                                        | Х     | X        | 1 | 0 | 0 | 0 | 0 | А |

| Capture triggered by negative edge on CEXn                                                                        | X     | X        | 0 | 1 | 0 | 0 | 0 | А |

| Capture triggered by any transition on CEXn                                                                       | X     | X        | 1 | 1 | 0 | 0 | 0 | А |

| Software Timer                                                                                                    | X     | В        | 0 | 0 | 1 | 0 | 0 | А |

| High Speed Output                                                                                                 | X     | В        | 0 | 0 | 1 | 1 | 0 | А |

| Frequency Output                                                                                                  | X     | В        | 0 | 0 | 0 | 1 | 1 | А |

| 8-Bit Pulse Width Modulator                                                                                       | 0     | В        | 0 | 0 | С | 0 | 1 | А |

| 16-Bit Pulse Width Modulator                                                                                      | 1     | В        | 0 | 0 | С | 0 | 1 | А |

| <ul> <li>Notes:</li> <li>1. X = Don't Care (no functional difference for individual module if 1 or 0).</li> </ul> |       |          |   |   |   |   |   |   |

#### Table 27.2. PCA0CPM Bit Settings for PCA Capture/Compare Modules

2. A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

3. B = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

4. C = When set, a match event will cause the CCFn flag for the associated channel to be set.

## SFR Definition 27.3. PCA0CPMn: PCA Capture/Compare Mode

| Bit   | 7      | 6     | 5     | 4     | 3    | 2    | 1    | 0     |

|-------|--------|-------|-------|-------|------|------|------|-------|

| Name  | PWM16n | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn |

| Туре  | R/W    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W   |

| Reset | 0      | 0     | 0     | 0     | 0    | 0    | 0    | 0     |

SFR Addresses: 0xDA (n = 0), 0xDB (n = 1), 0xDC (n = 2), 0xDD (n = 3), 0xDE (n = 4)

SFR Pages: All Pages (n = 0), All Pages (n = 1), All Pages (n = 2), All Pages (n = 3), All Pages (n = 4)

| Bit                                                                                                                                                                                                                       | Name   | Function                                                                                                                                                                                                                                                                                                      |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7                                                                                                                                                                                                                         | PWM16n | 16-bit Pulse Width Modulation Enable.                                                                                                                                                                                                                                                                         |  |  |  |

|                                                                                                                                                                                                                           |        | This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.<br>0: 8-bit PWM selected.<br>1: 16-bit PWM selected.                                                                                                                                                                                |  |  |  |

| 6                                                                                                                                                                                                                         | ECOMn  | Comparator Function Enable.                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                                                                                                                                                           |        | This bit enables the comparator function for PCA module n when set to 1.                                                                                                                                                                                                                                      |  |  |  |

| 5                                                                                                                                                                                                                         | CAPPn  | Capture Positive Function Enable.                                                                                                                                                                                                                                                                             |  |  |  |

|                                                                                                                                                                                                                           |        | This bit enables the positive edge capture for PCA module n when set to 1.                                                                                                                                                                                                                                    |  |  |  |

| 4                                                                                                                                                                                                                         | CAPNn  | Capture Negative Function Enable.                                                                                                                                                                                                                                                                             |  |  |  |

|                                                                                                                                                                                                                           |        | This bit enables the negative edge capture for PCA module n when set to 1.                                                                                                                                                                                                                                    |  |  |  |

| 3                                                                                                                                                                                                                         | MATn   | Match Function Enable.                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                                                                                                                                                                                           |        | This bit enables the match function for PCA module n when set to 1. When enabled, matches of the PCA counter with a module's capture/compare register cause the CCFn bit in PCA0MD register to be set to logic 1.                                                                                             |  |  |  |

| 2                                                                                                                                                                                                                         | TOGn   | Toggle Function Enable.                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                                                                                                                                                                                           |        | This bit enables the toggle function for PCA module n when set to 1. When enabled, matches of the PCA counter with a module's capture/compare register cause the logic level on the CEXn pin to toggle. If the PWMn bit is also set to logic 1, the module operates in Frequency Output Mode.                 |  |  |  |

| 1                                                                                                                                                                                                                         | PWMn   | Pulse Width Modulation Mode Enable.                                                                                                                                                                                                                                                                           |  |  |  |

|                                                                                                                                                                                                                           |        | This bit enables the PWM function for PCA module n when set to 1. When enabled, a pulse width modulated signal is output on the CEXn pin. 8-bit PWM is used if PWM16n is cleared; 16-bit mode is used if PWM16n is set to logic 1. If the TOGn bit is also set, the module operates in Frequency Output Mode. |  |  |  |

| 0                                                                                                                                                                                                                         | ECCFn  | Capture/Compare Flag Interrupt Enable.                                                                                                                                                                                                                                                                        |  |  |  |

|                                                                                                                                                                                                                           |        | This bit sets the masking of the Capture/Compare Flag (CCFn) interrupt.                                                                                                                                                                                                                                       |  |  |  |

|                                                                                                                                                                                                                           |        | <ul><li>0: Disable CCFn interrupts.</li><li>1: Enable a Capture/Compare Flag interrupt request when CCFn is set.</li></ul>                                                                                                                                                                                    |  |  |  |

| <b>Note:</b> When the WDTE bit is set to 1, the PCA0CPM4 register cannot be modified, and module 4 as watchdog timer. To change the contents of the PCA0CPM4 register or the function of module 4 Timer must be disabled. |        |                                                                                                                                                                                                                                                                                                               |  |  |  |