#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48 MIPS                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | ·                                                               |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                    |

| Data Converters            | A/D 21x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-LQFP                                                         |

| Supplier Device Package    | 32-LQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f383-gqr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

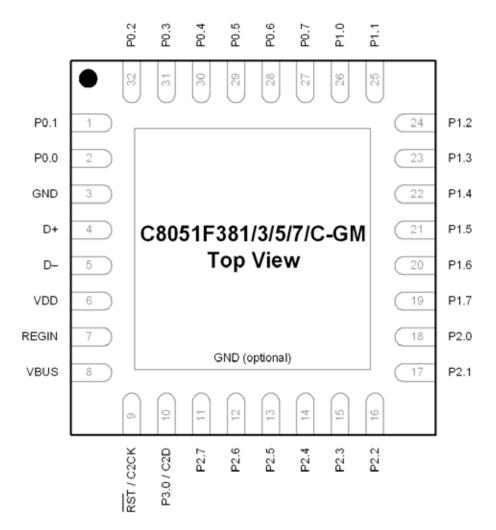

Figure 3.7. QFN-32 Pinout Diagram (Top View)

#### 6.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 6.5. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit                                      | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------------------------------------------|--------------|---|---|---|---|---|---|---|--|--|

| Name                                     | ADC0GTH[7:0] |   |   |   |   |   |   |   |  |  |

| Туре                                     | R/W          |   |   |   |   |   |   |   |  |  |

| Reset                                    |              |   |   |   |   |   |   |   |  |  |

| SFR Address = 0xC4; SFR Page = All Pages |              |   |   |   |   |   |   |   |  |  |

| Bit | Name         | Function                                     |

|-----|--------------|----------------------------------------------|

| 7:0 | ADC0GTH[7:0] | ADC0 Greater-Than Data Word High-Order Bits. |

#### SFR Definition 6.6. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit      | 7              | 6            | 5                                           | 4 | 2 | 2 | 1 | 0 |  |  |

|----------|----------------|--------------|---------------------------------------------|---|---|---|---|---|--|--|

| ы        | 1              | 0            | 5                                           | 4 | 3 | 2 | 1 | 0 |  |  |

| Nam      | e              | ADC0GTL[7:0] |                                             |   |   |   |   |   |  |  |

| Type R/W |                |              |                                             |   |   |   |   |   |  |  |

| Rese     | et 1           | 1            | 1                                           | 1 | 1 | 1 | 1 | 1 |  |  |

| SFR A    | Address = 0xC3 | ; SFR Page   | e = All Pages                               | 5 |   |   |   |   |  |  |

| Bit      | Name           |              | Function                                    |   |   |   |   |   |  |  |

| 7:0      | ADC0GTL[7:0    | ] ADC0 GI    | ADC0 Greater-Than Data Word Low-Order Bits. |   |   |   |   |   |  |  |

## SFR Definition 8.5. CPT0MX: Comparator0 MUX Selection

| Bit   | 7              | 6                                         | 5                              | 4            | 3          | 2        | 1          | 0 |  |  |

|-------|----------------|-------------------------------------------|--------------------------------|--------------|------------|----------|------------|---|--|--|

| Nam   | e              |                                           | CMX0N[2:0                      | )]           |            |          | CMX0P[2:0] |   |  |  |

| Туре  | e R            |                                           | R/W                            |              | R          | R/W      |            |   |  |  |

| Rese  | et 0           | 0                                         | 0                              | 0            | 0          | 0        | 0          | 0 |  |  |

| SFR / | Address = 0x9I | F; SFR Page                               | = All Page                     | S            |            | 1        |            |   |  |  |

| Bit   | Name           |                                           |                                |              | Function   |          |            |   |  |  |

| 7     | Unused         | Read = 0b;                                | Read = 0b; Write = don't care. |              |            |          |            |   |  |  |

| 6:4   | CMX0N[2:0]     | Comparato                                 | r0 Negativ                     | e Input MUX  | Selection. |          |            |   |  |  |

|       |                | Selection                                 | 32                             | -pin Package | ;          | 48-pin l | Package    |   |  |  |

|       |                | 000:                                      | P1                             | .1           |            | P2.1     |            |   |  |  |

|       |                | 001:                                      | P1                             | .5           |            | P2.6     |            |   |  |  |

|       |                | 010:                                      | P2                             | .1           |            | P3.5     |            |   |  |  |

|       |                | 011:                                      | P2                             | .5           |            | P4.4     |            |   |  |  |

|       |                | 100:                                      | PO                             | .1           |            | P0.4     |            |   |  |  |

|       |                | 101-111:                                  | Re                             | served       |            | Reserved |            |   |  |  |

| 3     | Unused         | Read = 0b;                                | Write = dor                    | 't care.     |            |          |            |   |  |  |

| 2:0   | CMX0P[2:0]     | Comparator0 Positive Input MUX Selection. |                                |              |            |          |            |   |  |  |

|       |                | Selection                                 | 32                             | -pin Package | ;          | 48-pin l | Package    |   |  |  |

|       |                | 000:                                      | P1                             | .0           |            | P2.0     |            |   |  |  |

|       |                | 001:                                      | P1                             | .4           |            | P2.5     |            |   |  |  |

|       |                | 010:                                      | 010: P2.0                      |              |            | P3.4     |            |   |  |  |

|       |                | 011:                                      | P2                             | .4           |            | P4.3     | P4.3       |   |  |  |

|       |                | 100:                                      | PO                             | .0           |            | P0.3     |            |   |  |  |

|       |                | 101-111:                                  | Re                             | served       |            | Reserved |            |   |  |  |

## SFR Definition 9.1. REG01CN: Voltage Regulator Control

| Bit                                      | 7        | 6                                                                                                                                                                                                                                                                                                                                                         | 5                                                                                                                                                                                                                                          | 4                                | 3                     | 2            | 1            | 0             |  |

|------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|--------------|--------------|---------------|--|

| Nam                                      | e REG0DI | S VBSTAT                                                                                                                                                                                                                                                                                                                                                  | Reserved                                                                                                                                                                                                                                   | REG0MD                           | STOPCF                | Reserved     | REG1MD       | Reserved      |  |

| Туре                                     | e R/W    | R                                                                                                                                                                                                                                                                                                                                                         | R/W                                                                                                                                                                                                                                        | R/W                              | R/W                   | R/W          | R/W          | R/W           |  |

| Rese                                     | et 0     | 0                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                          | 0                                | 0                     | 0            | 0            | 0             |  |

| SFR Address = 0xC9; SFR Page = All Pages |          |                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                            |                                  |                       |              |              |               |  |

| Bit                                      | Name     |                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                            |                                  | Function              |              |              |               |  |

| 7                                        | REG0DIS  | This bit enable<br>0: Voltage Re                                                                                                                                                                                                                                                                                                                          | Voltage Regulator (REG0) Disable.<br>This bit enables or disables the REG0 Voltage Regulator.<br>D: Voltage Regulator Enabled.<br>1: Voltage Regulator Disabled.                                                                           |                                  |                       |              |              |               |  |

| 6                                        | VBSTAT   | This bit indica<br>0: VBUS signa                                                                                                                                                                                                                                                                                                                          | VBUS Signal Status.<br>This bit indicates whether the device is connected to a USB network.<br>0: VBUS signal currently absent (device not attached to USB network).<br>1: VBUS signal currently present (device attached to USB network). |                                  |                       |              |              |               |  |

| 5                                        | Reserved | Must Write 0b                                                                                                                                                                                                                                                                                                                                             | Must Write 0b.                                                                                                                                                                                                                             |                                  |                       |              |              |               |  |

| 4                                        | REG0MD   | Voltage Regu                                                                                                                                                                                                                                                                                                                                              | lator (REG                                                                                                                                                                                                                                 | )) Mode Sel                      | ect.                  |              |              |               |  |

|                                          |          | This bit select<br>REG0 voltage<br>0: REG0 Volta<br>1: REG0 Volta                                                                                                                                                                                                                                                                                         | regulator op<br>ige Regulato                                                                                                                                                                                                               | perates in lov<br>or in normal r | wer power (s<br>node. |              |              | et to 1, the  |  |

| 3                                        | STOPCF   | Stop Mode C<br>This bit config<br>0: REG1 Regu<br>device.<br>1: REG1 Regu<br>reset the device                                                                                                                                                                                                                                                             | ures the RE<br>ulator is still a<br>ulator is shut                                                                                                                                                                                         | G1 regulator<br>active in STC    | P mode. An            | y enabled re | set source w | ill reset the |  |

| 2                                        | Reserved | Must Write 0b                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                            |                                  |                       |              |              |               |  |

| 1                                        | REG1MD   | Voltage Regulator (REG1) Mode.<br>This bit selects the Voltage Regulator mode for REG1. When REG1MD is set to 1, the<br>REG1 voltage regulator operates in lower power mode.<br>0: REG1 Voltage Regulator in normal mode.<br>1: REG1 Voltage Regulator in low power mode.<br>This bit should not be set to '1' if the REG0 Voltage Regulator is disabled. |                                                                                                                                                                                                                                            |                                  |                       |              |              | et to 1, the  |  |

| 0                                        | Reserved | Must Write 0b                                                                                                                                                                                                                                                                                                                                             | •                                                                                                                                                                                                                                          |                                  |                       |              |              |               |  |

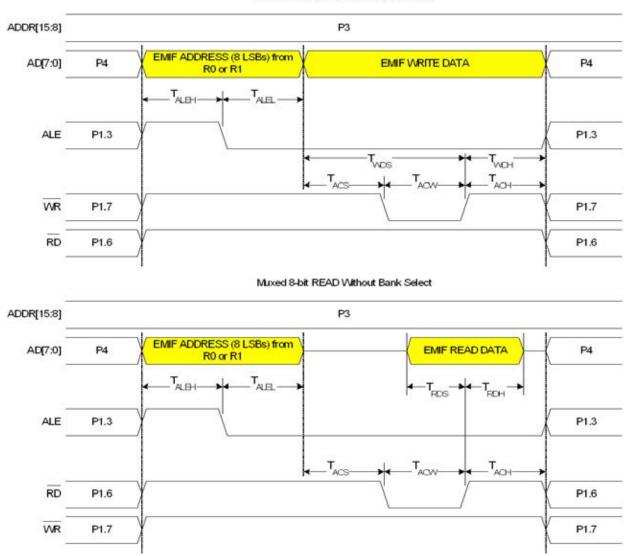

#### 14.7.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011

Muxed 8-bit WRITE Without Bank Select

## SFR Definition 16.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7            | 6                                                                                                                                                                                                                        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                              | 3                               | 2                               | 1                              | 0                          |  |  |

|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------|---------------------------------|--------------------------------|----------------------------|--|--|

| Nam   | e IN1PL      | IN1SL[2:0]                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                | IN0PL                           | IN0SL[2:0]                      |                                |                            |  |  |

| Туре  | e R/W        |                                                                                                                                                                                                                          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                | R/W                             |                                 | R/W                            |                            |  |  |

| Rese  | et 0         | 0                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                              | 0                               | 0                               | 0                              | 1                          |  |  |

| SFR A | ddress = 0xI | <br>E4; SFR Page                                                                                                                                                                                                         | = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                |                                 |                                 |                                | <u> </u> ]                 |  |  |

| Bit   | Name         |                                                                                                                                                                                                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |                                 |                                 |                                |                            |  |  |

| 7     | IN1PL        | INT1 Polarity<br>0: INT1 input<br>1: INT1 input                                                                                                                                                                          | is active low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |                                 |                                 |                                |                            |  |  |

| 6:4   | IN1SL[2:0]   | These bits se<br>independent<br>ing the periph<br>will not assig<br>000: Select F<br>001: Select F<br>010: Select F<br>100: Select F<br>100: Select F                                                                    | NT1 Port Pin Selection Bits.<br>hese bits select which Port pin is assigned to INT1. Note that this pin assignment is<br>independent of the Crossbar; INT1 will monitor the assigned Port pin without disturb-<br>ing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar<br>vill not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br>00: Select P0.0<br>01: Select P0.1<br>10: Select P0.2<br>11: Select P0.3<br>00: Select P0.4<br>01: Select P0.5<br>10: Select P0.6<br>11: Select P0.6 |                                                |                                 |                                 |                                |                            |  |  |

| 3     | IN0PL        | INTO Polarity<br>0: INTO input<br>1: INTO input                                                                                                                                                                          | is active low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |                                 |                                 |                                |                            |  |  |

| 2:0   | IN0SL[2:0]   | INTO Port Pi<br>These bits se<br>independent<br>ing the periph<br>will not assig<br>000: Select F<br>001: Select F<br>010: Select F<br>100: Select F<br>101: Select F<br>101: Select F<br>110: Select P<br>111: Select P | elect which P<br>of the Cross<br>heral that has<br>n the Port pi<br>20.0<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6                                                                                                                                                                                                                                                                                                                                                                                                                                      | Port pin is as<br>bar; INTO wi<br>s been assig | ill monitor the<br>ned the Port | e assigned F<br>t pin via the ( | Port pin witho<br>Crossbar. Th | out disturb-<br>e Crossbar |  |  |

### SFR Definition 19.6. OSCXCN: External Oscillator Control

| Bit   | 7       | 6           | 5 | 4 | 3 | 2         | 1 | 0 |

|-------|---------|-------------|---|---|---|-----------|---|---|

| Name  | XCLKVLD | XOSCMD[2:0] |   |   |   | XFCN[2:0] |   |   |

| Туре  | R       | R/W         |   |   | R | R/W       |   |   |

| Reset | 0       | 0           | 0 | 0 | 0 | 0         | 0 | 0 |

#### SFR Address = 0xB1; SFR Page = All Pages

| Bit | Name        |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                       | Function                                   |                 |  |  |  |  |

|-----|-------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|--|--|--|--|

| 7   | XCLKVLD     | Provides<br>tion exc<br>divide b<br>0: Exter                       |                                                                                                                                                                                                                                                                                                                                                                                                       | r not yet stable.                          |                 |  |  |  |  |

| 6:4 | XOSCMD[2:0] | 00x: Ext<br>010: Ext<br>011: Ext<br>100: RC<br>101: Ca<br>110: Cry | xternal Oscillator Mode Select.         0x: External Oscillator circuit off.         10: External CMOS Clock Mode.         11: External CMOS Clock Mode with divide-by-2 stage.         00: RC Oscillator Mode with divide-by-2 stage.         01: Capacitor Oscillator Mode with divide-by-2 stage.         10: Crystal Oscillator Mode.         11: Crystal Oscillator Mode with divide-by-2 stage. |                                            |                 |  |  |  |  |

| 3   | Unused      | Read =                                                             | Read = 0; Write = don't care                                                                                                                                                                                                                                                                                                                                                                          |                                            |                 |  |  |  |  |

| 2:0 | XFCN[2:0]   | Set acco                                                           | Il Oscillator Frequency<br>ording to the desired freq<br>ording to the desired K Fa                                                                                                                                                                                                                                                                                                                   | uency for RC mode.                         |                 |  |  |  |  |

|     |             | XFCN                                                               | Crystal Mode                                                                                                                                                                                                                                                                                                                                                                                          | RC Mode                                    | C Mode          |  |  |  |  |

|     |             | 000                                                                | f ≤ 20 kHz                                                                                                                                                                                                                                                                                                                                                                                            | f ≤ 25 kHz                                 | K Factor = 0.87 |  |  |  |  |

|     |             | 001                                                                | 20 kHz < f $\leq$ 58 kHz                                                                                                                                                                                                                                                                                                                                                                              | $25 \text{ kHz} < f \le 50 \text{ kHz}$    | K Factor = 2.6  |  |  |  |  |

|     |             | 010                                                                | 58 kHz < f ≤ 155 kHz                                                                                                                                                                                                                                                                                                                                                                                  | 50 kHz < f $\leq$ 100 kHz                  | K Factor = 7.7  |  |  |  |  |

|     |             | 011                                                                | 155 kHz $<$ f $\leq$ 415 kHz                                                                                                                                                                                                                                                                                                                                                                          | 100 kHz $<$ f $\leq$ 200 kHz               | K Factor = 22   |  |  |  |  |

|     |             | 100                                                                | 415 kHz $<$ f $\leq$ 1.1 MHz                                                                                                                                                                                                                                                                                                                                                                          | $200 \text{ kHz} < f \leq 400 \text{ kHz}$ | K Factor = 65   |  |  |  |  |

|     |             | 101                                                                | 1.1 MHz $< f \le 3.1$ MHz                                                                                                                                                                                                                                                                                                                                                                             | 400 kHz $<$ f $\le$ 800 kHz                | K Factor = 180  |  |  |  |  |

|     |             | 110                                                                | $3.1 \text{ MHz} < f \le 8.2 \text{ MHz}$                                                                                                                                                                                                                                                                                                                                                             | 800 kHz $< f \le 1.6$ MHz                  | K Factor = 664  |  |  |  |  |

|     |             | 111                                                                | $8.2 \text{ MHz} < f \le 25 \text{ MHz}$                                                                                                                                                                                                                                                                                                                                                              | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$  | K Factor = 1590 |  |  |  |  |

### SFR Definition 20.4. P0: Port 0

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------|---|---|---|---|---|---|---|--|

| Name  | P0[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W     |   |   |   |   |   |   |   |  |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

SFR Address = 0x80; SFR Page = All Pages; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P0[7:0] | <b>Port 0 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P0.n Port pin is logic<br>LOW.<br>1: P0.n Port pin is logic<br>HIGH. |

### SFR Definition 20.5. P0MDIN: Port 0 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------|---|---|---|---|---|---|---|--|

| Name  | P0MDIN[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

#### SFR Address = 0xF1; SFR Page = All Pages

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P0.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P0.n pin is not configured for analog mode.                                                |

| Endpoint  | Associated Pipes | USB Protocol Address |  |  |

|-----------|------------------|----------------------|--|--|

| Endpoint0 | Endpoint0 IN     | 0x00                 |  |  |

|           | Endpoint0 OUT    | 0x00                 |  |  |

| Endpoint1 | Endpoint1 IN     | 0x81                 |  |  |

|           | Endpoint1 OUT    | 0x01                 |  |  |

| Endpoint2 | Endpoint2 IN     | 0x82                 |  |  |

|           | Endpoint2 OUT    | 0x02                 |  |  |

| Endpoint3 | Endpoint3 IN     | 0x83                 |  |  |

|           | Endpoint3 OUT    | 0x03                 |  |  |

#### 21.2. USB Transceiver

The USB Transceiver is configured via the USB0XCN register shown in SFR Definition 21.1. This configuration includes Transceiver enable/disable, pull-up resistor enable/disable, and device speed selection (Full or Low Speed). When bit SPEED = 1, USB0 operates as a Full Speed USB function, and the on-chip pull-up resistor (if enabled) appears on the D+ pin. When bit SPEED = 0, USB0 operates as a Low Speed USB function, and the on-chip pull-up resistor (if enabled) appears on the D- pin. Bits4-0 of register USB0XCN can be used for Transceiver testing as described in SFR Definition 21.1. The pull-up resistor is enabled only when VBUS is present (see Section "9.1.2. VBUS Detection" on page 74 for details on VBUS detection).

Important Note: The USB clock should be active before the Transceiver is enabled.

Suspend Interrupt Service Routine (ISR) should perform application-specific configuration tasks such as disabling appropriate peripherals and/or configuring clock sources for low power modes. See Section "19.3. Programmable Internal High-Frequency (H-F) Oscillator" on page 145 for more details on internal oscillator configuration, including the Suspend mode feature of the internal oscillator.

USB0 exits Suspend mode when any of the following occur: (1) Resume signaling is detected or generated, (2) Reset signaling is detected, or (3) a device or USB reset occurs. If suspended, the internal oscillator will exit Suspend mode upon any of the above listed events.

**Resume Signaling:** USB0 will exit Suspend mode if Resume signaling is detected on the bus. A Resume interrupt will be generated upon detection if enabled (RESINTE = 1). Software may force a Remote Wakeup by writing 1 to the RESUME bit (POWER.2). When forcing a Remote Wakeup, software should write RESUME = 0 to end Resume signaling 10-15 ms after the Remote Wakeup is initiated (RESUME = 1).

**ISO Update:** When software writes 1 to the ISOUP bit (POWER.7), the ISO Update function is enabled. With ISO Update enabled, new packets written to an ISO IN endpoint will not be transmitted until a new Start-Of-Frame (SOF) is received. If the ISO IN endpoint receives an IN token before a SOF, USB0 will transmit a zero-length packet. When ISOUP = 1, ISO Update is enabled for all ISO endpoints.

**USB Enable:** USB0 is disabled following a Power-On-Reset (POR). USB0 is enabled by clearing the USBINH bit (POWER.4). Once written to 0, the USBINH can only be set to 1 by one of the following: (1) a Power-On-Reset (POR), or (2) an asynchronous USB0 reset generated by writing 1 to the USBRST bit (POWER.3).

Software should perform all USB0 configuration before enabling USB0. The configuration sequence should be performed as follows:

- 1. Select and enable the USB clock source.

- 2. Reset USB0 by writing USBRST= 1.

- 3. Configure and enable the USB Transceiver.

- 4. Perform any USB0 function configuration (interrupts, Suspend detect).

- 5. Enable USB0 by writing USBINH = 0.

#### 22.5.3. Write Sequence (Slave)

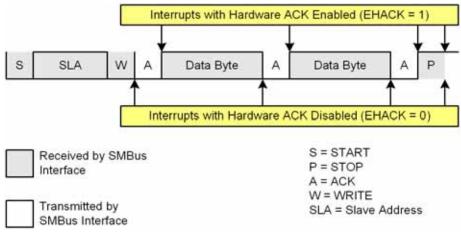

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

The interface exits Slave Receiver Mode after receiving a STOP. The interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 22.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 22.7. Typical Slave Write Sequence

#### 24.1. Baud Rate Generator

The UART1 baud rate is generated by a dedicated 16-bit timer which runs from the controller's core clock (SYSCLK), and has prescaler options of 1, 4, 12, or 48. The timer and prescaler options combined allow for a wide selection of baud rates over many SYSCLK frequencies.

The baud rate generator is configured using three registers: SBCON1, SBRLH1, and SBRLL1. The UART1 Baud Rate Generator Control Register (SBCON1, SFR Definition) enables or disables the baud rate generator, and selects the prescaler value for the timer. The baud rate generator must be enabled for UART1 to function. Registers SBRLH1 and SBRLL1 contain a 16-bit reload value for the dedicated 16-bit timer. The internal timer counts up from the reload value on every clock tick. On timer overflows (0xFFFF to 0x0000), the timer is reloaded. For reliable UART operation, it is recommended that the UART baud rate is not configured for baud rates faster than SYSCLK/16. The baud rate for UART1 is defined in Equation 24.1.

$Baud Rate = \frac{SYSCLK}{(65536 - (SBRLH1:SBRLL1))} \times \frac{1}{2} \times \frac{1}{Prescaler}$

Equation 24.1. UART1 Baud Rate

A quick reference for typical baud rates and system clock frequencies is given in Table 24.1.

|        | Target Baud | Actual Baud | Baud Rate | Oscillator       | SB1PS[1:0]       | Reload Value in |

|--------|-------------|-------------|-----------|------------------|------------------|-----------------|

|        | Rate (bps)  | Rate (bps)  | Error     | Divide<br>Factor | (Prescaler Bits) | SBRLH1:SBRLL1   |

| -      |             |             |           |                  |                  |                 |

| N      | 230400      | 230769      | 0.16%     | 52               | 11               | 0xFFE6          |

| MHz    | 115200      | 115385      | 0.16%     | 104              | 11               | 0xFFCC          |

| 2      | 57600       | 57692       | 0.16%     | 208              | 11               | 0xFF98          |

| Ĩ      | 28800       | 28846       | 0.16%     | 416              | 11               | 0xFF30          |

|        | 14400       | 14388       | 0.08%     | 834              | 11               | 0xFE5F          |

| 12     | 9600        | 9600        | 0.0%      | 1250             | 11               | 0xFD8F          |

| SYSCLK | 2400        | 2400        | 0.0%      | 5000             | 11               | 0xF63C          |

| S      | 1200        | 1200        | 0.0%      | 10000            | 11               | 0xEC78          |

| N      | 230400      | 230769      | 0.16%     | 104              | 11               | 0xFFCC          |

| MHz    | 115200      | 115385      | 0.16%     | 208              | 11               | 0xFF98          |

| 24 N   | 57600       | 57692       | 0.16%     | 416              | 11               | 0xFF30          |

| = 2    | 28800       | 28777       | 0.08%     | 834              | 11               | 0xFE5F          |

|        | 14400       | 14406       | 0.04%     | 1666             | 11               | 0xFCBF          |

| 12     | 9600        | 9600        | 0.0%      | 2500             | 11               | 0xFB1E          |

| SYSCLK | 2400        | 2400        | 0.0%      | 10000            | 11               | 0xEC78          |

| S      | 1200        | 1200        | 0.0%      | 20000            | 11               | 0xD8F0          |

|        | 230400      | 230769      | 0.16%     | 208              | 11               | 0xFF98          |

| MHz    | 115200      | 115385      | 0.16%     | 416              | 11               | 0xFF30          |

| 48 N   | 57600       | 57554       | 0.08%     | 834              | 11               | 0xFE5F          |

| =      | 28800       | 28812       | 0.04%     | 1666             | 11               | 0xFCBF          |

|        | 14400       | 14397       | 0.02%     | 3334             | 11               | 0xF97D          |

| SCLK   | 9600        | 9600        | 0.0%      | 5000             | 11               | 0xF63C          |

| SΥS    | 2400        | 2400        | 0.0%      | 20000            | 11               | 0xD8F0          |

| S      | 1200        | 1200        | 0.0%      | 40000            | 11               | 0xB1E0          |

Table 24.1. Baud Rate Generator Settings for Standard Baud Rates

#### 25.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

#### 25.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 25.5. For slave mode, the clock and data relationships are shown in Figure 25.6 and Figure 25.7. Note that CKPHA should be set to 0 on both the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 25.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

## SFR Definition 26.1. CKCON: Clock Control

| Bit   | 7    | 6    | 5    | 4    | 3   | 2   | 1        | 0 |

|-------|------|------|------|------|-----|-----|----------|---|

| Name  | ТЗМН | T3ML | T2MH | T2ML | T1M | ТОМ | SCA[1:0] |   |

| Туре  | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W      |   |

| Reset | 0    | 0    | 0    | 0    | 0   | 0   | 0        | 0 |

#### SFR Address = 0x8E; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ТЗМН     | Timer 3 High Byte Clock Select.                                                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).<br>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.<br>1: Timer 3 high byte uses the system clock.                                                                                                     |

| 6   | T3ML     | Timer 3 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 low byte uses the system clock.</li> </ul>                                    |

| 5   | T2MH     | Timer 2 High Byte Clock Select.                                                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).<br>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.<br>1: Timer 2 high byte uses the system clock.                                                                                                     |

| 4   | T2ML     | Timer 2 Low Byte Clock Select.                                                                                                                                                                                                                                                                                    |

|     |          | <ul> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |

| 3   | T1       | Timer 1 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                             |

| 2   | Т0       | Timer 0 Clock Select.                                                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.<br>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].<br>1: Counter/Timer 0 uses the system clock.                                                                                                             |

|     | 00414.01 |                                                                                                                                                                                                                                                                                                                   |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.These bits control the Timer 0/1 Clock Prescaler:00: System clock divided by 1201: System clock divided by 410: System clock divided by 4811: External clock divided by 8 (synchronized with the system clock)                                                                            |

|     |          | 1                                                                                                                                                                                                                                                                                                                 |

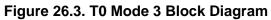

#### 26.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode, (split) 8-bit auto-reload mode, USB Start-of-Frame (SOF) capture mode, or Low-Frequency Oscillator (LFO) Rising Edge capture mode. The Timer 3 operation mode is defined by the T3SPLIT (TMR3CN.3), T3CE (TMR3CN.4) bits, and T3CSS (TMR3CN.1) bits.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 26.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 26.8, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 26.8. Timer 3 16-Bit Mode Block Diagram

### SFR Definition 26.15. TMR3RLL: Timer 3 Reload Register Low Byte

| Bit                              | 7    | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------------------------------|------|--------------|---|---|---|---|---|---|--|

| Name                             |      | TMR3RLL[7:0] |   |   |   |   |   |   |  |

| Туре                             |      | R/W          |   |   |   |   |   |   |  |

| Reset                            | 0    | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Address = 0x92; SFR Page = 0 |      |              |   |   |   |   |   |   |  |

| Bit                              | Name |              |   |   |   |   |   |   |  |

| Bit | Name         | Function                                                    |  |  |  |  |  |

|-----|--------------|-------------------------------------------------------------|--|--|--|--|--|

| 7:0 | TMR3RLL[7:0] | imer 3 Reload Register Low Byte.                            |  |  |  |  |  |

|     |              | TMR3RLL holds the low byte of the reload value for Timer 3. |  |  |  |  |  |

### SFR Definition 26.16. TMR3RLH: Timer 3 Reload Register High Byte

| Bit   | 7                 | 6          | 5                                  | 4              | 3            | 2            | 1    | 0 |

|-------|-------------------|------------|------------------------------------|----------------|--------------|--------------|------|---|

| Nam   | Name TMR3RLH[7:0] |            |                                    |                |              |              |      |   |

| Тур   | R/W               |            |                                    |                |              |              |      |   |

| Rese  | et 0              | 0          | 0                                  | 0              | 0            | 0            | 0    | 0 |

| SFR A | Address = 0x93    | ; SFR Page | = 0                                |                |              |              |      |   |

| Bit   | Name              |            |                                    |                |              |              |      |   |

| 7:0   | TMR3RLH[7:0       | -          | Timer 3 Reload Register High Byte. |                |              |              |      |   |

|       |                   | TMR3RL     | H holds the l                      | high byte of t | he reload va | lue for Time | r 3. |   |

### SFR Definition 26.17. TMR3L: Timer 3 Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|------------|---|---|---|---|---|---|--|--|

| Name  |   | TMR3L[7:0] |   |   |   |   |   |   |  |  |

| Туре  |   | R/W        |   |   |   |   |   |   |  |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

#### SFR Address = 0x94; SFR Page = 0

| Bit | Name       | Function                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L[7:0] | Timer 3 Low Byte.                                                                                                                             |

|     |            | In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-bit mode, TMR3L contains the 8-bit low byte timer value. |

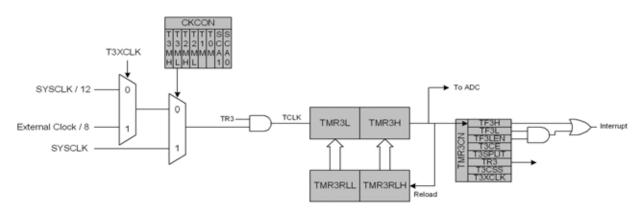

### 27.2. PCA0 Interrupt Sources

Figure 27.3 shows a diagram of the PCA interrupt tree. There are six independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter and the individual flags for each PCA channel (CCF0, CCF1, CCF2, CCF3, and CCF4), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

Figure 27.3. PCA Interrupt Block Diagram

### SFR Definition 27.2. PCA0MD: PCA Mode

| Bit                                      | 7        | 6                                                                                                                                                                                                                                                     | 5                                                                                                                                                                                                                                                                                                                                                                      | 4    | 3            | 2   | 1               | 0        |  |

|------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|-----|-----------------|----------|--|

| Name                                     | CIDL     | WDTE                                                                                                                                                                                                                                                  | WDLCK                                                                                                                                                                                                                                                                                                                                                                  |      | CPS[2:0] ECF |     |                 | ECF      |  |

| Туре                                     | R/W      | R/W                                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                    | R    |              | R/W |                 | R/W      |  |

| Reset                                    | t 0      | 1                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                      | 0    | 0            | 0   | 0               | 0        |  |

| SFR Address = 0xD9; SFR Page = All Pages |          |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                        |      |              |     |                 |          |  |

| Bit                                      | Name     |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                        |      | Function     |     |                 |          |  |

| 7                                        | CIDL     | Specifies PCA<br>0: PCA contin                                                                                                                                                                                                                        | <b>CA Counter/Timer Idle Control.</b><br>Specifies PCA behavior when CPU is in Idle Mode.<br>In PCA continues to function normally while the system controller is in Idle Mode.<br>In PCA operation is suspended while the system controller is in Idle Mode.                                                                                                          |      |              |     |                 |          |  |

| 6                                        | WDTE     | If this bit is se<br>0: Watchdog T                                                                                                                                                                                                                    | Watchdog Timer Enable.         f this bit is set, PCA Module 4 is used as the watchdog timer.         D: Watchdog Timer disabled.         1: PCA Module 4 enabled as Watchdog Timer.                                                                                                                                                                                   |      |              |     |                 |          |  |

| 5                                        | WDLCK    | This bit locks/<br>Timer may no<br>0: Watchdog T                                                                                                                                                                                                      | Watchdog Timer Lock.<br>This bit locks/unlocks the Watchdog Timer Enable. When WDLCK is set, the Watchdog<br>Timer may not be disabled until the next system reset.<br>0: Watchdog Timer Enable unlocked.<br>1: Watchdog Timer Enable locked.                                                                                                                          |      |              |     |                 |          |  |

| 4                                        | Unused   | Read = 0b, W                                                                                                                                                                                                                                          | rite = Don't c                                                                                                                                                                                                                                                                                                                                                         | are. |              |     |                 |          |  |

| 3:1                                      | CPS[2:0] | These bits sel<br>000: System o<br>001: System o<br>010: Timer 0 o<br>011: High-to-lo<br>100: System o                                                                                                                                                | PCA Counter/Timer Pulse Select.<br>These bits select the timebase source for the PCA counter<br>000: System clock divided by 12<br>001: System clock divided by 4<br>010: Timer 0 overflow<br>011: High-to-low transitions on ECI (max rate = system clock divided by 4)<br>100: System clock<br>101: External clock divided by 8 (synchronized with the system clock) |      |              |     |                 |          |  |