Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48 MIPS                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f385-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

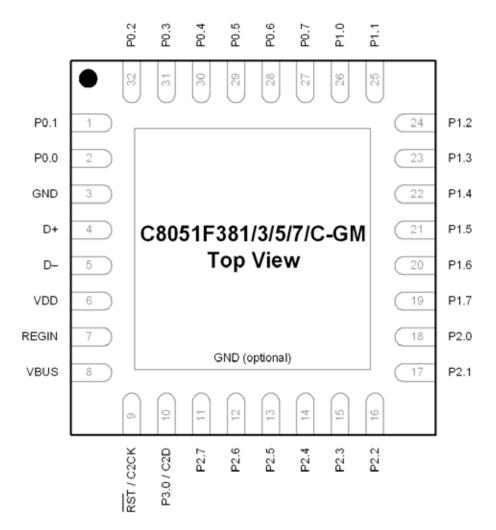

Figure 3.7. QFN-32 Pinout Diagram (Top View)

# SFR Definition 6.2. ADC0H: ADC0 Data Word MSB

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|---|---|---|---|--|

| Name  |   | ADC0H[7:0]      |   |    |   |   |   |   |  |

| Туре  |   |                 |   | R/ | W |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |

SFR Address = 0xBE; SFR Page = All Pages

| Bit | Name       | Function                                                                                                     |

|-----|------------|--------------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                              |

|     |            | For AD0LJST = 0: Bits 7–2 will read 000000b. Bits 1–0 are the upper 2 bits of the 10-<br>bit ADC0 Data Word. |

|     |            | For AD0LJST = 1: Bits 7–0 are the most-significant bits of the 10-bit ADC0 Data Word.                        |

#### SFR Definition 6.3. ADC0L: ADC0 Data Word LSB

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|---|---|---|---|--|

| Name  |   | ADC0L[7:0]      |   |    |   |   |   |   |  |

| Туре  |   |                 |   | R/ | W |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |

#### SFR Address = 0xBD; SFR Page = All Pages

| Bit | Name | Function                                                                                                                                                                                                            |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 |      | ADC0 Data Word Low-Order Bits.<br>For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the 10-bit Data Word.<br>For AD0LJST = 1: Bits 7–6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will<br>read 000000b. |

With the CIP-51's maximum system clock at 48 MHz, it has a peak throughput of 48 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/4 | 3  | 3/5 | 4 | 5 | 4/6 | 6 | 8 |

|------------------------|----|----|-----|----|-----|---|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 10 | 6   | 5 | 2 | 2   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources. C2 details can be found in Section "28. C2 Interface" on page 316.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

#### 11.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 11.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 11.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

# SFR Definition 11.6. PSW: Program Status Word

| Bit                                                       | 7       | 6                                    | 5            | 4              | 3               | 2                              | 1             | 0              |  |

|-----------------------------------------------------------|---------|--------------------------------------|--------------|----------------|-----------------|--------------------------------|---------------|----------------|--|

| Nam                                                       | e CY    | AC                                   | F0           | RS             | [1:0]           | OV                             | F1            | PARITY         |  |

| Туре                                                      | R/W     | R/W                                  | R/W          | R              | /W              | R/W                            | R/W           | R              |  |

| Rese                                                      | et 0    | 0                                    | 0            | 0              | 0               | 0                              | 0             | 0              |  |

| SFR Address = 0xD0; SFR Page = All Pages; Bit-Addressable |         |                                      |              |                |                 |                                |               |                |  |

| Bit                                                       | Name    |                                      |              |                | Function        |                                |               |                |  |

| 7                                                         | CY      | Carry Flag.                          |              |                |                 |                                |               |                |  |

|                                                           |         | This bit is set row (subtraction     |              |                |                 |                                |               | n) or a bor-   |  |

| 6                                                         | AC      | Auxiliary Car                        | ry Flag.     |                |                 |                                |               |                |  |

|                                                           |         | This bit is set                      |              |                |                 |                                |               |                |  |

|                                                           |         | borrow from (s<br>metic operatio     | ,            | the high ord   | er nibble. It   | is cleared to I                | logic 0 by al | I other arith- |  |

| 5                                                         | F0      | User Flag 0.                         |              |                |                 |                                |               |                |  |

|                                                           |         | This is a bit-ad                     | ddressable,  | general purp   | ose flag for    | use under so                   | oftware cont  | rol.           |  |

| 4:3                                                       | RS[1:0] | Register Ban                         | k Select.    |                |                 |                                |               |                |  |

|                                                           |         | These bits sel                       |              | -              | s used durir    | ng register ac                 | cesses.       |                |  |

|                                                           |         | 00: Bank 0, Ao<br>01: Bank 1, Ao     |              |                |                 |                                |               |                |  |

|                                                           |         | 10: Bank 2, A                        |              |                |                 |                                |               |                |  |

|                                                           |         | 11: Bank 3, Ac                       | dresses 0x   | 18-0x1F        |                 |                                |               |                |  |

| 2                                                         | OV      | <b>Overflow Flag</b>                 | g.           |                |                 |                                |               |                |  |

|                                                           |         | This bit is set                      |              | -              |                 |                                |               |                |  |

|                                                           |         |                                      |              |                |                 | n-change ove<br>greater than 2 |               |                |  |

|                                                           |         |                                      |              | es a divide-by | •               | •                              | 00).          |                |  |

|                                                           |         | The OV bit is other cases.           | cleared to 0 | by the ADD,    | ADDC, SU        | BB, MUL, and                   | d DIV instru  | ctions in all  |  |

| 1                                                         | F1      | User Flag 1.                         |              |                |                 |                                |               |                |  |

|                                                           |         | This is a bit-ad                     | ddressable,  | general purp   | ose flag for    | use under so                   | oftware cont  | rol.           |  |

| 0                                                         | PARITY  | Parity Flag.                         |              |                |                 |                                |               |                |  |

|                                                           |         | This bit is set t<br>if the sum is e | -            | ne sum of the  | e eight bits ir | n the accumu                   | lator is odd  | and cleared    |  |

## SFR Definition 14.1. EMI0CN: External Memory Interface Control

|       | <b>F</b> |                 |   |    |   |   |   |   |  |  |

|-------|----------|-----------------|---|----|---|---|---|---|--|--|

| Bit   | 7        | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

| Name  |          | PGSEL[7:0]      |   |    |   |   |   |   |  |  |

| Туре  |          |                 |   | R/ | W |   |   |   |  |  |

| Reset | 0        | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |  |

SFR Address = 0xAA; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                       |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PGSEL[7:0] | XRAM Page Select Bits.                                                                                                                                                                                                                                                                         |

|     |            | The XRAM Page Select Bits provide the high byte of the 16-bit external data mem-<br>ory address when using an 8-bit MOVX command, effectively selecting a 256-byte<br>page of RAM.<br>0x00: 0x0000 to 0x00FF<br>0x01: 0x0100 to 0x01FF<br><br>0xFE: 0xFE00 to 0xFEFF<br>0xFF: 0xFF00 to 0xFFFF |

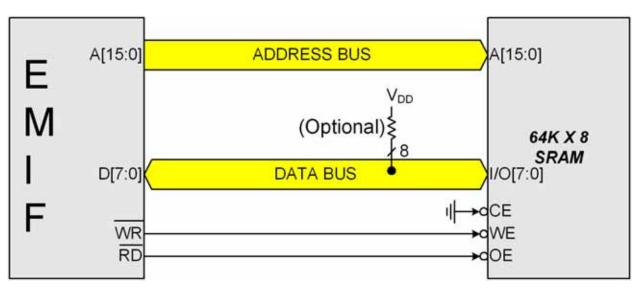

Figure 14.3. Non-multiplexed Configuration Example

| Address | Page   | 0(8)   | 1(9)     | 2(A)     | 3(B)     | 4(C)             | 5(D)     | 6(E)     | 7(F)           |

|---------|--------|--------|----------|----------|----------|------------------|----------|----------|----------------|

| F8      |        | SPI0CN | PCA0L    | PCA0H    | PCA0CPL0 | PCA0CPH0         | PCA0CPL4 | PCA0CPH4 | VDM0CN         |

| F0      |        | В      | P0MDIN   | P1MDIN   | P2MDIN   | P3MDIN           | P4MDIN   | EIP1     | EIP2           |

| E8      |        | ADC0CN | PCA0CPL1 | PCA0CPH1 | PCA0CPL2 | PCA0CPH2         | PCA0CPL3 | PCA0CPH3 | RSTSRC         |

| E0      | 0<br>F | ACC    | XBR0     | XBR1     | XBR2     | IT01CF<br>CKCON1 | SMOD1    | EIE1     | EIE2           |

| D8      |        | PCA0CN | PCA0MD   | PCA0CPM0 | PCA0CPM1 | PCA0CPM2         | PCA0CPM3 | PCA0CPM4 | P3SKIP         |

| D0      |        | PSW    | REF0CN   | SCON1    | SBUF1    | P0SKIP           | P1SKIP   | P2SKIP   | <b>USB0XCN</b> |

| C8      | 0      | TMR2CN | REG01CN  | TMR2RLL  | TMR2RLH  | TMR2L            | TMR2H    | SMB0ADM  | SMB0ADR        |

|         | F      | TMR5CN | REGUICIN | TMR5RLL  | TMR5RLH  | TMR5L            | TMR5H    | SMB1ADM  | SMB1ADR        |

| CO      | 0      | SMB0CN | SMB0CF   | SMB0DAT  | ADC0GTL  | ADC0GTH          | ADC0LTL  | ADC0LTH  | P4             |

|         | F      | SMB1CN | SMB1CF   | SMB1DAT  | ADCOGIL  | ADCOGIN /        | ADCULIL  | ADCULIN  | Γ4             |

| B8      | 0      | IP     | CLKMUL   | AMX0N    | AMX0P    | ADC0CF           | ADC0L    | ADC0H    | SFRPAGE        |

| Бо      | F      |        | SMBTC    |          | AIVIAUE  |                  | ADCOL    | ADCOIT   | SERFAGE        |

| B0      |        | P3     | OSCXCN   | OSCICN   | OSCICL   | SBRLL1           | SBRLH1   | FLSCL    | FLKEY          |

| A8      |        | IE     | CLKSEL   | EMIOCN   |          | SBCON1           |          | P4MDOUT  | PFE0CN         |

| A0      |        | P2     | SPI0CFG  | SPI0CKR  | SPI0DAT  | POMDOUT          | P1MDOUT  | P2MDOUT  | P3MDOUT        |

| 98      |        | SCON0  | SBUF0    | CPT1CN   | CPT0CN   | CPT1MD           | CPT0MD   | CPT1MX   | CPT0MX         |

| 90      | 0      | P1     | TMR3CN   | TMR3RLL  | TMR3RLH  | TMR3L            | TMR3H    | USB0ADR  | USB0DAT        |

| 90      | F      |        | TMR4CN   | TMR4RLL  | TMR4RLH  | TMR4L            | TMR4H    | USBUADR  | USBUDAI        |

| 88      |        | TCON   | TMOD     | TL0      | TL1      | TH0              | TH1      | CKCON    | PSCTL          |

| 80      |        | P0     | SP       | DPL      | DPH      | EMI0TC           | EMI0CF   | OSCLCN   | PCON           |

|         |        | 0(8)   | 1(9)     | 2(A)     | 3(B)     | 4(C)             | 5(D)     | 6(E)     | 7(F)           |

| Note    |        |        |          |          | -        | -                |          |          |                |

#### Table 15.1. Special Function Register (SFR) Memory Map

Notes:

1. SFR Addresses ending in 0x0 or 0x8 are bit-addressable locations and can be used with bitwise instructions.

2. Unless indicated otherwise, SFRs are available on both page 0 and page F.

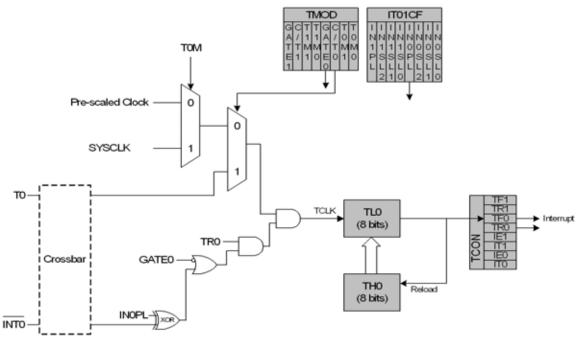

## 16.3. INTO and INT1 External Interrupt Sources

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "26.1. Timer 0 and Timer 1" on page 266) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INTO and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 16.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register PnSKIP (see Section "20.1. Priority Crossbar Decoder" on page 154 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INTO and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (INOPL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

# SFR Definition 19.6. OSCXCN: External Oscillator Control

| Bit   | 7       | 6           | 5 | 4 | 3 | 2         | 1 | 0 |

|-------|---------|-------------|---|---|---|-----------|---|---|

| Name  | XCLKVLD | XOSCMD[2:0] |   |   |   | XFCN[2:0] |   |   |

| Туре  | R       | R/W         |   |   | R | R/W       |   |   |

| Reset | 0       | 0           | 0 | 0 | 0 | 0         | 0 | 0 |

#### SFR Address = 0xB1; SFR Page = All Pages

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                  |                                            |                 |  |  |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|--|--|

| 7   | XCLKVLD     | <ul> <li>External Oscillator Valid Flag.</li> <li>Provides External Oscillator status and is valid at all times for all modes of operation except External CMOS Clock Mode and External CMOS Clock Mode with divide by 2. In these modes, XCLKVLD always returns 0.</li> <li>0: External Oscillator is unused or not yet stable.</li> <li>1: External Oscillator is running and stable.</li> </ul> |                                                                                                  |                                            |                 |  |  |

| 6:4 | XOSCMD[2:0] | External Oscillator Mode Select.00x: External Oscillator circuit off.010: External CMOS Clock Mode.011: External CMOS Clock Mode with divide-by-2 stage.100: RC Oscillator Mode with divide-by-2 stage.101: Capacitor Oscillator Mode with divide-by-2 stage.110: Crystal Oscillator Mode.111: Crystal Oscillator Mode with divide-by-2 stage.                                                     |                                                                                                  |                                            |                 |  |  |

| 3   | Unused      | Read = 0; Write = don't care                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |                                            |                 |  |  |

| 2:0 | XFCN[2:0]   | External Oscillator Frequency Control Bits.<br>Set according to the desired frequency for RC mode.<br>Set according to the desired K Factor for C mode.                                                                                                                                                                                                                                            |                                                                                                  |                                            |                 |  |  |

|     |             | XFCN Crystal Mode RC Mode C Mo                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                  |                                            |                 |  |  |

|     |             | 000                                                                                                                                                                                                                                                                                                                                                                                                | f ≤ 20 kHz                                                                                       | f ≤ 25 kHz                                 | K Factor = 0.87 |  |  |

|     |             | 001                                                                                                                                                                                                                                                                                                                                                                                                | 20 kHz < f $\leq$ 58 kHz                                                                         | $25 \text{ kHz} < f \le 50 \text{ kHz}$    | K Factor = 2.6  |  |  |

|     |             | 010                                                                                                                                                                                                                                                                                                                                                                                                | 58 kHz < f ≤ 155 kHz                                                                             | 50 kHz < f $\leq$ 100 kHz                  | K Factor = 7.7  |  |  |

|     |             | 011                                                                                                                                                                                                                                                                                                                                                                                                | 155 kHz $<$ f $\leq$ 415 kHz                                                                     | 100 kHz $<$ f $\leq$ 200 kHz               | K Factor = 22   |  |  |

|     |             | 100                                                                                                                                                                                                                                                                                                                                                                                                | 415 kHz $<$ f $\leq$ 1.1 MHz                                                                     | $200 \text{ kHz} < f \leq 400 \text{ kHz}$ | K Factor = 65   |  |  |

|     |             | 101                                                                                                                                                                                                                                                                                                                                                                                                | $1.1 \text{ MHz} < f \le 3.1 \text{ MHz}$                                                        | 400 kHz $<$ f $\le$ 800 kHz                | K Factor = 180  |  |  |

|     |             | 110                                                                                                                                                                                                                                                                                                                                                                                                | $3.1 \text{ MHz} < f \le 8.2 \text{ MHz}$                                                        | 800 kHz $< f \le 1.6$ MHz                  | K Factor = 664  |  |  |

|     |             | 111                                                                                                                                                                                                                                                                                                                                                                                                | 111         8.2 MHz < f $\leq$ 25 MHz         1.6 MHz < f $\leq$ 3.2 MHz         K Factor = 1590 |                                            |                 |  |  |

### 21.9. The Serial Interface Engine

The Serial Interface Engine (SIE) performs all low level USB protocol tasks, interrupting the processor when data has successfully been transmitted or received. When receiving data, the SIE will interrupt the processor when a complete data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When transmitting data, the SIE will interrupt the processor when a complete data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When transmitting data, the SIE will interrupt the processor when a complete data packet has been transmitted and the appropriate handshake signal has been received.

The SIE will not interrupt the processor when corrupted/erroneous packets are received.

### 21.10. Endpoint0

Endpoint0 is managed through the USB register E0CSR (USB Register Definition 21.18). The INDEX register must be loaded with 0x00 to access the E0CSR register.

An Endpoint0 interrupt is generated when:

- 1. A data packet (OUT or SETUP) has been received and loaded into the Endpoint0 FIFO. The OPRDY bit (E0CSR.0) is set to 1 by hardware.

- 2. An IN data packet has successfully been unloaded from the Endpoint0 FIFO and transmitted to the host; INPRDY is reset to 0 by hardware.

- 3. An IN transaction is completed (this interrupt generated during the status stage of the transaction).

- 4. Hardware sets the STSTL bit (E0CSR.2) after a control transaction ended due to a protocol violation.

- 5. Hardware sets the SUEND bit (E0CSR.4) because a control transfer ended before firmware sets the DATAEND bit (E0CSR.3).

The E0CNT register (USB Register Definition 21.11) holds the number of received data bytes in the Endpoint0 FIFO.

Hardware will automatically detect protocol errors and send a STALL condition in response. Firmware may force a STALL condition to abort the current transfer. When a STALL condition is generated, the STSTL bit will be set to 1 and an interrupt generated. The following conditions will cause hardware to generate a STALL condition:

- 1. The host sends an OUT token during a OUT data phase after the DATAEND bit has been set to 1.

- 2. The host sends an IN token during an IN data phase after the DATAEND bit has been set to 1.

- 3. The host sends a packet that exceeds the maximum packet size for Endpoint0.

- 4. The host sends a non-zero length DATA1 packet during the status phase of an IN transaction.

Firmware sets the SDSTL bit (E0CSR.5) to 1.

#### 21.10.1. Endpoint0 SETUP Transactions

All control transfers must begin with a SETUP packet. SETUP packets are similar to OUT packets, containing an 8-byte data field sent by the host. Any SETUP packet containing a command field of anything other than 8 bytes will be automatically rejected by USB0. An Endpoint0 interrupt is generated when the data from a SETUP packet is loaded into the Endpoint0 FIFO. Software should unload the command from the Endpoint0 FIFO, decode the command, perform any necessary tasks, and set the SOPRDY bit to indicate that it has serviced the OUT packet.

#### 21.10.2. Endpoint0 IN Transactions

When a SETUP request is received that requires USB0 to transmit data to the host, one or more IN requests will be sent by the host. For the first IN transaction, firmware should load an IN packet into the Endpoint0 FIFO, and set the INPRDY bit (E0CSR.1). An interrupt will be generated when an IN packet is transmitted successfully. Note that no interrupt will be generated if an IN request is received before firm-

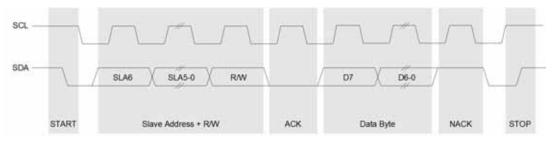

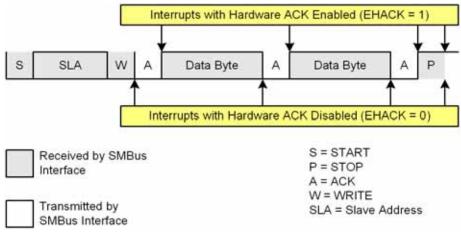

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 22.3 illustrates a typical SMBus transaction.

Figure 22.3. SMBus Transaction

#### 22.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 22.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "22.3.5. SCL High (SMBus Free) Timeout" on page 208). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 22.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 22.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

For the SMBus0 interface, Timer 3 is used to implement SCL low timeouts. Timer 4 is used on the SMBus1 interface for SCL low timeouts. The SCL low timeout feature is enabled by setting the SMBnTOE bit in SMBnCF. The associated timer is forced to reload when SCL is high, and allowed to count when SCL is

#### 22.5.3. Write Sequence (Slave)

During a write sequence, an SMBus master writes data to a slave device. The slave in this transfer will be a receiver during the address byte, and a receiver during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK, and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be set up by the software prior to receiving the byte when hardware ACK generation is enabled.

The interface exits Slave Receiver Mode after receiving a STOP. The interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 22.7 shows a typical slave write sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur at different places in the sequence, depending on whether hardware ACK generation is enabled. The interrupt occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled.

Figure 22.7. Typical Slave Write Sequence

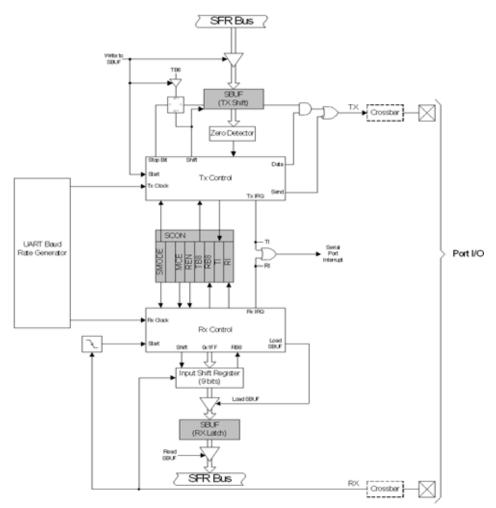

# 23. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "23.1. Enhanced Baud Rate Generation" on page 233). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 23.1. UART0 Block Diagram

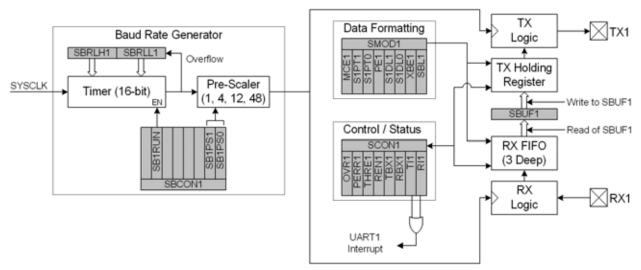

# 24. UART1

UART1 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates (details in Section "24.1. Baud Rate Generator" on page 241). A received data FIFO allows UART1 to receive up to three data bytes before data is lost and an overflow occurs.

UART1 has six associated SFRs. Three are used for the Baud Rate Generator (SBCON1, SBRLH1, and SBRLL1), two are used for data formatting, control, and status functions (SCON1, SMOD1), and one is used to send and receive data (SBUF1). The single SBUF1 location provides access to both the transmit holding register and the receive FIFO. Writes to SBUF1 always access the Transmit Holding Register. Reads of SBUF1 always access the first byte of the Receive FIFO; it is not possible to read data from the Transmit Holding Register.

With UART1 interrupts enabled, an interrupt is generated each time a transmit is completed (TI1 is set in SCON1), or a data byte has been received (RI1 is set in SCON1). The UART1 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART1 interrupt (transmit complete or receive complete). Note that if additional bytes are available in the Receive FIFO, the RI1 bit cannot be cleared by software.

Figure 24.1. UART1 Block Diagram

# SFR Definition 24.2. SMOD1: UART1 Mode

| Bit   | 7           | 6                                                                                                                                                                                                                                                            | 5             | 4   | 3   | 2              | 1                | 0            |  |  |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|----------------|------------------|--------------|--|--|

| Nam   | e MCE1      | S1P                                                                                                                                                                                                                                                          | [1:0]         | PE1 | S1D | L[1:0]         | XBE1             | SBL1         |  |  |

| Туре  | e R/W       | R/                                                                                                                                                                                                                                                           | W             | R/W | R   | /W             | R/W              | R/W          |  |  |

| Rese  | et 0        | 0                                                                                                                                                                                                                                                            | 0             | 0   | 1   | 1              | 0                | 0            |  |  |

| SFR A | Address = 0 | E5; SFR Page = All Pages                                                                                                                                                                                                                                     |               |     |     |                |                  |              |  |  |

| Bit   | Name        | Function                                                                                                                                                                                                                                                     |               |     |     |                |                  |              |  |  |

| 7     | MCE1        | Multiprocessor Communication Enable.                                                                                                                                                                                                                         |               |     |     |                |                  |              |  |  |

|       |             | <ul> <li>0: RI will be activated if stop bit(s) are 1.</li> <li>1: RI will be activated if stop bit(s) and extra bit are 1 (extra bit must be enabled using XBE1).</li> <li>Note: This function is not available when hardware parity is enabled.</li> </ul> |               |     |     |                |                  |              |  |  |

| 6:5   | S1PT[1:0]   | Parity Type Bits.                                                                                                                                                                                                                                            |               |     |     |                |                  |              |  |  |

|       |             | 00: Odd                                                                                                                                                                                                                                                      |               |     |     |                |                  |              |  |  |

|       |             | 01: Even<br>10: Mark                                                                                                                                                                                                                                         |               |     |     |                |                  |              |  |  |

|       |             | 11: Space                                                                                                                                                                                                                                                    |               |     |     |                |                  |              |  |  |

| 4     | PE1         | Parity Enable.                                                                                                                                                                                                                                               |               |     |     |                |                  |              |  |  |

|       |             | <ul> <li>This bit activates hardware parity generation and checking. The parity type is selected by bits S1PT1-0 when parity is enabled.</li> <li>0: Hardware parity is disabled.</li> <li>1: Hardware parity is enabled.</li> </ul>                         |               |     |     |                |                  |              |  |  |

| 3:2   | S1DL[1:0]   | Data Length.                                                                                                                                                                                                                                                 |               |     |     |                |                  |              |  |  |

|       |             | 00: 5-bit data                                                                                                                                                                                                                                               |               |     |     |                |                  |              |  |  |

|       |             | 01: 6-bit data<br>10: 7-bit data                                                                                                                                                                                                                             |               |     |     |                |                  |              |  |  |

|       |             | 11: 8-bit data                                                                                                                                                                                                                                               |               |     |     |                |                  |              |  |  |

| 1     | XBE1        | Extra Bit Enable.                                                                                                                                                                                                                                            |               |     |     |                |                  |              |  |  |

|       |             | When enabled, the value of TBX1 will be appended to the data field.                                                                                                                                                                                          |               |     |     |                |                  |              |  |  |

|       |             | 0: Extra Bit Di<br>1: Extra Bit Er                                                                                                                                                                                                                           |               |     |     |                |                  |              |  |  |

| 0     | SBL1        |                                                                                                                                                                                                                                                              |               |     |     |                |                  |              |  |  |

|       |             | Stop Bit Length.<br>0: Short—Stop bit is active for one bit time.                                                                                                                                                                                            |               |     |     |                |                  |              |  |  |

|       |             | 1: Long—Stop<br>(data length =                                                                                                                                                                                                                               | bit is active |     |     | ngth = 6, 7, o | or 8 bits), or 1 | .5 bit times |  |  |

Figure 26.2. T0 Mode 2 Block Diagram

#### 26.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates or overflow conditions for other peripherals. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

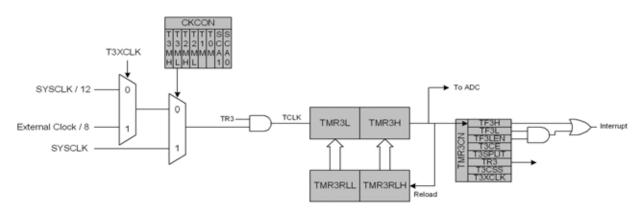

### 26.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode, (split) 8-bit auto-reload mode, USB Start-of-Frame (SOF) capture mode, or Low-Frequency Oscillator (LFO) Rising Edge capture mode. The Timer 3 operation mode is defined by the T3SPLIT (TMR3CN.3), T3CE (TMR3CN.4) bits, and T3CSS (TMR3CN.1) bits.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 26.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 26.8, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 26.8. Timer 3 16-Bit Mode Block Diagram

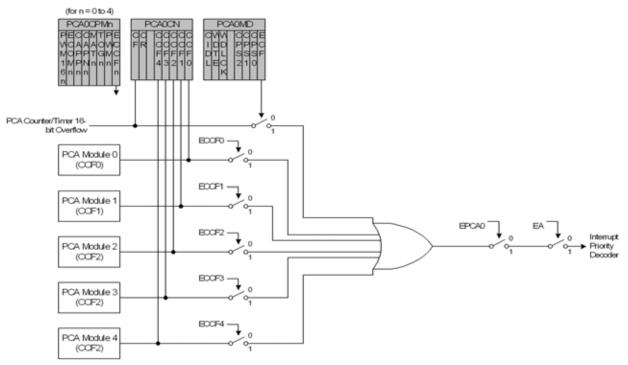

## 27.2. PCA0 Interrupt Sources

Figure 27.3 shows a diagram of the PCA interrupt tree. There are six independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter and the individual flags for each PCA channel (CCF0, CCF1, CCF2, CCF3, and CCF4), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

Figure 27.3. PCA Interrupt Block Diagram

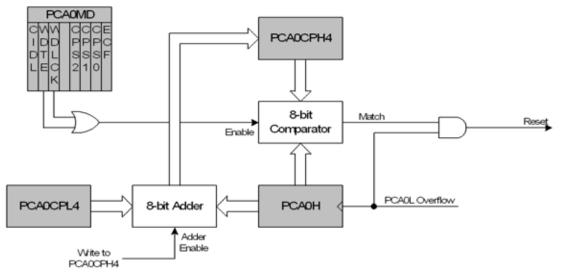

### 27.4. Watchdog Timer Mode

A programmable watchdog timer (WDT) function is available through the PCA Module 4. The WDT is used to generate a reset if the time between writes to the WDT update register (PCA0CPH4) exceed a specified limit. The WDT can be configured and enabled/disabled as needed by software.

With the WDTE bit set in the PCA0MD register, Module 4 operates as a watchdog timer (WDT). The Module 4 high byte is compared to the PCA counter high byte; the Module 4 low byte holds the offset to be used when WDT updates are performed. The Watchdog Timer is enabled on reset. Writes to some PCA registers are restricted while the Watchdog Timer is enabled. The WDT will generate a reset shortly after code begins execution. To avoid this reset, the WDT should be explicitly disabled (and optionally re-configured and re-enabled if it is used in the system).

#### 27.4.1. Watchdog Timer Operation

While the WDT is enabled:

- PCA counter is forced on.

- Writes to PCA0L and PCA0H are not allowed.

- PCA clock source bits (CPS2–CPS0) are frozen.

- PCA Idle control bit (CIDL) is frozen.

- Module 4 is forced into software timer mode.

- Writes to the Module 4 mode register (PCA0CPM4) are disabled.

While the WDT is enabled, writes to the CR bit will not change the PCA counter state; the counter will run until the WDT is disabled. The PCA counter run control bit (CR) will read zero if the WDT is enabled but user software has not enabled the PCA counter. If a match occurs between PCA0CPH4 and PCA0H while the WDT is enabled, a reset will be generated. To prevent a WDT reset, the WDT may be updated with a write of any value to PCA0CPH4. Upon a PCA0CPH4 write, PCA0H plus the offset held in PCA0CPL4 is loaded into PCA0CPH4 (See Figure 27.10).

Figure 27.10. PCA Module 4 with Watchdog Timer Enabled

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com