# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48 MIPS                                                        |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART, USB                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 40                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f386-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 14. External Data Memory Interface and On-Chip XRAM                     | 93    |

|-------------------------------------------------------------------------|-------|

| 14.1. Accessing XRAM                                                    |       |

| 14.1.1. 16-Bit MOVX Example                                             | 93    |

| 14.1.2. 8-Bit MOVX Example                                              |       |

| 14.2. Accessing USB FIFO Space                                          |       |

| 14.3. Configuring the External Memory Interface                         | 95    |

| 14.4. Port Configuration                                                |       |

| 14.5. Multiplexed and Non-multiplexed Selection                         | 98    |

| 14.5.1. Multiplexed Configuration                                       |       |

| 14.5.2. Non-multiplexed Configuration                                   |       |

| 14.6. Memory Mode Selection                                             |       |

| 14.6.1. Internal XRAM Only                                              |       |

| 14.6.2. Split Mode without Bank Select                                  |       |

| 14.6.3. Split Mode with Bank Select                                     |       |

| 14.6.4. External Only                                                   |       |

| 14.7. Timing                                                            |       |

| 14.7.1. Non-multiplexed Mode                                            |       |

| 14.7.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111                   |       |

| 14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111      |       |

| 14.7.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110                |       |

| 14.7.2. Multiplexed Mode                                                | . 107 |

| 14.7.2.1. 16-bit MOVX: EMIOCF[4:2] = 001, 010, or 011                   | . 107 |

| 14.7.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011      |       |

| 14.7.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010                |       |

| 15. Special Function Registers                                          |       |

| 15.1. 13.1. SFR Paging                                                  |       |

| 16. Interrupts                                                          |       |

| 16.1. MCU Interrupt Sources and Vectors<br>16.1.1. Interrupt Priorities |       |

| 16.1.2. Interrupt Latency                                               |       |

| 16.2. Interrupt Register Descriptions                                   |       |

| 16.3. INT0 and INT1 External Interrupt Sources                          |       |

| 17. Reset Sources                                                       |       |

| 17.1. Power-On Reset                                                    |       |

| 17.2. Power-Fail Reset / VDD Monitor                                    |       |

| 17.3. External Reset                                                    |       |

| 17.4. Missing Clock Detector Reset                                      |       |

| 17.5. Comparator0 Reset                                                 |       |

| 17.6. PCA Watchdog Timer Reset                                          |       |

| 17.7. Flash Error Reset                                                 |       |

| 17.8. Software Reset                                                    |       |

| 17.9. USB Reset                                                         |       |

| 18. Flash Memory                                                        | . 135 |

| 18.1. Programming The Flash Memory                                      | . 135 |

| 18.1.1. Flash Lock and Key Functions                                    | . 135 |

| SFR Definition 19.2. OSCICL: Internal H-F Oscillator Calibration          | . 145 |

|---------------------------------------------------------------------------|-------|

| SFR Definition 19.3. OSCICN: Internal H-F Oscillator Control              | . 146 |

| SFR Definition 19.4. CLKMUL: Clock Multiplier Control                     |       |

| SFR Definition 19.5. OSCLCN: Internal L-F Oscillator Control              | . 148 |

| SFR Definition 19.6. OSCXCN: External Oscillator Control                  | . 152 |

| SFR Definition 20.1. XBR0: Port I/O Crossbar Register 0                   | . 159 |

| SFR Definition 20.2. XBR1: Port I/O Crossbar Register 1                   | . 160 |

| SFR Definition 20.3. XBR2: Port I/O Crossbar Register 2                   | . 161 |

| SFR Definition 20.4. P0: Port 0                                           |       |

| SFR Definition 20.5. P0MDIN: Port 0 Input Mode                            | . 162 |

| SFR Definition 20.6. P0MDOUT: Port 0 Output Mode                          | . 163 |

| SFR Definition 20.7. P0SKIP: Port 0 Skip                                  |       |

| SFR Definition 20.8. P1: Port 1                                           |       |

| SFR Definition 20.9. P1MDIN: Port 1 Input Mode                            |       |

| SFR Definition 20.10. P1MDOUT: Port 1 Output Mode                         | . 165 |

| SFR Definition 20.11. P1SKIP: Port 1 Skip                                 | . 165 |

| SFR Definition 20.12. P2: Port 2                                          |       |

| SFR Definition 20.13. P2MDIN: Port 2 Input Mode                           | . 166 |

| SFR Definition 20.14. P2MDOUT: Port 2 Output Mode                         | . 167 |

| SFR Definition 20.15. P2SKIP: Port 2 Skip                                 | . 167 |

| SFR Definition 20.16. P3: Port 3                                          |       |

| SFR Definition 20.17. P3MDIN: Port 3 Input Mode                           | . 168 |

| SFR Definition 20.18. P3MDOUT: Port 3 Output Mode                         | . 169 |

| SFR Definition 20.19. P3SKIP: Port 3 Skip                                 | . 169 |

| SFR Definition 20.20. P4: Port 4                                          |       |

| SFR Definition 20.21. P4MDIN: Port 4 Input Mode                           | . 170 |

| SFR Definition 20.22. P4MDOUT: Port 4 Output Mode                         | . 171 |

| SFR Definition 21.1. USB0XCN: USB0 Transceiver Control                    | . 174 |

| SFR Definition 21.2. USB0ADR: USB0 Indirect Address                       | . 176 |

| SFR Definition 21.3. USB0DAT: USB0 Data                                   | . 177 |

| USB Register Definition 21.4. INDEX: USB0 Endpoint Index                  |       |

| USB Register Definition 21.5. CLKREC: Clock Recovery Control              | . 180 |

| USB Register Definition 21.6. FIFOn: USB0 Endpoint FIFO Access            |       |

| USB Register Definition 21.7. FADDR: USB0 Function Address                | . 183 |

| USB Register Definition 21.8. POWER: USB0 Power                           |       |

| USB Register Definition 21.9. FRAMEL: USB0 Frame Number Low               | . 186 |

| USB Register Definition 21.10. FRAMEH: USB0 Frame Number High             | . 186 |

| USB Register Definition 21.11. IN1INT: USB0 IN Endpoint Interrupt         | . 187 |

| USB Register Definition 21.12. OUT1INT: USB0 OUT Endpoint Interrupt       | . 188 |

| USB Register Definition 21.13. CMINT: USB0 Common Interrupt               | . 189 |

| USB Register Definition 21.14. IN1IE: USB0 IN Endpoint Interrupt Enable   | . 190 |

| USB Register Definition 21.15. OUT1IE: USB0 OUT Endpoint Interrupt Enable | . 191 |

| USB Register Definition 21.16. CMIE: USB0 Common Interrupt Enable         | . 192 |

| USB Register Definition 21.17. E0CSR: USB0 Endpoint0 Control              | . 195 |

| USB Register Definition 21.18. E0CNT: USB0 Endpoint0 Data Count           |       |

| -                                                                         |       |

#### 2.1. Hardware Incompatibilities

While the C8051F38x family includes a number of new features not found on the C8051F34x family, there are some differences that should be considered for any design port.

- Clock Multiplier: The C8051F38x does not include the 4x clock multiplier from the C8051F34x device families. This change only impacts systems which use the clock multiplier in conjunction with an external oscillator source.

- External Oscillator C and RC Modes: The C and RC modes of the oscillator have a divide-by-2 stage on the C8051F38x to aid in noise immunity. This was not present on the C8051F34x device family, and any clock generated with C or RC mode will change accordingly.

- **Fab Technology**: The C8051F38x is manufactured using a different technology process than the C8051F34x. As a result, many of the electrical performance parameters will have subtle differences. These differences should not affect most systems but it is nonetheless important to review the electrical parameters for any blocks that are used in the design, and ensure they are compatible with the existing hardware.

## 4. Typical Connection Diagrams

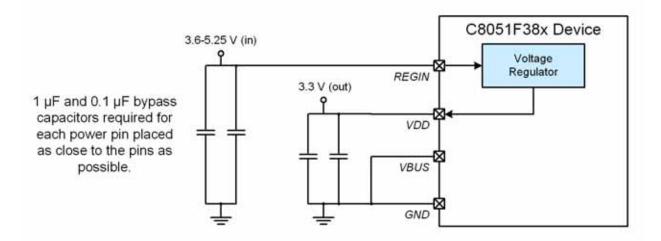

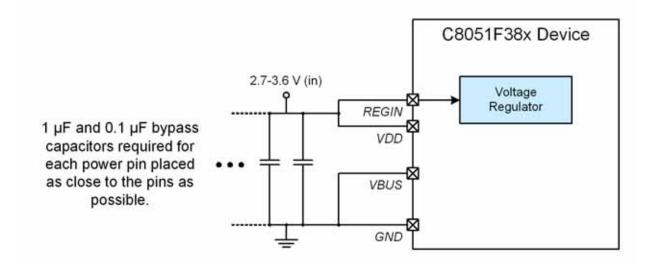

This section provides typical connection diagrams for C8051F38x devices.

#### 4.1. Power

Figure 4.1 shows a typical connection diagram for the power pins of the C8051F38x devices when the internal regulator is in use and USB is not used.

Figure 4.1. Connection Diagram with Voltage Regulator Used and No USB

Figure 4.2 shows a typical connection diagram for the power pins of the C8051F38x devices when the internal regulator and USB are not used.

Figure 4.2. Connection Diagram with Voltage Regulator Not Used and No USB

Figure 4.3 shows a typical connection diagram for the power pins of the C8051F38x devices when the internal regulator used and USB is connected (bus-powered). The VBUS signal is used to detect when

### SFR Definition 6.1. ADC0CF: ADC0 Configuration

| Bit   | 7                           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------------------|---|---|---|---|---|---|---|

| Name  | AD0SC[4:0] AD0LJST Reserved |   |   |   |   |   |   |   |

| Туре  | R/W R/W R/W                 |   |   |   |   |   |   |   |

| Reset | 1                           | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

SFR Address = 0xBC; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                     |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | AD0SC[4:0] | ADC0 SAR Conversion Clock Period Bits.                                                                                                                                                                                       |

|     |            | SAR Conversion clock is derived from system clock by the following equation, where <i>AD0SC</i> refers to the 5-bit value held in bits AD0SC4–0. SAR Conversion clock requirements are given in the ADC specification table. |

|     |            | $AD0SC = \frac{SYSCLK}{CLK_{SAR}} - 1$                                                                                                                                                                                       |

|     |            | <b>Note:</b> If the Memory Power Controller is enabled (MPCE = '1'), AD0SC must be set to at least "00001" for proper ADC operation.                                                                                         |

| 2   | AD0LJST    | ADC0 Left Justify Select.                                                                                                                                                                                                    |

|     |            | 0: Data in ADC0H:ADC0L registers are right-justified.                                                                                                                                                                        |

|     |            | 1: Data in ADC0H:ADC0L registers are left-justified.                                                                                                                                                                         |

|     |            | <b>Note:</b> The AD0LJST bit is only valid for 10-bit mode (AD08BE = 0).                                                                                                                                                     |

| 1:0 | Reserved   | Must Write 00b.                                                                                                                                                                                                              |

## **10. Power Management Modes**

The C8051F380/1/2/3/4/5/6/7/C devices have three software programmable power management modes: Idle, Stop, and Suspend. Idle mode and stop mode are part of the standard 8051 architecture, while suspend mode is an enhanced power-saving mode implemented by the high-speed oscillator peripheral.

Idle mode halts the CPU while leaving the peripherals and clocks active. In stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Suspend mode is similar to stop mode in that the internal oscillator is halted, but the device can wake on activity with the USB transceiver. The CPU is not halted in suspend mode, so it can run on another oscillator, if desired. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode and suspend mode consume the least power because the majority of the device is shut down with no clocks active. SFR Definition 10.1 describes the Power Control Register (PCON) used to control the C8051F380/1/2/3/4/5/6/7/C's Stop and Idle power management modes. Suspend mode is controlled by the SUSPEND bit in the OSCICN register (SFR Definition 19.3).

Although the C8051F380/1/2/3/4/5/6/7/C has Idle, Stop, and suspend modes available, more control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off oscillators lowers power consumption considerably, at the expense of reduced functionality.

#### 10.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the hardware to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Therefore, instructions that set the IDLE bit should be followed by an instruction that has two or more opcode bytes, for example:

| <pre>// in `C': PCON  = 0x01; PCON = PCON;</pre>   | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefi-

| Table 11.1. CIP-51 Instruction Set Summ | nary (Continued) |

|-----------------------------------------|------------------|

|-----------------------------------------|------------------|

| Mnemonic             | Description                                | Bytes | Clock<br>Cycles |  |

|----------------------|--------------------------------------------|-------|-----------------|--|

| XRL direct, #data    | Exclusive-OR immediate to direct byte      | 3     | 3               |  |

| CLR A                | Clear A                                    | 1     | 1               |  |

| CPLA                 | Complement A                               | 1     | 1               |  |

| RL A                 | Rotate A left                              | 1     | 1               |  |

| RLC A                | Rotate A left through Carry                | 1     | 1               |  |

| RR A                 | Rotate A right                             | 1     | 1               |  |

| RRC A                | Rotate A right through Carry               | 1     | 1               |  |

| SWAP A               | Swap nibbles of A                          | 1     | 1               |  |

| Data Transfer        |                                            |       | 1               |  |

| MOV A, Rn            | Move Register to A                         | 1     | 1               |  |

| MOV A, direct        | Move direct byte to A                      | 2     | 2               |  |

| MOV A, @Ri           | Move indirect RAM to A                     | 1     | 2               |  |

| MOV A, #data         | Move immediate to A                        | 2     | 2               |  |

| MOV Rn, A            | Move A to Register                         | 1     | 1               |  |

| MOV Rn, direct       | Move direct byte to Register               | 2     | 2               |  |

| MOV Rn, #data        | Move immediate to Register                 | 2     | 2               |  |

| MOV direct, A        | Move A to direct byte                      | 2     | 2               |  |

| MOV direct, Rn       | Move Register to direct byte               | 2     | 2               |  |

| MOV direct, direct   | Move direct byte to direct byte            | 3     | 3               |  |

| MOV direct, @Ri      | Move indirect RAM to direct byte           | 2     | 2               |  |

| MOV direct, #data    | Move immediate to direct byte              | 3     | 3               |  |

| MOV @Ri, A           | Move A to indirect RAM                     | 1     | 2               |  |

| MOV @Ri, direct      | Move direct byte to indirect RAM           | 2     | 2               |  |

| MOV @Ri, #data       | Move immediate to indirect RAM             | 2     | 2               |  |

| MOV DPTR, #data16    | Load DPTR with 16-bit constant             | 3     | 3               |  |

| MOVC A, @A+DPTR      | Move code byte relative DPTR to A          | 1     | 3               |  |

| MOVC A, @A+PC        | Move code byte relative PC to A            | 1     | 3               |  |

| MOVX A, @Ri          | Move external data (8-bit address) to A    | 1     | 3               |  |

| MOVX @Ri, A          | Move A to external data (8-bit address)    | 1     | 3               |  |

| MOVX A, @DPTR        | Move external data (16-bit address) to A   | 1     | 3               |  |

| MOVX @DPTR, A        | Move A to external data (16-bit address)   | 1     | 3               |  |

| PUSH direct          | Push direct byte onto stack                | 2     | 2               |  |

| POP direct           | Pop direct byte from stack                 | 2     | 2               |  |

| XCH A, Rn            | Exchange Register with A                   | 1     | 1               |  |

| XCH A, direct        | Exchange direct byte with A                | 2     | 2               |  |

| XCHA, @Ri            | Exchange indirect RAM with A               | 1     | 2               |  |

| XCHD A, @Ri          | Exchange low nibble of indirect RAM with A | 1     | 2               |  |

| Boolean Manipulation |                                            |       |                 |  |

| CLR C                | Clear Carry                                | 1     | 1               |  |

| CLR bit              | Clear direct bit                           | 2     | 2               |  |

| SETB C               | Set Carry                                  | 1     | 1               |  |

| SETB bit             | Set direct bit                             | 2     | 2               |  |

| CPL C                | Complement Carry                           | 1     | 1               |  |

| CPL bit              | Complement direct bit                      | 2     | 2               |  |

## 14. External Data Memory Interface and On-Chip XRAM

4 kB (C8051F380/1/4/5) or 2 kB (C8051F382/3/6/7/C) of RAM are included on-chip, and mapped into the external data memory space (XRAM). The 1 kB of USB FIFO space can also be mapped into XRAM address space for additional general-purpose data storage. Additionally, an External Memory Interface (EMIF) is available on the C8051F380/2/4/6 devices, which can be used to access off-chip data memories and memory-mapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using the MOVX indirect addressing mode using R0 or R1. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMIOCN, shown in SFR Definition 14.1). Note: the MOVX instruction can also be used for writing to the FLASH memory. See Section "18. Flash Memory" on page 135 for details. The MOVX instruction accesses XRAM by default.

#### 14.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read from or written to. The second method uses R0 or R1 in combination with the EMI0CN register to generate the effective XRAM address. Examples of both of these methods are given below.

#### 14.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

| MOV  | DPTR, #1234h | ; load DPTR with 16-bit address to read (0x1234 | ) |

|------|--------------|-------------------------------------------------|---|

| MOVX | A, @DPTR     | ; load contents of 0x1234 into accumulator A    |   |

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 14.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of the EMI0CN SFR to determine the upper 8-bits of the effective address to be accessed and the contents of R0 or R1 to determine the lower 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x1234 into the accumulator A.

| MOV  | EMIOCN, #12h | ; load high byte of address into EMIOCN      |  |

|------|--------------|----------------------------------------------|--|

| MOV  | R0, #34h     | ; load low byte of address into RO (or R1)   |  |

| MOVX | a, @R0       | ; load contents of 0x1234 into accumulator A |  |

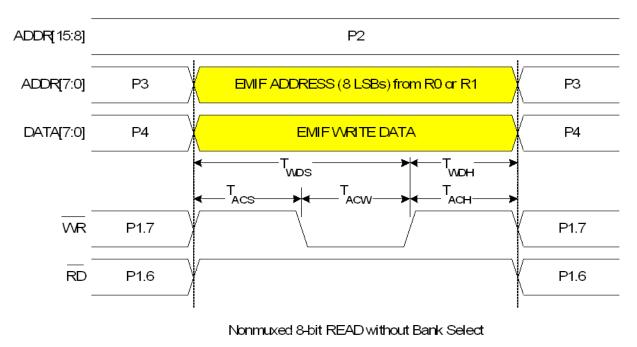

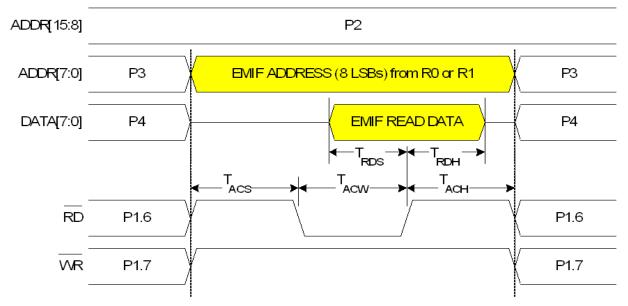

#### 14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111

Nonmuxed 8-bit WRITE without Bank Select

## 18. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operation is not required. Code execution is stalled during a Flash write/erase operation.

#### 18.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Labs or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "28. C2 Interface" on page 316.

To ensure the integrity of Flash contents, it is strongly recommended that the  $V_{DD}$  monitor be left enabled in any system which writes or erases Flash memory from code. It is also crucial to ensure that the FLRT bit in register FLSCL be set to '1' if a clock speed higher than 25 MHz is being used for the device.

#### 18.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 18.2.

#### 18.1.2. Flash Erase Procedure

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by: (1) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY); and (2) Setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed must be erased before a new value is written. The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- 1. Disable interrupts (recommended).

- 2. Write the first key code to FLKEY: 0xA5.

- 3. Write the second key code to FLKEY: 0xF1.

- 4. Set the PSEE bit (register PSCTL).

- 5. Set the PSWE bit (register PSCTL).

- 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- 7. Clear the PSWE bit (register PSCTL).

- 8. Clear the PSEE bit (register PSCTI).

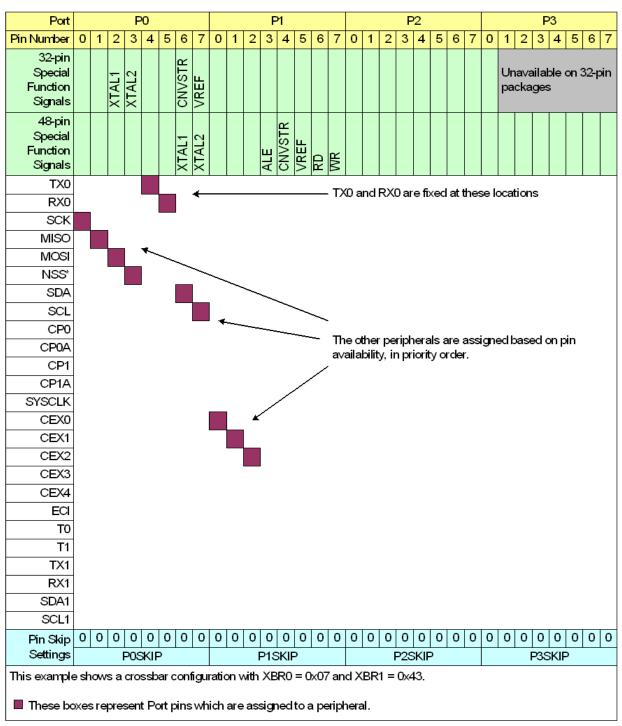

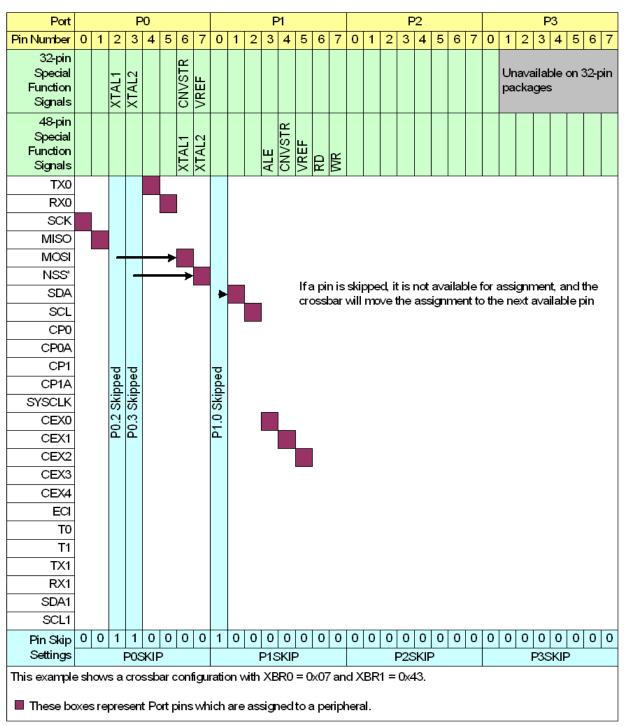

## Figure 20.4. Crossbar Priority Decoder in Example Configuration (No Pins Skipped)

Figure 20.5. Crossbar Priority Decoder in Example Configuration (3 Pins Skipped)

### SFR Definition 20.22. P4MDOUT: Port 4 Output Mode

| Bit                                      | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|--------------|-----|---|---|---|---|---|---|

| Name                                     | P4MDOUT[7:0] |     |   |   |   |   |   |   |

| Туре                                     |              | R/W |   |   |   |   |   |   |

| Reset                                    | t 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0xAE; SFR Page = All Pages |              |     |   |   |   |   |   |   |

| Bit                                      | Name         |     |   |   |   |   |   |   |

| 7:0 | P4MDOUT[7:0] | Output Configuration Bits for P4.7–P4.0 (respectively).                                                                                                                     |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |              | These bits are ignored if the corresponding bit in register P4MDIN is logic 0.<br>0: Corresponding P4.n Output is open-drain.<br>1: Corresponding P4.n Output is push-pull. |

#### 22.4.5. Data Register

The SMBus Data register SMBnDAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SIn flag is set. Software should not attempt to access the SMBnDAT register when the SMBus is enabled and the SIn flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMBnDAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMBnDAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMBnDAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMBnDAT.

#### SFR Definition 22.10. SMB0DAT: SMBus Data

| Bit                              | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------|---|-----------------|---|---|---|---|---|---|

| Name                             |   | SMB0DAT[7:0]    |   |   |   |   |   |   |

| Туре                             |   | R/W             |   |   |   |   |   |   |

| Reset                            | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

| SFR Address = 0xC2; SFR Page = 0 |   |                 |   |   |   |   |   |   |

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus0 Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus0 serial interface or a byte that has just been received on the SMBus0 serial interface. The CPU can read from or write to this register whenever the SI0 serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI0 flag is set. When the SI0 flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |

#### 25.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

#### 25.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 25.5. For slave mode, the clock and data relationships are shown in Figure 25.6 and Figure 25.7. Note that CKPHA should be set to 0 on both the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 25.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

### SFR Definition 26.9. TMR2CN: Timer 2 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1     | 0      |

|-------|------|------|--------|--------|---------|-----|-------|--------|

| Name  | TF2H | TF2L | TF2LEN | TF2CEN | T2SPLIT | TR2 | T2CSS | T2XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/W   | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0     | 0      |

#### SFR Address = 0xC8; SFR Page = 0; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF2H    | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                               |

|     |         | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                            |

| 6   | TF2L    | Timer 2 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                |

|     |         | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                         |

| 5   | TF2LEN  | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                             |

|     |         | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                                                                    |

| 4   | TF2CEN  | Timer 2 Low-Frequency Oscillator Capture Enable.                                                                                                                                                                                                                                                                                                                               |

|     |         | When set to 1, this bit enables Timer 2 Low-Frequency Oscillator Capture Mode. If TF2CEN is set and Timer 2 interrupts are enabled, an interrupt will be generated on a falling edge of the low-frequency oscillator output, and the current 16-bit timer value in TMR2H:TMR2L will be copied to TMR2RLH:TMR2RLL.                                                              |

| 3   | T2SPLIT | Timer 2 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                     |

|     |         | When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.                                                                                                                                                                                                                                                                                                   |

| 2   | TR2     | Timer 2 Run Control.                                                                                                                                                                                                                                                                                                                                                           |

|     |         | Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                                                                    |

| 1   | T2CSS   | Timer 2 Capture Source Select.                                                                                                                                                                                                                                                                                                                                                 |

|     |         | This bit selects the source of a capture event when bit T2CE is set to 1.                                                                                                                                                                                                                                                                                                      |

|     |         | 0: Capture source is USB SOF event.<br>1: Capture source is falling edge of Low-Frequency Oscillator.                                                                                                                                                                                                                                                                          |

| 0   | T2XCLK  | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                 |

|     |         | This bit selects the external clock source for Timer 2. However, the Timer 2 Clock<br>Select bits (T2MH and T2ML in register CKCON) may still be used to select between<br>the external clock and the system clock for either timer.<br>0: Timer 2 clock is the system clock divided by 12.<br>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK). |

### SFR Definition 26.13. TMR2H Timer 2 High Byte

| Bit   | 7             | 6                 | 5        | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------------|-------------------|----------|---|---|---|---|---|--|

| Nam   | e             | TMR2H[7:0]        |          |   |   |   |   |   |  |

| Туре  | 9             | R/W               |          |   |   |   |   |   |  |

| Rese  | et 0          | 0                 | 0        | 0 | 0 | 0 | 0 | 0 |  |

| SFR A | Address = 0xC | D; SFR Page       | e = 0    |   |   |   |   |   |  |

| Bit   | Name          |                   | Function |   |   |   |   |   |  |

| 7:0   | TMR2H[7:0]    | Timer 2 Low Byte. |          |   |   |   |   |   |  |

| L |     |            |                                                                                                                                                     |

|---|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                                                                                   |

|   |     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2H contains the 8-bit high byte timer value. |

### SFR Definition 26.18. TMR3H Timer 3 High Byte

| Bit    | 7                          | 7 6 5 4 3 2 1 0 |   |   |          |   |   |   |  |

|--------|----------------------------|-----------------|---|---|----------|---|---|---|--|

| Name   |                            | TMR3H[7:0]      |   |   |          |   |   |   |  |

| Туре   |                            | R/W             |   |   |          |   |   |   |  |

| Reset  | 0                          | 0               | 0 | 0 | 0        | 0 | 0 | 0 |  |

| SFR Ad | dress = 0x95; SFR Page = 0 |                 |   |   |          |   |   |   |  |

| Dit    | Namo                       |                 |   |   | Eurotion |   |   |   |  |

| Bit | Name       | Function                                                                                                                                        |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3H[7:0] | Timer 3 High Byte.                                                                                                                              |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-bit mode, TMR3H contains the 8-bit high byte timer value. |

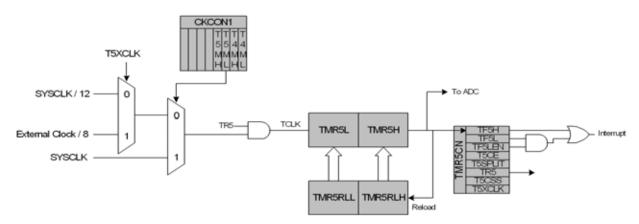

#### 26.5. Timer 5

Timer 5 is a 16-bit timer formed by two 8-bit SFRs: TMR5L (low byte) and TMR5H (high byte). Timer 5 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T5SPLIT bit (TMR5CN.3) defines

Timer 5 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 26.5.1. 16-bit Timer with Auto-Reload

When T5SPLIT (TMR5CN.3) is zero, Timer 5 operates as a 16-bit timer with auto-reload. Timer 5 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 5 reload registers (TMR5RLH and TMR5RLL) is loaded into the Timer 5 register as shown in Figure 26.14, and the Timer 5 High Byte Overflow Flag (TMR5CN.7) is set. If Timer 5 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 5 overflow. Additionally, if Timer 5 interrupts are enabled and the TF5LEN bit is set (TMR5CN.5), an interrupt will be generated each time the lower 8 bits (TMR5L) overflow from 0xFF to 0x00.

Figure 26.14. Timer 5 16-Bit Mode Block Diagram

### C2 Register Definition 28.4. FPCTL: C2 Flash Programming Control

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|----|---|---|---|---|

| Name  |   | FPCTL[7:0]      |   |    |   |   |   |   |

| Туре  |   |                 |   | R/ | W |   |   |   |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |

C2 Address: 0x02

| Bit | Name       | Function                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FPCTL[7:0] | Flash Programming Control Register.                                                                                                                                                                                                                                         |

|     |            | This register is used to enable Flash programming via the C2 interface. To enable C2 Flash programming, the following codes must be written in order: 0x02, 0x01. Note that once C2 Flash programming is enabled, a system reset must be issued to resume normal operation. |

#### C2 Register Definition 28.5. FPDAT: C2 Flash Programming Data

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|---|---|---|---|---|

| Name  |   | FPDAT[7:0]      |   |   |   |   |   |   |

| Туре  |   | R/W             |   |   |   |   |   |   |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

C2 Address: 0xAD

| Bit | Name       |                  | Function                                                                                                                   |  |  |  |

|-----|------------|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0 | FPDAT[7:0] | C2 Flash Program | 2 Flash Programming Data Register.                                                                                         |  |  |  |

|     |            | <b>v</b>         | his register is used to pass Flash commands, addresses, and data during C2 Flash ccesses. Valid commands are listed below. |  |  |  |

|     |            | Code             | Command                                                                                                                    |  |  |  |

|     |            | 0x06             | Flash Block Read                                                                                                           |  |  |  |

|     |            | 0x07             | Flash Block Write                                                                                                          |  |  |  |

|     |            | 0x08             | Flash Page Erase                                                                                                           |  |  |  |

|     |            | 0x03             | Device Erase                                                                                                               |  |  |  |