Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48 MIPS                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f387-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 22.1. Supporting Documents                  |     |

|----|---------------------------------------------|-----|

|    | 22.2. SMBus Configuration                   | 206 |

|    | 22.3. SMBus Operation                       | 206 |

|    | 22.3.1. Transmitter Vs. Receiver            | 207 |

|    | 22.3.2. Arbitration                         | 207 |

|    | 22.3.3. Clock Low Extension                 | 207 |

|    | 22.3.4. SCL Low Timeout                     |     |

|    | 22.3.5. SCL High (SMBus Free) Timeout       |     |

|    | 22.4. Using the SMBus                       |     |

|    | 22.4.1. SMBus Configuration Register        |     |

|    | 22.4.2. SMBus Timing Control Register       |     |

|    | 22.4.3. SMBnCN Control Register             |     |

|    | 22.4.3.1. Software ACK Generation           |     |

|    | 22.4.3.2. Hardware ACK Generation           |     |

|    | 22.4.4. Hardware Slave Address Recognition  |     |

|    | 22.4.5. Data Register                       |     |

|    | 22.5. SMBus Transfer Modes                  |     |

|    | 22.5.1. Write Sequence (Master)             |     |

|    | 22.5.2. Read Sequence (Master)              |     |

|    | 22.5.3. Write Sequence (Slave)              |     |

|    | 22.5.4. Read Sequence (Slave)               |     |

|    | 22.6. SMBus Status Decoding                 |     |

| 23 |                                             |     |

| _0 | 23.1. Enhanced Baud Rate Generation         |     |

|    | 23.2. Operational Modes                     |     |

|    | 23.2.1. 8-Bit UART                          |     |

|    | 23.2.2. 9-Bit UART                          |     |

|    | 23.3. Multiprocessor Communications         |     |

| 24 | UART1                                       |     |

|    | 24.1. Baud Rate Generator                   |     |

|    | 24.2. Data Format                           |     |

|    | 24.3. Configuration and Operation           |     |

|    | 24.3.1. Data Transmission                   |     |

|    | 24.3.2. Data Reception                      |     |

|    | 24.3.3. Multiprocessor Communications       | 244 |

| 25 | Enhanced Serial Peripheral Interface (SPI0) |     |

|    | 25.1. Signal Descriptions                   |     |

|    | 25.1.1. Master Out, Slave In (MOSI)         | 251 |

|    | 25.1.2. Master In, Slave Out (MISO)         | 251 |

|    | 25.1.3. Serial Clock (SCK)                  |     |

|    | 25.1.4. Slave Select (NSS)                  |     |

|    | 25.2. SPI0 Master Mode Operation            |     |

|    | 25.3. SPI0 Slave Mode Operation             |     |

|    | 25.4. SPI0 Interrupt Sources                |     |

|    | 25.5. Serial Clock Phase and Polarity       |     |

|    |                                             |     |

### 6.1. Output Code Formatting

The conversion code format differs between Single-ended and Differential modes. The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.0). When in Single-ended Mode, conversion codes are represented as 10-bit unsigned integers. Inputs are measured from 0 to VREF x 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to 0.

| Input Voltage<br>(Single-Ended) | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |  |  |

|---------------------------------|----------------------------------------------|---------------------------------------------|--|--|

| VREF x 1023/1024                | 0x03FF                                       | 0xFFC0                                      |  |  |

| VREF x 512/1024                 | 0x0200                                       | 0x8000                                      |  |  |

| VREF x 256/1024                 | 0x0100                                       | 0x4000                                      |  |  |

| 0                               | 0x0000                                       | 0x0000                                      |  |  |

When in Differential Mode, conversion codes are represented as 10-bit signed 2s complement numbers. Inputs are measured from –VREF to VREF x 511/512. Example codes are shown below for both right-justified and left-justified data. For right-justified data, the unused MSBs of ADC0H are a sign-extension of the data word. For left-justified data, the unused LSBs in the ADC0L register are set to 0.

| Input Voltage<br>(Differential) | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|---------------------------------|----------------------------------------------|---------------------------------------------|

| VREF x 511/512                  | 0x01FF                                       | 0x7FC0                                      |

| VREF x 256/512                  | 0x0100                                       | 0x4000                                      |

| 0                               | 0x0000                                       | 0x0000                                      |

| -VREF x 256/512                 | 0xFF00                                       | 0xC000                                      |

| -VREF                           | 0xFE00                                       | 0x8000                                      |

### 6.3.2. Tracking Modes

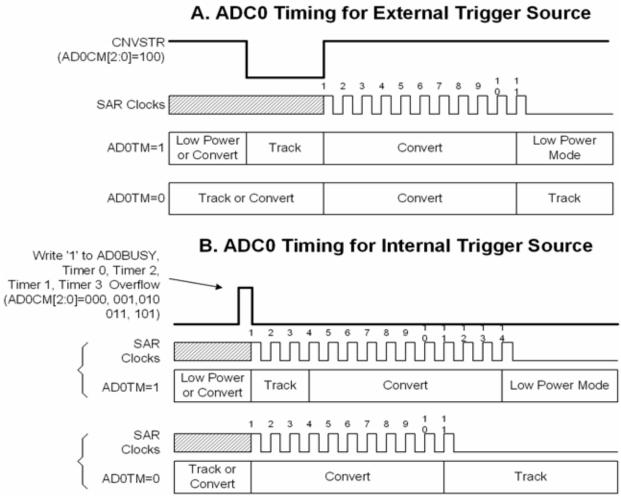

The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state, the ADC0 input is continuously tracked, except when a conversion is in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a track-ing period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR signal is used to initiate conversions in low-power tracking mode, ADC0 tracks only when CNVSTR is low; conversion begins on the rising edge of CNVSTR. See Figure 6.4 for track and convert timing details. Tracking can also be disabled (shutdown) when the device is in low power standby or sleep modes. Low-power track-and-hold mode is also useful when AMUX settings are frequently changed, due to the settling time requirements described in Section "6.3.3. Settling Time Requirements" on page 52.

Figure 6.4. 10-Bit ADC Track and Conversion Example Timing

### SFR Definition 6.1. ADC0CF: ADC0 Configuration

| Bit   | 7         | 6 | 5          | 4       | 3        | 2  | 1 | 0 |

|-------|-----------|---|------------|---------|----------|----|---|---|

| Name  |           |   | AD0SC[4:0] | AD0LJST | Reserved |    |   |   |

| Туре  |           |   | R/W        |         | R/W      | R/ | W |   |

| Reset | 1 1 1 1 1 |   |            |         |          | 0  | 0 | 0 |

SFR Address = 0xBC; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:3 | AD0SC[4:0] | DC0 SAR Conversion Clock Period Bits.                                                                                                                                                                                        |  |  |  |  |  |  |

|     |            | SAR Conversion clock is derived from system clock by the following equation, where <i>AD0SC</i> refers to the 5-bit value held in bits AD0SC4–0. SAR Conversion clock requirements are given in the ADC specification table. |  |  |  |  |  |  |

|     |            | $AD0SC = \frac{SYSCLK}{CLK_{SAR}} - 1$                                                                                                                                                                                       |  |  |  |  |  |  |

|     |            | <b>Note:</b> If the Memory Power Controller is enabled (MPCE = '1'), AD0SC must be set to at least "00001" for proper ADC operation.                                                                                         |  |  |  |  |  |  |

| 2   | AD0LJST    | ADC0 Left Justify Select.                                                                                                                                                                                                    |  |  |  |  |  |  |

|     |            | 0: Data in ADC0H:ADC0L registers are right-justified.                                                                                                                                                                        |  |  |  |  |  |  |

|     |            | 1: Data in ADC0H:ADC0L registers are left-justified.                                                                                                                                                                         |  |  |  |  |  |  |

|     |            | <b>Note:</b> The AD0LJST bit is only valid for 10-bit mode (AD08BE = 0).                                                                                                                                                     |  |  |  |  |  |  |

| 1:0 | Reserved   | Must Write 00b.                                                                                                                                                                                                              |  |  |  |  |  |  |

| Mnemonic                   | Description                                            | Bytes          | Clock<br>Cycles |

|----------------------------|--------------------------------------------------------|----------------|-----------------|

| ANL C, bit                 | AND direct bit to Carry                                | 2              | 2               |

| ANL C, /bit                | AND complement of direct bit to Carry                  | 2              | 2               |

| ORL C, bit                 | OR direct bit to carry                                 | 2              | 2               |

| ORL C, /bit                | OR complement of direct bit to Carry                   | 2              | 2               |

| MOV C, bit                 | Move direct bit to Carry                               | 2              | 2               |

| MOV bit, C                 | Move Carry to direct bit                               | 2              | 2               |

| Program Flow               |                                                        |                |                 |

| Timings are listed with th | e PFE on and FLRT = 0. Extra cycles are required for t | oranches if Fl | _RT = 1.        |

| JC rel                     | Jump if Carry is set                                   | 2              | 2/4             |

| JNC rel                    | Jump if Carry is not set                               | 2              | 2/4             |

| JB bit, rel                | Jump if direct bit is set                              | 3              | 3/5             |

| JNB bit, rel               | Jump if direct bit is not set                          | 3              | 3/5             |

| JBC bit, rel               | Jump if direct bit is set and clear bit                | 3              | 3/5             |

| ACALL addr11               | Absolute subroutine call                               | 2              | 4               |

| LCALL addr16               | Long subroutine call                                   | 3              | 5               |

| RET                        | Return from subroutine                                 | 1              | 6               |

| RETI                       | Return from interrupt                                  | 1              | 6               |

| AJMP addr11                | Absolute jump                                          | 2              | 4               |

| LJMP addr16                | Long jump                                              | 3              | 5               |

| SJMP rel                   | Short jump (relative address)                          | 2              | 4               |

| JMP @A+DPTR                | Jump indirect relative to DPTR                         | 1              | 4               |

| JZ rel                     | Jump if A equals zero                                  | 2              | 2/4             |

| JNZ rel                    | Jump if A does not equal zero                          | 2              | 2/4             |

| CJNE A, direct, rel        | Compare direct byte to A and jump if not equal         | 3              | 4/6             |

| CJNE A, #data, rel         | Compare immediate to A and jump if not equal           | 3              | 3/5             |

| CJNE Rn, #data, rel        | Compare immediate to Register and jump if not equal    | 3              | 3/5             |

| CJNE @Ri, #data, rel       | Compare immediate to indirect and jump if not equal    | 3              | 4/6             |

| DJNZ Rn, rel               | Decrement Register and jump if not zero                | 2              | 2/4             |

| DJNZ direct, rel           | Decrement direct byte and jump if not zero             | 3              | 3/5             |

| NOP                        | No operation                                           | 1              | 1               |

### Table 11.1. CIP-51 Instruction Set Summary (Continued)

### 11.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should always be written to the value indicated in the SFR description. Future product versions may use these bits to implement new features in which case the reset value of the bit will be the indicated value, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

### SFR Definition 11.1. DPL: Data Pointer Low Byte

| Bit   | 7            | 6                                                    | 5           | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|------------------------------------------------------|-------------|---|---|---|---|---|--|--|

| Nam   | ne DPL[7:0]  |                                                      |             |   |   |   |   |   |  |  |

| Туре  | R/W          |                                                      |             |   |   |   |   |   |  |  |

| Rese  | et 0         | 0                                                    | 0           | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A | ddress = 0x8 | 2; SFR Page                                          | = All Pages | - | - |   |   |   |  |  |

| Bit   | Name         |                                                      |             |   |   |   |   |   |  |  |

| 7:0   | DPL[7:0]     | PL[7:0] Data Pointer Low.                            |             |   |   |   |   |   |  |  |

|       |              | The DPL register is the low byte of the 16-bit DPTR. |             |   |   |   |   |   |  |  |

### SFR Definition 11.2. DPH: Data Pointer High Byte

| Bit                                      | 7    | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------------------------------------------|------|----------|---|---|---|---|---|---|--|--|

| Name                                     | •    | DPH[7:0] |   |   |   |   |   |   |  |  |

| Туре                                     |      | R/W      |   |   |   |   |   |   |  |  |

| Reset                                    | 0    | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR Address = 0x83; SFR Page = All Pages |      |          |   |   |   |   |   |   |  |  |

| Bit                                      | Name |          |   |   |   |   |   |   |  |  |

|                                          |      |          |   |   |   |   |   |   |  |  |

| 7:0 | DPH[7:0] | Data Pointer High.                                    |

|-----|----------|-------------------------------------------------------|

|     |          | The DPH register is the high byte of the 16-bit DPTR. |

### 14.5. Multiplexed and Non-multiplexed Selection

The External Memory Interface is capable of acting in a Multiplexed mode or a Non-multiplexed mode, depending on the state of the EMD2 (EMI0CF.4) bit.

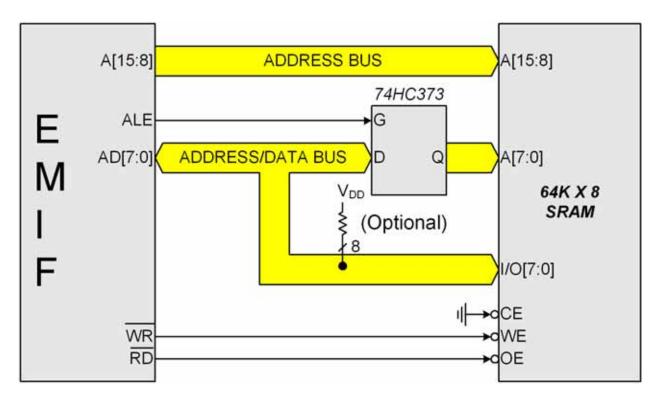

#### 14.5.1. Multiplexed Configuration

In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 14.2.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the 'Q' outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

See Section "14.7.2. Multiplexed Mode" on page 107 for more information.

Figure 14.2. Multiplexed Configuration Example

#### 14.5.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Non-multiplexed Configuration is shown in Figure 14.3. See Section "14.7.1. Non-multiplexed Mode" on page 104 for more information about Non-multiplexed operation.

### Table 15.2. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register             | Address | Page      | Description                 | Page |

|----------------------|---------|-----------|-----------------------------|------|

| SMB1CN               | 0xC0    | F         | SMBus1 Control              | 216  |

| SMB1DAT              | 0xC2    | F         | SMBus1 Data                 | 222  |

| SMBTC                | 0xB9    | F         | SMBus0/1 Timing Control     | 213  |

| SMOD1 0xE5 All Pages |         |           | UART1 Mode                  | 246  |

| SP 0x81 All Pages    |         |           | Stack Pointer               | 86   |

| SPI0CFG              | 0xA1    | All Pages | SPI Configuration           | 257  |

| SPI0CKR              | 0xA2    | All Pages | SPI Clock Rate Control      | 259  |

| SPIOCN 0xF8 A        |         | All Pages | SPI Control                 | 258  |

| SPIODAT              | 0xA3    | All Pages | SPI Data                    | 259  |

| TCON                 | 0x88    | All Pages | Timer/Counter Control       | 270  |

| THO 0x8C All         |         | All Pages | Timer/Counter 0 High        | 273  |

| TH1 0x8D All Page    |         |           | Timer/Counter 1 High        | 273  |

| TLO 0x8A All Pa      |         |           | Timer/Counter 0 Low         | 272  |

| TL1 0x8B All Page    |         |           | Timer/Counter 1 Low         | 272  |

| TMOD 0x89 All Pages  |         | All Pages | Timer/Counter Mode          | 271  |

| TMR2CN               | 0xC8    | 0         | Timer/Counter 2 Control     | 278  |

| TMR2H 0xCD           |         | 0         | Timer/Counter 2 High        | 280  |

| TMR2L 0xCC 0         |         | 0         | Timer/Counter 2 Low         | 279  |

| TMR2RLH              | 0xCB    | 0         | Timer/Counter 2 Reload High | 279  |

| TMR2RLL              | 0xCA    | 0         | Timer/Counter 2 Reload Low  | 279  |

| TMR3CN               | 0x91    | 0         | Timer/Counter 3 Control     | 285  |

| TMR3H                | 0x95    | 0         | Timer/Counter 3 High        | 287  |

| TMR3L                | 0x94    | 0         | Timer/Counter 3 Low         | 286  |

| TMR3RLH              | 0x93    | 0         | Timer/Counter 3 Reload High | 286  |

| TMR3RLL              | 0x92    | 0         | Timer/Counter 3 Reload Low  | 286  |

| TMR4CN               | 0x91    | F         | Timer/Counter 4 Control     | 290  |

| TMR4H                | 0x95    | F         | Timer/Counter 4 High        | 292  |

| TMR4L                | 0x94    | F         | Timer/Counter 4 Low         | 291  |

| TMR4RLH              | 0x93    | F         | Timer/Counter 4 Reload High | 291  |

| TMR4RLL              | 0x92    | F         | Timer/Counter 4 Reload Low  | 291  |

| TMR5CN 0xC8 F        |         | F         | Timer/Counter 5 Control     | 295  |

| TMR5H                | 0xCD    | F         | Timer/Counter 5 High        | 297  |

| TMR5L                | 0xCC    | F         | Timer/Counter 5 Low         | 296  |

| TMR5RLH              | 0xCB    | F         | Timer/Counter 5 Reload High | 296  |

### SFR Definition 19.6. OSCXCN: External Oscillator Control

| Bit   | 7       | 6 | 5         | 4  | 3 | 2 | 1         | 0 |

|-------|---------|---|-----------|----|---|---|-----------|---|

| Name  | XCLKVLD | Х | OSCMD[2:0 | )] |   |   | XFCN[2:0] |   |

| Туре  | R       |   | R/W       |    |   |   | R/W       |   |

| Reset | 0       | 0 | 0         | 0  | 0 | 0 | 0         | 0 |

#### SFR Address = 0xB1; SFR Page = All Pages

| Bit | Name        |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                          | Function                                   |                 |  |  |  |  |  |

|-----|-------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|--|--|--|--|--|

| 7   | XCLKVLD     | Provides<br>tion exc<br>divide b<br>0: Exter                       | Atternal Oscillator Valid Flag.ovides External Oscillator status and is valid at all times for all modes of opera-<br>n except External CMOS Clock Mode and External CMOS Clock Mode with<br>vide by 2. In these modes, XCLKVLD always returns 0.External Oscillator is unused or not yet stable.External Oscillator is running and stable.                                                                              |                                            |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | 00x: Ext<br>010: Ext<br>011: Ext<br>100: RC<br>101: Ca<br>110: Cry | <ul> <li>xernal Oscillator Mode Select.</li> <li>x: External Oscillator circuit off.</li> <li>b: External CMOS Clock Mode.</li> <li>c: External CMOS Clock Mode with divide-by-2 stage.</li> <li>b: RC Oscillator Mode with divide-by-2 stage.</li> <li>c: Capacitor Oscillator Mode with divide-by-2 stage.</li> <li>c: Crystal Oscillator Mode.</li> <li>c: Crystal Oscillator Mode with divide-by-2 stage.</li> </ul> |                                            |                 |  |  |  |  |  |

| 3   | Unused      | Read =                                                             | Read = 0; Write = don't care                                                                                                                                                                                                                                                                                                                                                                                             |                                            |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   | Set acco                                                           | Il Oscillator Frequency<br>ording to the desired freq<br>ording to the desired K Fa                                                                                                                                                                                                                                                                                                                                      | uency for RC mode.                         |                 |  |  |  |  |  |

|     |             | XFCN                                                               | Crystal Mode                                                                                                                                                                                                                                                                                                                                                                                                             | RC Mode                                    | C Mode          |  |  |  |  |  |

|     |             | 000                                                                | f ≤ 20 kHz                                                                                                                                                                                                                                                                                                                                                                                                               | f ≤ 25 kHz                                 | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001                                                                | 20 kHz < f $\leq$ 58 kHz                                                                                                                                                                                                                                                                                                                                                                                                 | $25 \text{ kHz} < f \le 50 \text{ kHz}$    | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010                                                                | 58 kHz < f ≤ 155 kHz                                                                                                                                                                                                                                                                                                                                                                                                     | 50 kHz < f $\leq$ 100 kHz                  | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011                                                                | 155 kHz $<$ f $\leq$ 415 kHz                                                                                                                                                                                                                                                                                                                                                                                             | 100 kHz $<$ f $\leq$ 200 kHz               | K Factor = 22   |  |  |  |  |  |

|     |             | 100                                                                | 415 kHz $<$ f $\leq$ 1.1 MHz                                                                                                                                                                                                                                                                                                                                                                                             | $200 \text{ kHz} < f \leq 400 \text{ kHz}$ | K Factor = 65   |  |  |  |  |  |

|     |             | 101                                                                | $1.1 \text{ MHz} < f \le 3.1 \text{ MHz}$                                                                                                                                                                                                                                                                                                                                                                                | 400 kHz $<$ f $\le$ 800 kHz                | K Factor = 180  |  |  |  |  |  |

|     |             | 110                                                                | $3.1 \text{ MHz} < f \le 8.2 \text{ MHz}$                                                                                                                                                                                                                                                                                                                                                                                | 800 kHz $< f \le 1.6$ MHz                  | K Factor = 664  |  |  |  |  |  |

|     |             | 111                                                                | $8.2 \text{ MHz} < f \le 25 \text{ MHz}$                                                                                                                                                                                                                                                                                                                                                                                 | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$  | K Factor = 1590 |  |  |  |  |  |

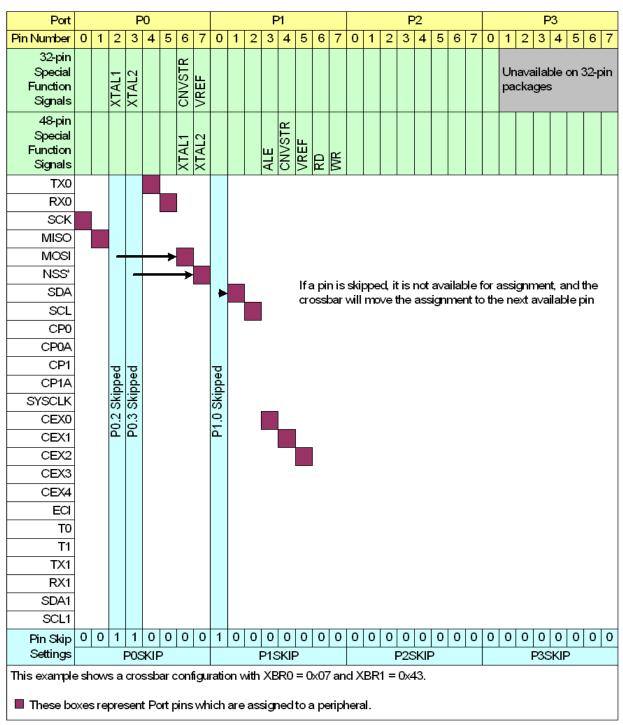

Figure 20.5. Crossbar Priority Decoder in Example Configuration (3 Pins Skipped)

### SFR Definition 20.12. P2: Port 2

| Bit   | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|---------------|---|---|---|---|---|---|--|--|--|

| Name  |   | P2[7:0]       |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W           |   |   |   |   |   |   |  |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |  |

SFR Address = 0xA0; SFR Page = All Pages; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P2[7:0] | <b>Port 2 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P2.n Port pin is logic<br>LOW.<br>1: P2.n Port pin is logic<br>HIGH. |

### SFR Definition 20.13. P2MDIN: Port 2 Input Mode

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|

| Name  |   | P2MDIN[7:0]     |   |   |   |   |   |   |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |

#### SFR Address = 0xF3; SFR Page = All Pages

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDIN[7:0] | Analog Configuration Bits for P2.7–P2.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P2.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P2.n pin is not configured for analog mode.                                                |

## SFR Definition 21.1. USB0XCN: USB0 Transceiver Control

| Bit   | 7             | 6                                                       | 5                                                                                                                                                                                                                                                                                                                                               | 4                                                                  | 3                            | 2               | 1            | 0         |  |  |  |

|-------|---------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------|-----------------|--------------|-----------|--|--|--|

| Nam   | e PREN        | PHYEN                                                   | SPEED                                                                                                                                                                                                                                                                                                                                           | PHYT                                                               | ST[1:0]                      | DFREC           | Dp           | Dn        |  |  |  |

| Туре  | R/W           | R/W                                                     | R/W                                                                                                                                                                                                                                                                                                                                             | R                                                                  | W                            | R               | R            | R         |  |  |  |

| Rese  | et O          | 0                                                       | 0                                                                                                                                                                                                                                                                                                                                               | 0                                                                  | 0                            | 0               | 0            | 0         |  |  |  |

| SFR A | ddress = 0xD7 | 7; SFR Page                                             | = All Pages                                                                                                                                                                                                                                                                                                                                     | 5                                                                  |                              | •               |              |           |  |  |  |

| Bit   | Name          |                                                         | Function                                                                                                                                                                                                                                                                                                                                        |                                                                    |                              |                 |              |           |  |  |  |

| 7     | PREN          | The locatio<br>0: Internal p<br>1: Internal p           | <ul> <li>hternal Pull-up Resistor Enable.</li> <li>The location of the pull-up resistor (D+ or D-) is determined by the SPEED bit.</li> <li>Internal pull-up resistor disabled (device effectively detached from USB network).</li> <li>Internal pull-up resistor enabled when VBUS is present (device attached to the USB network).</li> </ul> |                                                                    |                              |                 |              |           |  |  |  |

| 6     | PHYEN         | 0: USB0 ph                                              | hysical Layer Enable.<br>USB0 physical layer Transceiver disabled (suspend).<br>USB0 physical layer Transceiver enabled (normal).                                                                                                                                                                                                               |                                                                    |                              |                 |              |           |  |  |  |

| 5     | SPEED         | This bit sele<br>0: USB0 op<br>appears on<br>1: USB0 op | USB0 Speed Select.<br>This bit selects the USB0 speed.<br>0: USB0 operates as a Low Speed device. If enabled, the internal pull-up resistor<br>appears on the D– line.<br>1: USB0 operates as a Full Speed device. If enabled, the internal pull-up resistor<br>appears on the D+ line.                                                         |                                                                    |                              |                 |              |           |  |  |  |

| 4:3   | PHYTST[1:0]   | 00: Mode 0<br>01: Mode 1<br>10: Mode 2                  | : Differential<br>: Differential                                                                                                                                                                                                                                                                                                                | its.<br>on-test mode<br>1 Forced (E<br>0 Forced (E<br>led 0 Forced | 0+ = 1, D- =<br>0+ = 0, D- = | 0)<br>1)        |              |           |  |  |  |

| 2     | DFREC         | The state o<br>lines when<br>0: Different               | PHYEN = 1<br>ial 0 signalliı                                                                                                                                                                                                                                                                                                                    | cates the cu                                                       | S.                           | ntial value pre | esent on the | D+ and D- |  |  |  |

| 1     | Dp            | This bit indi<br>0: D+ signa                            | <b>D+ Signal Status.</b><br>This bit indicates the current logic level of the D+ pin.<br>0: D+ signal currently at logic 0.<br>1: D+ signal currently at logic 1.                                                                                                                                                                               |                                                                    |                              |                 |              |           |  |  |  |

| 0     | Dn            | 0: D- signal                                            |                                                                                                                                                                                                                                                                                                                                                 | -                                                                  | evel of the D                | - pin.          |              |           |  |  |  |

### 21.6. Function Addressing

The FADDR register holds the current USB0 function address. Software should write the host-assigned 7bit function address to the FADDR register when received as part of a SET\_ADDRESS command. A new address written to FADDR will not take effect (USB0 will not respond to the new address) until the end of the current transfer (typically following the status phase of the SET\_ADDRESS command transfer). The UPDATE bit (FADDR.7) is set to 1 by hardware when software writes a new address to the FADDR register. Hardware clears the UPDATE bit when the new address takes effect as described above.

### USB Register Definition 21.7. FADDR: USB0 Function Address

| Bit   | 7      | 6 | 5          | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------|---|------------|---|---|---|---|---|--|

| Name  | UPDATE |   | FADDR[6:0] |   |   |   |   |   |  |

| Туре  | R      |   | R/W        |   |   |   |   |   |  |

| Reset | 0      | 0 | 0          | 0 | 0 | 0 | 0 | 0 |  |

USB Register Address = 0x00

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                 |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | UPDATE     | <ul> <li>Function Address Update Bit.</li> <li>Set to 1 when software writes the FADDR register. USB0 clears this bit to 0 when the new address takes effect.</li> <li>0: The last address written to FADDR is in effect.</li> <li>1: The last address written to FADDR is not yet in effect.</li> </ul> |

| 6:0 | FADDR[6:0] | <b>Function Address Bits.</b><br>Holds the 7-bit function address for USB0. This address should be written by software when the SET_ADDRESS standard device request is received on Endpoint0. The new address takes effect when the device request completes.                                            |

### 21.7. Function Configuration and Control

The USB register POWER (USB Register Definition 21.8) is used to configure and control USB0 at the device level (enable/disable, Reset/Suspend/Resume handling, etc.).

USB Reset: The USBRST bit (POWER.3) is set to 1 by hardware when Reset signaling is detected on the bus. Upon this detection, the following occur:

- 1. The USB0 Address is reset (FADDR = 0x00).

- 2. Endpoint FIFOs are flushed.

- 3. Control/status registers are reset to 0x00 (E0CSR, EINCSRL, EINCSRH, EOUTCSRL, EOUTCSRH).

- 4. USB register INDEX is reset to 0x00.

- 5. All USB interrupts (excluding the Suspend interrupt) are enabled and their corresponding flags cleared.

- 6. A USB Reset interrupt is generated if enabled.

Writing a 1 to the USBRST bit will generate an asynchronous USB0 reset. All USB registers are reset to their default values following this asynchronous reset.

**Suspend Mode:** With Suspend Detection enabled (SUSEN = 1), USB0 will enter Suspend Mode when Suspend signaling is detected on the bus. An interrupt will be generated if enabled (SUSINTE = 1). The

## 22. SMBus0 and SMBus1 (I<sup>2</sup>C Compatible)

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus. The C8051F380/1/2/3/4/5/6/7/C devices contain two SMBus interfaces, SMBus0 and SMBus1.

Reads and writes to the SMBus by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock as a master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

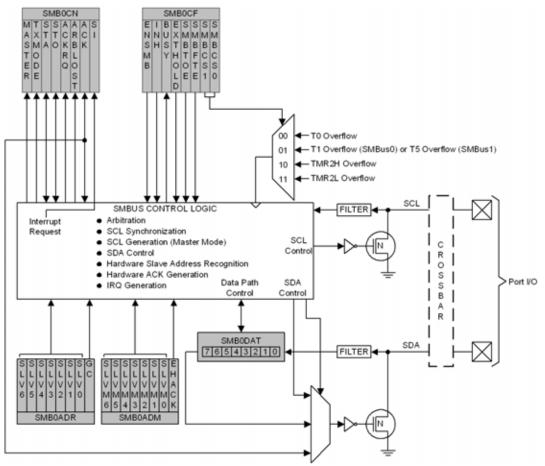

The SMBus may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. The SMBus peripherals can be fully driven by software (i.e., software accepts/rejects slave addresses, and generates ACKs), or hardware slave address recognition and automatic ACK generation can be enabled to minimize software overhead. A block diagram of the SMBus0 peripheral and the associated SFRs is shown in Figure 22.1. SMBus1 is identical, with the exception of the available timer options for the clock source, and the timer used to implement the SCL low time-out feature. Refer to the specific SFR definitions for more details.

Figure 22.1. SMBus Block Diagram

### SFR Definition 22.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7      | 6    | 5     | 4        | 3       | 2       | 1           | 0 |

|-------|--------|------|-------|----------|---------|---------|-------------|---|

| Name  | ENSMB0 | INH0 | BUSY0 | EXTHOLD0 | SMB0TOE | SMB0FTE | SMB0CS[1:0] |   |

| Туре  | R/W    | R/W  | R     | R/W      | R/W     | R/W     | R/W         |   |

| Reset | 0      | 0    | 0     | 0        | 0       | 0       | 0           | 0 |

### SFR Address = 0xC1; SFR Page = 0

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB0      | SMBus0 Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |             | This bit enables the SMBus0 interface when set to 1. When enabled, the interface constantly monitors the SDA0 and SCL0 pins.                                                                                                                                                                                                                                                                                                                    |

| 6   | INH0        | SMBus0 Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |             | When this bit is set to logic 1, the SMBus0 does not generate an interrupt when slave events occur. This effectively removes the SMBus0 slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                            |

| 5   | BUSY0       | SMBus0 Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |             | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                          |

| 4   | EXTHOLD0    | SMBus0 Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |             | <ul><li>This bit controls the SDA0 setup and hold times according to Table 22.2.</li><li>0: SDA0 Extended Setup and Hold Times disabled.</li><li>1: SDA0 Extended Setup and Hold Times enabled.</li></ul>                                                                                                                                                                                                                                       |

| 3   | SMB0TOE     | SMBus0 SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   |             | This bit enables SCL low timeout detection. If set to logic 1, the SMBus0 forces<br>Timer 3 to reload while SCL0 is high and allows Timer 3 to count when SCL0 goes<br>low. If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in<br>reload while SCL0 is high. Timer 3 should be programmed to generate interrupts at<br>25 ms, and the Timer 3 interrupt service routine should reset SMBus0 communica-<br>tion. |

| 2   | SMB0FTE     | SMBus0 Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |             | When this bit is set to logic 1, the bus will be considered free if SCL0 and SDA0 remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                                      |

| 1:0 | SMB0CS[1:0] | SMBus0 Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |             | These two bits select the SMBus0 clock source, which is used to generate the<br>SMBus0 bit rate. The selected device should be configured according to<br>Equation 22.1.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow<br>10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow                                                                                                                                                     |

## SFR Definition 24.2. SMOD1: UART1 Mode

| Bit   | 7           | 6                                                                  | 5                                                                    | 4                      | 3          | 2              | 1                | 0            |  |

|-------|-------------|--------------------------------------------------------------------|----------------------------------------------------------------------|------------------------|------------|----------------|------------------|--------------|--|

| Nam   | e MCE1      | S1P                                                                | [1:0]                                                                | PE1                    | S1D        | L[1:0]         | XBE1             | SBL1         |  |

| Туре  | e R/W       | R/                                                                 | W                                                                    | R/W                    | R          | /W             | R/W              | R/W          |  |

| Rese  | et 0        | 0                                                                  | 0                                                                    | 0                      | 1          | 1              | 0                | 0            |  |

| SFR A | Address = 0 | KE5; SFR Page                                                      | = All Pages                                                          | 5                      |            |                |                  |              |  |

| Bit   | Name        |                                                                    |                                                                      |                        | Function   |                |                  |              |  |

| 7     | MCE1        | Multiprocess                                                       | or Commur                                                            | nication Ena           | able.      |                |                  |              |  |

|       |             | 1: RI will be a<br>XBE1).                                          | ote: This function is not available when hardware parity is enabled. |                        |            |                |                  |              |  |

| 6:5   | S1PT[1:0]   | Parity Type B                                                      | rity Type Bits.                                                      |                        |            |                |                  |              |  |

|       |             | 00: Odd                                                            |                                                                      |                        |            |                |                  |              |  |

|       |             | 01: Even<br>10: Mark                                               |                                                                      |                        |            |                |                  |              |  |

|       |             | 11: Space                                                          |                                                                      |                        |            |                |                  |              |  |

| 4     | PE1         | Parity Enable                                                      | •                                                                    |                        |            |                |                  |              |  |

|       |             | This bit activa<br>by bits S1PT1<br>0: Hardware p<br>1: Hardware p | -0 when par<br>arity is disat                                        | ity is enable<br>bled. |            | checking. The  | e parity type    | is selected  |  |

| 3:2   | S1DL[1:0]   | Data Length.                                                       |                                                                      |                        |            |                |                  |              |  |

|       |             | 00: 5-bit data                                                     |                                                                      |                        |            |                |                  |              |  |

|       |             | 01: 6-bit data<br>10: 7-bit data                                   |                                                                      |                        |            |                |                  |              |  |

|       |             | 11: 8-bit data                                                     |                                                                      |                        |            |                |                  |              |  |

| 1     | XBE1        | Extra Bit Ena                                                      | ble.                                                                 |                        |            |                |                  |              |  |

|       |             | When enabled                                                       |                                                                      | of TBX1 will           | be appende | d to the data  | field.           |              |  |

|       |             | 0: Extra Bit Di<br>1: Extra Bit Er                                 |                                                                      |                        |            |                |                  |              |  |

| 0     | SBL1        | Stop Bit Leng                                                      |                                                                      |                        |            |                |                  |              |  |

|       |             | 0: Short—Stor                                                      | -                                                                    | e for one bit          | time.      |                |                  |              |  |

|       |             | 1: Long—Stop<br>(data length =                                     | bit is active                                                        |                        |            | ngth = 6, 7, o | or 8 bits), or 1 | .5 bit times |  |

### SFR Definition 25.3. SPI0CKR: SPI0 Clock Rate

| Bit   | 7            | 6               | 5             | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|-----------------|---------------|---|---|---|---|---|--|--|

| Name  | SCR[7:0]     |                 |               |   |   |   |   |   |  |  |

| Туре  | R/W          |                 |               |   |   |   |   |   |  |  |

| Reset | 0            | 0 0 0 0 0 0 0 0 |               |   |   |   |   |   |  |  |

|       | dress = 0xA2 | 2; SFR Page     | e = All Pages | 5 |   | 5 | 0 |   |  |  |

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                             |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SCR[7:0] | SPI0 Clock Rate.                                                                                                                                                                                                                                                                                                                     |

|     |          | These bits determine the frequency of the SCK output when the SPI0 module is configured for master mode operation. The SCK clock frequency is a divided version of the system clock, and is given in the following equation, where SYSCLK is the system clock frequency and SPI0CKR is the 8-bit value held in the SPI0CKR register. |

|     |          | $f_{SCK} = \frac{SYSCLK}{2 \times (SPIOCKR[7:0] + 1)}$                                                                                                                                                                                                                                                                               |

|     |          | for $0 \leq SPI0CKR \leq 255$                                                                                                                                                                                                                                                                                                        |

|     |          | Example: If SYSCLK = 2 MHz and SPI0CKR = 0x04,                                                                                                                                                                                                                                                                                       |

|     |          | $f_{SCK} = \frac{2000000}{2 \times (4+1)}$                                                                                                                                                                                                                                                                                           |

|     |          | f <sub>SCK</sub> = 200kHz                                                                                                                                                                                                                                                                                                            |

### SFR Definition 25.4. SPI0DAT: SPI0 Data

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | SPI0DAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xA3; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

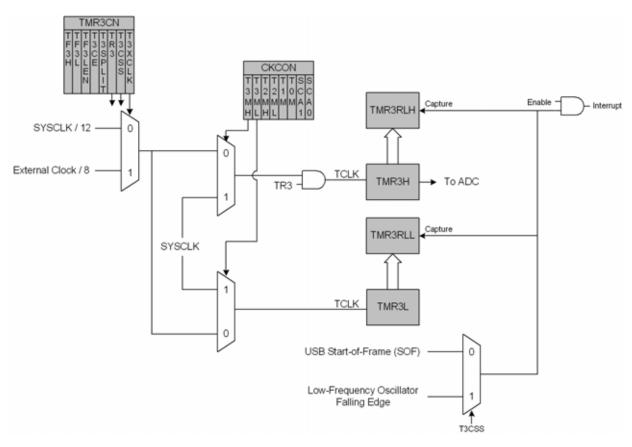

Figure 26.11. Timer 3 Capture Mode (T3SPLIT = 0)

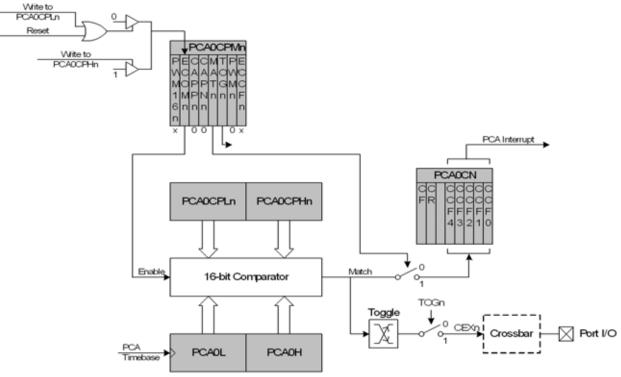

#### 27.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 27.6. PCA High-Speed Output Mode Diagram

### SFR Definition 27.3. PCA0CPMn: PCA Capture/Compare Mode

| Bit   | 7      | 6     | 5     | 4     | 3    | 2    | 1    | 0     |

|-------|--------|-------|-------|-------|------|------|------|-------|

| Name  | PWM16n | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn |

| Туре  | R/W    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W   |

| Reset | 0      | 0     | 0     | 0     | 0    | 0    | 0    | 0     |

SFR Addresses: 0xDA (n = 0), 0xDB (n = 1), 0xDC (n = 2), 0xDD (n = 3), 0xDE (n = 4)

SFR Pages: All Pages (n = 0), All Pages (n = 1), All Pages (n = 2), All Pages (n = 3), All Pages (n = 4)

| Bit   | Name                                                                                                                                                                                                                                            | Function                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7     | PWM16n                                                                                                                                                                                                                                          | 16-bit Pulse Width Modulation Enable.                                                                                                                                                                                                                                                                         |  |  |  |  |

|       |                                                                                                                                                                                                                                                 | This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.<br>0: 8-bit PWM selected.<br>1: 16-bit PWM selected.                                                                                                                                                                                |  |  |  |  |

| 6     | ECOMn                                                                                                                                                                                                                                           | Comparator Function Enable.                                                                                                                                                                                                                                                                                   |  |  |  |  |

|       |                                                                                                                                                                                                                                                 | This bit enables the comparator function for PCA module n when set to 1.                                                                                                                                                                                                                                      |  |  |  |  |

| 5     | CAPPn                                                                                                                                                                                                                                           | Capture Positive Function Enable.                                                                                                                                                                                                                                                                             |  |  |  |  |

|       |                                                                                                                                                                                                                                                 | This bit enables the positive edge capture for PCA module n when set to 1.                                                                                                                                                                                                                                    |  |  |  |  |

| 4     | CAPNn                                                                                                                                                                                                                                           | Capture Negative Function Enable.                                                                                                                                                                                                                                                                             |  |  |  |  |

|       |                                                                                                                                                                                                                                                 | This bit enables the negative edge capture for PCA module n when set to 1.                                                                                                                                                                                                                                    |  |  |  |  |

| 3     | MATn                                                                                                                                                                                                                                            | Match Function Enable.                                                                                                                                                                                                                                                                                        |  |  |  |  |

|       |                                                                                                                                                                                                                                                 | This bit enables the match function for PCA module n when set to 1. When enabled, matches of the PCA counter with a module's capture/compare register cause the CCFn bit in PCA0MD register to be set to logic 1.                                                                                             |  |  |  |  |

| 2     | TOGn                                                                                                                                                                                                                                            | Toggle Function Enable.                                                                                                                                                                                                                                                                                       |  |  |  |  |