Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 48 MIPS                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 2.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                   |

| Data Converters            | A/D 21x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 32-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f38c-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 14. External Data Memory Interface and On-Chip XRAM                     | 93    |

|-------------------------------------------------------------------------|-------|

| 14.1. Accessing XRAM                                                    |       |

| 14.1.1. 16-Bit MOVX Example                                             | 93    |

| 14.1.2. 8-Bit MOVX Example                                              |       |

| 14.2. Accessing USB FIFO Space                                          |       |

| 14.3. Configuring the External Memory Interface                         | 95    |

| 14.4. Port Configuration                                                |       |

| 14.5. Multiplexed and Non-multiplexed Selection                         | 98    |

| 14.5.1. Multiplexed Configuration                                       |       |

| 14.5.2. Non-multiplexed Configuration                                   |       |

| 14.6. Memory Mode Selection                                             |       |

| 14.6.1. Internal XRAM Only                                              |       |

| 14.6.2. Split Mode without Bank Select                                  |       |

| 14.6.3. Split Mode with Bank Select                                     |       |

| 14.6.4. External Only                                                   |       |

| 14.7. Timing                                                            |       |

| 14.7.1. Non-multiplexed Mode                                            |       |

| 14.7.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111                   |       |

| 14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111      |       |

| 14.7.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110                |       |

| 14.7.2. Multiplexed Mode                                                | . 107 |

| 14.7.2.1. 16-bit MOVX: EMIOCF[4:2] = 001, 010, or 011                   | . 107 |

| 14.7.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011      |       |

| 14.7.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010                |       |

| 15. Special Function Registers                                          |       |

| 15.1. 13.1. SFR Paging                                                  |       |

| 16. Interrupts                                                          |       |

| 16.1. MCU Interrupt Sources and Vectors<br>16.1.1. Interrupt Priorities |       |

| 16.1.2. Interrupt Latency                                               |       |

| 16.2. Interrupt Register Descriptions                                   |       |

| 16.3. INT0 and INT1 External Interrupt Sources                          |       |

| 17. Reset Sources                                                       |       |

| 17.1. Power-On Reset                                                    |       |

| 17.2. Power-Fail Reset / VDD Monitor                                    |       |

| 17.3. External Reset                                                    |       |

| 17.4. Missing Clock Detector Reset                                      |       |

| 17.5. Comparator0 Reset                                                 |       |

| 17.6. PCA Watchdog Timer Reset                                          |       |

| 17.7. Flash Error Reset                                                 |       |

| 17.8. Software Reset                                                    |       |

| 17.9. USB Reset                                                         |       |

| 18. Flash Memory                                                        | . 135 |

| 18.1. Programming The Flash Memory                                      | . 135 |

| 18.1.1. Flash Lock and Key Functions                                    | . 135 |

# 1. System Overview

C8051F380/1/2/3/4/5/6/7/C devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 48 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Universal Serial Bus (USB) Function Controller with eight flexible endpoint pipes, integrated transceiver, and 1 kB FIFO RAM

- Supply Voltage Regulator

- True 10-bit 500 ksps differential / single-ended ADC with analog multiplexer

- On-chip Voltage Reference and Temperature Sensor

- On-chip Voltage Comparators (2)

- Precision internal calibrated 48 MHz internal oscillator

- Internal low-frequency oscillator for additional power savings

- Up to 64 kB of on-chip Flash memory

- Up to 4352 Bytes of on-chip RAM (256 + 4 kB)

- External Memory Interface (EMIF) available on 48-pin versions.

- 2 I<sup>2</sup>C/SMBus, 2 UARTs, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Missing Clock Detector

- Up to 40 Port I/O (5 V tolerant)

With on-chip Power-On Reset,  $V_{DD}$  monitor, Voltage Regulator, Watchdog Timer, and clock oscillator, C8051F380/1/2/3/4/5/6/7/C devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 2.7–5.25 V operation over the industrial temperature range (–40 to +85 °C). For voltages above 3.6 V, the on-chip Voltage Regulator must be used. A minimum of 3.0 V is required for USB communication. The Port I/O and RST pins are tolerant of input signals up to 5 V. C8051F380/1/2/3/ 4/5/6/7/C devices are available in 48-pin TQFP, 32-pin LQFP, or 32-pin QFN packages. See Table 1.1, "Product Selection Guide," on page 17 for feature and package choices.

### **Table 5.5. Internal Voltage Regulator Electrical Characteristics**

-40 to +85 °C unless otherwise specified.

| Parameter                                       | Test Condition                               | Min          | Тур          | Max  | Unit  |

|-------------------------------------------------|----------------------------------------------|--------------|--------------|------|-------|

| Voltage Regulator (REG0)                        |                                              |              |              | 1    | -     |

| Input Voltage Range <sup>1</sup>                |                                              | 2.7          |              | 5.25 | V     |

| Output Voltage (V <sub>DD</sub> ) <sup>2</sup>  | Output Current = 1 to 100 mA                 | 3.0          | 3.3          | 3.6  | V     |

| Output Current <sup>2</sup>                     |                                              |              |              | 100  | mA    |

| Dropout Voltage (V <sub>DO</sub> ) <sup>3</sup> |                                              | —            | 1            | —    | mV/mA |

| Voltage Regulator (REG1)                        |                                              |              |              | 1    |       |

| Input Voltage Range                             |                                              | 1.8          | _            | 3.6  | V     |

| Notes:<br>1. Input range specified for          | regulation. When an external regulator is us | sed should l | he tied to ' |      | 1     |

1. Input range specified for regulation. When an external regulator is used, should be tied to  $V_{DD}$ . 2. Output current is total regulator output, including any current required by the C8051F380/1/2/3/4/5/6/7/C. 3. The minimum input voltage is 2.70 V or  $V_{DD} + V_{DO}$  (max load), whichever is greater.

### **Table 5.6. Flash Electrical Characteristics**

| Parameter                             | Test Condition                       | Min          | Тур     | Max  | Unit        |

|---------------------------------------|--------------------------------------|--------------|---------|------|-------------|

| Flash Size                            | C8051F380/1/4/5*                     | 65536*       |         |      | Bytes       |

|                                       | C8051F382/3/6/7                      | 32768        |         |      | Bytes       |

| Endurance                             |                                      | 10k          | 100k    | —    | Erase/Write |

| Erase Cycle Time                      | 25 MHz System Clock                  | 10           | 15      | 22.5 | ms          |

| Write Cycle Time                      | 25 MHz System Clock                  | 10           | 15      | 20   | μs          |

| Notes:<br>1. 1024 bytes at location ( | 0xFC00 to 0xFFFF are not available f | or program s | torage. |      |             |

2. Data Retention Information is published in the Quarterly Quality and Reliability Report.

### Table 5.14. USB Transceiver Electrical Characteristics

$V_{DD}$  = 3.0 V to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameter                                                  | Test Condition                                    | Min            | Тур      | Max       | Unit |

|------------------------------------------------------------|---------------------------------------------------|----------------|----------|-----------|------|

| Transmitter                                                |                                                   |                |          |           |      |

| Output High Voltage (V <sub>OH</sub> )                     |                                                   | 2.8            |          | _         | V    |

| Output Low Voltage (V <sub>OL</sub> )                      |                                                   |                | _        | 0.8       | V    |

| VBUS Detection Input Low<br>Voltage                        |                                                   | -              | _        | 1.0       | V    |

| VBUS Detection Input High<br>Voltage                       |                                                   | 3.0            | _        | _         | V    |

| Output Crossover Point<br>(V <sub>CRS</sub> )              |                                                   | 1.3            |          | 2.0       | V    |

| Output Impedance (Z <sub>DRV</sub> )                       | Driving High<br>Driving Low                       | _              | 38<br>38 | _         | W    |

| Pull-up Resistance (R <sub>PU</sub> )                      | Full Speed (D+ Pull-up)<br>Low Speed (D– Pull-up) | 1.425          | 1.5      | 1.575     | kΩ   |

| Output Rise Time (T <sub>R</sub> )                         | Low Speed<br>Full Speed                           | 75<br>4        |          | 300<br>20 | ns   |

| Output Fall Time (T <sub>F</sub> )                         | Low Speed<br>Full Speed                           | 75<br>4        |          | 300<br>20 | ns   |

| Receiver                                                   |                                                   | ·              |          |           |      |

| Differential Input<br>Sensitivity (V <sub>DI</sub> )       | (D+) – (D–)                                       | 0.2            | _        | _         | V    |

| Differential Input Common<br>Mode Range (V <sub>CM</sub> ) |                                                   | 0.8            | —        | 2.5       | V    |

| Input Leakage Current (IL)                                 | Pullups Disabled                                  | —              | <1.0     | —         | μA   |

| Note: Refer to the USB Specifica                           | ation for timing diagrams and symbo               | l definitions. |          |           | •    |

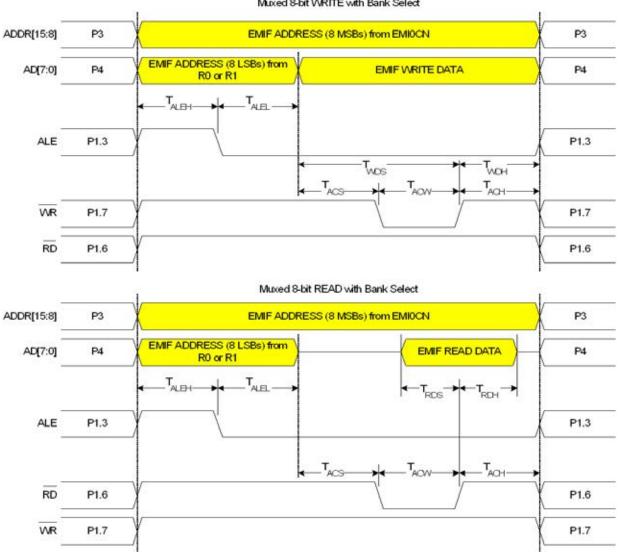

### 14.7.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110

Muxed 8-bit WRITE with Bank Select

Figure 14.7. Non-multiplexed 8-bit MOVX with Bank Select Timing

# SFR Definition 16.7. IT01CF: INT0/INT1 Configuration

| Bit   | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                                                                                                                                                                                                                        | 5                                                                                                                        | 4                                              | 3                               | 2                               | 1                              | 0                          |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------|---------------------------------|--------------------------------|----------------------------|--|--|--|--|--|--|--|--|

| Nam   | e IN1PL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                          | IN1SL[2:0]                                                                                                               |                                                | IN0PL                           |                                 | IN0SL[2:0]                     |                            |  |  |  |  |  |  |  |  |

| Туре  | e R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          | R/W                                                                                                                      |                                                | R/W                             |                                 | R/W                            |                            |  |  |  |  |  |  |  |  |

| Rese  | et 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                        | 0                                                                                                                        | 0                                              | 0                               | 0 0 1                           |                                |                            |  |  |  |  |  |  |  |  |

| SFR A | ddress = 0xI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>E4; SFR Page                                                                                                                                                                                                         | = 0                                                                                                                      |                                                |                                 |                                 |                                | <u> </u> ]                 |  |  |  |  |  |  |  |  |

| Bit   | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                          |                                                                                                                          |                                                | Function                        |                                 |                                |                            |  |  |  |  |  |  |  |  |

| 7     | 0: INT1 input is active low.<br>1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                          |                                                |                                 |                                 |                                |                            |  |  |  |  |  |  |  |  |

| 6:4   | <ul> <li>IN1SL[2:0] INT1 Port Pin Selection Bits.<br/>These bits select which Port pin is assigned to INT1. Note that this pin assignment is<br/>independent of the Crossbar; INT1 will monitor the assigned Port pin without disturb-<br/>ing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar<br/>will not assign the Port pin to a peripheral if it is configured to skip the selected pin.<br/>000: Select P0.0<br/>001: Select P0.1<br/>010: Select P0.2<br/>011: Select P0.3<br/>100: Select P0.4<br/>101: Select P0.5<br/>110: Select P0.6<br/>111: Select P0.7</li> </ul> |                                                                                                                                                                                                                          |                                                                                                                          |                                                |                                 |                                 |                                |                            |  |  |  |  |  |  |  |  |

| 3     | IN0PL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | INTO Polarity<br>0: INTO input<br>1: INTO input                                                                                                                                                                          | is active low                                                                                                            |                                                |                                 |                                 |                                |                            |  |  |  |  |  |  |  |  |

| 2:0   | IN0SL[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | INTO Port Pi<br>These bits se<br>independent<br>ing the periph<br>will not assig<br>000: Select F<br>001: Select F<br>010: Select F<br>100: Select F<br>101: Select F<br>101: Select F<br>110: Select P<br>111: Select P | elect which P<br>of the Cross<br>heral that has<br>n the Port pi<br>20.0<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6 | Port pin is as<br>bar; INTO wi<br>s been assig | ill monitor the<br>ned the Port | e assigned F<br>t pin via the ( | Port pin witho<br>Crossbar. Th | out disturb-<br>e Crossbar |  |  |  |  |  |  |  |  |

# SFR Definition 19.3. OSCICN: Internal H-F Oscillator Control

| Bit   | 7      | 6     | 5       | 4 | 3 | 2 | 1         | 0 |  |  |  |

|-------|--------|-------|---------|---|---|---|-----------|---|--|--|--|

| Name  | IOSCEN | IFRDY | SUSPEND |   |   |   | IFCN[1:0] |   |  |  |  |

| Туре  | R/W    | R     | R/W     | R | R | R | R/W       |   |  |  |  |

| Reset | 1      | 1     | 0       | 0 | 0 | 0 | 0         | 0 |  |  |  |

### SFR Address = 0xB2; SFR Page = All Pages

| Bit | Name      | Function                                                                                                                                                                            |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IOSCEN    | Internal H-F Oscillator Enable Bit.                                                                                                                                                 |

|     |           | 0: Internal H-F Oscillator Disabled.                                                                                                                                                |

|     |           | 1: Internal H-F Oscillator Enabled.                                                                                                                                                 |

| 6   | IFRDY     | Internal H-F Oscillator Frequency Ready Flag.                                                                                                                                       |

|     |           | 0: Internal H-F Oscillator is not running at programmed frequency.                                                                                                                  |

|     |           | 1: Internal H-F Oscillator is running at programmed frequency.                                                                                                                      |

| 5   | SUSPEND   | Internal Oscillator Suspend Enable Bit.                                                                                                                                             |

|     |           | Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The inter-<br>nal oscillator resumes operation when one of the SUSPEND mode awakening<br>events occurs. |

| 4:2 | Unused    | Read = 000b; Write = don't care                                                                                                                                                     |

| 1:0 | IFCN[1:0] | Internal H-F Oscillator Frequency Divider Control Bits.                                                                                                                             |

|     |           | The Internal H-F Oscillator is divided by the IFCN bit setting after a divide-by-4 stage.                                                                                           |

|     |           | 00: SYSCLK can be derived from Internal H-F Oscillator divided by 8 (1.5 MHz).                                                                                                      |

|     |           | 01: SYSCLK can be derived from Internal H-F Oscillator divided by 4 (3 MHz).                                                                                                        |

|     |           | 10: SYSCLK can be derived from Internal H-F Oscillator divided by 2 (6 MHz).11: SYSCLK can be derived from Internal H-F Oscillator divided by 1 (12 MHz).                           |

| Port                                                                                                                                                                                       |                                                                        |     | I     | P0             |         |          |      |      |        | Ρ  | 1    |     |     |            |     |            |   | Ρ   | 2 |   |      |     |      |    |     | Ρ                     | 3     |      |        |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|-------|----------------|---------|----------|------|------|--------|----|------|-----|-----|------------|-----|------------|---|-----|---|---|------|-----|------|----|-----|-----------------------|-------|------|--------|---|

| Pin Number                                                                                                                                                                                 | 0                                                                      | 1   | 2 3   | 4              | 56      | 7        | 0    | 1    | 2      | 3  | 4    | 5   | 6   | 7          | 0   | 1          | 2 | 3   | 4 | 5 | 6    | 7   | 0    | 1  | 2   | 3                     | 4     | 5    | 6      | 7 |

| SF Signals<br>(32-pin<br>Package)                                                                                                                                                          | XTAL1                                                                  |     | XTAL2 |                | CNVSTR  | VREF     |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      | Ur | ava | ⊃3.*<br>ailat<br>iges | ole ( | on S | 32-pir | 1 |

| SF Signals<br>(48-pin<br>Package)                                                                                                                                                          |                                                                        |     |       |                | XTAL1   | XTAL2    |      |      | CNVSTR |    | VREF | C Q | Ì   | <b>MVR</b> |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| TX0                                                                                                                                                                                        |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| RX0                                                                                                                                                                                        |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       | 1    |        |   |

| SCK<br>MISO                                                                                                                                                                                |                                                                        | _   |       |                |         |          |      |      |        |    |      |     |     | <u> </u>   |     |            |   |     |   |   |      |     |      |    |     | <u> </u>              |       |      | I      |   |

| MOSI                                                                                                                                                                                       |                                                                        | _   | _     |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     | -                     |       |      |        |   |

| NSS*                                                                                                                                                                                       |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| SDA                                                                                                                                                                                        |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| SCL                                                                                                                                                                                        |                                                                        | -   |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CP0                                                                                                                                                                                        |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CPOA                                                                                                                                                                                       |                                                                        | -   |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CP1                                                                                                                                                                                        |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CP1A                                                                                                                                                                                       |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| SYSCLK                                                                                                                                                                                     |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CEX0                                                                                                                                                                                       |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CEX1                                                                                                                                                                                       |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CEX2                                                                                                                                                                                       |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CEX3                                                                                                                                                                                       |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| CEX4                                                                                                                                                                                       |                                                                        | _   |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| ECI                                                                                                                                                                                        |                                                                        | _   |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| TO                                                                                                                                                                                         |                                                                        | _   |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| T1                                                                                                                                                                                         |                                                                        | _   |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| TX1<br>RX1                                                                                                                                                                                 |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| SDA1                                                                                                                                                                                       |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| SCL1                                                                                                                                                                                       |                                                                        | -   | _     |                |         | -        |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| Pin Skip                                                                                                                                                                                   | 0                                                                      | 0   | 0 0   | 0              | 0 0     | 0        | 0    | 0    | 0      | 0  | 0    | 0   | 0   | 0          | 0   | 0          | 0 | 0   | 0 | 0 | 0    | 0   | 0    | 0  | 0   | 0                     | 0     | 0    | 0      | 0 |

| Settings                                                                                                                                                                                   | ~                                                                      | ~1  |       | '   U<br>ISKIF |         | <u> </u> |      | -    |        |    | KI F |     | Ľ   | Ľ          |     | Г <u>,</u> |   | -2S |   |   | Ľ    | Ľ   | F    | Ľ  |     | <u>-</u> 3≲           |       |      | ĽĽ     | - |

|                                                                                                                                                                                            | peri                                                                   | ph  |       |                |         | ied i    | n pr | iori |        |    |      |     | top | to h       | off | om         |   |     |   |   | this | dia | adra | am |     |                       |       |      |        | - |

| The crossbar peripherals are assigned in priority order from top to bottom, according to this diagram.  These boxes represent Port pins which can potentially be assigned to a peripheral. |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| Special Function Signals are not assigned by the crossbar. When these signals are enabled, the Crossbar should be manually configured to skip the corresponding port pins.                 |                                                                        |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| Pins can                                                                                                                                                                                   | Pins can be "skipped" by setting the corresponding bit in PnSKIP to 1. |     |       |                |         |          |      |      |        |    |      |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

| * NSS is only                                                                                                                                                                              | pinr                                                                   | iec | dout  | wher           | n the S | SPI i    | sin  | 4-v  | vire   | mc | de.  |     |     |            |     |            |   |     |   |   |      |     |      |    |     |                       |       |      |        |   |

# Figure 20.3. Peripheral Availability on Port I/O Pins

# SFR Definition 20.20. P4: Port 4

| Bit   | 7       | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-------|---------|---|---|----|---|---|---|---|--|--|--|--|--|

| Name  | P4[7:0] |   |   |    |   |   |   |   |  |  |  |  |  |

| Туре  |         |   |   | R/ | W |   |   |   |  |  |  |  |  |

| Reset | 1       | 1 | 1 | 1  | 1 | 1 | 1 | 1 |  |  |  |  |  |

SFR Address = 0xC7; SFR Page = All Pages

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P4[7:0] | <b>Port 4 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P4.n Port pin is logic<br>LOW.<br>1: P4.n Port pin is logic<br>HIGH. |

# SFR Definition 20.21. P4MDIN: Port 4 Input Mode

| Bit   | 7 | 6           | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |  |  |  |

|-------|---|-------------|---|----|---|---|---|---|--|--|--|--|--|--|

| Name  |   | P4MDIN[7:0] |   |    |   |   |   |   |  |  |  |  |  |  |

| Туре  |   |             |   | R/ | W |   |   |   |  |  |  |  |  |  |

| Reset | 1 | 1           | 1 | 1  | 1 | 1 | 1 | 1 |  |  |  |  |  |  |

#### SFR Address = 0xF5; SFR Page = All Pages

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P4MDIN[7:0] | Analog Configuration Bits for P4.7–P4.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P4.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P4.n pin is not configured for analog mode.                                                |

# USB Register Definition 21.16. CMIE: USB0 Common Interrupt Enable

| Bit   | 7 | 6 | 5 | 4 | 3    | 2       | 1       | 0       |

|-------|---|---|---|---|------|---------|---------|---------|

| Name  |   |   |   |   | SOFE | RSTINTE | RSUINTE | SUSINTE |

| Туре  | R | R | R | R | R/W  | R/W     | R/W     | R/W     |

| Reset | 0 | 0 | 0 | 0 | 0    | 1       | 1       | 0       |

USB Register Address = 0x0B

| Bit | Name    | Function                                                                                     |

|-----|---------|----------------------------------------------------------------------------------------------|

| 7:4 | Unused  | Read = 0000b. Write = don't care.                                                            |

| 3   | SOFE    | Start of Frame Interrupt Enable.<br>0: SOF interrupt disabled.                               |

|     |         | 1: SOF interrupt enabled.                                                                    |

| 2   | RSTINTE | Reset Interrupt Enable.<br>0: Reset interrupt disabled.<br>1: Reset interrupt enabled.       |

| 1   | RSUINTE | Resume Interrupt Enable.<br>0: Resume interrupt disabled.<br>1: Resume interrupt enabled.    |

| 0   | SUSINTE | Suspend Interrupt Enable.<br>0: Suspend interrupt disabled.<br>1: Suspend interrupt enabled. |

### USB Register Definition 21.18. E0CNT: USB0 Endpoint0 Data Count

| Bit   | 7 | 6 | 5          | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---|---|------------|---|---|---|---|---|--|--|--|--|

| Name  |   |   | E0CNT[6:0] |   |   |   |   |   |  |  |  |  |

| Туре  | R |   |            |   | R |   |   |   |  |  |  |  |

| Reset | 0 | 0 | 0          | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

USB Register Address = 0x16

| Bit | Name       | Function                                                                                                                                |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused     | Read = 0b. Write = don't care.                                                                                                          |

| 6:0 | E0CNT[6:0] | Endpoint 0 Data Count.                                                                                                                  |

|     |            | This 7-bit number indicates the number of received data bytes in the Endpoint 0 FIFO. This number is only valid while bit OPRDY is a 1. |

### 21.11. Configuring Endpoints1-3

Endpoints1-3 are configured and controlled through their own sets of the following control/status registers: IN registers EINCSRL and EINCSRH, and OUT registers EOUTCSRL and EOUTCSRH. Only one set of endpoint control/status registers is mapped into the USB register address space at a time, defined by the contents of the INDEX register (USB Register Definition 21.4).

Endpoints1-3 can be configured as IN, OUT, or both IN/OUT (Split Mode) as described in Section 21.5.1. The endpoint mode (Split/Normal) is selected via the SPLIT bit in register EINCSRH.

When SPLIT = 1, the corresponding endpoint FIFO is split, and both IN and OUT pipes are available.

When SPLIT = 0, the corresponding endpoint functions as either IN or OUT; the endpoint direction is selected by the DIRSEL bit in register EINCSRH.

Endpoints1-3 can be disabled individually by the corresponding bits in the ENABLE register. When an Endpoint is disabled, it will not respond to bus traffic or stall the bus. All Endpoints are enabled by default.

### USB Register Definition 21.19. EENABLE: USB0 Endpoint Enable

| Bit   | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0   |

|-------|---|---|---|---|------|------|------|-----|

| Name  |   |   |   |   | EEN3 | EEN2 | EEN1 |     |

| Туре  | R | R | R | R | R/W  | R/W  | R/W  | R/W |

| Reset | 1 | 1 | 1 | 1 | 1    | 1    | 1    | 1   |

USB Register Address = 0x1E

| Bit | Name     | Function                                                                                                                                              |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused   | Read = 1111b. Write = don't care.                                                                                                                     |

| 3   | EEN3     | Endpoint 3 Enable.                                                                                                                                    |

|     |          | This bit enables/disables Endpoint 3.<br>0: Endpoint 3 is disabled (no NACK, ACK, or STALL on the USB network).<br>1: Endpoint 3 is enabled (normal). |

| 2   | EEN2     | Endpoint 2 Enable.                                                                                                                                    |

|     |          | This bit enables/disables Endpoint 2.<br>0: Endpoint 2 is disabled (no NACK, ACK, or STALL on the USB network).<br>1: Endpoint 2 is enabled (normal). |

| 1   | EEN1     | Endpoint 1 Enable.                                                                                                                                    |

|     |          | This bit enables/disables Endpoint 1.<br>0: Endpoint 1 is disabled (no NACK, ACK, or STALL on the USB network).<br>1: Endpoint 1 is enabled (normal). |

| 0   | Reserved | Must Write 1b.                                                                                                                                        |

# 21.12. Controlling Endpoints1-3 IN

Endpoints1-3 IN are managed via USB registers EINCSRL and EINCSRH. All IN endpoints can be used for Interrupt, Bulk, or Isochronous transfers. Isochronous (ISO) mode is enabled by writing 1 to the ISO bit in register EINCSRH. Bulk and Interrupt transfers are handled identically by hardware.

An Endpoint1-3 IN interrupt is generated by any of the following conditions:

- 1. An IN packet is successfully transferred to the host.

- 2. Software writes 1 to the FLUSH bit (EINCSRL.3) when the target FIFO is not empty.

- 3. Hardware generates a STALL condition.

### 21.12.1. Endpoints1-3 IN Interrupt or Bulk Mode

When the ISO bit (EINCSRH.6) = 0 the target endpoint operates in Bulk or Interrupt Mode. Once an endpoint has been configured to operate in Bulk/Interrupt IN mode (typically following an Endpoint0 SET\_IN-TERFACE command), firmware should load an IN packet into the endpoint IN FIFO and set the INPRDY bit (EINCSRL.0). Upon reception of an IN token, hardware will transmit the data, clear the INPRDY bit, and generate an interrupt.

Writing 1 to INPRDY without writing any data to the endpoint FIFO will cause a zero-length packet to be transmitted upon reception of the next IN token.

# USB Register Definition 21.23. EOUTCSRH: USB0 OUT Endpoint Control High Byte

| Bit   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------|-----|---|---|---|---|---|---|

| Name  | DBOEN | ISO |   |   |   |   |   |   |

| Туре  | R/W   | R/W | R | R | R | R | R | R |

| Reset | 0     | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

#### USB Register Address = 0x15

| Bit | Name   | Function                                                                                                                                                                              |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DBOEN  | Double-buffer Enable.                                                                                                                                                                 |

|     |        | <ul><li>0: Double-buffering disabled for the selected OUT endpoint.</li><li>1: Double-buffering enabled for the selected OUT endpoint.</li></ul>                                      |

| 6   | ISO    | Isochronous Transfer Enable.                                                                                                                                                          |

|     |        | This bit enables/disables isochronous transfers on the current endpoint.<br>0: Endpoint configured for bulk/interrupt transfers.<br>1: Endpoint configured for isochronous transfers. |

| 5:0 | Unused | Read = 000000b. Write = don't care.                                                                                                                                                   |

# USB Register Definition 21.24. EOUTCNTL: USB0 OUT Endpoint Count Low

| Bit                         | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------------------|-----------|---|---|---|---|---|---|---|--|--|

| Name                        | EOCL[7:0] |   |   |   |   |   |   |   |  |  |

| Туре                        |           |   |   | F | २ |   |   |   |  |  |

| Reset                       | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| USB Register Address = 0x16 |           |   |   |   |   |   |   |   |  |  |

| Bit | Name      | Function                                                                                                                                                                   |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | EOCL[7:0] | OUT Endpoint Count Low Byte.                                                                                                                                               |

|     |           | EOCL holds the lower 8-bits of the 10-bit number of data bytes in the last received packet in the current OUT endpoint FIFO. This number is only valid while $OPRDY = 1$ . |

# SFR Definition 22.3. SMBTC: SMBus Timing Control

| Bit   | 7 | 6 | 5 | 4 | 3            | 2 | 1            | 0 |

|-------|---|---|---|---|--------------|---|--------------|---|

| Name  |   |   |   |   | SMB1SDD[1:0] |   | SMB0SDD[1:0] |   |

| Туре  | R | R | R | R | R/W          |   | R/           | W |

| Reset | 0 | 0 | 0 | 0 | 0            | 0 | 0            | 0 |

### SFR Address = 0xB9; SFR Page = F

| Bit | Name         | Function                                                                                                    |

|-----|--------------|-------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused       | Read = 0000b; Write = don't care.                                                                           |

| 3:2 | SMB1SDD[1:0] | SMBus1 Start Detection Window                                                                               |

|     |              | These bits increase the hold time requirement between SDA falling and SCL fall-<br>ing for START detection. |

|     |              | 00: No additional hold time requirement (0-1 SYSCLK).                                                       |

|     |              | 01: Increase hold time window to 2-3 SYSCLKs.                                                               |

|     |              | 10: Increase hold time window to 4-5 SYSCLKs.                                                               |

|     |              | 11: Increase hold time window to 8-9 SYSCLKs.                                                               |

| 1:0 | SMB0SDD[1:0] | SMBus0 Start Detection Window                                                                               |

|     |              | These bits increase the hold time requirement between SDA falling and SCL fall-<br>ing for START detection. |

|     |              | 00: No additional hold time window (0-1 SYSCLK).                                                            |

|     |              | 01: Increase hold time window to 2-3 SYSCLKs.                                                               |

|     |              | 10: Increase hold time window to 4-5 SYSCLKs.                                                               |

|     |              | 11: Increase hold time window to 8-9 SYSCLKs.                                                               |

# SFR Definition 22.4. SMB0CN: SMBus Control

| Bit   | 7       | 6       | 5    | 4    | 3      | 2        | 1    | 0   |

|-------|---------|---------|------|------|--------|----------|------|-----|

| Name  | MASTER0 | TXMODE0 | STA0 | STO0 | ACKRQ0 | ARBLOST0 | ACK0 | SI0 |

| Туре  | R       | R       | R/W  | R/W  | R      | R        | R/W  | R/W |

| Reset | 0       | 0       | 0    | 0    | 0      | 0        | 0    | 0   |

### SFR Address = 0xC0; SFR Page = 0; Bit-Addressable

| Bit | Name     | Description                                                                                                                                                                                                    | Read                                                                                                                        | Write                                                                                                                                                                                |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER0  | SMBus0 Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus0 is<br>operating as a master.                                                                                                 | 0: SMBus0 operating in<br>slave mode.<br>1: SMBus0 operating in<br>master mode.                                             | N/A                                                                                                                                                                                  |

| 6   | TXMODE0  | SMBus0 Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus0 is<br>operating as a transmitter.                                                                                           | 0: SMBus0 in Receiver<br>Mode.<br>1: SMBus0 in Transmitter<br>Mode.                                                         | N/A                                                                                                                                                                                  |

| 5   | STA0     | SMBus0 Start Flag.                                                                                                                                                                                             | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                       | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO0     | SMBus0 Stop Flag.                                                                                                                                                                                              | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or<br>pending (if in Master<br>Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ0   | SMBus0 Acknowledge<br>Request.                                                                                                                                                                                 | 0: No ACK requested<br>1: ACK requested                                                                                     | N/A                                                                                                                                                                                  |

| 2   | ARBLOST0 | SMBus0 Arbitration Lost Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                             | N/A                                                                                                                                                                                  |

| 1   | ACK0     | SMBus0 Acknowledge.                                                                                                                                                                                            | 0: NACK received.<br>1: ACK received.                                                                                       | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SIO      | SMBus0 Interrupt Flag.<br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI0 must be<br>cleared by software. While SI0<br>is set, SCL0 is held low and<br>the SMBus0 is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                             | 0: Clear interrupt, and ini-<br>tiate next state machine<br>event.<br>1: Force interrupt.                                                                                            |

# SFR Definition 22.9. SMB1ADM: SMBus1 Slave Address Mask

| Bit   | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------|---------------|---|---|---|---|---|---|-----|

| Name  | SLVM1[6:0]    |   |   |   |   |   |   |     |

| Туре  | R/W           |   |   |   |   |   |   | R/W |

| Reset | 1 1 1 1 1 1 1 |   |   |   |   |   |   | 0   |

#### SFR Address = 0xCE; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                                                                                                             |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM1[6:0] | SMBus1 Slave Address Mask.                                                                                                                                                                                                                                                           |

|     |            | Defines which bits of register SMB1ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM1[6:0] enables comparisons with the corresponding bit in SLV1[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK1     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                         |

|     |            | <ul><li>Enables hardware acknowledgement of slave address and received data bytes.</li><li>0: Firmware must manually acknowledge all incoming address and data bytes.</li><li>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.</li></ul>                  |

# SFR Definition 23.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|---|---|---|---|---|--|

| Name  |   | SBUF0[7:0]      |   |   |   |   |   |   |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

SFR Address = 0x99; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBUF0[7:0] | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                                                                                                                                                                      |

|     |            | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for<br>serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of<br>SBUF0 returns the contents of the receive latch. |

### Table 23.1. Timer Settings for Standard Baud Rates Using Internal Oscillator

|      | Target<br>Baud | Actual<br>Baud | Baud<br>Rate | Oscillator<br>Divide | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale | T1M | Timer 1<br>Reload |

|------|----------------|----------------|--------------|----------------------|-----------------------|-------------------------|-----|-------------------|

|      | Rate (bps)     | Rate (bps)     | Error        | Factor               | course                | select*                 |     | Value (hex)       |

|      | 230400         | 230769         | 0.16%        | 52                   | SYSCLK                | XX                      | 1   | 0xE6              |

| MHz  | 115200         | 115385         | 0.16%        | 104                  | SYSCLK                | XX                      | 1   | 0xCC              |

| 2    | 57600          | 57692          | 0.16%        | 208                  | SYSCLK                | XX                      | 1   | 0x98              |

| 1    | 28800          | 28846          | 0.16%        | 416                  | SYSCLK                | XX                      | 1   | 0x30              |

|      | 14400          | 14423          | 0.16%        | 832                  | SYSCLK/4              | 01                      | 0   | 0x98              |

| SCLK | 9600           | 9615           | 0.16%        | 1248                 | SYSCLK / 4            | 01                      | 0   | 0x64              |

| SΥS  | 2400           | 2404           | 0.16%        | 4992                 | SYSCLK / 12           | 00                      | 0   | 0x30              |

| S    | 1200           | 1202           | 0.16%        | 9984                 | SYSCLK / 48           | 10                      | 0   | 0x98              |

| N    | 230400         | 230769         | 0.16%        | 104                  | SYSCLK                | XX                      | 1   | 0xCC              |

| MHz  | 115200         | 115385         | 0.16%        | 208                  | SYSCLK                | XX                      | 1   | 0x98              |

| 24 N | 57600          | 57692          | 0.16%        | 416                  | SYSCLK                | XX                      | 1   | 0x30              |

| 2    | 28800          | 28846          | 0.16%        | 832                  | SYSCLK/4              | 01                      | 0   | 0x98              |

|      | 14400          | 14423          | 0.16%        | 1664                 | SYSCLK/4              | 01                      | 0   | 0x30              |

| SCLK | 9600           | 9615           | 0.16%        | 2496                 | SYSCLK / 12           | 00                      | 0   | 0x98              |

| SΥS  | 2400           | 2404           | 0.16%        | 9984                 | SYSCLK / 48           | 10                      | 0   | 0x98              |

| S    | 1200           | 1202           | 0.16%        | 19968                | SYSCLK / 48           | 10                      | 0   | 0x30              |

| Ŗ    | 230400         | 230769         | 0.16%        | 208                  | SYSCLK                | XX                      | 1   | 0x98              |

| MHz  | 115200         | 115385         | 0.16%        | 416                  | SYSCLK                | XX                      | 1   | 0x30              |

| 48   | 57600          | 57692          | 0.16%        | 832                  | SYSCLK/4              | 01                      | 0   | 0x98              |