Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                            |

| Data Converters            | A/D 12x8b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 20-DIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908jk1cp |

## 4.7 FLASH Program Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0 or \$XXE0. Use this step-by-step procedure to program a row of FLASH memory: (Figure 4-2 shows a flowchart of the programming algorithm.)

**NOTE:** In order to avoid program disturbs, the row must be erased before any byte on that row is programmed.

- Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Write any data to any FLASH location within the address range of the row to be programmed.

- 3. Wait for a time,  $t_{nvs}$  (10 $\mu$ s).

- 4. Set the HVEN bit.

- 5. Wait for a time,  $t_{pqs}$  (5µs).

- 6. Write data to the byte being programmed.

- Wait for time, t<sub>PROG</sub> (30μs).

- 8. Repeat step 6 and 7 until all the bytes within the row are programmed.

- 9. Clear the PGM bit.

- 10. Wait for time, t<sub>nvh</sub> (5μs).

- 11. Clear the HVEN bit.

- 12. After time,  $t_{rcv}$  (1 $\mu$ s), the memory can be accessed in read mode again.

This program sequence is repeated throughout the memory until all data is programmed.

MC68H(R)C908JL3 — Rev. 1.1

Table 6-2. Opcode Map

|            | Bit Manipulation   Branch   Read-Modify-Write   Control   Register/Memory |                     |                    |                    |                     |                     |                     |                    |                    |                    |                   |                   |                   |                   |                   |                   |                   |                   |                  |

|------------|---------------------------------------------------------------------------|---------------------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR                                                                       | DIR                 | REL                | DIR                | INH                 | INH                 | IX1                 | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                                                                         | 1                   | 2                  | 3                  | 4                   | 5                   | 6                   | 9E6                | 7                  | 8                  | 9                 | Α                 | В                 | С                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | 5<br>BRSET0<br>3 DIR                                                      | BSET0<br>2 DIR      | 3<br>BRA<br>2 REL  | 4<br>NEG<br>2 DIR  | 1<br>NEGA<br>1 INH  | 1<br>NEGX<br>1 INH  | 4<br>NEG<br>2 IX1   |                    | 3<br>NEG<br>1 IX   | 7<br>RTI<br>1 INH  | 3<br>BGE<br>2 REL | SUB<br>2 IMM      | 3<br>SUB<br>2 DIR | SUB<br>3 EXT      | SUB<br>3 IX2      | 5<br>SUB<br>4 SP2 | 3<br>SUB<br>2 IX1 | 4<br>SUB<br>3 SP1 | SUB<br>1 IX      |

| 1          | 5<br>BRCLR0<br>3 DIR                                                      | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL  | 5<br>CBEQ<br>3 DIR | CBEQA<br>3 IMM      | CBEQX<br>3 IMM      | 5<br>CBEQ<br>3 IX1+ | 6<br>CBEQ<br>4 SP1 | CBEQ<br>2 IX+      | 4<br>RTS<br>1 INH  | 3<br>BLT<br>2 REL | 2<br>CMP<br>2 IMM | 3<br>CMP<br>2 DIR | 4<br>CMP<br>3 EXT | 4<br>CMP<br>3 IX2 | 5<br>CMP<br>4 SP2 | 3<br>CMP<br>2 IX1 | 4<br>CMP<br>3 SP1 | CMP<br>1 IX      |

| 2          | 5<br>BRSET1<br>3 DIR                                                      | 4<br>BSET1<br>2 DIR |                    |                    | 5<br>MUL<br>1 INH   | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH   |                    | 2<br>DAA<br>1 INH  |                    | 3<br>BGT<br>2 REL | SBC<br>2 IMM      | 3<br>SBC<br>2 DIR | SBC<br>3 EXT      | SBC<br>3 IX2      | 5<br>SBC<br>4 SP2 | 3<br>SBC<br>2 IX1 | 4<br>SBC<br>3 SP1 | SBC<br>1 IX      |

| 3          | 5<br>BRCLR1<br>3 DIR                                                      | 4<br>BCLR1<br>2 DIR |                    | COM<br>2 DIR       |                     | COMX<br>1 INH       | 4<br>COM<br>2 IX1   | 5<br>COM<br>3 SP1  |                    | 9<br>SWI<br>1 INH  |                   |                   |                   | CPX<br>3 EXT      |                   | 5<br>CPX<br>4 SP2 | 3<br>CPX<br>2 IX1 | 4<br>CPX<br>3 SP1 | CPX<br>1 IX      |

| 4          | 5<br>BRSET2<br>3 DIR                                                      | BSET2<br>2 DIR      | 3<br>BCC<br>2 REL  | 4<br>LSR<br>2 DIR  |                     | 1<br>LSRX<br>1 INH  | 4<br>LSR<br>2 IX1   | 5<br>LSR<br>3 SP1  |                    | 2<br>TAP<br>1 INH  | 2<br>TXS<br>1 INH |                   |                   | 4<br>AND<br>3 EXT |                   | 5<br>AND<br>4 SP2 | 3<br>AND<br>2 IX1 | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          |                                                                           | 4<br>BCLR2<br>2 DIR |                    | 4<br>STHX<br>2 DIR | 3<br>LDHX<br>3 IMM  | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM  |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH |                   |                   | 4<br>BIT<br>3 EXT |                   |                   | 3<br>BIT<br>2 IX1 | 4<br>BIT<br>3 SP1 | 2<br>BIT<br>1 IX |

| 6          |                                                                           | BSET3<br>2 DIR      |                    | 4<br>ROR<br>2 DIR  | 1<br>RORA<br>1 INH  |                     | 4<br>ROR<br>2 IX1   | 5<br>ROR<br>3 SP1  |                    | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM |                   | 4<br>LDA<br>3 EXT |                   | 5<br>LDA<br>4 SP2 | 3<br>LDA<br>2 IX1 | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          |                                                                           | 4<br>BCLR3<br>2 DIR | 3<br>BEQ<br>2 REL  | 4<br>ASR<br>2 DIR  | 1<br>ASRA<br>1 INH  | 1<br>ASRX<br>1 INH  | 4<br>ASR<br>2 IX1   | 5<br>ASR<br>3 SP1  |                    | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH |                   |                   | 4<br>STA<br>3 EXT | 4<br>STA<br>3 IX2 |                   | 3<br>STA<br>2 IX1 | 4<br>STA<br>3 SP1 | 2<br>STA<br>1 IX |

| 8          | -                                                                         | 4<br>BSET4<br>2 DIR | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH  | 1<br>LSLX<br>1 INH  | 4<br>LSL<br>2 IX1   | 5<br>LSL<br>3 SP1  | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | EOR<br>2 IMM      |                   | 4<br>EOR<br>3 EXT | 4<br>EOR<br>3 IX2 | 5<br>EOR<br>4 SP2 | 3<br>EOR<br>2 IX1 | 4<br>EOR<br>3 SP1 | 2<br>EOR<br>1 IX |

| 9          |                                                                           | BCLR4<br>2 DIR      | 3<br>BHCS<br>2 REL | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH  | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1   |                    | 3<br>ROL<br>1 IX   | 2<br>PSHX<br>1 INH | SEC<br>1 INH      | ADC<br>2 IMM      | 3<br>ADC<br>2 DIR | 4<br>ADC<br>3 EXT | 4<br>ADC<br>3 IX2 | 5<br>ADC<br>4 SP2 | 3<br>ADC<br>2 IX1 | 4<br>ADC<br>3 SP1 | 2<br>ADC<br>1 IX |

| A          | 5<br>BRSET5<br>3 DIR                                                      | 4<br>BSET5<br>2 DIR | 3<br>BPL<br>2 REL  | 4<br>DEC<br>2 DIR  | 1<br>DECA<br>1 INH  |                     | 4<br>DEC<br>2 IX1   | 5<br>DEC<br>3 SP1  | 3<br>DEC<br>1 IX   | 2<br>PULH<br>1 INH |                   | ORA<br>2 IMM      | 3<br>ORA<br>2 DIR | 4<br>ORA<br>3 EXT | 4<br>ORA<br>3 IX2 | 5<br>ORA<br>4 SP2 | 3<br>ORA<br>2 IX1 | 4<br>ORA<br>3 SP1 |                  |

| В          | 5<br>BRCLR5<br>3 DIR                                                      | 4<br>BCLR5<br>2 DIR | 3<br>BMI<br>2 REL  | 5<br>DBNZ<br>3 DIR | 3<br>DBNZA<br>2 INH | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1  | 6<br>DBNZ<br>4 SP1 | 4<br>DBNZ<br>2 IX  | 2<br>PSHH<br>1 INH | 2<br>SEI<br>1 INH | 2<br>ADD<br>2 IMM | 3<br>ADD<br>2 DIR | 4<br>ADD<br>3 EXT | 4<br>ADD<br>3 IX2 | 5<br>ADD<br>4 SP2 | 3<br>ADD<br>2 IX1 | 4<br>ADD<br>3 SP1 | 2<br>ADD<br>1 IX |

| С          | 5<br>BRSET6<br>3 DIR                                                      | BSET6<br>2 DIR      |                    | 4<br>INC<br>2 DIR  | 1<br>INCA<br>1 INH  | 1<br>INCX<br>1 INH  | 4<br>INC<br>2 IX1   | 5<br>INC<br>3 SP1  |                    | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR | 3<br>JMP<br>3 EXT |                   |                   | 3<br>JMP<br>2 IX1 |                   | JMP<br>1 IX      |

| D          |                                                                           | 4<br>BCLR6<br>2 DIR |                    | 3<br>TST<br>2 DIR  | 1<br>TSTA<br>1 INH  | 1<br>TSTX<br>1 INH  | 3<br>TST<br>2 IX1   | 4<br>TST<br>3 SP1  |                    |                    | 1<br>NOP<br>1 INH | 4<br>BSR<br>2 REL |                   | 5<br>JSR<br>3 EXT |                   |                   | 5<br>JSR<br>2 IX1 |                   | JSR<br>1 IX      |

| E          |                                                                           | BSET7<br>2 DIR      |                    |                    |                     | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD   |                    | 4<br>MOV<br>2 IX+D | 1<br>STOP<br>1 INH | *                 | LDX<br>2 IMM      |                   | 4<br>LDX<br>3 EXT |                   | 5<br>LDX<br>4 SP2 | 3<br>LDX<br>2 IX1 |                   | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7<br>3 DIR                                                      | 4<br>BCLR7<br>2 DIR | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH  | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1   | 4<br>CLR<br>3 SP1  | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | STX<br>2 DIR      | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | 5<br>STX<br>4 SP2 | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | STX<br>1 IX      |

INH Inherent IMM Immediate DIR Direct EXT Extended

**REL** Relative Indexed, No Offset IX1 Indexed, 8-Bit Offset IX2 Indexed, 16-Bit Offset IMD Immediate-Direct DD Direct-Direct IMD Immediate-Dire IX+D Indexed-Direct DIX+ Direct-Indexed

\*Pre-byte for stack pointer indexed instructions

Low Byte of Opcode in Hexadecimal

MSB High Byte of Opcode in Hexadecimal LSB 5 BRSET0 Opcode Mnemonic Opcode Mnemonic Number of Bytes / Addressing Mode

SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with Post Increment

IX1+ Indexed, 1-Byte Offset with Post Increment

## System Integration Module (SIM)

| 7.7   | Low-Power Modes                    | 88 |

|-------|------------------------------------|----|

| 7.7.1 | Wait Mode                          | 88 |

| 7.7.2 | Stop Mode                          | 90 |

| 7.8   | SIM Registers                      | 91 |

| 7.8.1 | Break Status Register (BSR)        | 91 |

| 7.8.2 | Reset Status Register (RSR)        | 92 |

| 7.8.3 | Break Flag Control Register (BFCR) | 94 |

#### 7.2 Introduction

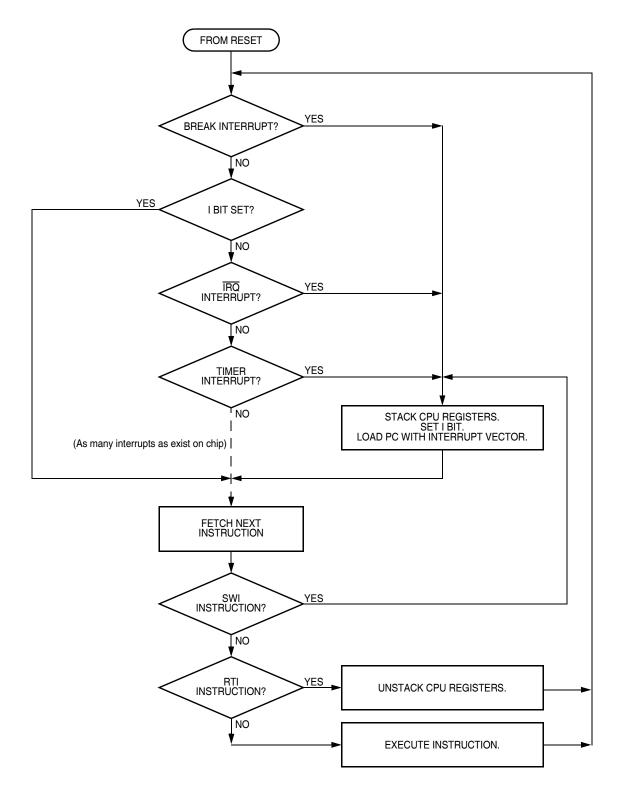

This section describes the system integration module (SIM), which supports up to 24 external and/or internal interrupts. Together with the CPU, the SIM controls all MCU activities. A block diagram of the SIM is shown in **Figure 7-1**. **Figure 7-2** is a summary of the SIM I/O registers. The SIM is a system state controller that coordinates CPU and exception timing. The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and COP timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

- Modular architecture expandable to 128 interrupt sources

# System Integration Module (SIM)

Figure 7-8. Interrupt Processing

## Section 8. Oscillator (OSC)

#### 8.1 Contents

| 8.2                                                                | Introduction95                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.3                                                                | X-tal Oscillator (MC68HC908xxx)96                                                                                                                                                                                                                          |

| 8.4                                                                | RC Oscillator (MC68HRC908xxx)97                                                                                                                                                                                                                            |

| 8.5<br>8.5.1<br>8.5.2<br>8.5.3<br>8.5.4<br>8.5.5<br>8.5.6<br>8.5.7 | I/O Signals98Crystal Amplifier Input Pin (OSC1)98Crystal Amplifier Output Pin (OSC2/PTA6/RCCLK)98Oscillator Enable Signal (SIMOSCEN)98X-tal Oscillator Clock (XTALCLK)98RC Oscillator Clock (RCCLK)99Oscillator Out 2 (2OSCOUT)99Oscillator Out (OSCOUT)99 |

| 8.6<br>8.6.1<br>8.6.2                                              | Low Power Modes                                                                                                                                                                                                                                            |

| 8.7                                                                | Oscillator During Break Mode100                                                                                                                                                                                                                            |

## 8.2 Introduction

The oscillator module provides the reference clock for the MCU system and bus. Two types of oscillator modules are available:

- MC68HC908xxx— built-in oscillator module (X-tal oscillator) that requires an external crystal or ceramic-resonator. This option also allows an external clock that can be driven directly into OSC1.

- MC68HRC908xxx built-in oscillator module (RC oscillator) that requires an external RC connection only.

MC68H(R)C908JL3 - Rev. 1.1

The series resistor  $(R_S)$  is included in the diagram to follow strict Pierce oscillator guidelines and may not be required for all ranges of operation, especially with high frequency crystals. Refer to the crystal manufacturer's data for more information.

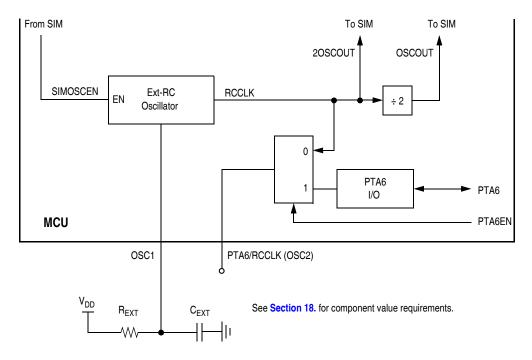

## 8.4 RC Oscillator (MC68HRC908xxx)

MC68H(R)C908JL3 — Rev. 1.1

The RC oscillator circuit is designed for use with external R and C to provide a clock source with tolerance less than 10%.

In its typical configuration, the RC oscillator requires two external components, one R and one C. Component values should have a tolerance of 1% or less, to obtain a clock source with less than 10% tolerance. The oscillator configuration uses two components:

- C<sub>EXT</sub>

- R<sub>EXT</sub>

Figure 8-2. RC Oscillator External Connections

Freescale Semiconductor Oscillator (OSC) 9

## 10.5 Functional Description

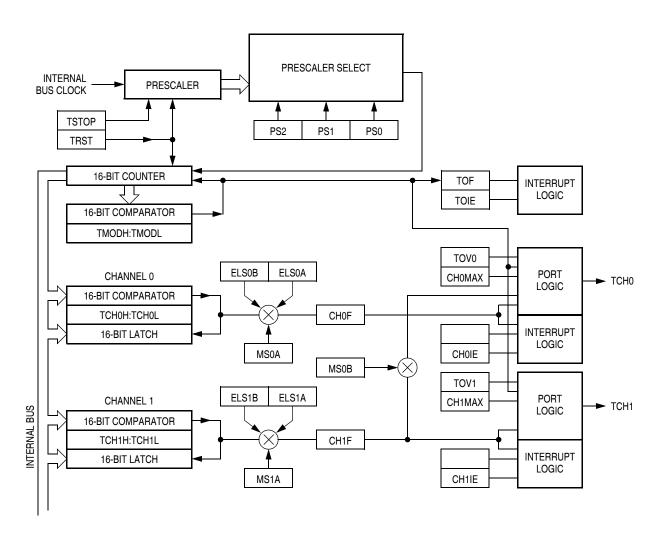

Figure 10-1 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels are programmable independently as input capture or output compare channels.

Figure 10-1. TIM Block Diagram

## Timer Interface Module (TIM)

## 10.5.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in **10.5.3 Output Compare**. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current output compare pulse. The interrupt routine has until the end of the counter overflow period to write the new value.

- when changing to a larger output compare value, enable channel x TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current counter overflow period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same counter overflow period.

### 10.5.3.2 Buffered Output Compare

Channels 0 and 1 can be linked to form a buffered output compare channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The output compare value in the TIM

**Table 10-2. Prescaler Selection**

| PS2 | PS1 | PS0 | TIM Clock Source        |  |  |  |

|-----|-----|-----|-------------------------|--|--|--|

| 0   | 0   | 0   | Internal Bus Clock ÷ 1  |  |  |  |

| 0   | 0   | 1   | Internal Bus Clock ÷ 2  |  |  |  |

| 0   | 1   | 0   | Internal Bus Clock ÷ 4  |  |  |  |

| 0   | 1   | 1   | Internal Bus Clock ÷ 8  |  |  |  |

| 1   | 0   | 0   | Internal Bus Clock ÷ 16 |  |  |  |

| 1   | 0   | 1   | Internal Bus Clock ÷ 32 |  |  |  |

| 1   | 1   | 0   | Internal Bus Clock ÷ 64 |  |  |  |

| 1   | 1   | 1   | Not available           |  |  |  |

## 10.10.2 TIM Counter Registers (TCNTH:TCNTL)

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

NOTE:

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

# Section 11. Analog-to-Digital Converter (ADC)

## 11.1 Contents

| 11.2 Introduction                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.3 Features                                                                                                                                                                                                 |

| 11.4 Functional Description  138    11.4.1 ADC Port I/O Pins  139    11.4.2 Voltage Conversion  140    11.4.3 Conversion Time  140    11.4.4 Continuous Conversion  140    11.4.5 Accuracy and Precision  141 |

| 11.5 Interrupts141                                                                                                                                                                                            |

| 11.6 Low-Power Modes  141    11.6.1 Wait Mode  141    11.6.2 Stop Mode  141                                                                                                                                   |

| 11.7  I/O Signals                                                                                                                                                                                             |

| 11.8  I/O Registers                                                                                                                                                                                           |

## 11.2 Introduction

This section describes the analog-to-digital converter (ADC). The ADC is an 8-bit, 12-channels analog-to-digital converter.

## **Analog-to-Digital Converter (ADC)**

**Table 11-1. MUX Channel Select**

| CH4 | СНЗ | CH2 | CH1 | СН0 | ADC Channel | Input Select                  |

|-----|-----|-----|-----|-----|-------------|-------------------------------|

| 0   | 0   | 0   | 0   | 0   | ADC0        | PTB0                          |

| 0   | 0   | 0   | 0   | 1   | ADC1        | PTB1                          |

| 0   | 0   | 0   | 1   | 0   | ADC2        | PTB2                          |

| 0   | 0   | 0   | 1   | 1   | ADC3        | PTB3                          |

| 0   | 0   | 1   | 0   | 0   | ADC4        | PTB4                          |

| 0   | 0   | 1   | 0   | 1   | ADC5        | PTB5                          |

| 0   | 0   | 1   | 1   | 0   | ADC6        | PTB6                          |

| 0   | 0   | 1   | 1   | 1   | ADC7        | PTB7                          |

| 0   | 1   | 0   | 0   | 0   | ADC8        | PTD3                          |

| 0   | 1   | 0   | 0   | 1   | ADC9        | PTD2                          |

| 0   | 1   | 0   | 1   | 0   | ADC10       | PTD1                          |

| 0   | 1   | 0   | 1   | 1   | ADC11       | PTD0                          |

| 0   | 1   | 1   | 0   | 0   |             |                               |

| :   | :   | :   | :   | :   | _           | Unused<br>(see Note 1)        |

| 1   | 1   | 0   | 1   | 0   |             | (000 11010 1)                 |

| 1   | 1   | 0   | 1   | 1   | _           | Reserved                      |

| 1   | 1   | 1   | 0   | 0   | _           | Unused                        |

| 1   | 1   | 1   | 0   | 1   |             | V <sub>DDA</sub> (see Note 2) |

| 1   | 1   | 1   | 1   | 0   |             | V <sub>SSA</sub> (see Note 2) |

| 1   | 1   | 1   | 1   | 1   |             | ADC power off                 |

#### NOTES:

## 11.8.2 ADC Data Register

One 8-bit result register is provided. This register is updated each time an ADC conversion completes.

<sup>1.</sup> If any unused channels are selected, the resulting ADC conversion will be unknown.

<sup>2.</sup> The voltage levels supplied from internal reference nodes as specified in the table are used to verify the operation of the ADC converter both in production test and for user applications.

# Section 13. External Interrupt (IRQ)

#### 13.1 Contents

| 13.2 | Introduction                           | 159 |

|------|----------------------------------------|-----|

| 13.3 | Features                               | 159 |

|      | Functional Description                 |     |

| 13.5 | IRQ Module During Break Interrupts     | 163 |

| 13.6 | IRQ Status and Control Register (ISCR) | 163 |

## 13.2 Introduction

The IRQ (external interrupt) module provides a maskable interrupt input.

#### 13.3 Features

Features of the IRQ module include the following:

- A dedicated external interrupt pin, IRQ1

- IRQ1 interrupt control bits

- Hysteresis buffer

- Programmable edge-only or edge and level interrupt sensitivity

- · Automatic interrupt acknowledge

- · Selectable internal pullup resistor

MC68H(R)C908JL3 - Rev. 1.1

## 13.5 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ1 latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear the latches during the break state. (See Section 7. System Integration Module (SIM).)

To allow software to clear the IRQ1 latch during a break interrupt, write a logic one to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latches during the break state, write a logic zero to the BCFE bit. With BCFE at logic zero (its default state), writing to the ACK1 bit in the IRQ status and control register during the break state has no effect on the IRQ latch.

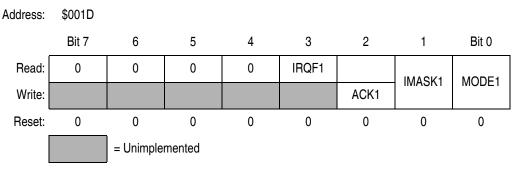

## 13.6 IRQ Status and Control Register (ISCR)

The IRQ Status and Control Register (ISCR) controls and monitors operation of the IRQ module. The ISCR has the following functions:

- Shows the state of the IRQ1 flag

- Clears the IRQ1 latch

- Masks IRQ1 and interrupt request

- Controls triggering sensitivity of the IRQ1 interrupt pin

Figure 13-3. IRQ Status and Control Register (INTSCR)

MC68H(R)C908JL3 — Rev. 1.1

# Section 14. Keyboard Interrupt Module (KBI)

#### 14.1 Contents

| 14.2   | Introduction                            |

|--------|-----------------------------------------|

| 14.3   | Features                                |

|        | Functional Description                  |

| 14.4.2 | Keyboard Interrupt Enable Register      |

| 14.5   | Wait Mode171                            |

| 14.6   | Stop Mode                               |

| 14.7   | Keyboard Module During Break Interrupts |

#### 14.2 Introduction

The keyboard interrupt module (KBI) provides seven independently maskable external interrupts which are accessible via PTA0–PTA6 pins.

#### 14.3 Features

Features of the keyboard interrupt module include the following:

- Seven keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Software configurable pull-up device if input pin is configured as input port bit

- Programmable edge-only or edge- and level- interrupt sensitivity

- Exit from low-power modes

MC68H(R)C908JL3 - Rev. 1.1

# Section 16. Low Voltage Inhibit (LVI)

#### 16.1 Contents

| 16.2   | Introduction                              |

|--------|-------------------------------------------|

| 16.3   | Features                                  |

| 16.4   | Functional Description                    |

| 16.5   | LVI Control Register (CONFIG2/CONFIG1)180 |

|        | Low-Power Modes                           |

| 16.6.1 | Wait Mode                                 |

| 16.6.2 | Stop Mode                                 |

## 16.2 Introduction

This section describes the low-voltage inhibit module (LVI), which monitors the voltage on the  $V_{DD}$  pin and generates a reset when the  $V_{DD}$  voltage falls to the LVI trip (LVI<sub>TRIP</sub>) voltage.

#### 16.3 Features

Features of the LVI module include the following:

- Selectable LVI trip voltage

- Selectable LVI circuit disable

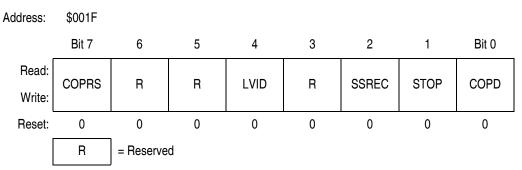

Figure 16-3. Configuration Register 1 (CONFIG1)

LVID — bLow Voltage Inhibit Disable Bit

1 = Low voltage inhibit disabled

0 = Low voltage inhibit enabled

#### LVIT1, LVIT0 — LVI Trip Voltage Selection

These two bits determine at which level of  $V_{DD}$  the LVI module will come into action. LVIT1 and LVIT0 are cleared by a Power-On Reset only.

| LVIT1 | LVIT0 | Trip Voltage <sup>(1)</sup> | Comments                          |

|-------|-------|-----------------------------|-----------------------------------|

| 0     | 0     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 0     | 1     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 1     | 0     | V <sub>LVR5</sub> (4.0V)    | For V <sub>DD</sub> =5V operation |

| 1     | 1     | Reserved                    |                                   |

<sup>1.</sup> See Section 18. Electrical Specifications for full parameters.

#### 16.6 Low-Power Modes

The STOP and WAIT instructions put the MCU in low-power-consumption standby modes.

#### 16.6.1 Wait Mode

The LVI module, when enabled, will continue to operate in WAIT Mode.

#### 16.6.2 Stop Mode

The LVI module, when enabled, will continue to operate in STOP Mode.

MC68H(R)C908JL3 - Rev. 1.1

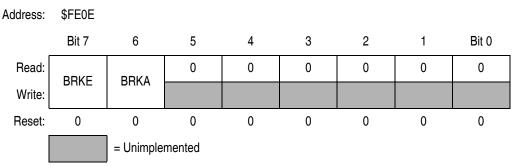

#### 17.5.1 Break Status and Control Register (BRKSCR)

The break status and control register contains break module enable and status bits.

Figure 17-3. Break Status and Control Register (BRKSCR)

### BRKE — Break Enable Bit

This read/write bit enables breaks on break address register matches. Clear BRKE by writing a logic zero to bit 7. Reset clears the BRKE bit.

- 1 = Breaks enabled on 16-bit address match

- 0 = Breaks disabled

#### BRKA — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a logic one to BRKA generates a break interrupt. Clear BRKA by writing a logic zero to it before exiting the break routine. Reset clears the BRKA bit.

- 1 = Break address match

- 0 = No break address match

## **Electrical Specifications**

## 18.3 Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it.

NOTE:

This device is not guaranteed to operate properly at the maximum ratings. Refer to Sections **18.6** and **18.9** for guaranteed operating conditions.

Table 18-1. Absolute Maximum Ratings<sup>(1)</sup>

| Characteristic                                                        | Symbol            | Value                            | Unit |

|-----------------------------------------------------------------------|-------------------|----------------------------------|------|

| Supply voltage                                                        | $V_{DD}$          | -0.3 to +6.0                     | V    |

| Input voltage                                                         | V <sub>IN</sub>   | $V_{SS}$ = 0.3 to $V_{DD}$ + 0.3 | V    |

| Mode entry voltage, IRQ1 pin                                          | $V_{DD}+V_{HI}$   | V <sub>SS</sub> -0.3 to +8.5     | V    |

| Maximum current per pin excluding V <sub>DD</sub> and V <sub>SS</sub> | I                 | ±25                              | mA   |

| Storage temperature                                                   | T <sub>STG</sub>  | -55 to +150                      | °C   |

| Maximum current out of V <sub>SS</sub>                                | I <sub>MVSS</sub> | 100                              | mA   |

| Maximum current into V <sub>DD</sub>                                  | I <sub>MVDD</sub> | 100                              | mA   |

#### NOTE:

#### **NOTE:**

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{IN}$  and  $V_{OUT}$  be constrained to the range  $V_{SS} \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ .)

<sup>1.</sup> Voltages referenced to V<sub>SS</sub>.

## **Electrical Specifications**

## **18.14 Memory Characteristics**

**Table 18-11. Memory Characteristics**

| Characteristic                             | Symbol                            | Min | Max | Unit   |

|--------------------------------------------|-----------------------------------|-----|-----|--------|

| RAM data retention voltage                 | V <sub>RDR</sub>                  | 1.3 | _   | V      |

| FLASH program bus clock frequency          | _                                 | 1   | _   | MHz    |

| FLASH read bus clock frequency             | f <sub>Read</sub> <sup>(1)</sup>  | 32k | 8M  | Hz     |

| FLASH page erase time                      | t <sub>Erase</sub> <sup>(2)</sup> | 1   | _   | ms     |

| FLASH mass erase time                      | t <sub>MErase</sub> (3)           | 4   | _   | ms     |

| FLASH PGM/ERASE to HVEN set up time        | t <sub>nvs</sub>                  | 10  | _   | μS     |

| FLASH high-voltage hold time               | t <sub>nvh</sub>                  | 5   | _   | μS     |

| FLASH high-voltage hold time (mass erase)  | t <sub>nvhl</sub>                 | 100 | _   | μS     |

| FLASH program hold time                    | t <sub>pgs</sub>                  | 5   | _   | μS     |

| FLASH program time                         | t <sub>PROG</sub>                 | 30  | 40  | μS     |

| FLASH return to read time                  | t <sub>rcv</sub> <sup>(4)</sup>   | 1   | _   | μS     |

| FLASH cumulative program hv period         | t <sub>HV</sub> <sup>(5)</sup>    | _   | 4   | ms     |

| FLASH row erase endurance <sup>(6)</sup>   | _                                 | 10k | _   | cycles |

| FLASH row program endurance <sup>(7)</sup> |                                   | 10k |     | cycles |

| FLASH data retention time <sup>(8)</sup>   | _                                 | 10  | _   | years  |

#### NOTES:

- 1.  $f_{Read}$  is defined as the frequency range for which the FLASH memory can be read. 2. If the page erase time is longer than  $t_{Erase}$  (Min), there is no erase-disturb, but it reduces the endurance of the FLASH memory.

- 3. If the mass erase time is longer than t<sub>MErase</sub> (Min), there is no erase-disturb, but it reduces the endurance of the FLASH memory.

- 4. t<sub>rcv</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to logic 0.

- 5. t<sub>HV</sub> is defined as the cumulative high voltage programming time to the same row before next erase.

- $t_{HV}$  must satisfy this condition:  $t_{nvs} + t_{nvh} + t_{pgs} + (t_{PROG} \times 32) \le t_{HV}$  max. 6. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase / program cycles.

- 7. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase / program cycles.

- 8. The FLASH is guaranteed to retain data over the entire operating temperature range for at least the minimum time specified.

# Section 20. Ordering Information

| 20  | 1 | Co | nto   | ntc   |

|-----|---|----|-------|-------|

| ZU. |   | CU | ııııe | 11112 |

| 20.2 | Introduction     | 207 |

|------|------------------|-----|

| 20.3 | MC Order Numbers | 208 |

## 20.2 Introduction

This section contains ordering numbers for the MC68H(R)C908JL3, MC68H(R)C908JK3, and MC68H(R)C908JK1.

MC68H(R)C908JL3 - Rev. 1.1