Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | LED, LVD, POR, PWM                                                      |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                             |

| Data Converters            | A/D 12x8b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 28-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908jl3cdw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Technical Data — MC68H(R)C908JL3

# Section 1. General Description

### 1.1 Contents

| 1.2 | Introduction      | 21 |

|-----|-------------------|----|

| 1.3 | Features          | 22 |

| 1.4 | MCU Block Diagram | 23 |

| 1.5 | Pin Assignments   | 25 |

| 1.6 | Pin Functions     | 26 |

### 1.2 Introduction

The MC68H(R)C908JL3 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is based on the customer-specified integrated circuit (CSIC) design strategy. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

**Table 1-1. Summary of Device Variations**

| Device          | FLASH Memory Size | Pin Count |

|-----------------|-------------------|-----------|

| MC68H(R)C908JL3 | 4096 bytes        | 28 pins   |

| MC68H(R)C908JK3 | 4096 bytes        | 20 pins   |

| MC68H(R)C908JK1 | 1536 bytes        | 20 pins   |

All references to the MC68H(R)C908JL3 in this data book apply equally to the MC68H(R)C908JK3 and MC68H(R)C908JK1, unless otherwise stated.

MC68H(R)C908JL3 — Rev. 1.1

# General Description

### 1.3 Features

Features of the MC68H(R)C908JL3 include the following:

- High-performance M68HC08 architecture

- Fully upward-compatible object code with M6805, M146805, and M68HC05 Families

- Low-power design; fully static with stop and wait modes

- 5V and 3V operating voltages

- 8MHz internal bus operation

- RC-oscillator circuit or crystal-oscillator options

- In-system FLASH programming

- FLASH security<sup>1</sup>

- User FLASH memory

- 4096 bytes for MC68H(R)C908JL3/JK3

- 1536 bytes for MC68H(R)C908JK1

- 128 bytes of on-chip random-access memory (RAM)

- 2-channel, 16-bit timer interface module (TIM)

- 12-channel, 8-bit analog-to-digital converter (ADC)

- 23 general purpose I/O ports for MC68H(R)C908JL3:

- 7 keyboard interrupt with internal pull-up

- 10 LED drivers

- 2 × 25mA open-drain I/O with pull-up

- 2 ICAP/OCAP/PWM

- 15 general purpose I/O ports for MC68H(R)C908JK3/JK1:

- 1 keyboard interrupt with internal pull-up (with RC oscillator option selected)

- 4 LED drivers

- 2 × 25mA open-drain I/O with pull-up

- 2 ICAP/OCAP/PWM

**Technical Data**

MC68H(R)C908JL3 — Rev. 1.1

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

## Memory

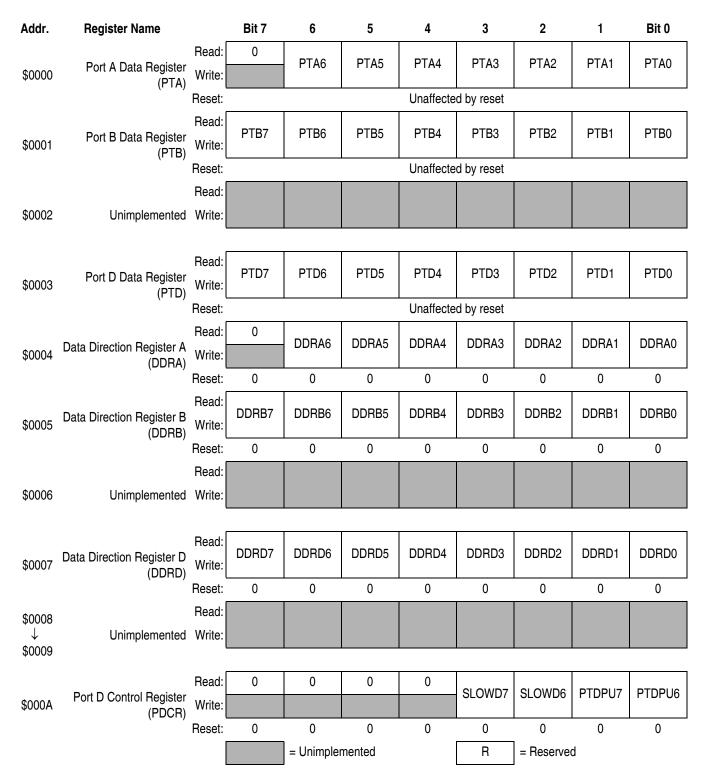

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 5)

**Technical Data**

MC68H(R)C908JL3 - Rev. 1.1

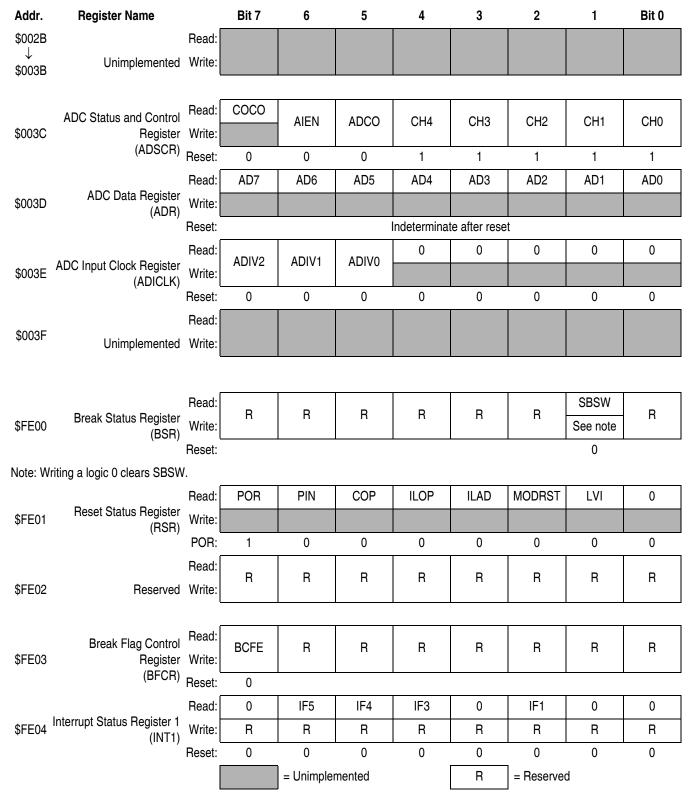

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 5)

MC68H(R)C908JL3 - Rev. 1.1

# Memory

| Addr.                 | Register Name                      |                 | Bit 7                        | 6        | 5       | 4        | 3           | 2        | 1     | Bit 0 |  |  |

|-----------------------|------------------------------------|-----------------|------------------------------|----------|---------|----------|-------------|----------|-------|-------|--|--|

|                       |                                    | Read:           | IF14                         | 0        | 0       | 0        | 0           | 0        | 0     | 0     |  |  |

| \$FE05                | Interrupt Status Register 2 (INT2) | Write:          | R                            | R        | R       | R        | R           | R        | R     | R     |  |  |

|                       | ()                                 | Reset:          | 0                            | 0        | 0       | 0        | 0           | 0        | 0     | 0     |  |  |

|                       | lata annual Otatua Daniatan O      | Read:           | 0                            | 0        | 0       | 0        | 0           | 0        | 0     | IF15  |  |  |

| \$FE06                | Interrupt Status Register 3 (INT3) | Write:          | R                            | R        | R       | R        | R           | R        | R     | R     |  |  |

|                       | ,                                  | Reset:          | 0                            | 0        | 0       | 0        | 0           | 0        | 0     | 0     |  |  |

| \$FE07                | Reserved                           | Read:<br>Write: | R                            | R        | R       | R        | R           | R        | R     | R     |  |  |

|                       |                                    | 1               |                              |          | T -     |          | Ι           |          | T     |       |  |  |

| ¢ΓΓΛΩ                 | FLASH Control Register<br>(FLCR)   | Read:<br>Write: | 0                            | 0        | 0       | 0        | HVEN        | MASS     | ERASE | PGM   |  |  |

| \$FE08                |                                    | Reset:          | 0                            | 0        | 0       | 0        | 0           | 0        | 0     | 0     |  |  |

|                       |                                    | Read:           | 0                            | I        | T       | I        | I           | I        | T     | 0     |  |  |

| \$FE09                | FLASH Block Protect                | Write:          | BPR7                         | BPR6     | BPR5    | BPR4     | BPR3        | BPR2     | BPR1  | 0     |  |  |

| Ψι ΔΟ                 | Register (FLBPR)                   | Reset:          | 0                            | 0        | 0       | 0        | 0           | 0        | 0     | 0     |  |  |

|                       |                                    | Read:           |                              | Ι        | Ι       | Π        | Ι           |          |       |       |  |  |

| \$FE0A<br>↓<br>\$FE0B | Reserved                           |                 | R                            | R        | R       | R        | R           | R        | R     | R     |  |  |

|                       |                                    | أرامهما         |                              | <u> </u> | 1       | <u> </u> | I           |          | 1     |       |  |  |

| \$FE0C                | Break Address High<br>Register     | Read:<br>Write: | Bit15                        | Bit14    | Bit13   | Bit12    | Bit11       | Bit10    | Bit9  | Bit8  |  |  |

|                       | (DDIZLI)                           |                 | 0                            | 0        | 0       | 0        | 0           | 0        | 0     | 0     |  |  |

|                       | Break Address low                  | Read:           | Bit7                         | Bit6     | Bit5    | Bit4     | Bit3        | Bit2     | Bit1  | Bit0  |  |  |

| \$FE0D                | Register                           | Write:          | DIL/                         | DIIO     | ыю      | DIL4     | DIIO        | DILZ     | DILI  | Dito  |  |  |

|                       | (BRKL)                             | Reset:          | 0                            | 0        | 0       | 0        | 0           | 0        | 0     | 0     |  |  |

|                       | Break Status and Control           | Read:           | BRKE                         | BRKA     | 0       | 0        | 0           | 0        | 0     | 0     |  |  |

| \$FE0E                | Register                           | Write:          | DITTLE                       | DNINA    |         |          |             |          |       |       |  |  |

|                       | (BRKSCR)                           | Reset:          | 0 0 0 0                      |          |         |          | 0           | 0        | 0     | 0     |  |  |

|                       |                                    | (               |                              |          |         |          |             |          |       |       |  |  |

|                       | COP Control Register               | Read:           | Low byte of reset vector     |          |         |          |             |          |       |       |  |  |

| \$FFFF                | (COPCTL)                           | Write:          |                              |          | Writing |          | counter (an | y value) |       |       |  |  |

|                       |                                    | Reset:          |                              |          |         |          |             |          |       |       |  |  |

|                       |                                    |                 | = Unimplemented R = Reserved |          |         |          |             |          |       |       |  |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 5)

Technical Data MC68H(R)C908JL3 — Rev. 1.1

34 Memory Freescale Semiconductor

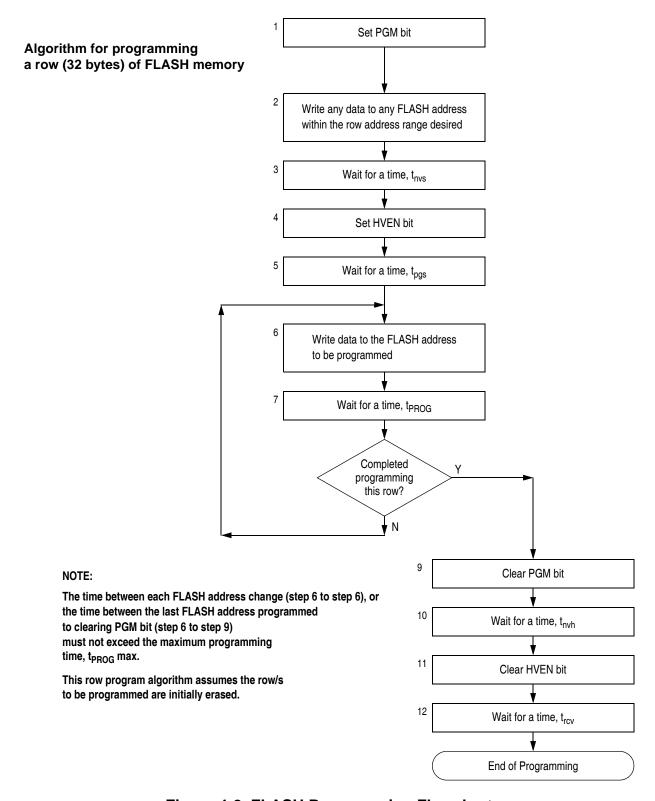

Figure 4-2. FLASH Programming Flowchart

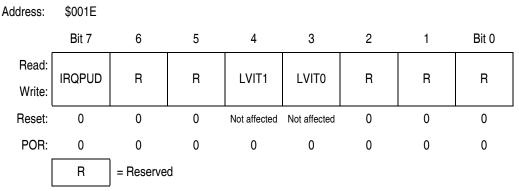

# **Configuration Register (CONFIG)**

# 5.3 Functional Description

The configuration register is used in the initialization of various options. The configuration register can be written once after each reset. All of the configuration register bits are cleared during reset. Since the various options affect the operation of the MCU it is recommended that this register be written immediately after reset. The configuration register is located at \$001E and \$001F, and may be read at anytime.

**NOTE:** The CONFIG registers are one-time writable by the user after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in **Figure 5-1** and **Figure 5-2**.

Figure 5-1. Configuration Register 2 (CONFIG2)

IRQPUD — IRQ1 Pin Pull-up control bit

1 = Internal Pull-up is disconnected

0 = Internal Pull-up is connected between  $\overline{IRQ1}$  pin and  $V_{DD}$

LVIT1, LVIT0 — Low Voltage Inhibit trip voltage selection bits

Detail description of the LVI control signals is given in Section 16.

**Table 6-1. Instruction Set Summary**

| Source<br>Form                                                                                | Operation                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |          | Effect on CCR |           |          |          | Address<br>Mode                       | ope                                              | Operand                                         | es                                   |

|-----------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|---------------|-----------|----------|----------|---------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| FOIIII                                                                                        |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |          | I             | N         | z        | С        | Addı<br>Mod                           | əpoodo                                           | Ope                                             | Cycles                               |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB,X<br>SUB opr,SP<br>SUB opr,SP | Subtract                  | A ← (A) − (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>\$</b> | _        | _             | <b>‡</b>  | <b>‡</b> | <b>\</b> | IMM DIR EXT IX2 IX1 IX SP1 SP2        | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| SWI                                                                                           | Software Interrupt        | $\begin{array}{c} \text{PC} \leftarrow (\text{PC}) + 1;  \text{Push}  (\text{PCL}) \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{Push}  (\text{PCH}) \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{Push}  (\text{X}) \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{Push}  (\text{A}) \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{Push}  (\text{CCR}) \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{I} \leftarrow 1 \\ \text{PCH} \leftarrow \text{Interrupt}  \text{Vector}  \text{High}  \text{Byte} \\ \text{PCL} \leftarrow \text{Interrupt}  \text{Vector}  \text{Low}  \text{Byte} \end{array}$ |           |          | 1             |           |          | -        | INH                                   | 83                                               |                                                 | 9                                    |

| TAP                                                                                           | Transfer A to CCR         | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>‡</b>  | <b>‡</b> | \$            | <b>‡</b>  | <b>‡</b> | <b>‡</b> | INH                                   | 84                                               |                                                 | 2                                    |

| TAX                                                                                           | Transfer A to X           | X ← (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _         | _        | _             | _         | -        | _        | INH                                   | 97                                               |                                                 | 1                                    |

| TPA                                                                                           | Transfer CCR to A         | A ← (CCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _         | -        | _             | -         | _        | -        | INH                                   | 85                                               |                                                 | 1                                    |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP                                  | Test for Negative or Zero | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0         | _        | _             | <b>\$</b> | <b>‡</b> | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D               | dd<br>ff<br>ff                                  | 3<br>1<br>1<br>3<br>2<br>4           |

| TSX                                                                                           | Transfer SP to H:X        | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -         | -        | -             | -         | -        | _        | INH                                   | 95                                               |                                                 | 2                                    |

| TXA                                                                                           | Transfer X to A           | $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _         | -        | _             | -         | -        | -        | INH                                   | 9F                                               |                                                 | 1                                    |

| TXS                                                                                           | Transfer H:X to SP        | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -         | -        | -             | -         | -        | -        | INH                                   | 94                                               |                                                 | 2                                    |

# System Integration Module (SIM)

#### 7.4.2.5 LVI Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the LVI trip voltage  $V_{TRIP}$ . The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RSTB) is held low while the SIM counter counts out 4096 2OSCCLK cycles. Sixty-four 2OSCOUT cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the (RSTB) pin for all internal reset sources.

### 7.5 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as a prescaler for the computer operating properly module (COP). The SIM counter uses 12 stages for counting, followed by a 13th stage that triggers a reset of SIM counters and supplies the clock for the COP module. The SIM counter is clocked by the falling edge of 2OSCOUT.

### 7.5.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit asserts the signal PORRST. Once the SIM is initialized, it enables the oscillator to drive the bus clock state machine.

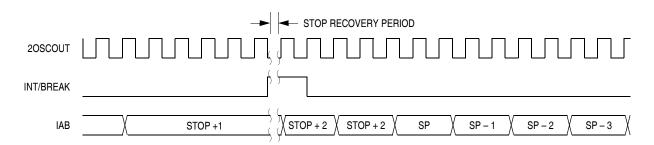

## 7.5.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt, break, or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the mask option register. If the SSREC bit is a logic one, then the stop recovery is reduced from the normal delay of 4096 2OSCOUT cycles down to 32 2OSCOUT cycles. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode. External crystal applications should use the full stop recovery time, that is, with SSREC cleared in the configuration register (CONFIG).

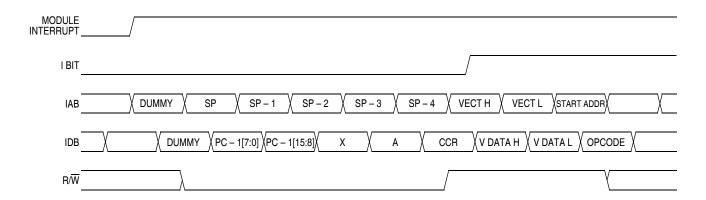

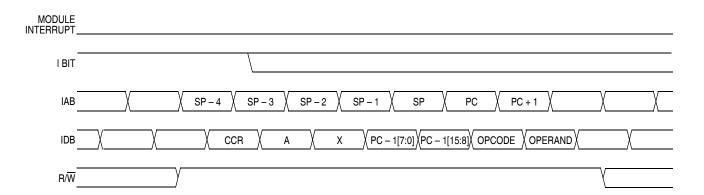

At the beginning of an interrupt, the CPU saves the CPU register contents on the stack and sets the interrupt mask (I bit) to prevent additional interrupts. At the end of an interrupt, the RTI instruction recovers the CPU register contents from the stack so that normal processing can resume. Figure 7-9 shows interrupt entry timing. Figure 7-10 shows interrupt recovery timing.

Figure 7-9. Interrupt Entry

Figure 7-10. Interrupt Recovery

### 7.6.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register), and if the corresponding interrupt enable bit is

MC68H(R)C908JL3 — Rev. 1.1

### System Integration Module (SIM)

set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

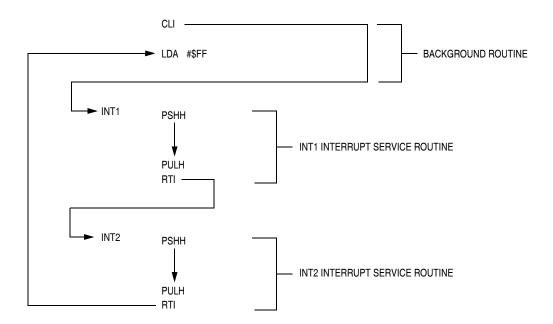

If more than one interrupt is pending at the end of an instruction execution, the highest priority interrupt is serviced first. **Figure 7-11** demonstrates what happens when two interrupts are pending. If an interrupt is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

Figure 7-11. Interrupt Recognition Example

The LDA opcode is prefetched by both the INT1 and INT2 RTI instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

**NOTE:**

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

### 7.6.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an interrupt regardless of the state of the interrupt mask (I bit) in the condition code register.

**NOTE:** A software interrupt pushes PC onto the stack. A software interrupt does **not** push PC - 1, as a hardware interrupt does.

### 7.6.2 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. **Table 7-3** summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

INT **Priority** Source Flag Mask<sup>1</sup> Register **Vector Address** Flag Highest Reset \$FFFE\_\$FFFF **SWI** Instruction \$FFFC-\$FFFD IRQ1 Pin IRQF1 IMASK1 IF1 \$FFFA-\$FFFB Timer Channel 0 Interrupt CH0F CH0IE IF3 \$FFF6-\$FFF7 Timer Channel 1 Interrupt CH1F CH1IE IF4 \$FFF4-\$FFF5 TOF TOIE IF5 Timer Overflow Interrupt \$FFF2-\$FFF3 Keyboard Interrupt **KEYF IMASKK** IF14 \$FFE0-\$FFE1 ADC Conversion Complete Interrupt **AIEN** IF15 COCO \$FFDE-\$FFDF Lowest

**Table 7-3. Interrupt Sources**

Note:

<sup>1.</sup> The I bit in the condition code register is a global mask for all interrupts sources except the SWI instruction.

Figure 7-19. Stop Mode Recovery from Interrupt or Break

# 7.8 SIM Registers

The SIM has three memory mapped registers. **Table 7-4** shows the mapping of these registers.

Address

Register

Access Mode

\$FE00

BSR

User

\$FE01

RSR

User

\$FE03

BFCR

User

Table 7-4. SIM Registers

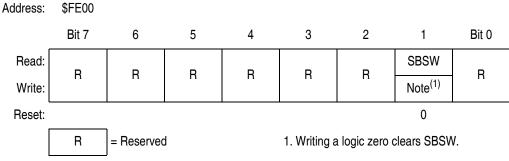

### 7.8.1 Break Status Register (BSR)

The break status register contains a flag to indicate that a break caused an exit from stop or wait mode.

Figure 7-20. Break Status Register (BSR)

# Oscillator (OSC)

# 8.7 Oscillator During Break Mode

The oscillator continues to drive OSCOUT and 2OSCOUT when the device enters the break state.

### Technical Data — MC68H(R)C908JL3

# Section 9. Monitor ROM (MON)

### 9.1 Contents

| 9.2   | Introduction           |

|-------|------------------------|

| 9.3   | Features               |

| 9.4   | Functional Description |

| 9.4.1 | Entering Monitor Mode  |

| 9.4.2 | Baud Rate107           |

| 9.4.3 | Data Format            |

| 9.4.4 | Echoing108             |

| 9.4.5 | Break Signal           |

| 9.4.6 | Commands109            |

| 9.5   | Security               |

#### 9.2 Introduction

This section describes the monitor ROM (MON) and the monitor mode entry methods. The monitor ROM allows complete testing of the MCU through a single-wire interface with a host computer. This mode is also used for programming and erasing of FLASH memory in the MCU. Monitor mode entry can be achieved without use of the higher test voltage,  $V_{DD} + V_{HI}$ , as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

MC68H(R)C908JL3 — Rev. 1.1

write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- When changing to a longer pulse width, enable channel x TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

NOTE:

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

### 10.5.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function, and TIM channel 1 status and control register

### Timer Interface Module (TIM)

overflow occurs before the clearing sequence is complete, then writing logic zero to TOF has no effect. Therefore, a TOF interrupt request cannot be lost due to inadvertent clearing of TOF. Reset clears the TOF bit. Writing a logic one to TOF has no effect.

- 1 = TIM counter has reached modulo value

- 0 = TIM counter has not reached modulo value

#### TOIE — TIM Overflow Interrupt Enable Bit

This read/write bit enables TIM overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

- 1 = TIM overflow interrupts enabled

- 0 = TIM overflow interrupts disabled

### TSTOP — TIM Stop Bit

This read/write bit stops the TIM counter. Counting resumes when TSTOP is cleared. Reset sets the TSTOP bit, stopping the TIM counter until software clears the TSTOP bit.

- 1 = TIM counter stopped

- 0 = TIM counter active

# **NOTE:** Do not set the TSTOP bit before entering wait mode if the TIM is required to exit wait mode.

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as logic zero. Reset clears the TRST bit.

- 1 = Prescaler and TIM counter cleared

- 0 = No effect

# **NOTE:** Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

#### PS[2:0] — Prescaler Select Bits

These read/write bits select one of the seven prescaler outputs as the input to the TIM counter as **Table 10-2** shows. Reset clears the PS[2:0] bits.

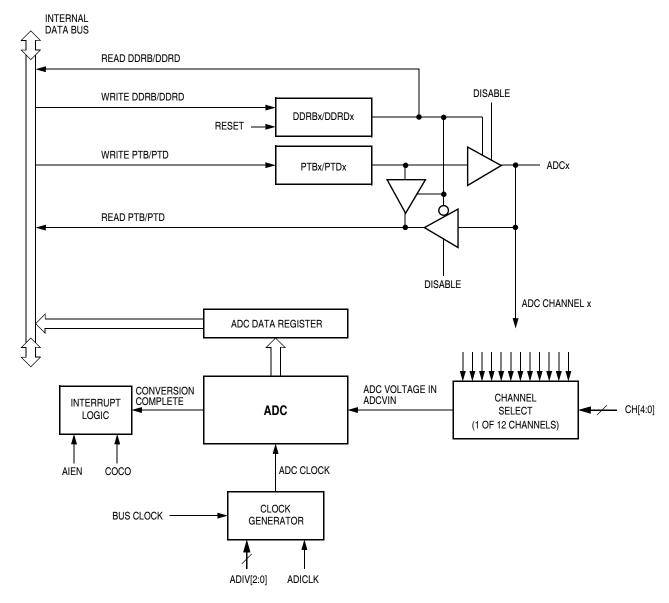

Figure 11-2. ADC Block Diagram

#### 11.4.1 ADC Port I/O Pins

PTB0-PTB7 and PTD0-PTD3 are general-purpose I/O pins that are shared with the ADC channels. The channel select bits (ADC Status and Control register, \$003C), define which ADC channel/port pin will be used as the input signal. The ADC overrides the port I/O logic by forcing that pin as input to the ADC. The remaining ADC channels/port pins are controlled by the port I/O logic and can be used as general-purpose I/O.

MC68H(R)C908JL3 - Rev. 1.1

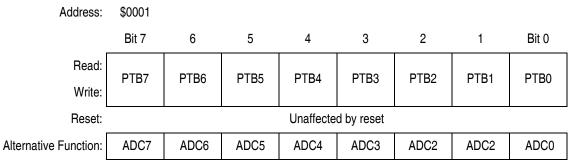

### 12.5 Port B

Port B is an 8-bit special function port that shares all eight of its port pins with the Analog-to-Digital converter (ADC) module, **See Section 11.**

### 12.5.1 Port B Data Register (PTB)

The port B data register contains a data latch for each of the eight port B pins.

Figure 12-6. Port B Data Register (PTB)

### PTB[7:0] — Port B Data Bits

These read/write bits are software programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

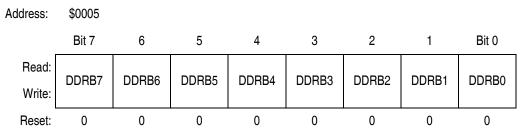

### 12.5.2 Data Direction Register B (DDRB)

Data direction register B determines whether each port B pin is an input or an output. Writing a logic one to a DDRB bit enables the output buffer for the corresponding port B pin; a logic zero disables the output buffer.

Figure 12-7. Data Direction Register B (DDRB)

MC68H(R)C908JL3 — Rev. 1.1

# Low Voltage Inhibit (LVI)