Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | LED, LVD, POR, PWM                                                       |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                              |

| Data Converters            | A/D 12x8b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hrc908jk1cdw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

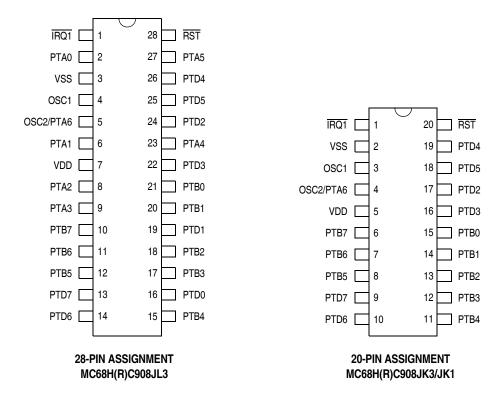

## 1.5 Pin Assignments

MC68H(R)C908JL3 - Rev. 1.1

The MC68H(R)C908JL3 is available in 28-pin packages and the MC68H(R)C908JK3/JK1 in 20-pin packages. Figure 1-2 shows the pin assignment for the two packages.

Pins not bonded out on 20-pin package: PTA0, PTA1, PTA2, PTA3, PTA4, PTA5, PTD0, PTD1.

**Technical Data**

Figure 1-2. MCU Pin Assignments

Freescale Semiconductor

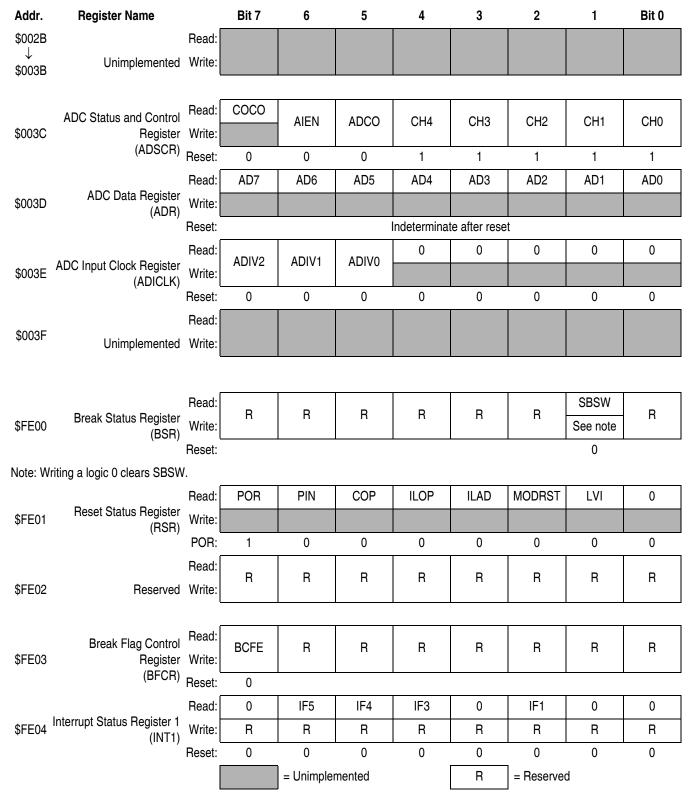

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 5)

MC68H(R)C908JL3 - Rev. 1.1

**Technical Data**

## Technical Data — MC68H(R)C908JL3

## Section 4. FLASH Memory (FLASH)

#### 4.1 Contents

| 4.2 | Introduction                 | . 39 |

|-----|------------------------------|------|

| 4.3 | Functional Description       | .40  |

| 4.4 | FLASH Control Register       | .40  |

| 4.5 | FLASH Block Erase Operation  | .41  |

| 4.6 | FLASH Mass Erase Operation   | .42  |

| 4.7 | FLASH Program Operation      | .43  |

| 4.8 | FLASH Protection             | .44  |

| 4.9 | FLASH Block Protect Register | . 46 |

#### 4.2 Introduction

This section describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

MC68H(R)C908JL3/JK3: 4096 bytes user FLASH from \$EC00 - \$FBFF.

MC68H(R)C908JK1: 1536 bytes user FLASH from \$F600 - \$FBFF.

## Central Processor Unit (CPU)

**Table 6-1. Instruction Set Summary**

| Source<br>Form                                                                                   | Operation                              | Description                              |          |          |   | ct (     |          |          | Address<br>Mode                                                         | Opcode                                           | Operand                                         | les                                  |

|--------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|----------|----------|---|----------|----------|----------|-------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| 101111                                                                                           |                                        |                                          | ٧        | Н        | ı | N        | Z        | С        | Add                                                                     | obc                                              | Ope                                             | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC opr,X<br>ADC ,X<br>ADC opr,SP<br>ADC opr,SP | Add with Carry                         | $A \leftarrow (A) + (M) + (C)$           | <b>‡</b> | <b>‡</b> |   | <b>‡</b> | <b>‡</b> | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                     | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ADD #opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD opr,X<br>ADD ,X<br>ADD opr,SP<br>ADD opr,SP | Add without Carry                      | A ← (A) + (M)                            | <b>‡</b> | <b>‡</b> | _ | <b>‡</b> | <b>‡</b> | <b>‡</b> | IMM DIR EXT IX2 IX1 IX SP1 SP2                                          | AB BB CB DB EB FB 9EEB                           | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| AIS #opr                                                                                         | Add Immediate Value (Signed) to SP     | SP ← (SP) + (16 « M)                     | _        | -        | _ | -        | -        | _        | IMM                                                                     | A7                                               | ii                                              | 2                                    |

| AIX #opr                                                                                         | Add Immediate Value (Signed) to H:X    | H:X ← (H:X) + (16 « M)                   | -        | -        | - | -        | -        | -        | IMM                                                                     | AF                                               | ii                                              | 2                                    |

| AND #opr<br>AND opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND ,X<br>AND opr,SP<br>AND opr,SP   | Logical AND                            | A ← (A) & (M)                            | 0        | _        | _ | \$       | \$       | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                     | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                     | Arithmetic Shift Left<br>(Same as LSL) | C 0 0 b7 b0                              | <b>‡</b> | _        | _ | <b>‡</b> | <b>‡</b> | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                   | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                  | Arithmetic Shift Right                 | b7 b0                                    | <b>‡</b> | _        | _ | <b>‡</b> | <b></b>  | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                   | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| BCC rel                                                                                          | Branch if Carry Bit Clear              | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$ | -        | -        | _ | -        | -        | -        | REL                                                                     | 24                                               | rr                                              | 3                                    |

| BCLR n, opr                                                                                      | Clear Bit n in M                       | Mn ← 0                                   | _        | _        | _ | _        | _        | _        | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D           | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd    | 4<br>4<br>4<br>4<br>4<br>4<br>4      |

**Technical Data**

MC68H(R)C908JL3 — Rev. 1.1

## Central Processor Unit (CPU)

**Table 6-1. Instruction Set Summary**

| Source                                                                                                | Operation                         | Description                                                                                                                                                                                                                                                                                                                |   |   |   | ct c | n |          | ess                                                                                          | ode                                          | and                                                                  | Cycles                               |

|-------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|------|---|----------|----------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|--------------------------------------|

| Form                                                                                                  |                                   |                                                                                                                                                                                                                                                                                                                            | ٧ | Н | I | N    | z | С        | Address<br>Mode                                                                              | Opcode                                       | Opcode<br>Operand                                                    |                                      |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear | PC ← (PC) + 3 + rel? (Mn) = 0                                                                                                                                                                                                                                                                                              | _ | _ | _ | _    | _ | <b>‡</b> | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7)                      | 01<br>03<br>05<br>07<br>09<br>0B<br>0D       | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5 5 5 5 5 5 5 5                      |

| BRN rel                                                                                               | Branch Never                      | PC ← (PC) + 2                                                                                                                                                                                                                                                                                                              | - | - | - | _    | _ | _        | REL                                                                                          | 21                                           | rr                                                                   | 3                                    |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set   | PC ← (PC) + 3 + rel? (Mn) = 1                                                                                                                                                                                                                                                                                              | _ | _ | _ | _    | _ | \$       | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7)                      | 00<br>02<br>04<br>06<br>08<br>0A<br>0C       | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M             | Mn ← 1                                                                                                                                                                                                                                                                                                                     | _ | _ | _ |      | _ |          | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                         | 4<br>4<br>4<br>4<br>4<br>4<br>4      |

| BSR rel                                                                                               | Branch to Subroutine              | $PC \leftarrow (PC) + 2; push (PCL)$ $SP \leftarrow (SP) - 1; push (PCH)$ $SP \leftarrow (SP) - 1$ $PC \leftarrow (PC) + rel$                                                                                                                                                                                              | _ | - | _ | _    | _ | _        | REL                                                                                          | AD                                           | rr                                                                   | 4                                    |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal       | PC $\leftarrow$ (PC) + 3 + rel ? (A) - (M) = \$00<br>PC $\leftarrow$ (PC) + 3 + rel ? (A) - (M) = \$00<br>PC $\leftarrow$ (PC) + 3 + rel ? (X) - (M) = \$00<br>PC $\leftarrow$ (PC) + 3 + rel ? (A) - (M) = \$00<br>PC $\leftarrow$ (PC) + 2 + rel ? (A) - (M) = \$00<br>PC $\leftarrow$ (PC) + 4 + rel ? (A) - (M) = \$00 |   | _ | _ | _    | _ | _        | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 31<br>41<br>51<br>61<br>71<br>9E61           | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                      | 5<br>4<br>4<br>5<br>4<br>6           |

| CLC                                                                                                   | Clear Carry Bit                   | C ← 0                                                                                                                                                                                                                                                                                                                      |   | _ | _ | _    | _ | 0        | INH                                                                                          | 98                                           |                                                                      | 1                                    |

| CLI                                                                                                   | Clear Interrupt Mask              | I ← 0                                                                                                                                                                                                                                                                                                                      |   | _ | 0 | _    | _ | _        | INH                                                                                          | 9A                                           |                                                                      | 2                                    |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                                  | Clear                             | $\begin{array}{c} M \leftarrow \$00 \\ A \leftarrow \$00 \\ X \leftarrow \$00 \\ H \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ \end{array}$                                                                                                                     |   | _ | _ | 0    | 1 | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F     | dd<br>ff<br>ff                                                       | 3<br>1<br>1<br>1<br>3<br>2<br>4      |

## Central Processor Unit (CPU)

## System Integration Module (SIM)

#### 7.4.2.5 LVI Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the LVI trip voltage  $V_{TRIP}$ . The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RSTB) is held low while the SIM counter counts out 4096 2OSCCLK cycles. Sixty-four 2OSCOUT cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the (RSTB) pin for all internal reset sources.

#### 7.5 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as a prescaler for the computer operating properly module (COP). The SIM counter uses 12 stages for counting, followed by a 13th stage that triggers a reset of SIM counters and supplies the clock for the COP module. The SIM counter is clocked by the falling edge of 2OSCOUT.

### 7.5.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit asserts the signal PORRST. Once the SIM is initialized, it enables the oscillator to drive the bus clock state machine.

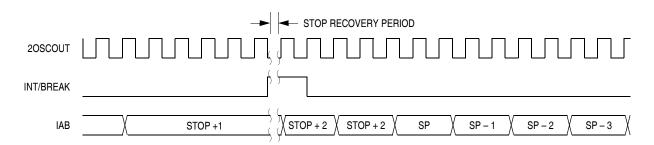

## 7.5.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt, break, or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the mask option register. If the SSREC bit is a logic one, then the stop recovery is reduced from the normal delay of 4096 2OSCOUT cycles down to 32 2OSCOUT cycles. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode. External crystal applications should use the full stop recovery time, that is, with SSREC cleared in the configuration register (CONFIG).

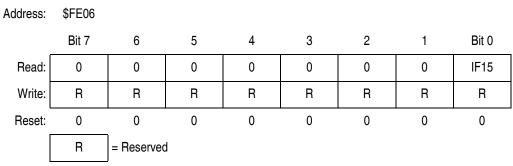

#### 7.6.2.3 Interrupt Status Register 3

Figure 7-14. Interrupt Status Register 3 (INT3)

IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in **Table 7-3**.

1 = Interrupt request present

0 = No interrupt request present

Bit 1 to 7 — Always read 0

#### 7.6.3 **Reset**

All reset sources always have equal and highest priority and cannot be arbitrated.

#### 7.6.4 Break Interrupts

The break module can stop normal program flow at a software-programmable break point by asserting its break interrupt output. (See **Section 17. Break Module (BREAK)**.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

#### 7.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are

MC68H(R)C908JL3 — Rev. 1.1

Technical Data

Figure 7-19. Stop Mode Recovery from Interrupt or Break

## 7.8 SIM Registers

The SIM has three memory mapped registers. **Table 7-4** shows the mapping of these registers.

Address

Register

Access Mode

\$FE00

BSR

User

\$FE01

RSR

User

\$FE03

BFCR

User

Table 7-4. SIM Registers

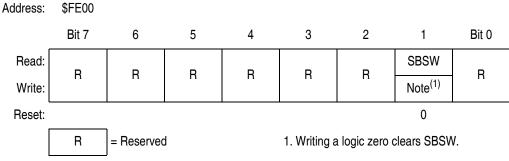

## 7.8.1 Break Status Register (BSR)

The break status register contains a flag to indicate that a break caused an exit from stop or wait mode.

Figure 7-20. Break Status Register (BSR)

## **Monitor ROM (MON)**

#### 9.4.3 Data Format

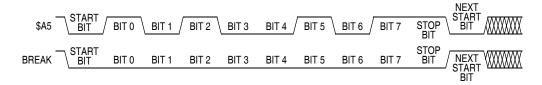

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format. (See Figure 9-3 and Figure 9-4.)

Figure 9-3. Monitor Data Format

Figure 9-4. Sample Monitor Waveforms

The data transmit and receive rate can be anywhere from 4800 baud to 28.8k-baud. Transmit and receive baud rates must be identical.

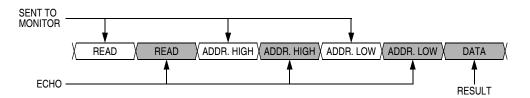

## 9.4.4 Echoing

As shown in **Figure 9-5**, the monitor ROM immediately echoes each received byte back to the PTB0 pin for error checking.

Figure 9-5. Read Transaction

Any result of a command appears after the echo of the last byte of the command.

**Technical Data**

MC68H(R)C908JL3 — Rev. 1.1

# Section 10. Timer Interface Module (TIM)

## 10.1 Contents

| 10.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.3 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.4 Pin Name Conventions116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10.5       Functional Description       117         10.5.1       TIM Counter Prescaler       119         10.5.2       Input Capture       119         10.5.3       Output Compare       119         10.5.3.1       Unbuffered Output Compare       120         10.5.3.2       Buffered Output Compare       120         10.5.4       Pulse Width Modulation (PWM)       121         10.5.4.1       Unbuffered PWM Signal Generation       122         10.5.4.2       Buffered PWM Signal Generation       123         10.5.4.3       PWM Initialization       124 |

| 10.6 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10.7 Wait Mode125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.8 TIM During Break Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10.9 I/O Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10.10 I/O Registers.12710.10.1 TIM Status and Control Register (TSC)12710.10.2 TIM Counter Registers (TCNTH:TCNTL)12910.10.3 TIM Counter Modulo Registers (TMODH:TMODL)13010.10.4 TIM Channel Status and Control Registers (TSC0:TSC1)13110.10.5 TIM Channel Registers (TCH0H/L:TCH1H/L)135                                                                                                                                                                                                                                                                       |

## Timer Interface Module (TIM)

#### 10.2 Introduction

This section describes the timer interface module (TIM2, Version B). The TIM is a two-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions.

Figure 10-1 is a block diagram of the TIM.

#### 10.3 Features

Features of the TIM include the following:

- Two input capture/output compare channels

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Buffered and unbuffered pulse width modulation (PWM) signal generation

- Programmable TIM clock input with 7-frequency internal bus clock prescaler selection

- Free-running or modulo up-count operation

- Toggle any channel pin on overflow

- TIM counter stop and reset bits

- Modular architecture expandable to eight channels

#### 10.4 Pin Name Conventions

The TIM share two I/O pins with two port D I/O pins. The full name of the TIM I/O pins are listed in **Table 10-1**. The generic pin name appear in the text that follows.

**Table 10-1. Pin Name Conventions**

| TIM Generic Pin Names: | TCH0      | TCH1      |

|------------------------|-----------|-----------|

| Full TIM Pin Names:    | PTD4/TCH0 | PTD5/TCH1 |

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM status control register 0 (TSCR0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and clearing the TOVx bit generates a 100% duty cycle output. (See 10.10.4 TIM Channel Status and Control Registers (TSC0:TSC1).)

## 10.6 Interrupts

The following TIM sources can generate interrupt requests:

- TIM overflow flag (TOF) The TOF bit is set when the TIM counter value rolls over to \$0000 after matching the value in the TIM counter modulo registers. The TIM overflow interrupt enable bit, TOIE, enables TIM overflow CPU interrupt requests. TOF and TOIE are in the TIM status and control register.

- TIM channel flags (CH1F:CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIM CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE. Channel x TIM CPU interrupt requests are enabled when CHxIE=1. CHxF and CHxIE are in the TIM channel x status and control register.

#### 10.7 Wait Mode

The WAIT instruction puts the MCU in low-power-consumption standby mode.

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

MC68H(R)C908JL3 — Rev. 1.1

Technical Data

#### 11.4.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

## 11.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating a CPU interrupt after each ADC conversion. A CPU interrupt is generated if the COCO bit is at logic 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

#### 11.6 Low-Power Modes

The following subsections describe the ADC in low-power modes.

#### 11.6.1 Wait Mode

The ADC continues normal operation during wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting the CH[4:0] bits in the ADC Status and Control register to logic 1's before executing the WAIT instruction.

#### 11.6.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

## 11.7 I/O Signals

The ADC module has 12 channels that are shared with I/O port B and port D.

## 13.5 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ1 latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear the latches during the break state. (See Section 7. System Integration Module (SIM).)

To allow software to clear the IRQ1 latch during a break interrupt, write a logic one to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latches during the break state, write a logic zero to the BCFE bit. With BCFE at logic zero (its default state), writing to the ACK1 bit in the IRQ status and control register during the break state has no effect on the IRQ latch.

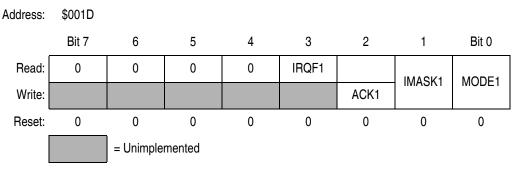

## 13.6 IRQ Status and Control Register (ISCR)

The IRQ Status and Control Register (ISCR) controls and monitors operation of the IRQ module. The ISCR has the following functions:

- Shows the state of the IRQ1 flag

- Clears the IRQ1 latch

- Masks IRQ1 and interrupt request

- Controls triggering sensitivity of the IRQ1 interrupt pin

Figure 13-3. IRQ Status and Control Register (INTSCR)

MC68H(R)C908JL3 — Rev. 1.1

Technical Data

## External Interrupt (IRQ)

IRQF1 — IRQ1 Flag

This read-only status bit is high when the IRQ1 interrupt is pending.

$1 = \overline{IRQ1}$  interrupt pending

$0 = \overline{IRQ1}$  interrupt not pending

ACK1 — IRQ1 Interrupt Request Acknowledge Bit

Writing a logic one to this write-only bit clears the IRQ1 latch. ACK1 always reads as logic zero. Reset clears ACK1.

IMASK1 — IRQ1 Interrupt Mask Bit

Writing a logic one to this read/write bit disables IRQ1 interrupt requests. Reset clears IMASK1.

1 = IRQ1 interrupt requests disabled

0 = IRQ1 interrupt requests enabled

MODE1 — IRQ1 Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ1 pin. Reset clears MODE1.

$1 = \overline{IRQ1}$  interrupt requests on falling edges and low levels

$0 = \overline{IRQ1}$  interrupt requests on falling edges only

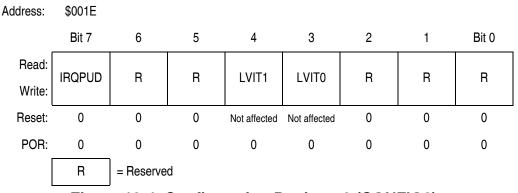

Figure 13-4. Configuration Register 2 (CONFIG2)

IRQPUD — IRQ1 Pin Pull-up control bit

1 = Internal pull-up is disconnected

$0 = Internal pull-up is connected between <math>\overline{IRQ1}$  pin and  $V_{DD}$

#### 14.5 Wait Mode

The keyboard modules remain active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

## 14.6 Stop Mode

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

## 14.7 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect.

#### SBSW — SIM Break Stop/Wait

This status bit is useful in applications requiring a return to wait or stop mode after exiting from a break interrupt. Clear SBSW by writing a logic zero to it. Reset clears SBSW.

- 1 = Stop mode or wait mode was exited by break interrupt

- 0 = Stop mode or wait mode was not exited by break interrupt

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it. The following code is an example of this. Writing zero to the SBSW bit clears it.

```

; This code works if the H register has been pushed onto the stack in the break

; service routine software. This code should be executed at the end of the

; break service routine software.

HIBYTE

EQU

LOBYTE EQU

6

If not SBSW, do RTI

BRCLR SBSW, BSR, RETURN ; See if wait mode or stop mode was exited

; by break.

; If RETURNLO is not zero,

TST

LOBYTE, SP

DOLO

; then just decrement low byte.

BNE

DEC

HIBYTE, SP

; Else deal with high byte, too.

; Point to WAIT/STOP opcode.

DOTIO

DEC

LOBYTE, SP

RETURN

PULH

; Restore H register.

RTI

```

## Technical Data — MC68H(R)C908JL3

## Section 18. Electrical Specifications

## 18.1 Contents

| 18.2  | Introduction                     |

|-------|----------------------------------|

| 18.3  | Absolute Maximum Ratings         |

| 18.4  | Functional Operating Range193    |

| 18.5  | Thermal Characteristics          |

| 18.6  | 5V DC Electrical Characteristics |

| 18.7  | 5V Control Timing                |

| 18.8  | 5V Oscillator Characteristics    |

| 18.9  | 3V DC Electrical Characteristics |

| 18.10 | 3V Control Timing198             |

| 18.11 | 3V Oscillator Characteristics    |

| 18.12 | Typical Supply Currents          |

| 18.13 | ADC Characteristics              |

| 18.14 | Memory Characteristics           |

## 18.2 Introduction

This section contains electrical and timing specifications.

## 18.4 Functional Operating Range

**Table 18-2. Operating Range**

| Characteristic              | Symbol         | Va          | Unit       |    |

|-----------------------------|----------------|-------------|------------|----|

| Operating temperature range | T <sub>A</sub> | -40 to +125 | -40 to +85 | °C |

| Operating voltage range     | $V_{DD}$       | 5V ± 10%    | 3V ± 10%   | V  |

### 18.5 Thermal Characteristics

**Table 18-3. Thermal Characteristics**

| Characteristic                                                     | Symbol                | Value                                                                    | Unit                 |

|--------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------|----------------------|

| Thermal resistance 20-Pin PDIP 20-Pin SOIC 28-Pin PDIP 28-Pin SOIC | $\theta_{	extsf{JA}}$ | 70<br>70<br>70<br>70                                                     | °C/W<br>°C/W<br>°C/W |

| I/O pin power dissipation                                          | P <sub>I/O</sub>      | User determined                                                          | W                    |

| Power dissipation <sup>(1)</sup>                                   | P <sub>D</sub>        | $P_D = (I_{DD} \times V_{DD}) + P_{I/O} = K/(T_J + 273 \text{ °C})$      | W                    |

| Constant <sup>(2)</sup>                                            | К                     | $P_{D} \times (T_{A} + 273 \text{ °C})$ $+ P_{D}^{2} \times \theta_{JA}$ | W/°C                 |

| Average junction temperature                                       | TJ                    | $T_A + (P_D \times \theta_{JA})$                                         | °C                   |

| Maximum junction temperature                                       | $T_JM$                | 100                                                                      | °C                   |

Power dissipation is a function of temperature.

K constant unique to the device. K can be determined for a known T<sub>A</sub> and measured P<sub>D</sub>. With this value of K, P<sub>D</sub> and T<sub>J</sub> can be determined for any value of T<sub>A</sub>.