Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 14                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                            |

| Data Converters            | A/D 12x8b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 20-DIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchrc908jk1cpe |

# Table of Contents

|                                                          | I/O Signals                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.4.1                                                   | 2OSCOUT175                                                                                                                                                                                                                                                                                                        |

| 15.4.2                                                   | COPCTL Write                                                                                                                                                                                                                                                                                                      |

| 15.4.3                                                   | Power-On Reset175                                                                                                                                                                                                                                                                                                 |

| 15.4.4                                                   | Internal Reset175                                                                                                                                                                                                                                                                                                 |

| 15.4.5                                                   | Reset Vector Fetch176                                                                                                                                                                                                                                                                                             |

| 15.4.6                                                   | COPD (COP Disable)176                                                                                                                                                                                                                                                                                             |

| 15.4.7                                                   | COPRS (COP Rate Select)                                                                                                                                                                                                                                                                                           |

| 15.5                                                     | COP Control Register177                                                                                                                                                                                                                                                                                           |

| 15.6                                                     | Interrupts                                                                                                                                                                                                                                                                                                        |

| 15.7                                                     | Monitor Mode                                                                                                                                                                                                                                                                                                      |

| 15.8                                                     | Low-Power Modes                                                                                                                                                                                                                                                                                                   |

| 15.8.1                                                   | Wait Mode                                                                                                                                                                                                                                                                                                         |

| 15.8.2                                                   | Stop Mode                                                                                                                                                                                                                                                                                                         |

| 15.9                                                     | COP Module During Break Mode                                                                                                                                                                                                                                                                                      |

|                                                          | O                                                                                                                                                                                                                                                                                                                 |

|                                                          | Section 16. Low Voltage Inhibit (LVI)                                                                                                                                                                                                                                                                             |

| 16.1                                                     | Contents                                                                                                                                                                                                                                                                                                          |

| 16.1<br>16.2                                             | • , ,                                                                                                                                                                                                                                                                                                             |

|                                                          | Contents                                                                                                                                                                                                                                                                                                          |

| 16.2                                                     | Contents                                                                                                                                                                                                                                                                                                          |

| 16.2<br>16.3                                             | Contents       .179         Introduction       .179         Features       .179                                                                                                                                                                                                                                   |

| 16.2<br>16.3<br>16.4<br>16.5                             | Contents         .179           Introduction         .179           Features         .179           Functional Description         .180                                                                                                                                                                           |

| 16.2<br>16.3<br>16.4<br>16.5                             | Contents       .179         Introduction       .179         Features       .179         Functional Description       .180         LVI Control Register (CONFIG2/CONFIG1)       .180         Low-Power Modes       .181                                                                                            |

| 16.2<br>16.3<br>16.4<br>16.5<br>16.6                     | Contents       179         Introduction       179         Features       179         Functional Description       180         LVI Control Register (CONFIG2/CONFIG1)       180         Low-Power Modes       181         Wait Mode       181                                                                      |

| 16.2<br>16.3<br>16.4<br>16.5<br>16.6<br>16.6.1           | Contents       179         Introduction       179         Features       179         Functional Description       180         LVI Control Register (CONFIG2/CONFIG1)       180         Low-Power Modes       181         Wait Mode       181         Stop Mode       181                                          |

| 16.2<br>16.3<br>16.4<br>16.5<br>16.6<br>16.6.1<br>16.6.2 | Contents       179         Introduction       179         Features       179         Functional Description       180         LVI Control Register (CONFIG2/CONFIG1)       180         Low-Power Modes       181         Wait Mode       181         Stop Mode       181         Section 17. Break Module (BREAK) |

| 16.2<br>16.3<br>16.4<br>16.5<br>16.6<br>16.6.1           | Contents       179         Introduction       179         Features       179         Functional Description       180         LVI Control Register (CONFIG2/CONFIG1)       180         Low-Power Modes       181         Wait Mode       181         Stop Mode       181                                          |

| 16.2<br>16.3<br>16.4<br>16.5<br>16.6<br>16.6.1<br>16.6.2 | Contents       179         Introduction       179         Features       179         Functional Description       180         LVI Control Register (CONFIG2/CONFIG1)       180         Low-Power Modes       181         Wait Mode       181         Stop Mode       181         Section 17. Break Module (BREAK) |

**Technical Data**

MC68H(R)C908JL3 — Rev. 1.1

| 17.4<br>17.4.1<br>17.4.2<br>17.4.3<br>17.4.4 | TIM During Break Interrupts186        |

|----------------------------------------------|---------------------------------------|

| 17.5<br>17.5.1<br>17.5.2<br>17.5.3<br>17.5.4 | Break Address Registers               |

| 17.6<br>17.6.1<br>17.6.2                     |                                       |

|                                              | Section 18. Electrical Specifications |

| 18.1                                         | Contents                              |

| 18.2                                         | Introduction191                       |

| 18.3                                         | Absolute Maximum Ratings              |

| 18.4                                         | Functional Operating Range193         |

| 18.5                                         | Thermal Characteristics               |

| 18.6                                         | 5V DC Electrical Characteristics194   |

| 18.7                                         | 5V Control Timing195                  |

| 18.8                                         | 5V Oscillator Characteristics         |

| 18.9                                         | 3V DC Electrical Characteristics197   |

| 18.10                                        | 3V Control Timing198                  |

| 18.11                                        | 3V Oscillator Characteristics         |

| 18.12                                        | Typical Supply Currents               |

| 18.13                                        | ADC Characteristics                   |

| 18.14                                        | Memory Characteristics                |

MC68H(R)C908JL3 — Rev. 1.1

Technical Data

# **Table of Contents**

# **Section 19. Mechanical Specifications**

| 19.1 | Contents                         |

|------|----------------------------------|

| 19.2 | Introduction                     |

| 19.3 | 20-Pin PDIP                      |

| 19.4 | 20-Pin SOIC                      |

| 19.5 | 28-Pin PDIP                      |

| 19.6 | 28-Pin SOIC                      |

|      | Section 20. Ordering Information |

| 20.1 | Contents                         |

| 20.2 | Introduction                     |

| 20.3 | MC Order Numbers                 |

**Technical Data**

## 1.5 Pin Assignments

MC68H(R)C908JL3 - Rev. 1.1

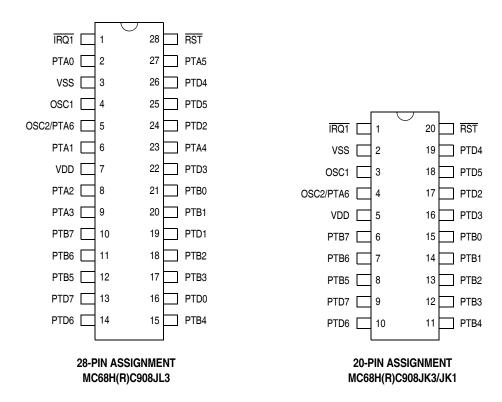

The MC68H(R)C908JL3 is available in 28-pin packages and the MC68H(R)C908JK3/JK1 in 20-pin packages. **Figure 1-2** shows the pin assignment for the two packages.

Pins not bonded out on 20-pin package: PTA0, PTA1, PTA2, PTA3, PTA4, PTA5, PTD0, PTD1.

Figure 1-2. MCU Pin Assignments

Freescale Semiconductor General Description 25

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation or block erase operation when the ERASE bit is set.

- 1 = Mass Erase operation selected

- 0 = Block Erase operation selected

#### ERASE — Erase Control Bit

This read/write bit configures the memory for erase operation. This bit and the PGM bit should not be set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation not selected

### PGM — Program Control Bit

This read/write bit configures the memory for program operation. This bit and the ERASE bit should not be set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation not selected

## 4.5 FLASH Block Erase Operation

Use the following procedure to erase a block of FLASH memory. A block consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80 or \$XXC0. The 48-byte User Interrupt Vectors area also forms a block. Any block within the 4K bytes User Memory area (\$EC00–\$FBFF) can be erased alone. The 48-byte User Interrupt Vector blocks can not be erased alone due to security concern. Mass erase is required to erase this block.

- Set the ERASE bit and clear the MASS bit in the FLASH Control Register.

- 2. Write any data to any FLASH location within the address range of the block to be erased.

- 3. Wait for a time,  $t_{nvs}$  (10 $\mu$ s).

- 4. Set the HVEN bit.

# Central Processor Unit (CPU)

**Table 6-1. Instruction Set Summary**

| Source<br>Form                                                                                 | Operation                           | Description                                                                                                                                                             |           | E |   | ct o      |           |          | Address<br>Mode                                     | ode                                              | Operand                                         | es                                   |

|------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---|---|-----------|-----------|----------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           |                                     | ·                                                                                                                                                                       | ٧         | Н | I | N         | z         | С        | Addı                                                | Opcode                                           | Ope                                             | Cycles                               |

| EOR #opr<br>EOR opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR ,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A               | A ← (A ⊕ M)                                                                                                                                                             | 0         | _ | _ | \$        | \$        | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8         | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                           | $M \leftarrow (M) + 1$<br>$A \leftarrow (A) + 1$<br>$X \leftarrow (X) + 1$<br>$M \leftarrow (M) + 1$<br>$M \leftarrow (M) + 1$<br>$M \leftarrow (M) + 1$                | <b>‡</b>  | _ | _ | <b>‡</b>  | <b>‡</b>  | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff                                        | 4<br>1<br>1<br>4<br>3<br>5           |

| JMP opr<br>JMP opr<br>JMP opr,X<br>JMP opr,X<br>JMP ,X                                         | Jump                                | PC ← Jump Address                                                                                                                                                       | _         | _ | _ | _         | _         | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC<br>CC<br>DC<br>EC<br>FC                       | dd<br>hh II<br>ee ff<br>ff                      | 2<br>3<br>4<br>3<br>2                |

| JSR opr<br>JSR opr<br>JSR opr,X<br>JSR opr,X<br>JSR ,X                                         | Jump to Subroutine                  | PC $\leftarrow$ (PC) + $n$ ( $n$ = 1, 2, or 3)<br>Push (PCL); SP $\leftarrow$ (SP) – 1<br>Push (PCH); SP $\leftarrow$ (SP) – 1<br>PC $\leftarrow$ Unconditional Address | _         | _ | _ | _         | _         | -        | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD<br>CD<br>DD<br>ED<br>FD                       | dd<br>hh II<br>ee ff<br>ff                      | 4<br>5<br>6<br>5<br>4                |

| LDA #opr<br>LDA opr<br>LDA opr<br>LDA opr,X<br>LDA opr,X<br>LDA ,X<br>LDA opr,SP<br>LDA opr,SP | Load A from M                       | A ← (M)                                                                                                                                                                 | 0         | _ | _ | <b>‡</b>  | <b>‡</b>  | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A6<br>B6<br>C6<br>D6<br>E6<br>F6<br>9EE6         | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LDHX #opr<br>LDHX opr                                                                          | Load H:X from M                     | H:X ← (M:M + 1)                                                                                                                                                         | 0         | _ | _ | <b>‡</b>  | <b>‡</b>  | _        | IMM<br>DIR                                          | 45<br>55                                         | ii jj<br>dd                                     | 3<br>4                               |

| LDX #opr<br>LDX opr<br>LDX opr<br>LDX opr,X<br>LDX opr,X<br>LDX ,X<br>LDX opr,SP<br>LDX opr,SP | Load X from M                       | X ← (M)                                                                                                                                                                 | 0         | _ | _ | <b>\_</b> | <b>\_</b> | _        | IMM DIR EXT IX2 IX1 IX SP1 SP2                      | AE<br>BE<br>CE<br>DE<br>EE<br>FE<br>9EEE<br>9EDE | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LSL opr<br>LSLA<br>LSLX<br>LSL opr,X<br>LSL ,X<br>LSL opr,SP                                   | Logical Shift Left<br>(Same as ASL) | © 0 b7 b0                                                                                                                                                               | <b>\$</b> | _ | _ | <b>‡</b>  | <b>‡</b>  | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

**Technical Data**

MC68H(R)C908JL3 — Rev. 1.1

# System Integration Module (SIM)

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

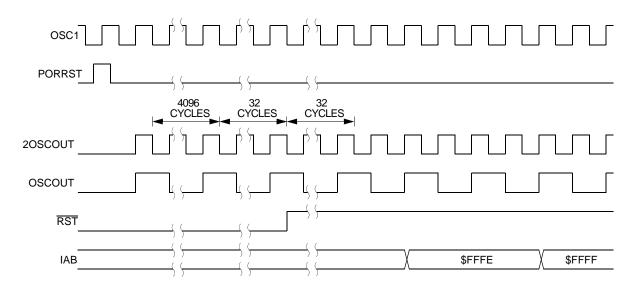

#### 7.4.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power-on has occurred. The external reset pin (RST) is held low while the SIM counter counts out 4096 2OSCOUT cycles. Sixty-four 2OSCOUT cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power-on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables the oscillator to drive 2OSCOUT.

- Internal clocks to the CPU and modules are held inactive for 4096

2OSCOUT cycles to allow stabilization of the oscillator.

- The RST pin is driven low during the oscillator stabilization time.

- The POR bit of the reset status register (RSR) is set and all other bits in the register are cleared.

Figure 7-7. POR Recovery

# System Integration Module (SIM)

#### 7.4.2.5 LVI Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the LVI trip voltage  $V_{TRIP}$ . The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RSTB) is held low while the SIM counter counts out 4096 2OSCCLK cycles. Sixty-four 2OSCOUT cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the (RSTB) pin for all internal reset sources.

### 7.5 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as a prescaler for the computer operating properly module (COP). The SIM counter uses 12 stages for counting, followed by a 13th stage that triggers a reset of SIM counters and supplies the clock for the COP module. The SIM counter is clocked by the falling edge of 2OSCOUT.

## 7.5.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit asserts the signal PORRST. Once the SIM is initialized, it enables the oscillator to drive the bus clock state machine.

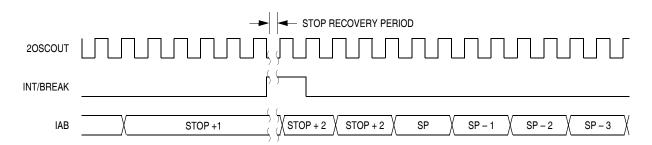

## 7.5.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt, break, or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the mask option register. If the SSREC bit is a logic one, then the stop recovery is reduced from the normal delay of 4096 2OSCOUT cycles down to 32 2OSCOUT cycles. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode. External crystal applications should use the full stop recovery time, that is, with SSREC cleared in the configuration register (CONFIG).

Figure 7-19. Stop Mode Recovery from Interrupt or Break

## 7.8 SIM Registers

The SIM has three memory mapped registers. **Table 7-4** shows the mapping of these registers.

Address

Register

Access Mode

\$FE00

BSR

User

\$FE01

RSR

User

\$FE03

BFCR

User

Table 7-4. SIM Registers

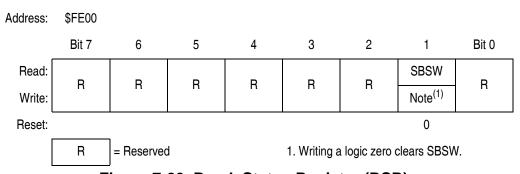

## 7.8.1 Break Status Register (BSR)

The break status register contains a flag to indicate that a break caused an exit from stop or wait mode.

Figure 7-20. Break Status Register (BSR)

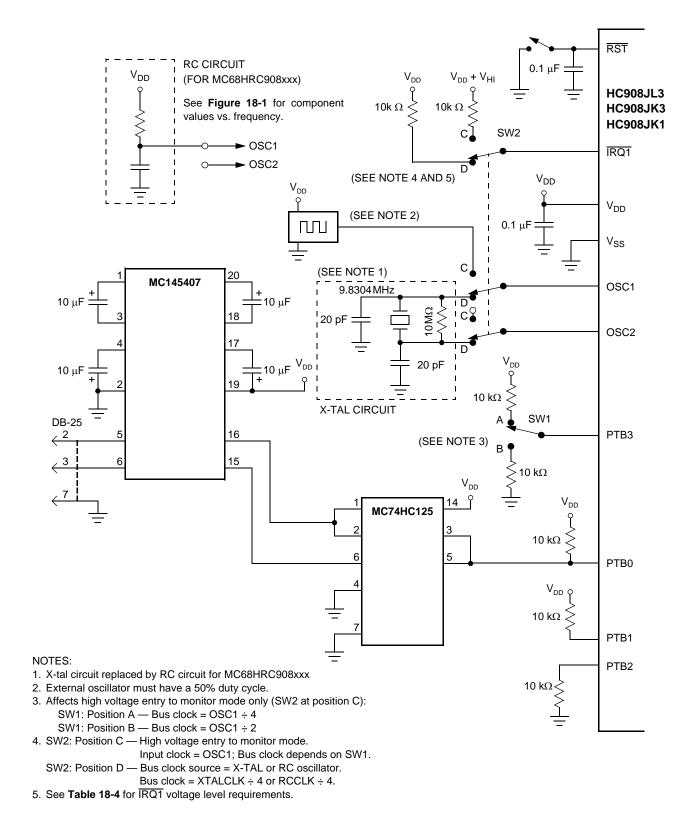

Figure 9-1. Monitor Mode Circuit

MC68H(R)C908JL3 — Rev. 1.1 Technical Data

Freescale Semiconductor Monitor ROM (MON) 103

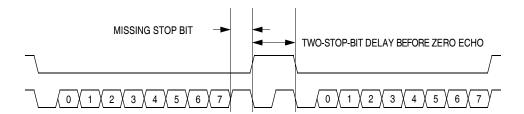

## 9.4.5 Break Signal

A start bit followed by nine low bits is a break signal. (See **Figure 9-6.)** When the monitor receives a break signal, it drives the PTB0 pin high for the duration of two bits before echoing the break signal.

Figure 9-6. Break Transaction

### 9.4.6 Commands

The monitor ROM uses the following commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

**Table 10-2. Prescaler Selection**

| PS2 | PS1 | PS0 | TIM Clock Source        |

|-----|-----|-----|-------------------------|

| 0   | 0   | 0   | Internal Bus Clock ÷ 1  |

| 0   | 0   | 1   | Internal Bus Clock ÷ 2  |

| 0   | 1   | 0   | Internal Bus Clock ÷ 4  |

| 0   | 1   | 1   | Internal Bus Clock ÷ 8  |

| 1   | 0   | 0   | Internal Bus Clock ÷ 16 |

| 1   | 0   | 1   | Internal Bus Clock ÷ 32 |

| 1   | 1   | 0   | Internal Bus Clock ÷ 64 |

| 1   | 1   | 1   | Not available           |

## 10.10.2 TIM Counter Registers (TCNTH:TCNTL)

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

NOTE:

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

## **Analog-to-Digital Converter (ADC)**

Writes to the port register or DDR will not have any affect on the port pin that is selected by the ADC. Read of a port pin which is in use by the ADC will return a logic 0 if the corresponding DDR bit is at logic 0. If the DDR bit is at logic 1, the value in the port data latch is read.

### 11.4.2 Voltage Conversion

When the input voltage to the ADC equals  $V_{DD}$ , the ADC converts the signal to \$FF (full scale). If the input voltage equals  $V_{SS}$ , the ADC converts it to \$00. Input voltages between  $V_{DD}$  and  $V_{SS}$  are a straight-line linear conversion. All other input voltages will result in \$FF if greater than  $V_{DD}$  and \$00 if less than  $V_{SS}$ .

**NOTE:** Input voltage should not exceed the analog supply voltages.

#### 11.4.3 Conversion Time

Sixteen ADC internal clocks are required to perform one conversion. The ADC starts a conversion on the first rising edge of the ADC internal clock immediately following a write to the ADSCR. If the ADC internal clock is selected to run at 1 MHz, then one conversion will take  $16\mu s$  to complete. With a 1 MHz ADC internal clock the maximum sample rate is  $62.5 \, kHz$ .

Number of Bus Cycles = Conversion Time  $\times$  Bus Frequency

#### 11.4.4 Continuous Conversion

In the continuous conversion mode, the ADC continuously converts the selected channel filling the ADC data register with new data after each conversion. Data from the previous conversion will be overwritten whether that data has been read or not. Conversions will continue until the ADCO bit is cleared. The COCO bit (ADC Status & Control register, \$003C) is set after each conversion and can be cleared by writing the ADC status and control register or reading of the ADC data register.

**Technical Data**

MC68H(R)C908JL3 — Rev. 1.1

### 11.4.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

## 11.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating a CPU interrupt after each ADC conversion. A CPU interrupt is generated if the COCO bit is at logic 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

### 11.6 Low-Power Modes

The following subsections describe the ADC in low-power modes.

#### 11.6.1 Wait Mode

The ADC continues normal operation during wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting the CH[4:0] bits in the ADC Status and Control register to logic 1's before executing the WAIT instruction.

## 11.6.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

## 11.7 I/O Signals

The ADC module has 12 channels that are shared with I/O port B and port D.

## Technical Data — MC68H(R)C908JL3

# Section 12. I/O Ports

### 12.1 Contents

| 12.2   | Introduction147                     |

|--------|-------------------------------------|

| 12.3   | Port A                              |

| 12.4.1 | Port A Data Register (PTA)          |

| 12.5.1 | Port B                              |

| 12.6   | Port D                              |

| 12.6.1 | Port D Data Register (PTD)          |

| 12.6.2 | Data Direction Register D (DDRD)156 |

| 12.6.3 | Port D Control Register (PDCR)      |

## 12.2 Introduction

Twenty three bidirectional input-output (I/O) pins form three parallel ports. All I/O pins are programmable as inputs or outputs.

#### NOTE:

Connect any unused I/O pins to an appropriate logic level, either  $V_{DD}$  or  $V_{SS}$ . Although the I/O ports do not require termination for proper operation, termination reduces excess current consumption and the possibility of electrostatic damage.

MC68H(R)C908JL3 - Rev. 1.1

Technical Data

# I/O Ports

### 14.5 Wait Mode

The keyboard modules remain active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

## 14.6 Stop Mode

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

## 14.7 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect.

# Technical Data — MC68H(R)C908JL3

# Section 18. Electrical Specifications

## 18.1 Contents

| 18.2  | Introduction191                     |

|-------|-------------------------------------|

| 18.3  | Absolute Maximum Ratings            |

| 18.4  | Functional Operating Range193       |

| 18.5  | Thermal Characteristics             |

| 18.6  | 5V DC Electrical Characteristics194 |

| 18.7  | 5V Control Timing195                |

| 18.8  | 5V Oscillator Characteristics       |

| 18.9  | 3V DC Electrical Characteristics197 |

| 18.10 | 3V Control Timing198                |

| 18.11 | 3V Oscillator Characteristics       |

| 18.12 | Typical Supply Currents             |

| 18.13 | ADC Characteristics                 |

| 18.14 | Memory Characteristics              |

## 18.2 Introduction

This section contains electrical and timing specifications.

## **Electrical Specifications**

## **18.14 Memory Characteristics**

**Table 18-11. Memory Characteristics**

| Characteristic                             | Symbol                            | Min | Max | Unit   |

|--------------------------------------------|-----------------------------------|-----|-----|--------|

| RAM data retention voltage                 | V <sub>RDR</sub>                  | 1.3 | _   | V      |

| FLASH program bus clock frequency          | _                                 | 1   | _   | MHz    |

| FLASH read bus clock frequency             | f <sub>Read</sub> <sup>(1)</sup>  | 32k | 8M  | Hz     |

| FLASH page erase time                      | t <sub>Erase</sub> <sup>(2)</sup> | 1   | _   | ms     |

| FLASH mass erase time                      | t <sub>MErase</sub> (3)           | 4   | _   | ms     |

| FLASH PGM/ERASE to HVEN set up time        | t <sub>nvs</sub>                  | 10  | _   | μS     |

| FLASH high-voltage hold time               | t <sub>nvh</sub>                  | 5   | _   | μS     |

| FLASH high-voltage hold time (mass erase)  | t <sub>nvhl</sub>                 | 100 | _   | μS     |

| FLASH program hold time                    | t <sub>pgs</sub>                  | 5   | _   | μS     |

| FLASH program time                         | t <sub>PROG</sub>                 | 30  | 40  | μS     |

| FLASH return to read time                  | t <sub>rcv</sub> <sup>(4)</sup>   | 1   | _   | μS     |

| FLASH cumulative program hv period         | t <sub>HV</sub> <sup>(5)</sup>    | _   | 4   | ms     |

| FLASH row erase endurance <sup>(6)</sup>   | _                                 | 10k | _   | cycles |

| FLASH row program endurance <sup>(7)</sup> |                                   | 10k | _   | cycles |

| FLASH data retention time <sup>(8)</sup>   | _                                 | 10  | _   | years  |

#### NOTES:

- 1.  $f_{Read}$  is defined as the frequency range for which the FLASH memory can be read. 2. If the page erase time is longer than  $t_{Erase}$  (Min), there is no erase-disturb, but it reduces the endurance of the FLASH memory.

- 3. If the mass erase time is longer than t<sub>MErase</sub> (Min), there is no erase-disturb, but it reduces the endurance of the FLASH memory.

- 4. t<sub>rcv</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to logic 0.

- 5. t<sub>HV</sub> is defined as the cumulative high voltage programming time to the same row before next erase.

- $t_{HV}$  must satisfy this condition:  $t_{nvs} + t_{nvh} + t_{pgs} + (t_{PROG} \times 32) \le t_{HV}$  max. 6. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase / program cycles.

- 7. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase / program cycles.

- 8. The FLASH is guaranteed to retain data over the entire operating temperature range for at least the minimum time specified.