Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                            |

| Data Converters            | A/D 12x8b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 20-DIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchrc908jk3cpe |

# List of Sections

# **Table of Contents**

# **Section 19. Mechanical Specifications**

| 19.1 | Contents                         |

|------|----------------------------------|

| 19.2 | Introduction                     |

| 19.3 | 20-Pin PDIP                      |

| 19.4 | 20-Pin SOIC                      |

| 19.5 | 28-Pin PDIP                      |

| 19.6 | 28-Pin SOIC                      |

|      | Section 20. Ordering Information |

| 20.1 | Contents                         |

| 20.2 | Introduction                     |

| 20.3 | MC Order Numbers                 |

# Memory

| \$0000<br>↓           | I/O REGISTERS                              |                                               |

|-----------------------|--------------------------------------------|-----------------------------------------------|

| \$003F                | 64 BYTES                                   |                                               |

| \$0040                | RESERVED                                   |                                               |

| ↓<br>\$007F           | 64 BYTES                                   |                                               |

| \$0080                | RAM                                        |                                               |

| ↓<br>\$00FF           | 128 BYTES                                  |                                               |

| \$0100                | UNIMPLEMENTED                              |                                               |

| ↓<br>\$EBFF           | 60160 BYTES                                | UNIMPLEMENTED<br>62720 BYTES                  |

| \$EC00                | FLASH MEMORY                               |                                               |

| ↓<br>\$FBFF           | MC68H(R)C908JL3/JK3<br>4096 BYTES          | FLASH MEMORY<br>MC68H(R)C908JK1<br>1536 BYTES |

| \$FÇ00                | MONITOR ROM                                |                                               |

| ↓<br>\$FDFF           | 512 BYTES                                  |                                               |

| \$FE00                | BREAK STATUS REGISTER (BSR)                |                                               |

| \$FE01                | RESET STATUS REGISTER (RSR)                |                                               |

| \$FE02                | RESERVED (UBAR)                            |                                               |

| \$FE03                | BREAK FLAG CONTROL REGISTER (BFCR)         |                                               |

| \$FE04                | INTERRUPT STATUS REGISTER 1 (INT1)         |                                               |

| \$FE05                | INTERRUPT STATUS REGISTER 2 (INT2)         |                                               |

| \$FE06                | INTERRUPT STATUS REGISTER 3 (INT3)         |                                               |

| \$FE07                | RESERVED                                   |                                               |

| \$FE08                | FLASH CONTROL REGISTER (FLCR)              |                                               |

| \$FE09                | FLASH BLOCK PROTECT REGISTER (FLBPR)       |                                               |

| \$FE0A                | RESERVED                                   |                                               |

| \$FE0B                | RESERVED                                   |                                               |

| \$FE0C                | BREAK ADDRESS HIGH REGISTER (BRKH)         |                                               |

| \$FE0D                | BREAK ADDRESS LOW REGISTER (BRKL)          |                                               |

| \$FE0E                | BREAK STATUS AND CONTROL REGISTER (BRKSCR) |                                               |

| \$FE0F                | RESERVED                                   |                                               |

| \$FE10<br>↓<br>\$FFCF | MONITOR ROM<br>448 BYTES                   |                                               |

| \$FFD0<br>↓<br>\$FFFF | USER VECTORS<br>48 BYTES                   |                                               |

Figure 2-1. Memory Map

Memory

Technical Data

28

MC68H(R)C908JL3 — Rev. 1.1

\$0100 ↓ \$F5FF

\$F600 ↓ \$FBFF

## Memory

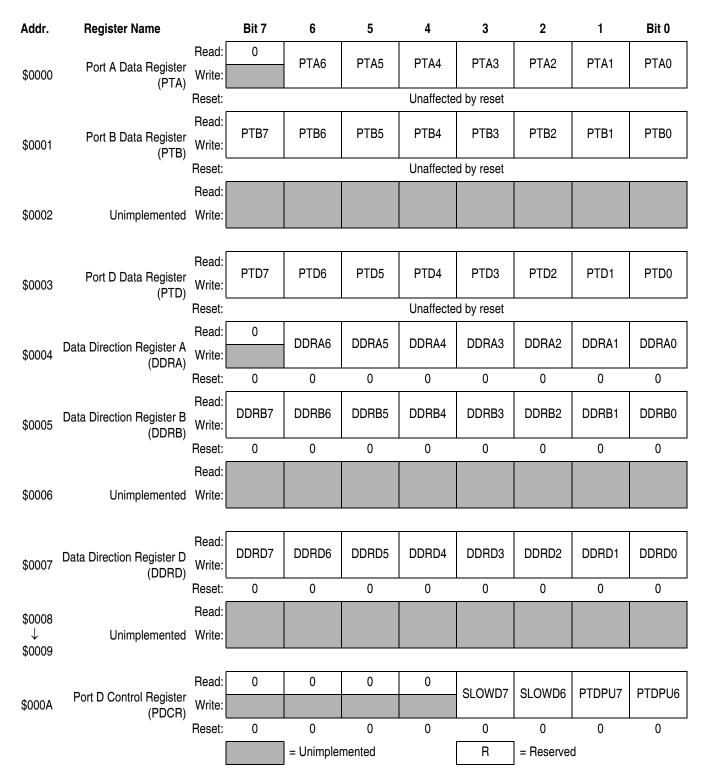

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 5)

**Technical Data**

MC68H(R)C908JL3 - Rev. 1.1

### Technical Data — MC68H(R)C908JL3

# Section 5. Configuration Register (CONFIG)

#### 5.1 Contents

| 5.2 | Introduction           | .47 |

|-----|------------------------|-----|

| 5.3 | Functional Description | .48 |

#### 5.2 Introduction

This section describes the configuration registers (CONFIG1 and CONFIG2). The configuration registers enables or disables the following options:

- Stop mode recovery time (32 × 20SCOUT cycles or 4096 × 20SCOUT cycles)

- STOP instruction

- Computer operating properly module (COP)

- COP reset period (COPRS),  $(2^{13}-2^4) \times 20$ SCOUT or  $(2^{18}-2^4) \times 20$ SCOUT

- Enable LVI circuit

- Select LVI trip voltage

#### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

1 = Interrupts disabled

0 = Interrupts enabled

#### **NOTE:**

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

#### N — Negative flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

1 = Negative result

0 = Non-negative result

#### Z — Zero flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

1 = Zero result

0 = Non-zero result

**Table 6-1. Instruction Set Summary**

| Source<br>Form                                                                                 | Operation                 | Description                                                                                                                                                                                                 |          |   | Effec<br>CC |          |          |          | Address<br>Mode                       | Opcode                                           | rand                                            | les                                  |

|------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|-------------|----------|----------|----------|---------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| 101111                                                                                         |                           |                                                                                                                                                                                                             |          | Н | ı           | N        | Z        | С        | Add                                   | obc                                              | Ope                                             | Cycles                               |

| LSR opr<br>LSRA<br>LSRX<br>LSR opr,X<br>LSR ,X<br>LSR opr,SP                                   | Logical Shift Right       | 0 - C<br>b7 b0                                                                                                                                                                                              | <b>‡</b> | 1 | _           | 0        | <b>‡</b> | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 34<br>44<br>54<br>64<br>74<br>9E64               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| MOV opr,opr<br>MOV opr,X+<br>MOV #opr,opr<br>MOV X+,opr                                        | Move                      | $(M)_{Destination} \leftarrow (M)_{Source}$ $H:X \leftarrow (H:X) + 1 (IX+D, DIX+)$                                                                                                                         | 0        | ı | _           | <b>‡</b> | <b>‡</b> | _        | DD<br>DIX+<br>IMD<br>IX+D             | 4E<br>5E<br>6E<br>7E                             | dd dd<br>dd<br>ii dd<br>dd                      | 5<br>4<br>4<br>4                     |

| MUL                                                                                            | Unsigned multiply         | $X:A \leftarrow (X) \times (A)$                                                                                                                                                                             | _        | 0 | _           | -        | -        | 0        | INH                                   | 42                                               |                                                 | 5                                    |

| NEG opr<br>NEGA<br>NEGX<br>NEG opr,X<br>NEG ,X<br>NEG opr,SP                                   | Negate (Two's Complement) | $\begin{aligned} M &\leftarrow -(M) = \$00 - (M) \\ A &\leftarrow -(A) = \$00 - (A) \\ X &\leftarrow -(X) = \$00 - (X) \\ M &\leftarrow -(M) = \$00 - (M) \\ M &\leftarrow -(M) = \$00 - (M) \end{aligned}$ | <b>‡</b> | - | _           | <b>‡</b> | <b>‡</b> | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 30<br>40<br>50<br>60<br>70<br>9E60               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| NOP                                                                                            | No Operation              | None                                                                                                                                                                                                        | _        | _ | _           | _        | -        | -        | INH                                   | 9D                                               |                                                 | 1                                    |

| NSA                                                                                            | Nibble Swap A             | A ← (A[3:0]:A[7:4])                                                                                                                                                                                         | -        | - | _           | -        | -        | -        | INH                                   | 62                                               |                                                 | 3                                    |

| ORA #opr<br>ORA opr<br>ORA opr<br>ORA opr,X<br>ORA opr,X<br>ORA ,X<br>ORA opr,SP<br>ORA opr,SP | Inclusive OR A and M      | A ← (A)   (M)                                                                                                                                                                                               | 0        |   | _           | \$       | <b>‡</b> | _        | IMM DIR EXT IX2 IX1 IX SP1 SP2        | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EEA<br>9EDA | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| PSHA                                                                                           | Push A onto Stack         | Push (A); SP ← (SP) – 1                                                                                                                                                                                     | -        | _ | _           | _        | -        | _        | INH                                   | 87                                               |                                                 | 2                                    |

| PSHH                                                                                           | Push H onto Stack         | Push (H); SP ← (SP) – 1                                                                                                                                                                                     | _        | - | -           | -        | -        | -        | INH                                   | 8B                                               |                                                 | 2                                    |

| PSHX                                                                                           | Push X onto Stack         | Push (X); SP $\leftarrow$ (SP) – 1                                                                                                                                                                          | _        | _ | _           | _        | -        | -        | INH                                   | 89                                               |                                                 | 2                                    |

| PULA                                                                                           | Pull A from Stack         | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                          | -        | - | _           | _        | -        | -        | INH                                   | 86                                               |                                                 | 2                                    |

| PULH                                                                                           | Pull H from Stack         | SP ← (SP + 1); Pull (H)                                                                                                                                                                                     | -        | _ | -           | -        | -        | -        | INH                                   | 8A                                               |                                                 | 2                                    |

| PULX                                                                                           | Pull X from Stack         | $SP \leftarrow (SP + 1); Pull(X)$                                                                                                                                                                           | -        | _ | -           | -        | -        | -        | INH                                   | 88                                               |                                                 | 2                                    |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                   | Rotate Left through Carry |                                                                                                                                                                                                             | <b>‡</b> | _ | _           | <b>‡</b> | <b>‡</b> | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

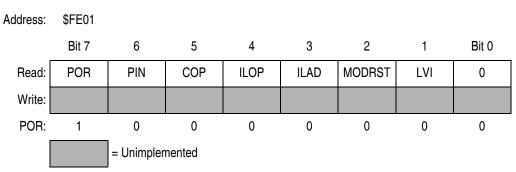

Figure 7-21. Reset Status Register (RSR)

POR — Power-On Reset Bit

1 = Last reset caused by POR circuit

0 = Read of SRSR

PIN — External Reset Bit

1 = Last reset caused by external reset pin  $(\overline{RST})$

0 = POR or read of SRSR

COP — Computer Operating Properly Reset Bit

1 = Last reset caused by COP counter

0 = POR or read of SRSR

ILOP — Illegal Opcode Reset Bit

1 = Last reset caused by an illegal opcode

0 = POR or read of SRSR

ILAD — Illegal Address Reset Bit (opcode fetches only)

1 = Last reset caused by an opcode fetch from an illegal address

0 = POR or read of SRSR

MODRST — Monitor Mode Entry Module Reset bit

1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$00 after POR while IRQB = V<sub>DD</sub>

0 = POR or read of SRSR

LVI — Low Voltage Inhibit Reset bit

1 = Last reset caused by LVI circuit

0 = POR or read of SRSR

93

## Technical Data — MC68H(R)C908JL3

# Section 9. Monitor ROM (MON)

#### 9.1 Contents

| 9.2   | Introduction           |

|-------|------------------------|

| 9.3   | Features               |

| 9.4   | Functional Description |

| 9.4.1 | Entering Monitor Mode  |

| 9.4.2 | Baud Rate107           |

| 9.4.3 | Data Format            |

| 9.4.4 | Echoing108             |

| 9.4.5 | Break Signal           |

| 9.4.6 | Commands109            |

| 9.5   | Security               |

#### 9.2 Introduction

This section describes the monitor ROM (MON) and the monitor mode entry methods. The monitor ROM allows complete testing of the MCU through a single-wire interface with a host computer. This mode is also used for programming and erasing of FLASH memory in the MCU. Monitor mode entry can be achieved without use of the higher test voltage,  $V_{DD} + V_{HI}$ , as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

MC68H(R)C908JL3 — Rev. 1.1

### **Monitor ROM (MON)**

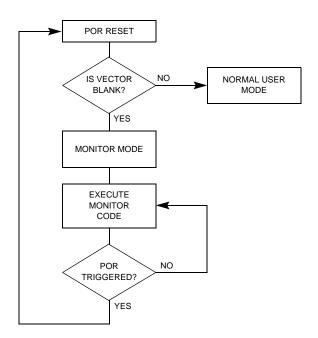

Figure 9-2. Low-Voltage Monitor Mode Entry Flowchart

Enter monitor mode with the pin configuration shown above by pulling RST low and then high. The rising edge of RST latches monitor mode. Once monitor mode is latched, the values on the specified pins can change.

Once out of reset, the MCU waits for the host to send eight security bytes. (See **9.5 Security**.) After the security bytes, the MCU sends a break signal (10 consecutive logic zeros) to the host, indicating that it is ready to receive a command. The break signal also provides a timing reference to allow the host to determine the necessary baud rate.

In monitor mode, the MCU uses different vectors for reset, SWI, and break interrupt. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

### 9.4.5 Break Signal

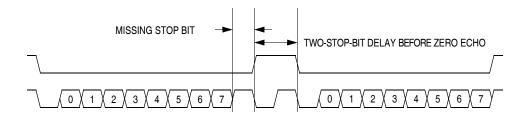

A start bit followed by nine low bits is a break signal. (See **Figure 9-6.)** When the monitor receives a break signal, it drives the PTB0 pin high for the duration of two bits before echoing the break signal.

Figure 9-6. Break Transaction

#### 9.4.6 Commands

The monitor ROM uses the following commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

### **Monitor ROM (MON)**

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6—\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a FLASH location returns an invalid value and trying to execute code from FLASH causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

**NOTE:**

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$40 is set. If it is, then the correct security code has been entered and FLASH can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the FLASH module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

# **Analog-to-Digital Converter (ADC)**

#### 11.3 Features

Features of the ADC module include:

- 12 channels with multiplexed input

- Linear successive approximation with monotonicity

- 8-bit resolution

- Single or continuous conversion

- Conversion complete flag or conversion complete interrupt

- Selectable ADC clock

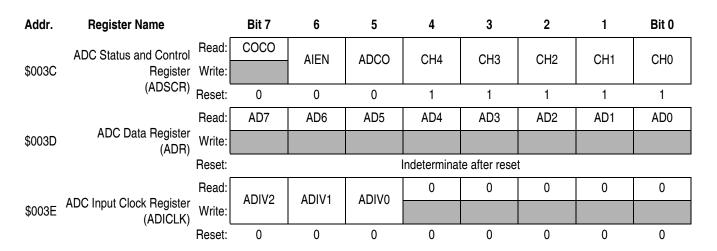

Figure 11-1. ADC I/O Register Summary

# 11.4 Functional Description

Twelve ADC channels are available for sampling external sources at pins PTB0–PTB7 and PTD0–PTD3. An analog multiplexer allows the single ADC converter to select one of the 12 ADC channels as ADC voltage input (ADCVIN). ADCVIN is converted by the successive approximation register-based counters. The ADC resolution is 8 bits. When the conversion is completed, ADC puts the result in the ADC data register and sets a flag or generates an interrupt. Figure 11-2 shows a block diagram of the ADC.

#### 11.4.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

## 11.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating a CPU interrupt after each ADC conversion. A CPU interrupt is generated if the COCO bit is at logic 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

#### 11.6 Low-Power Modes

The following subsections describe the ADC in low-power modes.

#### 11.6.1 Wait Mode

The ADC continues normal operation during wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting the CH[4:0] bits in the ADC Status and Control register to logic 1's before executing the WAIT instruction.

### 11.6.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

# 11.7 I/O Signals

The ADC module has 12 channels that are shared with I/O port B and port D.

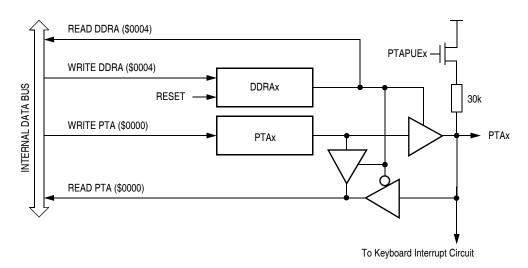

Figure 12-4. Port A I/O Circuit

When DDRAx is a logic 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a logic 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

### 12.4.2 Port A Input Pull-up Enable Register (PTAPUE)

The Port A Input Pull-up Enable Register (PTAPUE) contains a software configurable pull-up device for each if the seven port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx be configured as input. Each pull-up device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

## 13.5 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ1 latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear the latches during the break state. (See Section 7. System Integration Module (SIM).)

To allow software to clear the IRQ1 latch during a break interrupt, write a logic one to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latches during the break state, write a logic zero to the BCFE bit. With BCFE at logic zero (its default state), writing to the ACK1 bit in the IRQ status and control register during the break state has no effect on the IRQ latch.

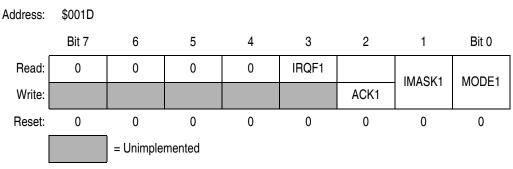

# 13.6 IRQ Status and Control Register (ISCR)

The IRQ Status and Control Register (ISCR) controls and monitors operation of the IRQ module. The ISCR has the following functions:

- Shows the state of the IRQ1 flag

- Clears the IRQ1 latch

- Masks IRQ1 and interrupt request

- Controls triggering sensitivity of the IRQ1 interrupt pin

Figure 13-3. IRQ Status and Control Register (INTSCR)

MC68H(R)C908JL3 — Rev. 1.1

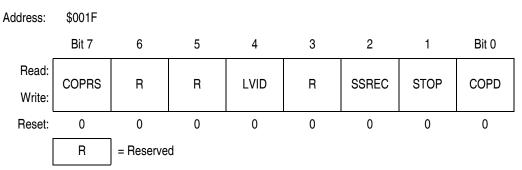

Figure 16-3. Configuration Register 1 (CONFIG1)

LVID — bLow Voltage Inhibit Disable Bit

1 = Low voltage inhibit disabled

0 = Low voltage inhibit enabled

#### LVIT1, LVIT0 — LVI Trip Voltage Selection

These two bits determine at which level of  $V_{DD}$  the LVI module will come into action. LVIT1 and LVIT0 are cleared by a Power-On Reset only.

| LVIT1 | LVIT0 | Trip Voltage <sup>(1)</sup> | Comments                          |

|-------|-------|-----------------------------|-----------------------------------|

| 0     | 0     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 0     | 1     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 1     | 0     | V <sub>LVR5</sub> (4.0V)    | For V <sub>DD</sub> =5V operation |

| 1     | 1     | Reserved                    |                                   |

<sup>1.</sup> See Section 18. Electrical Specifications for full parameters.

#### 16.6 Low-Power Modes

The STOP and WAIT instructions put the MCU in low-power-consumption standby modes.

#### 16.6.1 Wait Mode

The LVI module, when enabled, will continue to operate in WAIT Mode.

#### 16.6.2 Stop Mode

The LVI module, when enabled, will continue to operate in STOP Mode.

MC68H(R)C908JL3 - Rev. 1.1

# **Electrical Specifications**

## 18.6 5V DC Electrical Characteristics

Table 18-4. DC Electrical Characteristics (5V)

| Characteristic <sup>(1)</sup>                                                                                                                                                      | Symbol                               | Min                  | Тур <sup>(2)</sup> | Max                   | Unit                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------|--------------------|-----------------------|----------------------|

| Output high voltage (I <sub>LOAD</sub> = -2.0mA)<br>PTA0-PTA6, PTB0-PTB7, PTD0-PTD7                                                                                                | V <sub>OH</sub>                      | V <sub>DD</sub> -0.8 | _                  | _                     | V                    |

| Output low voltage (I <sub>LOAD</sub> = 1.6mA)<br>PTA6, PTB0–PTB7, PTD0, PTD1, PTD4, PTD5                                                                                          | V <sub>OL</sub>                      | _                    | _                  | 0.4                   | V                    |

| Output low voltage (I <sub>LOAD</sub> = 25mA)<br>PTD6, PTD7                                                                                                                        | V <sub>OL</sub>                      | _                    | _                  | 0.5                   | V                    |

| LED drives (V <sub>OL</sub> = 3V)<br>PTA0–PTA5, PTD2, PTD3, PTD6, PTD7                                                                                                             | I <sub>OL</sub>                      | 10                   | 19                 | 25                    | mA                   |

| Input high voltage PTA0-PTA6, PTB0-PTB7, PTD0-PTD7, RST, IRQ1, OSC1                                                                                                                | V <sub>IH</sub>                      | $0.7 \times V_{DD}$  | _                  | V <sub>DD</sub>       | V                    |

| Input low voltage PTA0-PTA6, PTB0-PTB7, PTD0-PTD7, RST, IRQ1, OSC1                                                                                                                 | V <sub>IL</sub>                      | V <sub>SS</sub>      | _                  | $0.3 \times V_{DD}$   | V                    |

| $V_{DD}$ supply current<br>Run, $f_{OP} = 4 MHz^{(3)}$<br>Wait (MC68HRC908xxx) <sup>(4)</sup><br>Wait (MC68HC908xxx) <sup>(4)</sup><br>Stop <sup>(5)</sup> $-40^{\circ}$ C to 85°C | I <sub>DD</sub>                      | _<br>_<br>_<br>_     | 7<br>1<br>5<br>1   | 10<br>1.5<br>5.5<br>5 | mA<br>mA<br>mA<br>μA |

| Digital I/O ports Hi-Z leakage current                                                                                                                                             | I <sub>IL</sub>                      | _                    | _                  | ± 10                  | μА                   |

| Input current                                                                                                                                                                      | I <sub>IN</sub>                      | _                    | _                  | ± 1                   | μΑ                   |

| Capacitance Ports (as input or output)                                                                                                                                             | C <sub>OUT</sub><br>C <sub>IN</sub>  | _                    | _                  | 12<br>8               | pF                   |

| POR rearm voltage <sup>(6)</sup>                                                                                                                                                   | V <sub>POR</sub>                     | 0                    | _                  | 100                   | mV                   |

| POR rise time ramp rate <sup>(7)</sup>                                                                                                                                             | R <sub>POR</sub>                     | 0.035                | _                  | _                     | V/ms                 |

| Monitor mode entry voltage                                                                                                                                                         | $V_{DD}+V_{HI}$                      | $1.5 \times V_{DD}$  | _                  | 8.5                   | V                    |

| Pullup resistors <sup>(8)</sup> PTD6, PTD7 RST, IRQ1, PTA0–PTA6                                                                                                                    | R <sub>PU1</sub><br>R <sub>PU2</sub> | 1.8<br>16            | 3.3<br>26          | 4.8<br>36             | kΩ<br>kΩ             |

| LVI reset voltage                                                                                                                                                                  | V <sub>LVR5</sub>                    | 3.6                  | 4.0                | 4.4                   | V                    |

#### Table 18-4. DC Electrical Characteristics (5V)

| Characteristic <sup>(1)</sup> | Symbol | Min | Typ <sup>(2)</sup> | Max | Unit |  |

|-------------------------------|--------|-----|--------------------|-----|------|--|

|-------------------------------|--------|-----|--------------------|-----|------|--|

#### NOTES:

- 1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

- 2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

- 3. Run (operating)  $I_{DD}$  measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L$  = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

- 4. Wait  $I_{DD}$  measured using external square wave clock source ( $f_{OP} = 4$ MHz); all inputs 0.2 V from rail; no dc loads; less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2; all ports configured as inputs; OSC2 capacitance linearly affects wait  $I_{DD}$ .

- 5. STOP I<sub>DD</sub> measured with OSC1 grounded, no port pins sourcing current. LVI is disabled.

- 6. Maximum is highest voltage that POR is guaranteed.

- If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, RST must be driven low externally until minimum V<sub>DD</sub> is reached.

- 8.  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 5.0V$

## 18.7 5V Control Timing

### Table 18-5. Control Timing (5V)

| Characteristic <sup>(1)</sup>               | Symbol           | Min | Max | Unit |

|---------------------------------------------|------------------|-----|-----|------|

| Internal operating frequency <sup>(2)</sup> | f <sub>OP</sub>  | _   | 8   | MHz  |

| RST input pulse width low <sup>(3)</sup>    | t <sub>IRL</sub> | 750 | _   | ns   |

#### NOTES:

- 1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ ; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{SS}$ , unless otherwise noted

- Some modules may require a minimum frequency greater than dc for proper operation; see appropriate table for this information.

- 3. Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

# **Mechanical Specifications**