Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LED, LVD, POR, PWM                                                    |

| Number of I/O              | 14                                                                    |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                           |

| Data Converters            | A/D 12x8b                                                             |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 20-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcr908jk1cdwe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

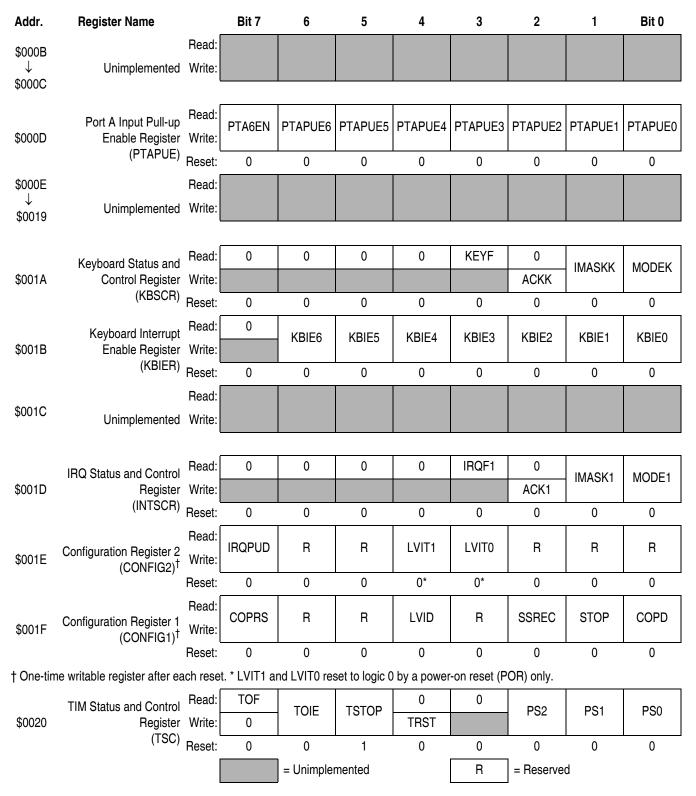

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 5)

MC68H(R)C908JL3 - Rev. 1.1

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 5)

MC68H(R)C908JL3 - Rev. 1.1

## Technical Data — MC68H(R)C908JL3

# Section 3. Random-Access Memory (RAM)

### 3.1 Contents

| 3.2 | Introduction3          | 3 / |

|-----|------------------------|-----|

| 3.3 | Functional Description | 37  |

### 3.2 Introduction

This section describes the 128 bytes of RAM.

# 3.3 Functional Description

Addresses \$0080 through \$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

**NOTE:** For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 128 bytes of RAM. Because the location of the stack RAM is programmable, all page zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved from its reset location at \$00FF, direct addressing mode instructions can access efficiently all page zero RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

**NOTE:** For M6805 compatibility, the H register is not stacked.

MC68H(R)C908JL3 — Rev. 1.1

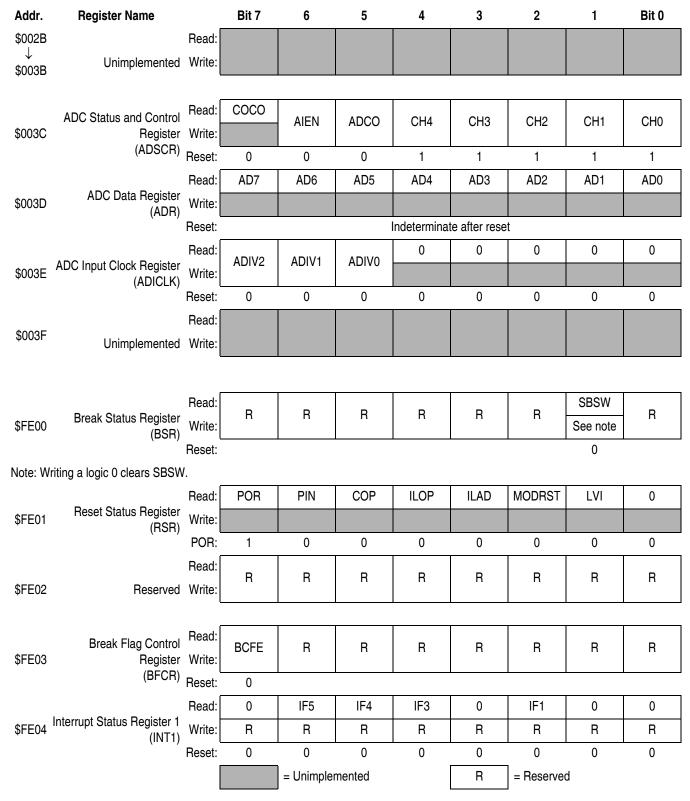

Figure 4-2. FLASH Programming Flowchart

# FLASH Memory (FLASH)

# **Central Processor Unit (CPU)**

### 6.4.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 6-3. Index Register (H:X)

### 6.4.3 Stack Pointer

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset, the stack pointer is preset to \$00FF. The reset stack pointer (RSP) instruction sets the least significant byte to \$FF and does not affect the most significant byte. The stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

In the stack pointer 8-bit offset and 16-bit offset addressing modes, the stack pointer can function as an index register to access data on the stack. The CPU uses the contents of the stack pointer to determine the conditional address of the operand.

MC68H(R)C908JL3 — Rev. 1.1

Table 6-2. Opcode Map

|            | Bit Manipulation   Branch   Read-Modify-Write   Control   Register/Memory |                     |                    |                    |                     |                     |                     |                    |                    |                    |                   |                   |                   |                   |                   |                   |                   |                   |                  |

|------------|---------------------------------------------------------------------------|---------------------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR                                                                       | DIR                 | REL                | DIR                | INH                 | INH                 | IX1                 | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                                                                         | 1                   | 2                  | 3                  | 4                   | 5                   | 6                   | 9E6                | 7                  | 8                  | 9                 | Α                 | В                 | С                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | 5<br>BRSET0<br>3 DIR                                                      | BSET0<br>2 DIR      | 3<br>BRA<br>2 REL  | 4<br>NEG<br>2 DIR  | 1<br>NEGA<br>1 INH  | 1<br>NEGX<br>1 INH  | 4<br>NEG<br>2 IX1   |                    | 3<br>NEG<br>1 IX   | 7<br>RTI<br>1 INH  | 3<br>BGE<br>2 REL | SUB<br>2 IMM      | 3<br>SUB<br>2 DIR | SUB<br>3 EXT      | SUB<br>3 IX2      | 5<br>SUB<br>4 SP2 | 3<br>SUB<br>2 IX1 | 4<br>SUB<br>3 SP1 | SUB<br>1 IX      |

| 1          | 5<br>BRCLR0<br>3 DIR                                                      | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL  | 5<br>CBEQ<br>3 DIR | 4<br>CBEQA<br>3 IMM | CBEQX<br>3 IMM      | 5<br>CBEQ<br>3 IX1+ | 6<br>CBEQ<br>4 SP1 | CBEQ<br>2 IX+      | 4<br>RTS<br>1 INH  | 3<br>BLT<br>2 REL | 2<br>CMP<br>2 IMM | 3<br>CMP<br>2 DIR | 4<br>CMP<br>3 EXT | 4<br>CMP<br>3 IX2 | 5<br>CMP<br>4 SP2 | 3<br>CMP<br>2 IX1 | 4<br>CMP<br>3 SP1 | CMP<br>1 IX      |

| 2          | 5<br>BRSET1<br>3 DIR                                                      | 4<br>BSET1<br>2 DIR |                    |                    | 5<br>MUL<br>1 INH   | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH   |                    | 2<br>DAA<br>1 INH  |                    | 3<br>BGT<br>2 REL | SBC<br>2 IMM      | 3<br>SBC<br>2 DIR | SBC<br>3 EXT      | SBC<br>3 IX2      | 5<br>SBC<br>4 SP2 | 3<br>SBC<br>2 IX1 | 4<br>SBC<br>3 SP1 | SBC<br>1 IX      |

| 3          | 5<br>BRCLR1<br>3 DIR                                                      | 4<br>BCLR1<br>2 DIR |                    | COM<br>2 DIR       |                     | COMX<br>1 INH       | 4<br>COM<br>2 IX1   | 5<br>COM<br>3 SP1  |                    | 9<br>SWI<br>1 INH  |                   |                   | CPX<br>2 DIR      | CPX<br>3 EXT      |                   | 5<br>CPX<br>4 SP2 | 3<br>CPX<br>2 IX1 | 4<br>CPX<br>3 SP1 | CPX<br>1 IX      |

| 4          | 5<br>BRSET2<br>3 DIR                                                      | BSET2<br>2 DIR      | 3<br>BCC<br>2 REL  | 4<br>LSR<br>2 DIR  |                     | 1<br>LSRX<br>1 INH  | 4<br>LSR<br>2 IX1   | 5<br>LSR<br>3 SP1  |                    | 2<br>TAP<br>1 INH  | 2<br>TXS<br>1 INH |                   | 3<br>AND<br>2 DIR | 4<br>AND<br>3 EXT |                   | 5<br>AND<br>4 SP2 | 3<br>AND<br>2 IX1 | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          |                                                                           | 4<br>BCLR2<br>2 DIR |                    | 4<br>STHX<br>2 DIR | 3<br>LDHX<br>3 IMM  | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM  |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH |                   |                   | 4<br>BIT<br>3 EXT |                   |                   | 3<br>BIT<br>2 IX1 | 4<br>BIT<br>3 SP1 | 2<br>BIT<br>1 IX |

| 6          |                                                                           | BSET3<br>2 DIR      |                    | 4<br>ROR<br>2 DIR  | 1<br>RORA<br>1 INH  |                     | 4<br>ROR<br>2 IX1   | 5<br>ROR<br>3 SP1  |                    | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM |                   | 4<br>LDA<br>3 EXT |                   | 5<br>LDA<br>4 SP2 | 3<br>LDA<br>2 IX1 | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          |                                                                           | 4<br>BCLR3<br>2 DIR | 3<br>BEQ<br>2 REL  | 4<br>ASR<br>2 DIR  | 1<br>ASRA<br>1 INH  | 1<br>ASRX<br>1 INH  | 4<br>ASR<br>2 IX1   | 5<br>ASR<br>3 SP1  |                    | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH |                   |                   | 4<br>STA<br>3 EXT | 4<br>STA<br>3 IX2 |                   | 3<br>STA<br>2 IX1 | 4<br>STA<br>3 SP1 | 2<br>STA<br>1 IX |

| 8          | -                                                                         | 4<br>BSET4<br>2 DIR | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH  | 1<br>LSLX<br>1 INH  | 4<br>LSL<br>2 IX1   | 5<br>LSL<br>3 SP1  | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | EOR<br>2 IMM      |                   | 4<br>EOR<br>3 EXT | 4<br>EOR<br>3 IX2 | 5<br>EOR<br>4 SP2 | 3<br>EOR<br>2 IX1 | 4<br>EOR<br>3 SP1 | 2<br>EOR<br>1 IX |

| 9          |                                                                           | BCLR4<br>2 DIR      | 3<br>BHCS<br>2 REL | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH  | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1   |                    | 3<br>ROL<br>1 IX   | 2<br>PSHX<br>1 INH | SEC<br>1 INH      | ADC<br>2 IMM      | 3<br>ADC<br>2 DIR | 4<br>ADC<br>3 EXT | 4<br>ADC<br>3 IX2 | 5<br>ADC<br>4 SP2 | 3<br>ADC<br>2 IX1 | 4<br>ADC<br>3 SP1 | 2<br>ADC<br>1 IX |

| A          | 5<br>BRSET5<br>3 DIR                                                      | 4<br>BSET5<br>2 DIR | 3<br>BPL<br>2 REL  | 4<br>DEC<br>2 DIR  | 1<br>DECA<br>1 INH  |                     | 4<br>DEC<br>2 IX1   | 5<br>DEC<br>3 SP1  | 3<br>DEC<br>1 IX   | 2<br>PULH<br>1 INH |                   | 2<br>ORA<br>2 IMM | 3<br>ORA<br>2 DIR | 4<br>ORA<br>3 EXT | 4<br>ORA<br>3 IX2 | 5<br>ORA<br>4 SP2 | 3<br>ORA<br>2 IX1 | 4<br>ORA<br>3 SP1 |                  |

| В          | 5<br>BRCLR5<br>3 DIR                                                      | 4<br>BCLR5<br>2 DIR | 3<br>BMI<br>2 REL  | 5<br>DBNZ<br>3 DIR | 3<br>DBNZA<br>2 INH | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1  | 6<br>DBNZ<br>4 SP1 | 4<br>DBNZ<br>2 IX  | 2<br>PSHH<br>1 INH | 2<br>SEI<br>1 INH | 2<br>ADD<br>2 IMM | 3<br>ADD<br>2 DIR | 4<br>ADD<br>3 EXT | 4<br>ADD<br>3 IX2 | 5<br>ADD<br>4 SP2 | 3<br>ADD<br>2 IX1 | 4<br>ADD<br>3 SP1 | 2<br>ADD<br>1 IX |

| С          | 5<br>BRSET6<br>3 DIR                                                      | BSET6<br>2 DIR      |                    | 4<br>INC<br>2 DIR  | 1<br>INCA<br>1 INH  | 1<br>INCX<br>1 INH  | 4<br>INC<br>2 IX1   | 5<br>INC<br>3 SP1  |                    | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR | 3<br>JMP<br>3 EXT |                   |                   | 3<br>JMP<br>2 IX1 |                   | JMP<br>1 IX      |

| D          |                                                                           | 4<br>BCLR6<br>2 DIR |                    | 3<br>TST<br>2 DIR  | 1<br>TSTA<br>1 INH  | 1<br>TSTX<br>1 INH  | 3<br>TST<br>2 IX1   | 4<br>TST<br>3 SP1  |                    |                    | 1<br>NOP<br>1 INH | 4<br>BSR<br>2 REL |                   | 5<br>JSR<br>3 EXT |                   |                   | 5<br>JSR<br>2 IX1 |                   | JSR<br>1 IX      |

| E          |                                                                           | BSET7<br>2 DIR      |                    |                    |                     | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD   |                    | 4<br>MOV<br>2 IX+D | 1<br>STOP<br>1 INH | *                 | LDX<br>2 IMM      |                   | 4<br>LDX<br>3 EXT |                   | 5<br>LDX<br>4 SP2 | 3<br>LDX<br>2 IX1 |                   | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7<br>3 DIR                                                      | 4<br>BCLR7<br>2 DIR | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH  | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1   | 4<br>CLR<br>3 SP1  | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | 3<br>STX<br>2 DIR | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | 5<br>STX<br>4 SP2 | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | STX<br>1 IX      |

INH Inherent IMM Immediate DIR Direct EXT Extended

**REL** Relative Indexed, No Offset IX1 Indexed, 8-Bit Offset IX2 Indexed, 16-Bit Offset IMD Immediate-Direct DD Direct-Direct IMD Immediate-Dire IX+D Indexed-Direct DIX+ Direct-Indexed

\*Pre-byte for stack pointer indexed instructions

Low Byte of Opcode in Hexadecimal

MSB High Byte of Opcode in Hexadecimal LSB 5 BRSET0 Opcode Mnemonic Opcode Mnemonic Number of Bytes / Addressing Mode

SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with Post Increment

IX1+ Indexed, 1-Byte Offset with Post Increment

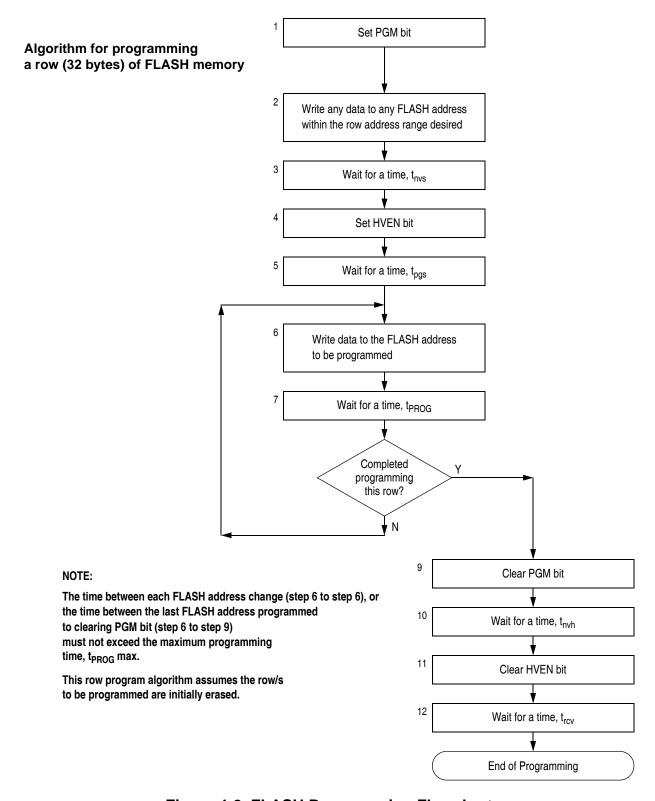

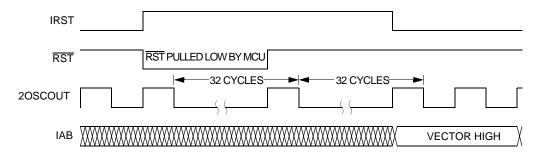

Figure 7-4. External Reset Timing

#### 7.4.2 Active Resets from Internal Sources

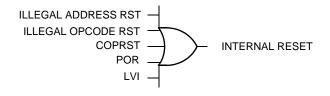

All internal reset sources actively pull the RST pin low for 32 2OSCOUT cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (Figure 7-5). An internal reset can be caused by an illegal address, illegal opcode, COP time-out, or POR. (See Figure 7-6. Sources of Internal Reset.) Note that for POR resets, the SIM cycles through 4096 2OSCOUT cycles during which the SIM forces the RST pin low. The internal reset signal then follows the sequence from the falling edge of RST shown in Figure 7-5.

Figure 7-5. Internal Reset Timing

The COP reset is asynchronous to the bus clock.

Figure 7-6. Sources of Internal Reset

MC68H(R)C908JL3 — Rev. 1.1

# **System Integration Module (SIM)**

### 7.7.2 Stop Mode

In stop mode, the SIM counter is reset and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset or break also causes an exit from stop mode.

The SIM disables the oscillator signals (OSCOUT and 2OSCOUT) in stop mode, stopping the CPU and peripherals. Stop recovery time is selectable using the SSREC bit in the configuration register (CONFIG). If SSREC is set, stop recovery is reduced from the normal delay of 4096 2OSCOUT cycles down to 32. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode.

**NOTE:** External crystal applications should use the full stop recovery time by clearing the SSREC bit.

A break interrupt during stop mode sets the SIM break stop/wait bit (SBSW) in the break status register (BSR).

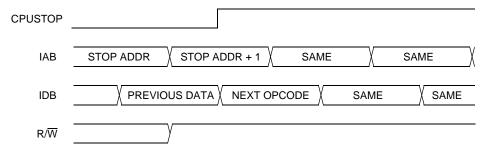

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. **Figure 7-18** shows stop mode entry timing.

**NOTE:** To minimize stop current, all pins configured as inputs should be driven to a logic 1 or logic 0.

NOTE: Previous data can be operand data or the STOP opcode, depending on the last instruction.

Figure 7-18. Stop Mode Entry Timing

# System Integration Module (SIM)

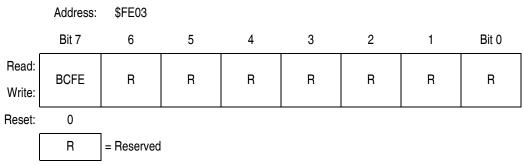

### 7.8.3 Break Flag Control Register (BFCR)

The break control register contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 7-22. Break Flag Control Register (BFCR)

### BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

# Oscillator (OSC)

# 8.7 Oscillator During Break Mode

The oscillator continues to drive OSCOUT and 2OSCOUT when the device enters the break state.

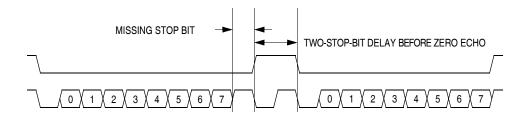

## 9.4.5 Break Signal

A start bit followed by nine low bits is a break signal. (See **Figure 9-6.)** When the monitor receives a break signal, it drives the PTB0 pin high for the duration of two bits before echoing the break signal.

Figure 9-6. Break Transaction

### 9.4.6 Commands

The monitor ROM uses the following commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

# 10.5 Functional Description

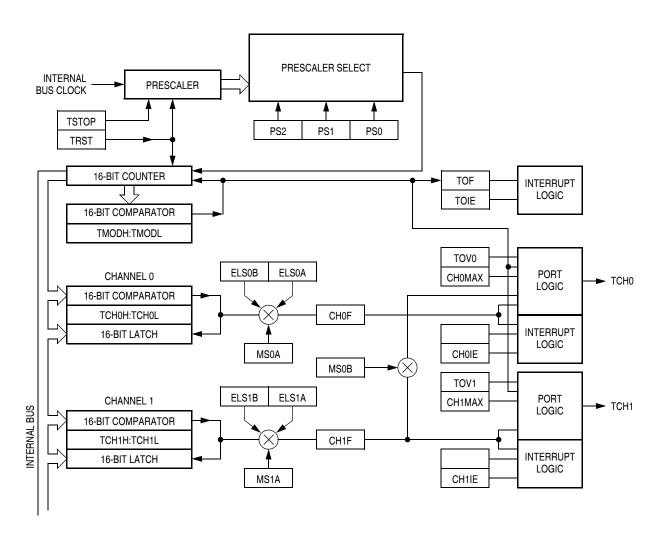

Figure 10-1 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels are programmable independently as input capture or output compare channels.

Figure 10-1. TIM Block Diagram

## Timer Interface Module (TIM)

overflow occurs before the clearing sequence is complete, then writing logic zero to TOF has no effect. Therefore, a TOF interrupt request cannot be lost due to inadvertent clearing of TOF. Reset clears the TOF bit. Writing a logic one to TOF has no effect.

- 1 = TIM counter has reached modulo value

- 0 = TIM counter has not reached modulo value

### TOIE — TIM Overflow Interrupt Enable Bit

This read/write bit enables TIM overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

- 1 = TIM overflow interrupts enabled

- 0 = TIM overflow interrupts disabled

### TSTOP — TIM Stop Bit

This read/write bit stops the TIM counter. Counting resumes when TSTOP is cleared. Reset sets the TSTOP bit, stopping the TIM counter until software clears the TSTOP bit.

- 1 = TIM counter stopped

- 0 = TIM counter active

# **NOTE:** Do not set the TSTOP bit before entering wait mode if the TIM is required to exit wait mode.

### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as logic zero. Reset clears the TRST bit.

- 1 = Prescaler and TIM counter cleared

- 0 = No effect

# **NOTE:** Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

### PS[2:0] — Prescaler Select Bits

These read/write bits select one of the seven prescaler outputs as the input to the TIM counter as **Table 10-2** shows. Reset clears the PS[2:0] bits.

**Table 10-2. Prescaler Selection**

| PS2 | PS1 | PS0 | TIM Clock Source        |

|-----|-----|-----|-------------------------|

| 0   | 0   | 0   | Internal Bus Clock ÷ 1  |

| 0   | 0   | 1   | Internal Bus Clock ÷ 2  |

| 0   | 1   | 0   | Internal Bus Clock ÷ 4  |

| 0   | 1   | 1   | Internal Bus Clock ÷ 8  |

| 1   | 0   | 0   | Internal Bus Clock ÷ 16 |

| 1   | 0   | 1   | Internal Bus Clock ÷ 32 |

| 1   | 1   | 0   | Internal Bus Clock ÷ 64 |

| 1   | 1   | 1   | Not available           |

# 10.10.2 TIM Counter Registers (TCNTH:TCNTL)

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

NOTE:

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

## Timer Interface Module (TIM)

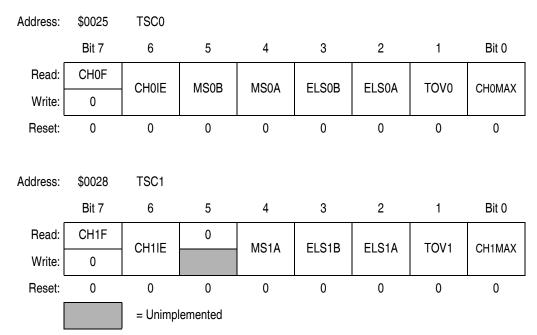

Figure 10-7. TIM Channel Status and Control Registers (TSC0:TSC1)

### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

When TIM CPU interrupt requests are enabled (CHxIE=1), clear CHxF by reading the TIM channel x status and control register with CHxF set and then writing a logic zero to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing logic zero to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a logic one to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

### CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

## External Interrupt (IRQ)

# 13.4 Functional Description

A logic zero applied to the external interrupt pin can latch a CPU interrupt request. Figure 13-1 shows the structure of the IRQ module.

Interrupt signals on the IRQ1 pin are latched into the IRQ1 latch. An interrupt latch remains set until one of the following actions occurs:

- Vector fetch A vector fetch automatically generates an interrupt acknowledge signal that clears the IRQ latch.

- Software clear Software can clear the interrupt latch by writing to the acknowledge bit in the interrupt status and control register (ISCR). Writing a logic one to the ACK1 bit clears the IRQ1 latch.

- Reset A reset automatically clears the interrupt latch.

The external interrupt pin is falling-edge-triggered and is software-configurable to be either falling-edge or falling-edge and low-level-triggered. The MODE1 bit in the ISCR controls the triggering sensitivity of the IRQ1 pin.

When the interrupt pin is edge-triggered only, the CPU interrupt request remains set until a vector fetch, software clear, or reset occurs.

When the interrupt pin is both falling-edge and low-level-triggered, the CPU interrupt request remains set until both of the following occur:

- Vector fetch or software clear

- Return of the interrupt pin to logic one

The vector fetch or software clear may occur before or after the interrupt pin returns to logic one. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE1 control bit, thereby clearing the interrupt even if the pin stays low.

When set, the IMASK1 bit in the ISCR mask all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK1 bit is clear.

# Technical Data — MC68H(R)C908JL3

# Section 14. Keyboard Interrupt Module (KBI)

### 14.1 Contents

| 14.2   | Introduction                            |

|--------|-----------------------------------------|

| 14.3   | Features                                |

|        | Functional Description                  |

| 14.4.2 | Keyboard Status and Control Register    |

| 14.5   | Wait Mode171                            |

| 14.6   | Stop Mode                               |

| 14.7   | Keyboard Module During Break Interrupts |

### 14.2 Introduction

The keyboard interrupt module (KBI) provides seven independently maskable external interrupts which are accessible via PTA0–PTA6 pins.

### 14.3 Features

Features of the keyboard interrupt module include the following:

- Seven keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Software configurable pull-up device if input pin is configured as input port bit

- Programmable edge-only or edge- and level- interrupt sensitivity

- Exit from low-power modes

MC68H(R)C908JL3 - Rev. 1.1

# Technical Data — MC68H(R)C908JL3

# Section 18. Electrical Specifications

# 18.1 Contents

| 18.2  | Introduction                     |

|-------|----------------------------------|

| 18.3  | Absolute Maximum Ratings         |

| 18.4  | Functional Operating Range193    |

| 18.5  | Thermal Characteristics          |

| 18.6  | 5V DC Electrical Characteristics |

| 18.7  | 5V Control Timing                |

| 18.8  | 5V Oscillator Characteristics    |

| 18.9  | 3V DC Electrical Characteristics |

| 18.10 | 3V Control Timing198             |

| 18.11 | 3V Oscillator Characteristics    |

| 18.12 | Typical Supply Currents          |

| 18.13 | ADC Characteristics              |

| 18.14 | Memory Characteristics           |

# 18.2 Introduction

This section contains electrical and timing specifications.

# **Electrical Specifications**

# 18.3 Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the MCU can be exposed without permanently damaging it.

NOTE:

This device is not guaranteed to operate properly at the maximum ratings. Refer to Sections **18.6** and **18.9** for guaranteed operating conditions.

Table 18-1. Absolute Maximum Ratings<sup>(1)</sup>

| Characteristic                                                        | Symbol            | Value                            | Unit |

|-----------------------------------------------------------------------|-------------------|----------------------------------|------|

| Supply voltage                                                        | $V_{DD}$          | -0.3 to +6.0                     | V    |

| Input voltage                                                         | V <sub>IN</sub>   | $V_{SS}$ = 0.3 to $V_{DD}$ + 0.3 | V    |

| Mode entry voltage, IRQ1 pin                                          | $V_{DD}+V_{HI}$   | V <sub>SS</sub> -0.3 to +8.5     | V    |

| Maximum current per pin excluding V <sub>DD</sub> and V <sub>SS</sub> | I                 | ±25                              | mA   |

| Storage temperature                                                   | T <sub>STG</sub>  | -55 to +150                      | °C   |

| Maximum current out of V <sub>SS</sub>                                | I <sub>MVSS</sub> | 100                              | mA   |

| Maximum current into V <sub>DD</sub>                                  | I <sub>MVDD</sub> | 100                              | mA   |

#### NOTE:

### **NOTE:**

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{IN}$  and  $V_{OUT}$  be constrained to the range  $V_{SS} \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ .)

<sup>1.</sup> Voltages referenced to V<sub>SS</sub>.