Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LED, LVD, POR, PWM                                                    |

| Number of I/O              | 15                                                                    |

| Program Memory Size        | 4KB (4K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                           |

| Data Converters            | A/D 12x8b                                                             |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 20-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcr908jk3cdwe |

## Technical Data — MC68H(R)C908JL3

# **List of Sections**

| Section 1. General Description21                 |

|--------------------------------------------------|

| Section 2. Memory                                |

| Section 3. Random-Access Memory (RAM)37          |

| Section 4. FLASH Memory (FLASH)39                |

| Section 5. Configuration Register (CONFIG)47     |

| Section 6. Central Processor Unit (CPU)51        |

| Section 7. System Integration Module (SIM)71     |

| Section 8. Oscillator (OSC)95                    |

| Section 9. Monitor ROM (MON)101                  |

| Section 10. Timer Interface Module (TIM)         |

| Section 11. Analog-to-Digital Converter (ADC)137 |

| Section 12. I/O Ports                            |

| Section 13. External Interrupt (IRQ)159          |

| Section 14. Keyboard Interrupt Module (KBI)165   |

| Section 15. Computer Operating Properly (COP)173 |

| Section 16. Low Voltage Inhibit (LVI)179         |

| Section 17. Break Module (BREAK)183              |

| Section 18. Electrical Specifications191         |

| Section 19. Mechanical Specifications            |

| Section 20. Ordering Information207              |

MC68H(R)C908JL3 — Rev. 1.1

# List of Sections

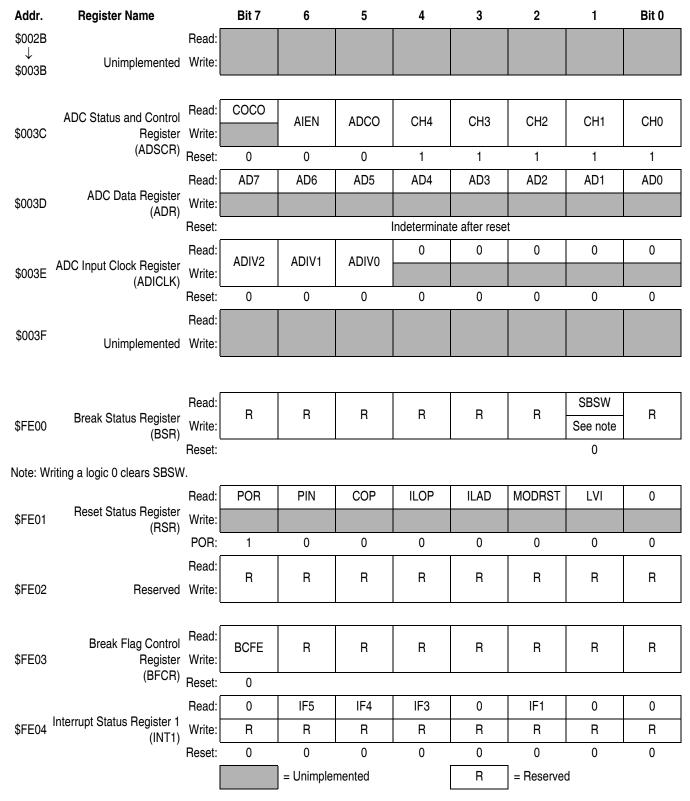

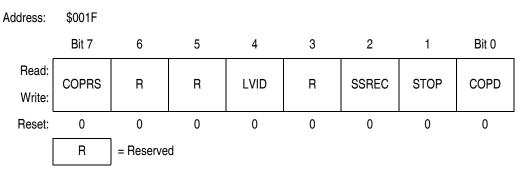

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 5)

MC68H(R)C908JL3 - Rev. 1.1

## Random-Access Memory (RAM)

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

NOTE:

Be careful when using nested subroutines. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

# System Integration Module (SIM)

| Addr.                                     | Register Name                        |        | Bit 7 | 6   | 5       | 4    | 3          | 2      | 1    | Bit 0 |

|-------------------------------------------|--------------------------------------|--------|-------|-----|---------|------|------------|--------|------|-------|

| \$FE00 Break Status Register (BSR)        | Read:                                | R      | R     | R   | R       | R    | R          | SBSW   | R    |       |

|                                           | Write:                               | n      |       |     |         |      |            | NOTE   |      |       |

|                                           |                                      | Reset: | 0     | 0   | 0       | 0    | 0          | 0      | 0    | 0     |

| Note: W                                   | Note: Writing a logic 0 clears SBSW. |        |       |     |         |      |            |        |      |       |

|                                           |                                      | Read:  | POR   | PIN | COP     | ILOP | ILAD       | MODRST | LVI  | 0     |

| \$FE01                                    | Reset Status Register (RSR)          | Write: |       |     |         |      |            |        |      |       |

|                                           |                                      | POR:   | 1     | 0   | 0       | 0    | 0          | 0      | 0    | 0     |

|                                           |                                      | Read:  | R     | R   | R       | R    | R          | R      | R    | R     |

| \$FE02                                    | Reserved                             | Write: | 11    | 11  | 11      | 11   | 11         | 11     | 11   | 11    |

|                                           |                                      | Reset: |       |     |         |      |            |        |      |       |

|                                           | Break Flag Control                   | Read:  | BCFE  | R   | R       | R    | R          | R      | R    | R     |

| \$FE03 Register                           | Write:                               | DOLL   | 11    | 11  | 11      | 11   | 11         | 11     | 11   |       |

| (BFCR)                                    |                                      | Reset: | 0     |     |         |      |            |        |      |       |

|                                           |                                      | Read:  | 0     | IF5 | IF4     | IF3  | 0          | IF1    | 0    | 0     |

| \$FE04                                    | Interrupt Status Register 1 (INT1)   | Write: | R     | R   | R       | R    | R          | R      | R    | R     |

| ()                                        |                                      | Reset: | 0     | 0   | 0       | 0    | 0          | 0      | 0    | 0     |

| \$FE05 Interrupt Status Register 2 (INT2) | Read:                                | IF14   | 0     | 0   | 0       | 0    | 0          | 0      | 0    |       |

|                                           | Write:                               | R      | R     | R   | R       | R    | R          | R      | R    |       |

|                                           | Reset:                               | 0      | 0     | 0   | 0       | 0    | 0          | 0      | 0    |       |

| \$FE06 Interrupt Status Register 3 (INT3) | Read:                                | 0      | 0     | 0   | 0       | 0    | 0          | 0      | IF15 |       |

|                                           | Write:                               | R      | R     | R   | R       | R    | R          | R      | R    |       |

| (                                         |                                      | Reset: | 0     | 0   | 0       | 0    | 0          | 0      | 0    | 0     |

|                                           | = Unimplemented R                    |        |       |     |         | R    | = Reserved | t      |      |       |

|                                           |                                      | F: 4   | 7 2   |     | ) Dogio | - C  |            | _      |      |       |

Figure 7-2. SIM I/O Register Summary

## **System Integration Module (SIM)**

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

## 7.4 Reset and System Initialization

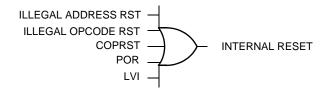

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE–FFFF (\$FEFE–FEFF in Monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see **7.5 SIM Counter**), but an external reset does not. Each of the resets sets a corresponding bit in the reset status register (RSR). (See **7.8 SIM Registers**.)

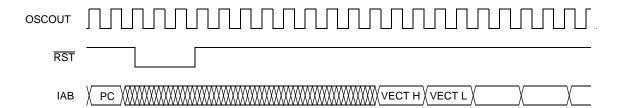

#### 7.4.1 External Pin Reset

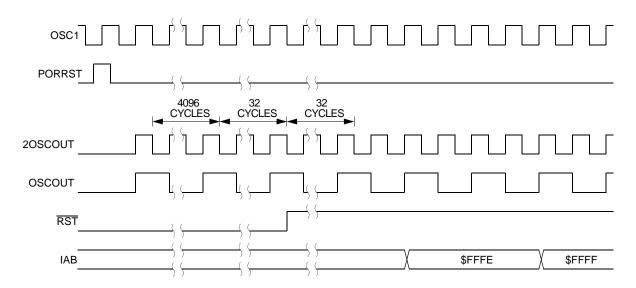

The RST pin circuits include an internal pull-up device. Pulling the asynchronous RST pin low halts all processing. The PIN bit of the reset status register (RSR) is set as long as RST is held low for a minimum of 67 2OSCCLK cycles, assuming that the POR was not the source of the reset. See Table 7-2 for details. Figure 7-4 shows the relative timing.

Table 7-2. PIN Bit Set Timing

| Reset Type | Number of Cycles Required to Set PIN |  |  |

|------------|--------------------------------------|--|--|

| POR        | 4163 (4096 + 64 + 3)                 |  |  |

| All others | 67 (64 + 3)                          |  |  |

Figure 7-4. External Reset Timing

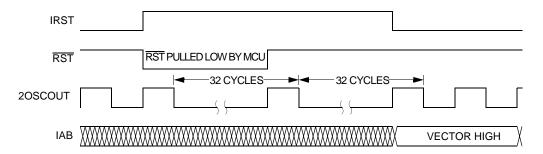

#### 7.4.2 Active Resets from Internal Sources

All internal reset sources actively pull the RST pin low for 32 2OSCOUT cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (Figure 7-5). An internal reset can be caused by an illegal address, illegal opcode, COP time-out, or POR. (See Figure 7-6. Sources of Internal Reset.) Note that for POR resets, the SIM cycles through 4096 2OSCOUT cycles during which the SIM forces the RST pin low. The internal reset signal then follows the sequence from the falling edge of RST shown in Figure 7-5.

Figure 7-5. Internal Reset Timing

The COP reset is asynchronous to the bus clock.

Figure 7-6. Sources of Internal Reset

MC68H(R)C908JL3 — Rev. 1.1

## System Integration Module (SIM)

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

#### 7.4.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power-on has occurred. The external reset pin (RST) is held low while the SIM counter counts out 4096 2OSCOUT cycles. Sixty-four 2OSCOUT cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power-on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables the oscillator to drive 2OSCOUT.

- Internal clocks to the CPU and modules are held inactive for 4096

2OSCOUT cycles to allow stabilization of the oscillator.

- The RST pin is driven low during the oscillator stabilization time.

- The POR bit of the reset status register (RSR) is set and all other bits in the register are cleared.

Figure 7-7. POR Recovery

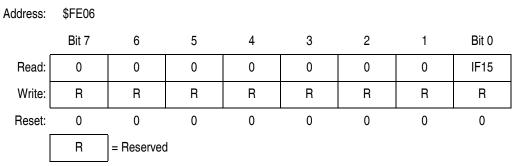

## 7.6.2.3 Interrupt Status Register 3

Figure 7-14. Interrupt Status Register 3 (INT3)

IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in **Table 7-3**.

1 = Interrupt request present

0 = No interrupt request present

Bit 1 to 7 — Always read 0

#### 7.6.3 **Reset**

All reset sources always have equal and highest priority and cannot be arbitrated.

#### 7.6.4 Break Interrupts

The break module can stop normal program flow at a software-programmable break point by asserting its break interrupt output. (See **Section 17. Break Module (BREAK)**.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

## 7.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are

MC68H(R)C908JL3 — Rev. 1.1

## **Monitor ROM (MON)**

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6—\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a FLASH location returns an invalid value and trying to execute code from FLASH causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

**NOTE:**

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$40 is set. If it is, then the correct security code has been entered and FLASH can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the FLASH module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

## 11.4.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

## 11.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating a CPU interrupt after each ADC conversion. A CPU interrupt is generated if the COCO bit is at logic 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

#### 11.6 Low-Power Modes

The following subsections describe the ADC in low-power modes.

#### 11.6.1 Wait Mode

The ADC continues normal operation during wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting the CH[4:0] bits in the ADC Status and Control register to logic 1's before executing the WAIT instruction.

## 11.6.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

## 11.7 I/O Signals

The ADC module has 12 channels that are shared with I/O port B and port D.

## **Analog-to-Digital Converter (ADC)**

## 11.7.1 ADC Voltage In (ADCVIN)

ADCVIN is the input voltage signal from one of the 12 ADC channels to the ADC module.

## 11.8 I/O Registers

These I/O registers control and monitor ADC operation:

- ADC Status and Control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

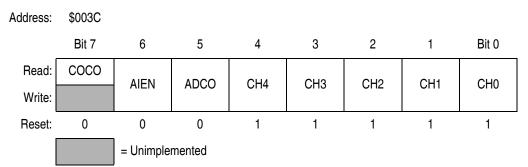

### 11.8.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC Status and Control register.

Figure 11-3. ADC Status and Control Register (ADSCR)

#### COCO — Conversions Complete Bit

When the AIEN bit is a logic 0, the COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the ADC status and control register is written or whenever the ADC data register is read. Reset clears this bit.

1 = conversion completed (AIEN = 0)

0 = conversion not completed (AIEN = 0)

When the AIEN bit is a logic 1 (CPU interrupt enabled), the COCO is a read-only bit, and will always be logic 0 when read.

## AIEN — ADC Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when the data register is read or the status/control register is written. Reset clears the AIEN bit.

- 1 = ADC interrupt enabled

- 0 = ADC interrupt disabled

#### ADCO — ADC Continuous Conversion Bit

When set, the ADC will convert samples continuously and update the ADR register at the end of each conversion. Only one conversion is allowed when this bit is cleared. Reset clears the ADCO bit.

- 1 = Continuous ADC conversion

- 0 = One ADC conversion

## ADCH[4:0] — ADC Channel Select Bits

ADCH4, ADCH3, ADCH2, ADCH1, and ADCH0 form a 5-bit field which is used to select one of the ADC channels. The five channel select bits are detailed in the following table. Care should be taken when using a port pin as both an analog and a digital input simultaneously to prevent switching noise from corrupting the analog signal. (See **Table 11-1.**)

The ADC subsystem is turned off when the channel select bits are all set to one. This feature allows for reduced power consumption for the MCU when the ADC is not used. Reset sets all of these bits to a logic 1.

**NOTE:** Recovery from the disabled state requires one conversion cycle to stabilize.

When DDRDx is a logic 1, reading address \$0003 reads the PTDx data latch. When DDRDx is a logic 0, reading address \$0003 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. **Table 12-3** summarizes the operation of the port D pins.

**Table 12-3. Port D Pin Functions**

| DDRD<br>Bit | PTD Bit          | I/O Pin<br>Mode            | Accesses<br>to DDRA | Accesses to PTD |                         |  |

|-------------|------------------|----------------------------|---------------------|-----------------|-------------------------|--|

| ы           |                  | WIOGE                      | Read/Write          | Read            | Write                   |  |

| 0           | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRD[7:0]           | Pin             | PTD[7:0] <sup>(3)</sup> |  |

| 1           | Х                | Output                     | DDRD[7:0]           | Pin             | PTD[7:0]                |  |

<sup>1.</sup> X = don't care

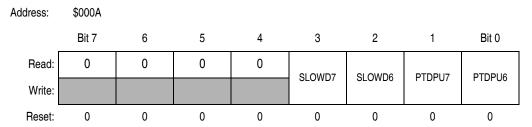

## 12.6.3 Port D Control Register (PDCR)

The Port D Control Register enables/disables the pull-up resistor and slow-edge high current capability of pins PTD6 and PTD7.

Figure 12-12. Port D Control Register (PDCR)

SLOWDx — Slow Edge Enable

The SLOWD6 and SLOWD7 bits enable the Slow-edge, open-drain, high current output (25mA sink) of port pins PTD6 and PTD7 respectively. DDRx bit is not affected by SLOWDx.

- 1 = Slow edge enabled; pin is open-drain output

- 0 = Slow edge disabled; pin is push-pull

PTDPUx — Pull-up Enable

The PTDPU6 and PTDPU7 bits enable the 5k pull-up on PTD6 and PTD7 respectively, regardless the status of DDRDx bit.

- 1 = Enable 5k pull-up

- 0 = Disable 5k pull-up

MC68H(R)C908JL3 — Rev. 1.1

<sup>2.</sup> Hi-Z = high impedance

<sup>3.</sup> Writing affects data register, but does not affect the input.

I/O Ports

Figure 16-3. Configuration Register 1 (CONFIG1)

LVID — bLow Voltage Inhibit Disable Bit

1 = Low voltage inhibit disabled

0 = Low voltage inhibit enabled

### LVIT1, LVIT0 — LVI Trip Voltage Selection

These two bits determine at which level of  $V_{DD}$  the LVI module will come into action. LVIT1 and LVIT0 are cleared by a Power-On Reset only.

| LVIT1 | LVIT0 | Trip Voltage <sup>(1)</sup> | Comments                          |

|-------|-------|-----------------------------|-----------------------------------|

| 0     | 0     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 0     | 1     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 1     | 0     | V <sub>LVR5</sub> (4.0V)    | For V <sub>DD</sub> =5V operation |

| 1     | 1     | Reserved                    |                                   |

<sup>1.</sup> See Section 18. Electrical Specifications for full parameters.

#### 16.6 Low-Power Modes

The STOP and WAIT instructions put the MCU in low-power-consumption standby modes.

#### 16.6.1 Wait Mode

The LVI module, when enabled, will continue to operate in WAIT Mode.

### 16.6.2 Stop Mode

The LVI module, when enabled, will continue to operate in STOP Mode.

MC68H(R)C908JL3 - Rev. 1.1

## Technical Data — MC68H(R)C908JL3

# Section 17. Break Module (BREAK)

## 17.1 Contents

| 17.2   | Introduction                                  |

|--------|-----------------------------------------------|

| 17.3   | Features                                      |

| 17.4   | Functional Description                        |

| 17.4.1 | Flag Protection During Break Interrupts186    |

| 17.4.2 | CPU During Break Interrupts                   |

| 17.4.3 | TIM During Break Interrupts186                |

| 17.4.4 | COP During Break Interrupts                   |

| 17.5   | Break Module Registers                        |

| 17.5.1 | Break Status and Control Register (BRKSCR)187 |

| 17.5.2 | Break Address Registers                       |

| 17.5.3 | Break Status Register188                      |

| 17.5.4 | Break Flag Control Register (BFCR)            |

| 17.6   | Low-Power Modes                               |

| 17.6.1 | Wait Mode                                     |

| 17.6.2 | Stop Mode                                     |

## 17.2 Introduction

This section describes the break module. The break module can generate a break interrupt that stops normal program flow at a defined address to enter a background program.

MC68H(R)C908JL3 — Rev. 1.1

## SBSW — SIM Break Stop/Wait

This status bit is useful in applications requiring a return to wait or stop mode after exiting from a break interrupt. Clear SBSW by writing a logic zero to it. Reset clears SBSW.

- 1 = Stop mode or wait mode was exited by break interrupt

- 0 = Stop mode or wait mode was not exited by break interrupt

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it. The following code is an example of this. Writing zero to the SBSW bit clears it.

```

; This code works if the H register has been pushed onto the stack in the break

; service routine software. This code should be executed at the end of the

; break service routine software.

HIBYTE

EQU

LOBYTE EQU

6

If not SBSW, do RTI

BRCLR SBSW, BSR, RETURN ; See if wait mode or stop mode was exited

; by break.

; If RETURNLO is not zero,

TST

LOBYTE, SP

DOLO

; then just decrement low byte.

BNE

DEC

HIBYTE, SP

; Else deal with high byte, too.

; Point to WAIT/STOP opcode.

DOTIO

DEC

LOBYTE, SP

RETURN

PULH

; Restore H register.

RTI

```

# **Mechanical Specifications**

## Ordering Information

## 20.3 MC Order Numbers

Table 20-1. MC Order Numbers

| MC order number                                                            | Oscillator type    | FLASH memory | Package        |  |  |

|----------------------------------------------------------------------------|--------------------|--------------|----------------|--|--|

| MC68HC908JL3CP<br>MC68HC908JL3CDW<br>MC68HC908JL3MP<br>MC68HC908JL3MDW     | Crystal oscillator | 4096 Bytes   | 28-pin package |  |  |

| MC68HRC908JL3CP<br>MC68HRC908JL3CDW<br>MC68HRC908JL3MP<br>MC68HRC908JL3MDW | RC oscillator      | 4090 Dytes   |                |  |  |

| MC68HC908JK3CP<br>MC68HC908JK3CDW<br>MC68HC908JK3MP<br>MC68HC908JK3MDW     | Crystal oscillator | 4096 Bytes   |                |  |  |

| MC68HRC908JK3CP<br>MC68HRC908JK3CDW<br>MC68HRC908JK3MP<br>MC68HRC908JK3MDW | RC oscillator      | 4090 Dytes   | 20-pin package |  |  |

| MC68HC908JK1CP<br>MC68HC908JK1CDW                                          | Crystal oscillator | 1526 Pytos   |                |  |  |

| MC68HRC908JK1CP<br>MC68HRC908JK1CDW                                        | RC oscillator      | 1536 Bytes   |                |  |  |

#### Notes:

$C = -40 \, ^{\circ}C$  to +85  $^{\circ}C$

M = -40 °C to +125 °C (available for  $V_{DD} = 5V$  only) P = Plastic dual in-line package (PDIP)

DW = Small outline integrated circuit package (SOIC)