# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | XCore                                                            |

| Core Size                  | 32-Bit 12-Core                                                   |

| Speed                      | 1000MIPS                                                         |

| Connectivity               | Configurable                                                     |

| Peripherals                | -                                                                |

| Number of I/O              | 73                                                               |

| Program Memory Size        | 128KB (32K x 32)                                                 |

| Program Memory Type        | SRAM                                                             |

| EEPROM Size                | -                                                                |

| RAM Size                   | -                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                        |

| Data Converters            | A/D 8x12b                                                        |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 217-LFBGA                                                        |

| Supplier Device Package    | 217-FBGA (16x16)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-u12a-128-fb217-i10 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1  | xCORE Multicore Microcontrollers         | 2   |

|----|------------------------------------------|-----|

| 2  | XS1-U12A-128-FB217 Features              | 4   |

| 3  | Pin Configuration                        | 5   |

| 4  | Signal Description                       | 6   |

| 5  | Example Application Diagram              |     |

| 6  | Product Overview                         | 11  |

| 7  | xCORE Tile Resources                     | 12  |

| 8  | Oscillator                               | 15  |

| 9  | Boot Procedure                           | 17  |

| 10 | Memory                                   |     |

| 11 | USB PHÝ                                  |     |

| 12 | Analog-to-Digital Converter              |     |

| 13 | Supervisor Logic                         |     |

| 14 | Energy management                        | 22  |

| 15 | JTAG                                     |     |

| 16 | Board Integration                        |     |

| 17 | Example XS1-U12A-128-FB217 Board Designs | 31  |

| 18 | DC and Switching Characteristics         | 35  |

| 19 | Package Information                      | 40  |

| 20 | Ordering Information                     |     |

|    | endices                                  |     |

| A  | Configuring the device                   |     |

| B  | Processor Status Configuration           |     |

| Ċ  | xCORE Tile Configuration                 | 54  |

| D  | Digital Node Configuration               | 61  |

| E  | Analogue Node Configuration              |     |

| È. | USB PHY Configuration                    |     |

| G  | ADC Configuration                        |     |

| н  | Deep sleep memory Configuration          | 22  |

| Π. | Oscillator Configuration                 | 81  |

| 1  | Real time clock Configuration            | 86  |

| K  | Power control block Configuration        |     |

|    | Device Errata                            |     |

|    | JTAG, xSCOPE and Debugging               |     |

| M  |                                          |     |

| N  | Schematics Design Check List             | 101 |

| 0  | PCB Layout Design Check List             |     |

| P  | Associated Design Documentation          |     |

| Q  | Related Documentation                    |     |

| R  | Revision History                         | 105 |

#### **xCORE** Multicore Microcontrollers 1

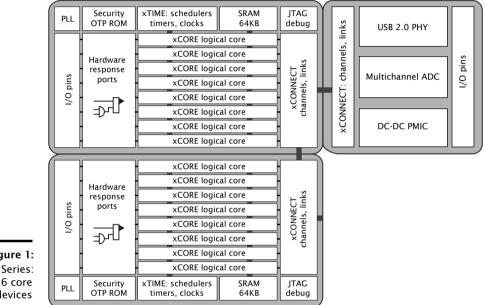

The XS1-U Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

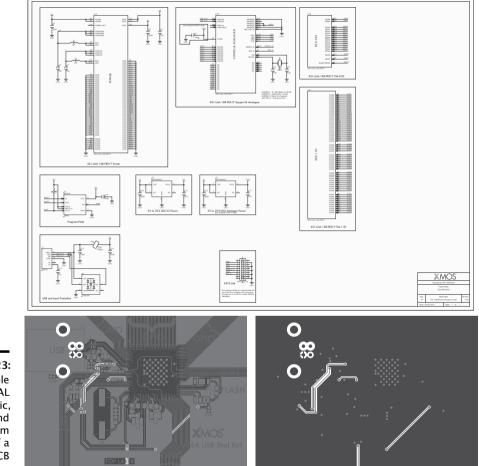

Figure 1: XS1-U Series: 6-16 core devices

Key features of the XS1-U12A-128-FB217 include:

- Tiles: Devices consist of one or more xCORE tiles. Each tile contains between four and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- Logical cores Each logical core can execute tasks such as computational code. DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 7.1

- xTIME scheduler The xTIME scheduler performs functions similar to an RTOS. in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 7.2

| Signal | Function                        |                   | Туре | Properties |

|--------|---------------------------------|-------------------|------|------------|

| X1D51  | XLC <sup>2</sup> <sub>out</sub> | 32A <sup>2</sup>  | I/0  | PDs        |

| X1D52  | XLC <sup>1</sup> <sub>out</sub> | 32A <sup>3</sup>  | I/O  | PDs        |

| X1D53  | XLC <sup>0</sup> <sub>out</sub> | 32A <sup>4</sup>  | I/O  | PDs        |

| X1D54  | XLC <sup>0</sup> <sub>in</sub>  | 32A <sup>5</sup>  | I/O  | PDs        |

| X1D55  | XLC <sup>1</sup> <sub>in</sub>  | 32A <sup>6</sup>  | I/O  | PDs        |

| X1D56  | XLC <sup>2</sup> <sub>in</sub>  | 32A <sup>7</sup>  | I/0  | PDs        |

| X1D57  | XLC <sup>3</sup> <sub>in</sub>  | 32A <sup>8</sup>  | I/O  | PDs        |

| X1D58  | XLC <sup>4</sup> <sub>in</sub>  | 32A <sup>9</sup>  | I/O  | PDs        |

| X1D61  | XLD <sup>4</sup> <sub>out</sub> | 32A <sup>10</sup> | I/O  | PDs        |

| X1D62  | XLD <sup>3</sup> <sub>out</sub> | 32A <sup>11</sup> | I/O  | PDs        |

| X1D63  | XLD <sup>2</sup> <sub>out</sub> | 32A <sup>12</sup> | I/O  | PDs        |

| X1D64  | XLD <sup>1</sup> <sub>out</sub> | 32A <sup>13</sup> | I/O  | PDs        |

| X1D65  | XLD <sup>0</sup> <sub>out</sub> | 32A <sup>14</sup> | I/O  | PDs        |

| X1D66  | XLD <sup>0</sup> <sub>in</sub>  | 32A <sup>15</sup> | I/O  | PDs        |

| X1D67  | XLD <sup>1</sup> <sub>in</sub>  | 32A <sup>16</sup> | I/O  | PDs        |

| X1D68  | XLD <sup>2</sup> <sub>in</sub>  | 32A <sup>17</sup> | I/O  | PDs        |

| X1D69  | XLD <sup>3</sup> <sub>in</sub>  | 32A <sup>18</sup> | I/O  | PDs        |

| X1D70  | XLD <sup>4</sup> <sub>in</sub>  | 32A <sup>19</sup> | I/O  | PDs        |

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools perform this operation by default. Further details on configuring the clock can be found in the XS1-L Clock Frequency Control document, X1433.

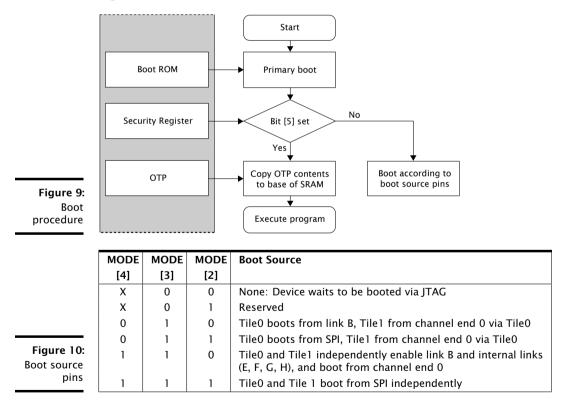

## 9 Boot Procedure

The device is kept in reset by driving RST\_N low. When in reset, all GPIO pins are high impedance. When the device is taken out of reset by releasing RST\_N the processor starts its internal reset process. After approximately 750,000 input clocks, all GPIO pins have their internal pull-resistor enabled, and the processor boots at a clock speed that depends on MODE0 and MODE1.

The processor boot procedure is illustrated in Figure 9. In normal usage, MODE[4:2] controls the boot source according to the table in Figure 10. If bit 5 of the security register (*see* 10.1) is set, the device boots from OTP.

The boot image has the following format:

A 32-bit program size *s* in words.

- 2. Input a word on channel-end 0. It will use this word as a channel to acknowledge the boot. Provide the null-channel-end 0x0000FF02 if no acknowledgment is required.

- 3. Input the boot image specified above, including the CRC.

- 4. Input an END control token.

- 5. Output an END control token to the channel-end received in step 2.

- 6. Free channel-end 0.

- 7. Jump to the loaded code.

#### 9.3 Boot from OTP

If an xCORE tile is set to use secure boot (see Figure 9), the boot image is read from address 0 of the OTP memory in the tile's security module.

This feature can be used to implement a secure bootloader which loads an encrypted image from external flash, decrypts and CRC checks it with the processor, and discontinues the boot process if the decryption or CRC check fails. XMOS provides a default secure bootloader that can be written to the OTP along with secret decryption keys.

Each tile has its own individual OTP memory, and hence some tiles can be booted from OTP while others are booted from SPI or the channel interface. This enables systems to be partially programmed, dedicating one or more tiles to perform a particular function, leaving the other tiles user-programmable.

#### 9.4 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 12 provide a strong level of protection and are sufficient for providing strong IP security.

## 10 Memory

#### 10.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit

to save power (see Appendix I). To ensure that the real-time counter increases linearly over time, a programmable value is added to the counter on every 31,250 Hz clock-tick. This means that the clock will run at a granularity of 31,250 Hz but still maintain real-time in terms of the frequency of the main oscillator. If an accurate clock is required, even whilst asleep, then an external crystal or oscillator shall be provided that is used in both AWAKE and ASLEEP state.

The designer has to make a trade-off between accuracy of clocks when asleep and awake, costs, and deep-sleep power consumption. Four example designs are shown in Figure 15.

Figure 15: Example trade-offs in oscillator selection

| Clocks used    |                | Power   | BOM     | M Accuracy |         |

|----------------|----------------|---------|---------|------------|---------|

| Awake          | Asleep         | Asleep  | costs   | Awake      | Asleep  |

| 20 Mhz SiOsc   | 31,250 SiOsc   | lowest  | lowest  | lowest     | lowest  |

| 24 MHz Crystal | 31,250 SiOsc   | lowest  | medium  | highest    | lowest  |

| 5 MHz ext osc  | 5 MHz ext osc  | medium  | highest | highest    | highest |

| 24 MHz Crystal | 24 MHz crystal | highest | medium  | highest    | highest |

During deep-sleep, the program can store some state in 128 bytes of Deep Sleep Memory.

#### 14.4 Requirements during sleep mode

Whilst in sleep mode, the device must still be powered as normal over 3V3 or 5V0 on VSUP, and 3V3 on VDDIO; however it will draw less power on both VSUP and VDDIO.

For best results (lowest power):

- ▶ The XTAL bias and XTAL oscillators should be switched off.

- ► The sleep register should be configured to

- Disable all power supplies except DCDC2.

- Set all power supplies to PFM mode

- Mask the clock

- Assert reset

- All GPIO and JTAG pins should be quiescent, and none should be driven against a pull-up or pull-down.

- ▶ 3V3 should be supplied as the input voltage to VSUP.

This will result in a power consumption of less than 100 uA on both VSUP and VDDIO.

If any power supply loses power-good status during the asleep-to-awake or awake-to-asleep transitions, a system reset is issued.

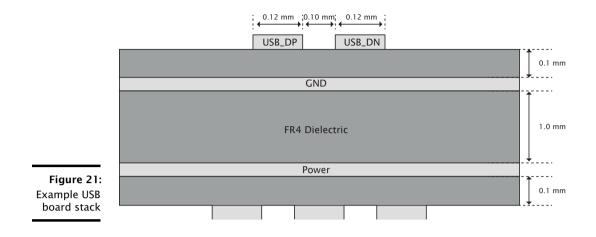

For best results, most of the routing should be done on the top layer (assuming the USB connector and XS1-U12A-128-FB217 are on the top layer) closest to GND. Reference planes should be below the transmission lines in order to maintain control of the trace impedance.

We recommend that the high-speed clock and high-speed USB differential pairs are routed first before any other routing. When routing high speed USB signals, the following guidelines should be followed:

- ▶ High speed differential pairs should be routed together.

- ▶ High-speed USB signal pair traces should be trace-length matched. Maximum trace-length mismatch should be no greater than 4mm.

- Ensure that high speed signals (clocks, USB differential pairs) are routed as far away from off-board connectors as possible.

- ▶ High-speed clock and periodic signal traces that run parallel should be at least 1.27mm away from USB\_DP/USB\_DN (see Figure 20).

- Low-speed and non-periodic signal traces that run parallel should be at least 0.5mm away from USB\_DP/USB\_DN (see Figure 20).

- ▶ Route high speed USB signals on the top of the PCB wherever possible.

- Route high speed USB traces over continuous power planes, with no breaks. If a trade-off must be made, changing signal layers is preferable to crossing plane splits.

- Follow the  $20 \times h$  rule; keep traces  $20 \times h$  (the height above the power plane) away from the edge of the power plane.

- ▶ Use a minimum of vias in high speed USB traces.

- Avoid corners in the trace. Where necessary, rather than turning through a 90 degree angle, use two 45 degree turns or an arc.

- DO NOT route USB traces near clock sources, clocked circuits or magnetic devices.

- Avoid stubs on high speed USB signals.

#### 16.3 Land patterns and solder stencils

The land pattern recommendations in this document are based on a RoHS compliant process and derived, where possible, from the nominal *Generic Requirements for Surface Mount Design and Land Pattern Standards* IPC-7351B specifications. This standard aims to achieve desired targets of heel, toe and side fillets for solder-joints.

Solder paste and ground via recommendations are based on our engineering and development kit board production. They have been found to work and optimized as appropriate to achieve a high yield. These factors should be taken into account during design and manufacturing of the PCB.

The following land patterns and solder paste contains recommendations. Final land pattern and solder paste decisions are the responsibility of the customer. These should be tuned during manufacture to suit the manufacturing process.

The package is a 217 pin Fine Ball Grid Array package on a 0.8mm pitch with 0.4mm balls.

An example land pattern is shown in Figure 22.

Pad widths and spacings are such that solder mask can still be applied between the pads using standard design rules. This is highly recommended to reduce solder shorts.

#### 16.4 Ground and Thermal Vias

Vias next to every other ground ball into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance. Vias with with a 0.6mm diameter annular ring and a 0.3mm drill would be suitable.

#### 16.5 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour pressure of moisture. Example damage can include bond wire damage, die lifting, internal or external package cracks and/or delamination.

All XMOS devices are Moisture Sensitivity Level (MSL) 3 - devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they

-XMOS<sup>®</sup>

Figure 23: Example XTAL schematic, with top and bottom layout of a 2-layer PCB

| Symbol    | Parameter                           | MIN | TYP  | MAX | UNITS    | Notes |

|-----------|-------------------------------------|-----|------|-----|----------|-------|

| VDD1V8    | 1V8 Supply Voltage                  |     | 1.80 |     | V        |       |

| V(RIPPLE) | Ripple Voltage (peak to peak)       |     | 10   | 40  | mV       |       |

| V(ACC)    | Voltage Accuracy                    | -5  |      | 5   | %        | А     |

| F(S)      | Switching Frequency                 |     | 1    |     | MHz      |       |

| F(SVAR)   | Variation in Switching<br>Frequency | -10 |      | 10  | %        |       |

| Effic     | Efficiency                          |     | 80   |     | %        |       |

| PGT(HIGH) | Powergood Threshold<br>(High)       |     | 95   |     | %/VDD1V8 |       |

| PGT(LOW)  | Powergood Threshold<br>(Low)        |     | 80   |     | %/VDD1V8 |       |

### 18.3 DC2 Characteristics

Figure 28: DC2 characteristics

A If supplied externally.

## 18.4 ADC Characteristics

| Symbol    | Parameter                     | MIN | TYP | MAX  | UNITS  | Notes |

|-----------|-------------------------------|-----|-----|------|--------|-------|

| N         | Resolution                    |     | 12  |      | bits   |       |

| Fs        | Conversion Speed              |     |     | 1    | MSPS   |       |

| Nch       | Number of Channels            |     | 8   |      |        |       |

| Vin       | Input Range                   | 0   |     | AVDD | V      |       |

| DNL       | Differential Non Linearity    | -1  |     | 1.5  | LSB    |       |

| INL       | Integral Non Linearity        | -4  |     | 4    | LSB    |       |

| E(GAIN)   | Gain Error                    | -10 |     | 10   | LSB    |       |

| E(OFFSET) | Offset Error                  | -3  |     | 3    | mV     |       |

| T(PWRUP)  | Power time for ADC Clock Fclk |     |     | 7    | 1/Fclk |       |

| ENOB      | Effective Number of bits      |     | 10  |      |        |       |

Figure 29: ADC characteristics

## 18.5 USB Characteristics

Figure 30: USB characteristics

|   | Symbol | Parameter                | MIN | TYP | MAX  | UNITS | Notes |

|---|--------|--------------------------|-----|-----|------|-------|-------|

|   | VBUS   | Power supply             | 0   | 5   | 5.25 | V     | А     |

|   | ID     | Device ID (OTG)          | 0   |     | 3.3  | V     |       |

| • | DP     | Data positive            | 0   |     | 3.3  | V     |       |

|   | DN     | Data negative (inverted) | 0   |     | 3.3  | V     |       |

|   |        |                          |     |     |      |       |       |

A The VBUS pin is used for measuring the VBUS voltage only.

Contact XMOS for further details on USB characteristics.

### 18.6 Digital I/O Characteristics

|              | V(IL) | Inp |

|--------------|-------|-----|

| Figure 31:   | V(OH) | Οι  |

| Digital I/O  | V(OL) | Οι  |

| characteris- | R(PU) | Pu  |

| tics         |       | Du  |

| Symbol | Parameter            | MIN   | TYP | MAX  | UNITS | Notes |

|--------|----------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage   | 2.00  |     | 3.60 | V     | А     |

| V(IL)  | Input low voltage    | -0.30 |     | 0.70 | V     | A     |

| V(OH)  | Output high voltage  | 2.00  |     |      | V     | B, C  |

| V(OL)  | Output low voltage   |       |     | 0.60 | V     | B, C  |

| R(PU)  | Pull-up resistance   |       | 35K |      | Ω     | D     |

| R(PD)  | Pull-down resistance |       | 35K |      | Ω     | D     |

A All pins except power supply pins.

B Ports 1A, 1D, 1E, 1H, 1I, 1J, 1K and 1L are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry.

#### 18.7 ESD Stress Voltage

Figure ESD str volta

| e 32: | Symbol | Parameter            | MIN | TYP | MAX  | UNITS | Notes |

|-------|--------|----------------------|-----|-----|------|-------|-------|

| ress  | HBM    | Human body model     |     |     | 2.00 | kV    |       |

| tage  | CDM    | Charged Device Model |     |     | 500  | V     |       |

#### 18.8 Device Timing Characteristics

|                                                     | Symbol   | Parameter                              | MIN | TYP | MAX | UNITS | Notes |

|-----------------------------------------------------|----------|----------------------------------------|-----|-----|-----|-------|-------|

|                                                     | T(RST)   | Reset pulse width                      | 5   |     |     | μs    |       |

| Figure 33:<br>Device timing<br>characteris-<br>tics | T(INIT)  | Initialisation (On Silicon Oscillator) |     |     | TBC | ms    | А     |

|                                                     | 1(1111)  | Initialisation (Crystal Oscillator)    |     |     | TBC | ms    |       |

|                                                     | T(WAKE)  | Wake up time (Sleep to Active)         |     |     | TBC | ms    |       |

|                                                     | T(SLEEP) | Sleep Time (Active to Sleep)           |     |     | TBC | ms    |       |

A Shows the time taken to start booting after RST\_N has gone high.

### 18.9 Crystal Oscillator Characteristics

#### Figure 34: Crystal oscillator characteristics

| Symbol | Parameter       | MIN | ТҮР | MAX | UNITS | Notes |

|--------|-----------------|-----|-----|-----|-------|-------|

| F(FO)  | Input Frequency | 5   |     | 30  | MHz   | А     |

A For use with USB, the design should use a 12 or 24 MHz +/- 150 ppm crystal.

### 18.10 External Oscillator Characteristics

Figure 35: External oscillator characteristics

| Symbol | Parameter          | MIN  | ТҮР | MAX  | UNITS | Notes |

|--------|--------------------|------|-----|------|-------|-------|

| F(EXT) | External Frequency |      |     | 100  | MHz   | А     |

| V(IH)  | Input high voltage | 1.62 |     | 1.98 | V     |       |

| V(IL)  | Input low voltage  |      |     | 0.4  | V     |       |

A For use with USB, the design should use a 12 or 24 MHz +/- 150 ppm crystal.

#### 18.11 Power Consumption

| Figure 36: | Symbol   | Parameter                     | MIN | TYP | MAX | UNITS | Notes |

|------------|----------|-------------------------------|-----|-----|-----|-------|-------|

| xCORE Tile | P(AWAKE) | Active Power for awake states | TBC | 600 | ТВС | mW    |       |

| currents   | P(SLEEP) | Power when asleep             | TBC | 500 | ТВС | μW    |       |

#### 18.12 Clock

#### Figure 37: Clock

L

| Symbol | Parameter                 | MIN | TYP | MAX | UNITS | Notes |

|--------|---------------------------|-----|-----|-----|-------|-------|

| f(MAX) | Processor clock frequency |     |     | 500 | MHz   | А     |

A Assumes typical tile and I/O voltages with nominal activity.

### 18.13 Processor I/O AC Characteristics

|                             | Symbol       | Parameter                                                           | MIN | TYP | MAX | UNITS | Notes |

|-----------------------------|--------------|---------------------------------------------------------------------|-----|-----|-----|-------|-------|

| <b></b>                     | T(XOVALID)   | Input data valid window                                             | 8   |     |     | ns    |       |

| Figure 38:                  | T(XOINVALID) | Output data invalid window                                          | 9   |     |     | ns    |       |

| I/O AC char-<br>acteristics | T(XIFMAX)    | Rate at which data can be sampled with respect to an external clock |     |     | 60  | MHz   |       |

The input valid window parameter relates to the capability of the device to capture data input to the chip with respect to an external clock source. It is calculated as the sum of the input setup time and input hold time with respect to the external clock as measured at the pins. The output invalid window specifies the time for which an output is invalid with respect to the external clock. Note that these parameters are specified as a window rather than absolute numbers since the device provides functionality to delay the incoming clock with respect to the incoming data.

Information on interfacing to high-speed synchronous interfaces can be found in the XS1 Port I/O Timing document, X5821.

|             | Symbol     | Parameter                      | MIN | TYP | MAX | UNITS  | Notes |

|-------------|------------|--------------------------------|-----|-----|-----|--------|-------|

|             | B(2blinkP) | 2b link bandwidth (packetized) |     |     | 103 | MBit/s | A, B  |

| Figure 39:  | B(5blinkP) | 5b link bandwidth (packetized) |     |     | 271 | MBit/s | A, B  |

| Link        | B(2blinkS) | 2b link bandwidth (streaming)  |     |     | 125 | MBit/s | В     |

| performance | B(5blinkS) | 5b link bandwidth (streaming)  |     |     | 313 | MBit/s | В     |

#### 18.14 xConnect Link Performance

A Assumes 32-byte packet in 3-byte header mode. Actual performance depends on size of the header and payload.

B 7.5 ns symbol time.

The asynchronous nature of links means that the relative phasing of CLK clocks is not important in a multi-clock system, providing each meets the required stability criteria.

18.15 JTAG Timing

|   | Symbol   | Parameter                     | MIN | TYP | MAX | UNITS | Notes |

|---|----------|-------------------------------|-----|-----|-----|-------|-------|

|   | f(TCK_D) | TCK frequency (debug)         |     |     | TBC | MHz   |       |

|   | f(TCK_B) | TCK frequency (boundary scan) |     |     | TBC | MHz   |       |

| • | T(SETUP) | TDO to TCK setup time         | TBC |     |     | ns    | А     |

| • | T(HOLD)  | TDO to TCK hold time          | TBC |     |     | ns    | А     |

| - | T(DELAY) | TCK to output delay           |     |     | TBC | ns    | В     |

Figure 40: JTAG timing

A Timing applies to TMS and TDI inputs.

B Timing applies to TDO output from negative edge of TCK.

All JTAG operations are synchronous to TCK.

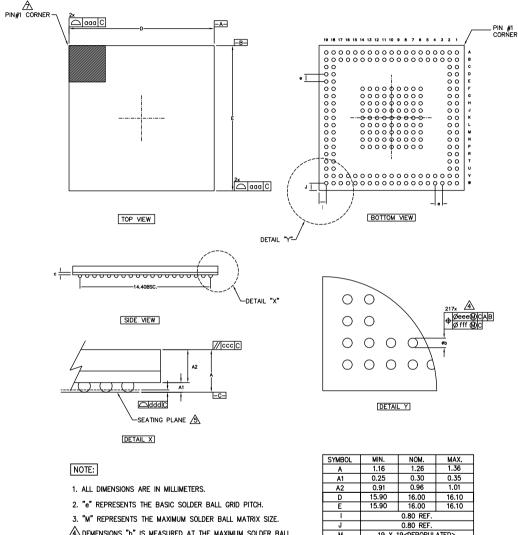

## 19 Package Information

- A DEMENSIONS "b" IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER PARALLEL TO PRIMARY DATUM C. A PRIMARY DATUM C. AND SEATING PLANE ARE DESIGNED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

- 6. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

- A1 CORNER MUST BE IDENTIFIED BY INK OR LASER MARK.

- 8. PACKAGE DIMENSIONS CONFORM TO JEDEC REGISTRATION MO-275.

| Α   | 1.16              | 1.26                                            | 1.36  |  |  |  |

|-----|-------------------|-------------------------------------------------|-------|--|--|--|

| A1  | 0.25              | 0.30                                            | 0.35  |  |  |  |

| A2  | 0.91              | 0.96                                            | 1.01  |  |  |  |

| D   | 15.90             | 16.00                                           | 16.10 |  |  |  |

| E   | 15.90             | 16.00                                           | 16.10 |  |  |  |

| -   |                   | 0.80 REF.                                       |       |  |  |  |

| J   |                   | 0.80 REF.                                       |       |  |  |  |

| м   | 19 X <sup>-</sup> | 19 <depopul< td=""><td>ATED&gt;</td></depopul<> | ATED> |  |  |  |

| aaa |                   |                                                 | 0.15  |  |  |  |

| ccc |                   |                                                 | 0.20  |  |  |  |

| ddd |                   |                                                 | 0.10  |  |  |  |

| eee |                   |                                                 | 0.15  |  |  |  |

| fff |                   |                                                 | 0.08  |  |  |  |

| b   | 0.35              | 0.40                                            | 0.45  |  |  |  |

| e   |                   | 0.80 BSC.                                       |       |  |  |  |

| c   |                   | 0.26 REF.                                       |       |  |  |  |

| Bits  | Perm | Init | Description                                                                                                                                                                                                                                       |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                                          |

| 17:16 | DRW  |      | If the debug interrupt was caused by a hardware breakpoint<br>or hardware watchpoint, this field contains the number of the<br>breakpoint or watchpoint. If multiple breakpoints or watch-<br>points trigger at once, the lowest number is taken. |

| 15:8  | DRW  |      | If the debug interrupt was caused by a logical core, this field<br>contains the number of that core. Otherwise this field is 0.                                                                                                                   |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                                          |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point                          |

**0x15:** Debug interrupt type

### B.17 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

0x16 Debug interrupt data

| <b>0x16:</b><br>Debug | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| ot data               | 31:0 | DRW  |      | Value.      |

#### B.18 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

**0x18:** Debug core control

| Bits | Perm | Init | Description                                                                                                                                                   |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                                                                                                                                      |

| 7:0  | DRW  |      | 1-hot vector defining which logical cores are stopped when not<br>in debug mode. Every bit which is set prevents the respective<br>logical core from running. |

#### B.19 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over JTAG. This is the same set of registers as the Debug Scratch registers in the xCORE tile configuration.

0x20 .. 0x27: Debug scratch

| 0x27:<br>ebug | Bits | Perm | Init | Description |

|---------------|------|------|------|-------------|

| atch          | 31:0 | DRW  |      | Value.      |

#### B.20 Instruction breakpoint address: 0x30 .. 0x33

This register contains the address of the instruction breakpoint. If the PC matches this address, then a debug interrupt will be taken. There are four instruction breakpoints that are controlled individually.

0x30 .. 0x33: Instruction breakpoint address

| ction |      |      |      |             |

|-------|------|------|------|-------------|

| point | Bits | Perm | Init | Description |

| dress | 31:0 | DRW  |      | Value.      |

### B.21 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

| Bits  | Perm | Init | Description                                                                                                                                                                                 |  |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:24 | RO   | -    | Reserved                                                                                                                                                                                    |  |

| 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                           |  |

| 15:2  | RO   | -    | Reserved                                                                                                                                                                                    |  |

| 1     | DRW  | 0    | Set to 1 to cause an instruction breakpoint if the PC is not<br>equal to the breakpoint address. By default, the breakpoint is<br>triggered when the PC is equal to the breakpoint address. |  |

| 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                               |  |

0x40 .. 0x43: Instruction breakpoint control

### B.22 Data watchpoint address 1: 0x50 ... 0x53

This set of registers contains the first address for the four data watchpoints.

0x50 .. 0x53: Data watchpoint address 1

| Data<br>point | Bits | Perm | Init | Description |  |  |

|---------------|------|------|------|-------------|--|--|

| ress 1        | 31:0 | DRW  |      | Value.      |  |  |

#### B.23 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

0x60 .. 0x63: Data watchpoint address 2

| ita<br>int | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| 5 2        | 31:0 | DRW  |      | Value.      |

#### B.24 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

|                      | Bits  | Perm | Init | Description                                                                                                                                                                                                                                                                                              |  |

|----------------------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | 31:24 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                 |  |

|                      | 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                                                                                                                                        |  |

|                      | 15:3  | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                 |  |

|                      | 2     | DRW  | 0    | Set to 1 to enable breakpoints to be triggered on loads. Breakpoints always trigger on stores.                                                                                                                                                                                                           |  |

| 3:<br>ta<br>nt<br>ol | 1     | DRW  | 0    | By default, data watchpoints trigger if memory in the rang<br>[Address1Address2] is accessed (the range is inclusive of A<br>dress1 and Address2). If set to 1, data watchpoints trigger<br>memory outside the range (Address2Address1) is accesse<br>(the range is exclusive of Address2 and Address1). |  |

| er                   | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                                                                                                                                            |  |

0x70 .. 0x73: Data breakpoint control register

#### B.25 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

-XMOS<sup>®</sup>

## D Digital Node Configuration

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...) for reads and writes).

| Number    | Perm | Description                           |  |

|-----------|------|---------------------------------------|--|

| 0x00      | RO   | Device identification                 |  |

| 0x01      | RO   | System switch description             |  |

| 0x04      | RW   | Switch configuration                  |  |

| 0x05      | RW   | Switch node identifier                |  |

| 0x06      | RW   | PLL settings                          |  |

| 0x07      | RW   | System switch clock divider           |  |

| 0x08      | RW   | Reference clock                       |  |

| 0x0C      | RW   | Directions 0-7                        |  |

| 0x0D      | RW   | Directions 8-15                       |  |

| 0x10      | RW   | DEBUG_N configuration                 |  |

| 0x1F      | RO   | Debug source                          |  |

| 0x20 0x27 | RW   | Link status, direction, and network   |  |

| 0x40 0x43 | RW   | PLink status and network              |  |

| 0x80 0x87 | RW   | Link configuration and initialization |  |

| 0xA0 0xA7 | RW   | Static link configuration             |  |

Figure 46: Summary

## D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

|                | Bits  | Perm | Init | Description                                    |

|----------------|-------|------|------|------------------------------------------------|

|                | 31:24 | RO   | 0x00 | Chip identifier.                               |

| 0x00:          | 23:16 | RO   |      | Sampled values of pins MODE0, MODE1, on reset. |

| Device         | 15:8  | RO   |      | SSwitch revision.                              |

| identification | 7:0   | RO   |      | SSwitch version.                               |

## D.2 System switch description: 0x01

This register specifies the number of processors and links that are connected to this switch.

$\cdot \mathbf{X} MOS$

XS1-U12A-128-FB217

| Bits | Perm | Init | Description                                        |  |

|------|------|------|----------------------------------------------------|--|

| 31:8 | RO   | -    | Reserved                                           |  |

| 7    | RW   | 0    | Set to 1 to switch UIFM to EXTVBUSIND mode.        |  |

| 6    | RW   | 0    | Set to 1 to switch UIFM to DRVVBUSEXT mode.        |  |

| 5    | RO   | -    | Reserved                                           |  |

| 4    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ CHRGVBUS mode.    |  |

| 3    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DISCHRGVBUS mode. |  |

| 2    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DMPULLDOWN mode.  |  |

| 1    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DPPULLDOWN mode.  |  |

| 0    | RW   | 0    | Set to 1 to switch UIFM to IDPULLUP mode.          |  |

**0x10:** UIFM on-the-go control

## F.6 UIFM on-the-go flags: 0x14

Status flags used for on-the-go negotiation

| Bits | Perm | Init | Description                  |

|------|------|------|------------------------------|

| 31:6 | RO   | -    | Reserved                     |

| 5    | RO   | 0    | Value of UTMI+ Bvalid flag.  |

| 4    | RO   | 0    | Value of UTMI+ IDGND flag.   |

| 3    | RO   | 0    | Value of UTMI+ HOSTDIS flag. |

| 2    | RO   | 0    | Value of UTMI+ VBUSVLD flag. |

| 1    | RO   | 0    | Value of UTMI+ SESSVLD flag. |

| 0    | RO   | 0    | Value of UTMI+ SESSEND flag. |

**0x14:** UIFM on-the-go flags

| Bits  | Perm | Init | Description                                                                                                                                                             |  |

|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:30 | RO   | -    | Reserved                                                                                                                                                                |  |

| 29    | RO   | 0    | 1 if VOUT6 was enabled in the previous state.                                                                                                                           |  |

| 28    | RO   | 0    | 1 if LDO5 was enabled in the previous state.                                                                                                                            |  |

| 27:26 | RO   | -    | Reserved                                                                                                                                                                |  |

| 25    | RO   | 1    | 1 if DCDC2 was enabled in the previous state.                                                                                                                           |  |

| 24    | RO   | 0    | 1 if DCDC1 was enabled in the previous state.                                                                                                                           |  |

| 23:19 | RO   | -    | Reserved                                                                                                                                                                |  |

| 18:16 | RO   |      | Current state of the power sequence state machine<br>0: Reset<br>1: Asleep<br>2: Waking 1<br>3: Waking 2<br>4: Awake Wait<br>5: Awake<br>6: Sleeping 1<br>7: Sleeping 2 |  |

| 15    | RO   | -    | Reserved                                                                                                                                                                |  |

| 14    | RO   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                                                            |  |

| 13:10 | RO   | -    | Reserved                                                                                                                                                                |  |

| 9     | RO   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                                                                       |  |

| 8     | RO   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                                                                       |  |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                |  |

| 5     | RO   | 0    | Set to 1 to enable VOUT6 (IO supply).                                                                                                                                   |  |

| 4     | RO   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                                                              |  |

| 3:2   | RO   | -    | Reserved                                                                                                                                                                |  |

| 1     | RO   | 0    | Set to 1 to enable DCDC2 (analogue supply).                                                                                                                             |  |

| 0     | RO   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                                                                 |  |

0x24: Power sequence status

## K.11 DCDC control: 0x2C

This register controls the two DC-DC converters.

-XMOS<sup>®</sup>