Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Active                                                                 |

| Туре                    | Fixed Point                                                            |

| Interface               | Host Interface, Serial Port                                            |

| Clock Rate              | 80MHz                                                                  |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 80kB                                                                   |

| Voltage - I/O           | 1.8V, 2.5V, 3.3V                                                       |

| Voltage - Core          | 1.80V                                                                  |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                        |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 100-LQFP                                                               |

| Supplier Device Package | 100-LQFP (14x14)                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-2185nkstz-320 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **TABLE OF CONTENTS**

| General Description              |

|----------------------------------|

| Architecture Overview            |

| Modes Of Operation               |

| Interrupts 5                     |

| Low-power Operation              |

| System Interface                 |

| Reset                            |

| Power Supplies                   |

| Memory Architecture              |

| Bus Request and Bus Grant        |

| Flag I/O Pins                    |

| Instruction Set Description      |

| Development System               |

| Additional Information           |

| Pin Descriptions                 |

| Memory Interface Pins            |

| Terminating Unused Pins          |

| Specifications                   |

| Recommended Operating Conditions |

| Electrical Characteristics       |

| Absolute Maximum Ratings         |

| ESD Sensitivity                  |

| ESD Diode Protection             |

| Power Dissipation                |

| Environmental Conditions         |

| Test Conditions                  |

| Timing Specifications            |

| LQFP Package Pinout              |

| BGA Package Pinout               |

| Outline Dimensions               |

| Surface Mount Design             |

| Ordering Guide                   |

### **REVISION HISTORY**

| 3/06—Rev. 0 to Rev. A                             |

|---------------------------------------------------|

| Miscellaneous Format Updates                      |

| Applied Corrections or Additional Information to: |

| Clock Signals                                     |

| External Crystal Connections                      |

| ADSP-2185 Memory Architecture                     |

| Electrical Characteristics                        |

| Absolute Maximum Ratings                          |

| ESD Diode Protection                              |

| Memory Read                                       |

| Memory Write                                      |

| Serial Ports                                      |

| Outline Dimensions                                |

| Ordering Guide                                    |

The two address buses (PMA and DMA) share a single external address bus, allowing memory to be expanded off-chip, and the two data buses (PMD and DMD) share a single external data bus. Byte memory space and I/O memory space also share the external buses.

Program memory can store both instructions and data, permitting ADSP-218xN series members to fetch two operands in a single cycle, one from program memory and one from data memory. ADSP-218xN series members can fetch an operand from program memory and the next instruction in the same cycle.

In lieu of the address and data bus for external memory connection, ADSP-218xN series members may be configured for 16-bit Internal DMA port (IDMA port) connection to external systems. The IDMA port is made up of 16 data/address pins and five control pins. The IDMA port provides transparent, direct access to the DSP's on-chip program and data RAM.

An interface to low-cost byte-wide memory is provided by the Byte DMA port (BDMA port). The BDMA port is bidirectional and can directly address up to four megabytes of external RAM or ROM for off-chip storage of program overlays or data tables.

The byte memory and I/O memory space interface supports slow memories and I/O memory-mapped peripherals with programmable wait state generation. External devices can gain control of external buses with bus request/grant signals ( $\overline{BR}$ ,  $\overline{BGH}$ , and  $\overline{BG}$ ). One execution mode (Go Mode) allows the ADSP-218xN to continue running from on-chip memory. Normal execution mode requires the processor to halt while buses are granted.

ADSP-218xN series members can respond to eleven interrupts. There can be up to six external interrupts (one edge-sensitive, two level-sensitive, and three configurable) and seven internal interrupts generated by the timer, the serial ports (SPORT), the BDMA port, and the power-down circuitry. There is also a master  $\overline{\text{RESET}}$  signal. The two serial ports provide a complete synchronous serial interface with optional companding in hardware and a wide variety of framed or frameless data transmit and receive modes of operation.

Each port can generate an internal programmable serial clock or accept an external serial clock.

ADSP-218xN series members provide up to 13 general-purpose flag pins. The data input and output pins on SPORT1 can be alternatively configured as an input flag and an output flag. In addition, eight flags are programmable as inputs or outputs, and three flags are always outputs.

A programmable interval timer generates periodic interrupts. A 16-bit count register (TCOUNT) decrements every n processor cycle, where n is a scaling value stored in an 8-bit register (TSCALE). When the value of the count register reaches zero, an interrupt is generated and the count register is reloaded from a 16-bit period register (TPERIOD).

#### **Serial Ports**

ADSP-218xN series members incorporate two complete synchronous serial ports (SPORT0 and SPORT1) for serial communications and multiprocessor communication.

Following is a brief list of the capabilities of the ADSP-218xN SPORTs. For additional information on Serial Ports, refer to the *ADSP-218x DSP Hardware Reference*.

- SPORTs are bidirectional and have a separate, doublebuffered transmit and receive section.

- SPORTs can use an external serial clock or generate their own serial clock internally.

- SPORTs have independent framing for the receive and transmit sections. Sections run in a frameless mode or with frame synchronization signals internally or externally generated. Frame sync signals are active high or inverted, with either of two pulsewidths and timings.

- SPORTs support serial data word lengths from 3 bits to 16 bits and provide optional A-law and  $\mu$ -law companding, according to CCITT recommendation G.711.

- SPORT receive and transmit sections can generate unique interrupts on completing a data word transfer.

- SPORTs can receive and transmit an entire circular buffer of data with only one overhead cycle per data word. An interrupt is generated after a data buffer transfer.

- SPORT0 has a multichannel interface to selectively receive and transmit a 24 word or 32-word, time-division multiplexed, serial bitstream.

- SPORT1 can be configured to have two external interrupts (IRQ0 and IRQ1) and the FI and FO signals. The internally generated serial clock may still be used in this configuration.

#### MODES OF OPERATION

The ADSP-218xN series modes of operation appear in Table 2.

Table 2. Modes of Operation

| Mode D | Mode C | Mode B | Mode A | Booting Method                                                                                                                                                                                                                                                   |

|--------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X      | 0      | 0      | 0      | BDMA feature is used to load the first 32 program memory words from the byte memory space. Program execution is held off until all 32 words have been loaded. Chip is configured in Full Memory Mode. <sup>1</sup>                                               |

| X      | 0      | 1      | 0      | No automatic boot operations occur. Program execution starts at external memory location 0. Chip is configured in Full Memory Mode. BDMA can still be used, but the processor does not automatically use or wait for these operations.                           |

| 0      | 1      | 0      | 0      | BDMA feature is used to load the first 32 program memory words from the byte memory space. Program execution is held off until all 32 words have been loaded. Chip is configured in Host Mode. IACK has active pull-down. (Requires additional hardware.)        |

| 0      | 1      | 0      | 1      | IDMA feature is used to load any internal memory as desired. Program execution is held off until the host writes to internal program memory location 0. Chip is configured in Host Mode. IACK has active pull-down. <sup>1</sup>                                 |

| 1      | 1      | 0      | 0      | BDMA feature is used to load the first 32 program memory words from the byte memory space. Program execution is held off until all 32 words have been loaded. Chip is configured in Host Mode; IACK requires external pull-down. (Requires additional hardware.) |

| 1      | 1      | 0      | 1      | IDMA feature is used to load any internal memory as desired. Program execution is held off until the host writes to internal program memory location 0. Chip is configured in Host Mode. IACK requires external pull-down. <sup>1</sup>                          |

<sup>&</sup>lt;sup>1</sup> Considered as standard operating settings. Using these configurations allows for easier design and better memory management.

#### **Setting Memory Mode**

Memory Mode selection for the ADSP-218xN series is made during chip reset through the use of the Mode C pin. This pin is multiplexed with the DSP's PF2 pin, so care must be taken in how the mode selection is made. The two methods for selecting the value of Mode C are active and passive.

#### **Passive Configuration**

Passive Configuration involves the use of a pull-up or pull-down resistor connected to the Mode C pin. To minimize power consumption, or if the PF2 pin is to be used as an output in the DSP application, a weak pull-up or pull-down resistance, on the order of  $10~\mathrm{k}\Omega$ , can be used. This value should be sufficient to pull the pin to the desired level and still allow the pin to operate as a programmable flag output without undue strain on the processor's output driver. For minimum power consumption during power-down, reconfigure PF2 to be an input, as the pull-up or pull-down resistance will hold the pin in a known state, and will not switch.

#### **Active Configuration**

Active Configuration involves the use of a three-statable external driver connected to the Mode C pin. A driver's output enable should be connected to the DSP's  $\overline{\text{RESET}}$  signal such that it only drives the PF2 pin when  $\overline{\text{RESET}}$  is active (low). When  $\overline{\text{RESET}}$  is deasserted, the driver should be three-state, thus allowing full use of the PF2 pin as either an input or output. To minimize power consumption during power-down, configure

the programmable flag as an output when connected to a threestated buffer. This ensures that the pin will be held at a constant level, and will not oscillate should the three-state driver's level hover around the logic switching point.

#### **IDMA ACK Configuration**

Mode D = 0 and in host mode:  $\overline{IACK}$  is an active, driven signal and cannot be "wire-OR'ed." Mode D = 1 and in host mode:  $\overline{IACK}$  is an open drain and requires an external pull-down, but multiple  $\overline{IACK}$  pins can be "wire-OR'ed" together.

#### **INTERRUPTS**

The interrupt controller allows the processor to respond to the eleven possible interrupts and reset with minimum overhead. ADSP-218xN series members provide four dedicated external interrupt input pins:  $\overline{IRQ2}$ ,  $\overline{IRQL0}$ ,  $\overline{IRQL1}$ , and  $\overline{IRQE}$  (shared with the PF7–4 pins). In addition, SPORT1 may be reconfigured for  $\overline{IRQ0}$ ,  $\overline{IRQ1}$ , FI, and FO, for a total of six external interrupts. The ADSP-218xN also supports internal interrupts from the timer, the byte DMA port, the two serial ports, software, and the power-down control circuit. The interrupt levels are internally prioritized and individually maskable (except power-down and reset). The  $\overline{IRQ2}$ ,  $\overline{IRQ0}$ , and  $\overline{IRQ1}$  input pins can be programmed to be either level- or edge-sensitive.  $\overline{IRQL0}$  and  $\overline{IRQL1}$  are level-sensitive and  $\overline{IRQE}$  is edge-sensitive. The priorities and vector addresses of all interrupts are shown in Table 3.

Table 3. Interrupt Priority and Interrupt Vector Addresses

| Source Of Interrupt               | Interrupt Vector Address (Hex) |

|-----------------------------------|--------------------------------|

| Reset (or Power-Up with PUCR = 1) | 0x0000 (Highest Priority)      |

| Power-Down (Nonmaskable)          | 0x002C                         |

| ĪRQ2                              | 0x0004                         |

| ĪRQL1                             | 0x0008                         |

| ĪRQL0                             | 0x000C                         |

| SPORT0 Transmit                   | 0x0010                         |

| SPORT0 Receive                    | 0x0014                         |

| ĪRQE                              | 0x0018                         |

| BDMA Interrupt                    | 0x001C                         |

| SPORT1 Transmit or IRQ1           | 0x0020                         |

| SPORT1 Receive or IRQ0            | 0x0024                         |

| Timer                             | 0x0028 (Lowest Priority)       |

Interrupt routines can either be nested with higher priority interrupts taking precedence or processed sequentially. Interrupts can be masked or unmasked with the IMASK register. Individual interrupt requests are logically ANDed with the bits in IMASK; the highest priority unmasked interrupt is then selected. The power-down interrupt is nonmaskable.

ADSP-218xN series members mask all interrupts for one instruction cycle following the execution of an instruction that modifies the IMASK register. This does not affect serial port autobuffering or DMA transfers.

The interrupt control register, ICNTL, controls interrupt nesting and defines the  $\overline{IRQ0}$ ,  $\overline{IRQ1}$ , and  $\overline{IRQ2}$  external interrupts to be either edge- or level-sensitive. The  $\overline{IRQE}$  pin is an external edge-sensitive interrupt and can be forced and cleared. The  $\overline{IRQL0}$  and  $\overline{IRQL1}$  pins are external level sensitive interrupts.

The IFC register is a write-only register used to force and clear interrupts. On-chip stacks preserve the processor status and are automatically maintained during interrupt handling. The stacks are 12 levels deep to allow interrupt, loop, and subroutine nesting. The following instructions allow global enable or disable servicing of the interrupts (including power-down), regardless of the state of IMASK:

ENA INTS;

DIS INTS;

Disabling the interrupts does not affect serial port autobuffering or DMA. When the processor is reset, interrupt servicing is enabled.

#### **LOW-POWER OPERATION**

ADSP-218xN series members have three low-power modes that significantly reduce the power dissipation when the device operates under standby conditions. These modes are:

- · Power-Down

- Idle

- Slow Idle

The CLKOUT pin may also be disabled to reduce external power dissipation.

#### Power-Down

ADSP-218xN series members have a low-power feature that lets the processor enter a very low-power dormant state through hardware or software control. Following is a brief list of power-down features. Refer to the *ADSP-218x DSP Hardware Reference*, "System Interface" chapter, for detailed information about the power-down feature.

- Quick recovery from power-down. The processor begins executing instructions in as few as 200 CLKIN cycles.

- Support for an externally generated TTL or CMOS processor clock. The external clock can continue running during power-down without affecting the lowest power rating and 200 CLKIN cycle recovery.

- Support for crystal operation includes disabling the oscillator to save power (the processor automatically waits approximately 4096 CLKIN cycles for the crystal oscillator to start or stabilize), and letting the oscillator run to allow 200 CLKIN cycle start-up.

- Power-down is initiated by either the power-down pin (PWD) or the software power-down force bit. Interrupt support allows an unlimited number of instructions to be executed before optionally powering down. The powerdown interrupt also can be used as a nonmaskable, edgesensitive interrupt.

- Context clear/save control allows the processor to continue where it left off or start with a clean context when leaving the power-down state.

- The RESET pin also can be used to terminate power-down.

- Power-down acknowledge pin (PWDACK) indicates when the processor has entered power-down.

#### Idle

When the ADSP-218xN is in the Idle Mode, the processor waits indefinitely in a low-power state until an interrupt occurs. When an unmasked interrupt occurs, it is serviced; execution then continues with the instruction following the IDLE instruction. In Idle mode IDMA, BDMA, and autobuffer cycle steals still occur.

#### Slow Idle

The IDLE instruction is enhanced on ADSP-218xN series members to let the processor's internal clock signal be slowed, further reducing power consumption. The reduced clock frequency, a programmable fraction of the normal clock rate, is specified by a selectable divisor given in the IDLE instruction.

The format of the instruction is:

IDLE (n);

where n = 16, 32, 64, or 128. This instruction keeps the processor fully functional, but operating at the slower clock rate. While it is in this state, the processor's other internal clock signals,

such as SCLK, CLKOUT, and timer clock, are reduced by the same ratio. The default form of the instruction, when no clock divisor is given, is the standard IDLE instruction.

When the IDLE (n) instruction is used, it effectively slows down the processor's internal clock and thus its response time to incoming interrupts. The one-cycle response time of the standard idle state is increased by n, the clock divisor. When an enabled interrupt is received, ADSP-218xN series members remain in the idle state for up to a maximum of n processor cycles (n = 16, 32, 64, or 128) before resuming normal operation.

When the IDLE (n) instruction is used in systems that have an externally generated serial clock (SCLK), the serial clock rate may be faster than the processor's reduced internal clock rate. Under these conditions, interrupts must not be generated at a

faster rate than can be serviced, due to the additional time the processor takes to come out of the idle state (a maximum of n processor cycles).

#### **SYSTEM INTERFACE**

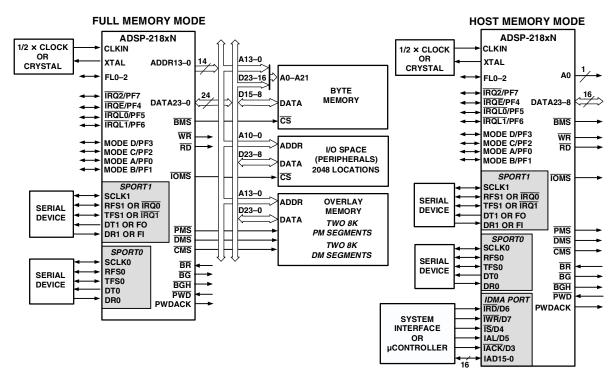

Figure 2 shows typical basic system configurations with the ADSP-218xN series, two serial devices, a byte-wide EPROM, and optional external program and data overlay memories (mode-selectable). Programmable wait state generation allows the processor to connect easily to slow peripheral devices. ADSP-218xN series members also provide four external interrupts and two serial ports or six external interrupts and one serial port. Host Memory Mode allows access to the full external data bus, but limits addressing to a single address bit (A0). Through the use of external hardware, additional system peripherals can be added in this mode to generate and latch address signals.

Figure 2. Basic System Interface

## **PIN DESCRIPTIONS**

ADSP-218xN series members are available in a 100-lead LQFP package and a 144-ball BGA package. In order to maintain maximum functionality and reduce package size and pin count, some serial port, programmable flag, interrupt and external bus pins have dual, multiplexed functionality. The external bus pins are configured during  $\overline{\text{RESET}}$  only, while serial port pins are

software configurable during program execution. Flag and interrupt functionality is retained concurrently on multiplexed pins. In cases where pin functionality is reconfigurable, the default state is shown in plain text in Table 9, while alternate functionality is shown in *italics*.

Table 9. Common-Mode Pins

| Pin Name        | No. of Pins | I/O | Function                                                       |  |  |

|-----------------|-------------|-----|----------------------------------------------------------------|--|--|

| RESET           | 1           | I   | Processor Reset Input                                          |  |  |

| BR              | 1           | I   | Bus Request Input                                              |  |  |

| BG              | 1           | 0   | Bus Grant Output                                               |  |  |

| BGH             | 1           | 0   | Bus Grant Hung Output                                          |  |  |

| DMS             | 1           | 0   | Data Memory Select Output                                      |  |  |

| PMS             | 1           | 0   | Program Memory Select Output                                   |  |  |

| ĪOMS            | 1           | 0   | Memory Select Output                                           |  |  |

| BMS             | 1           | 0   | Byte Memory Select Output                                      |  |  |

| CMS             | 1           | 0   | Combined Memory Select Output                                  |  |  |

| RD              | 1           | 0   | Memory Read Enable Output                                      |  |  |

| $\overline{WR}$ | 1           | 0   | Memory Write Enable Output                                     |  |  |

| ĪRQ2            | 1           | I   | Edge- or Level-Sensitive Interrupt Request <sup>1</sup>        |  |  |

| PF7             |             | I/O | Programmable I/O Pin                                           |  |  |

| ĪRQL1           | 1           | I   | Level-Sensitive Interrupt Requests <sup>1</sup>                |  |  |

| PF6             |             | I/O | Programmable I/O Pin                                           |  |  |

| ĪRQL0           | 1           | I   | Level-Sensitive Interrupt Requests <sup>1</sup>                |  |  |

| PF5             |             | I/O | Programmable I/O Pin                                           |  |  |

| ĪRQE            | 1           | I   | Edge-Sensitive Interrupt Requests <sup>1</sup>                 |  |  |

| PF4             |             | I/O | Programmable I/O Pin                                           |  |  |

| Mode D          | 1           | I   | Mode Select Input—Checked Only During RESET                    |  |  |

| PF3             |             | I/O | Programmable I/O Pin During Normal Operation                   |  |  |

| Mode C          | 1           | 1   | Mode Select Input—Checked Only During RESET                    |  |  |

| PF2             |             | I/O | Programmable I/O Pin During Normal Operation                   |  |  |

| Mode B          | 1           | I   | Mode Select Input—Checked Only During RESET                    |  |  |

| PF1             |             | I/O | Programmable I/O Pin During Normal Operation                   |  |  |

| Mode A          | 1           | 1   | Mode Select Input—Checked Only During RESET                    |  |  |

| PF0             |             | I/O | Programmable I/O Pin During Normal Operation                   |  |  |

| CLKIN           | 1           | I   | Clock Input                                                    |  |  |

| XTAL            | 1           | 0   | Quartz Crystal Output                                          |  |  |

| CLKOUT          | 1           | 0   | Processor Clock Output                                         |  |  |

| SPORT0          | 5           | I/O | Serial Port I/O Pins                                           |  |  |

| SPORT1          | 5           | I/O | Serial Port I/O Pins                                           |  |  |

| ĪRQ1−0, FI, FO  |             |     | Edge- or Level-Sensitive Interrupts, FI, FO <sup>2</sup>       |  |  |

| PWD             | 1           | I   | Power-Down Control Input                                       |  |  |

| PWDACK          | 1           | 0   | Power-Down Acknowledge Control Output                          |  |  |

| FL0, FL1, FL2   | 3           | 0   | Output Flags                                                   |  |  |

| $V_{DDINT}$     | 2           | 1   | Internal V <sub>DD</sub> (1.8 V) Power (LQFP)                  |  |  |

| $V_{DDEXT}$     | 4           | 1   | External V <sub>DD</sub> (1.8 V, 2.5 V, or 3.3 V) Power (LQFP) |  |  |

| GND             | 10          | I   | Ground (LQFP)                                                  |  |  |

Table 9. Common-Mode Pins (Continued)

| Pin Name    | No. of Pins | I/O | Function                                                      |

|-------------|-------------|-----|---------------------------------------------------------------|

| $V_{DDINT}$ | 4           | I   | Internal V <sub>DD</sub> (1.8 V) Power (BGA)                  |

| $V_{DDEXT}$ | 7           | I   | External V <sub>DD</sub> (1.8 V, 2.5 V, or 3.3 V) Power (BGA) |

| GND         | 20          | 1   | Ground (BGA)                                                  |

| EZ-Port     | 9           | I/O | For Emulation Use                                             |

<sup>&</sup>lt;sup>1</sup> Interrupt/Flag pins retain both functions concurrently. If IMASK is set to enable the corresponding interrupts, the DSP will vector to the appropriate interrupt vector address when the pin is asserted, either by external devices or set as a programmable flag.

#### **MEMORY INTERFACE PINS**

ADSP-218xN series members can be used in one of two modes: Full Memory Mode, which allows BDMA operation with full external overlay memory and I/O capability, or Host Mode, which allows IDMA operation with limited external addressing capabilities.

The operating mode is determined by the state of the Mode C pin during RESET and cannot be changed while the processor is running. Table 10 and Table 11 list the active signals at specific pins of the DSP during either of the two operating modes (Full Memory or Host). A signal in one table shares a pin with a signal from the other table, with the active signal determined by the mode that is set. For the shared pins and their alternate signals (e.g., A4/IAD3), refer to the package pinouts in Table 27 on Page 41 and Table 28 on Page 43.

Table 10. Full Memory Mode Pins (Mode C = 0)

| Pin Name | No. of Pins | I/O | Function                                                                                   |

|----------|-------------|-----|--------------------------------------------------------------------------------------------|

| A13-0    | 14          | 0   | Address Output Pins for Program, Data, Byte, and I/O Spaces                                |

| D23-0    | 24          | I/O | Data I/O Pins for Program, Data, Byte, and I/O Spaces (8 MSBs are also used as Byte Memory |

|          |             |     | Addresses.)                                                                                |

Table 11. Host Mode Pins (Mode C = 1)

| Pin Name | No. of Pins | I/O | Function                                                                |  |  |

|----------|-------------|-----|-------------------------------------------------------------------------|--|--|

| IAD15-0  | 16          | I/O | IDMA Port Address/Data Bus                                              |  |  |

| A0       | 1           | 0   | ddress Pin for External I/O, Program, Data, or Byte Access <sup>1</sup> |  |  |

| D23-8    | 16          | I/O | Data I/O Pins for Program, Data, Byte, and I/O Spaces                   |  |  |

| ĪWR      | 1           | I   | IDMA Write Enable                                                       |  |  |

| ĪRD      | 1           | I   | DMA Read Enable                                                         |  |  |

| IAL      | 1           | I   | IDMA Address Latch Pin                                                  |  |  |

| ĪS       | 1           | I   | IDMA Select                                                             |  |  |

| IACK     | 1           | 0   | IDMA Port Acknowledge Configurable in Mode D; Open Drain                |  |  |

$<sup>^{1}</sup>$  In Host Mode, external peripheral addresses can be decoded using the A0,  $\overline{\text{CMS}}$ ,  $\overline{\text{PMS}}$ ,  $\overline{\text{DMS}}$ , and  $\overline{\text{IOMS}}$  signals.

#### **TERMINATING UNUSED PINS**

Table 12 shows the recommendations for terminating unused pins.

Table 12. Unused Pin Terminations

| Pin Name <sup>1</sup> | I/O<br>3-State<br>(Z) <sup>2</sup> | Reset<br>State | Hi-Z <sup>3</sup> Caused By | Unused Configuration |

|-----------------------|------------------------------------|----------------|-----------------------------|----------------------|

| XTAL                  | 0                                  | 0              |                             | Float                |

| CLKOUT                | 0                                  | 0              |                             | Float <sup>4</sup>   |

| A13-1 or              | O (Z)                              | Hi-Z           | BR, EBR                     | Float                |

| IAD12-0               | I/O (Z)                            | Hi-Z           | ĪS                          | Float                |

| A0                    | O (Z)                              | Hi-Z           | BR, EBR                     | Float                |

$<sup>^2\,\</sup>mathrm{SPORT}$  configuration determined by the DSP System Control Register. Software configurable.

Table 12. Unused Pin Terminations (Continued)

|                       | I/O<br>3-State   | Reset |                 |                                                                                |  |

|-----------------------|------------------|-------|-----------------|--------------------------------------------------------------------------------|--|

| Pin Name <sup>1</sup> | (Z) <sup>2</sup> | State | Hi-Z³ Caused By | Unused Configuration                                                           |  |

| D23-8                 | I/O (Z)          | Hi-Z  | BR, EBR         | Float                                                                          |  |

| D7 or                 | I/O (Z)          | Hi-Z  | BR, EBR         | Float                                                                          |  |

| ĪWR                   | 1                | I     |                 | High (Inactive)                                                                |  |

| D6 or                 | I/O (Z)          | Hi-Z  | BR, EBR         | Float                                                                          |  |

| ĪRD                   | 1                | ı     | BR, EBR         | High (Inactive)                                                                |  |

| D5 or                 | I/O (Z)          | Hi-Z  |                 | Float                                                                          |  |

| IAL                   | 1                | ı     |                 | Low (Inactive)                                                                 |  |

| D4 or                 | I/O (Z)          | Hi-Z  | BR, EBR         | Float                                                                          |  |

| ĪS                    | 1                | I     |                 | High (Inactive)                                                                |  |

| D3 or                 | I/O (Z)          | Hi-Z  | BR, EBR         | Float                                                                          |  |

| ĪACK                  |                  |       |                 | Float                                                                          |  |

| D2-0 or               | I/O (Z)          | Hi-Z  | BR, EBR         | Float                                                                          |  |

| IAD15-13              | I/O (Z)          | Hi-Z  | ĪS              | Float                                                                          |  |

| PMS                   | O (Z)            | 0     | BR, EBR         | Float                                                                          |  |

| <del>DMS</del>        | O (Z)            | 0     | BR, EBR         | Float                                                                          |  |

| BMS                   | O (Z)            | 0     | BR, EBR         | Float                                                                          |  |

| ĪOMS                  | O (Z)            | 0     | BR, EBR         | Float                                                                          |  |

| <del>CMS</del>        | O (Z)            | 0     | BR, EBR         | Float                                                                          |  |

| RD                    | O (Z)            | 0     | BR, EBR         | Float                                                                          |  |

| $\overline{WR}$       | O (Z)            | 0     | BR, EBR         | Float                                                                          |  |

| BR                    | 1                | I     |                 | High (Inactive)                                                                |  |

| BG                    | O (Z)            | 0     | EE              | Float                                                                          |  |

| BGH                   | 0                | 0     |                 | Float                                                                          |  |

| ĪRQ2/PF7              | I/O (Z)          | I     |                 | Input = High (Inactive) or Program as Output, Set 1, Let Float <sup>5</sup>    |  |

| IRQL1/PF6             | I/O (Z)          | I     |                 | Input = High (Inactive) or Program as Output, Set to 1, Let Float <sup>5</sup> |  |

| IRQL0/PF5             | I/O (Z)          | I     |                 | Input = High (Inactive) or Program as Output, Set to 1, Let Float <sup>5</sup> |  |

| IRQE/PF4              | I/O (Z)          | I     |                 | Input = High (Inactive) or Program as Output, Set to 1, Let Float <sup>5</sup> |  |

| PWD                   | 1                | I     |                 | High                                                                           |  |

| SCLK0                 | I/O              | I     |                 | Input = High or Low, Output = Float                                            |  |

| RFS0                  | I/O              | I     |                 | High or Low                                                                    |  |

| DR0                   | 1                | I     |                 | High or Low                                                                    |  |

| TFS0                  | I/O              | I     | High or Low     |                                                                                |  |

| DT0                   | 0                | О     |                 | Float                                                                          |  |

| SCLK1                 | I/O              | I     |                 | Input = High or Low, Output = Float                                            |  |

| RFS1/IRQ0             | I/O              | I     |                 | High or Low                                                                    |  |

| DR1/FI                | 1                | I     |                 | High or Low                                                                    |  |

| TFS1/IRQ1             | I/O              | I     |                 | High or Low                                                                    |  |

| DT1/FO                | 0                | 0     |                 | Float                                                                          |  |

| EE                    | I                | I     |                 | Float                                                                          |  |

| EBR                   | I                | I     |                 | Float                                                                          |  |

| EBG                   | 0                | 0     |                 | Float                                                                          |  |

#### TIMING SPECIFICATIONS

This section contains timing information for the DSP's external signals.

#### **General Notes**

Use the exact timing information given. Do not attempt to derive parameters from the addition or subtraction of others. While addition or subtraction would yield meaningful results for an individual device, the values given in this data sheet reflect statistical variations and worst cases. Consequently, parameters cannot be added up meaningfully to derive longer times.

### **Timing Notes**

Switching characteristics specify how the processor changes its signals. Designers have no control over this timing—circuitry external to the processor must be designed for compatibility with these signal characteristics. Switching characteristics tell what the processor will do in a given circumstance. Switching characteristics can also be used to ensure that any timing requirement of a device connected to the processor (such as memory) is satisfied.

Timing requirements apply to signals that are controlled by circuitry external to the processor, such as the data input for a read operation. Timing requirements guarantee that the processor operates correctly with other devices.

#### **Frequency Dependency For Timing Specifications**

$t_{\rm CK}$  is defined as 0.5  $t_{\rm CKI}$ . The ADSP-218xN uses an input clock with a frequency equal to half the instruction rate. For example, a 40 MHz input clock (which is equivalent to 25 ns) yields a 12.5 ns processor cycle (equivalent to 80 MHz).  $t_{\rm CK}$  values within the range of 0.5  $t_{\rm CKI}$  period should be substituted for all relevant timing parameters to obtain the specification value.

Example:  $t_{CKH} = 0.5 t_{CK} - 2 ns = 0.5 (12.5 ns) - 2 ns = 4.25 ns$

#### **Output Drive Currents**

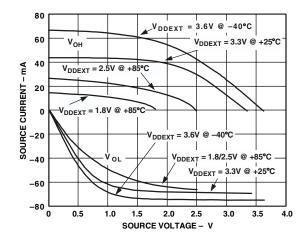

Figure 21 shows typical I-V characteristics for the output drivers on the ADSP-218xN series. The curves represent the current drive capability of the output drivers as a function of output voltage.

Figure 23 shows the typical power-down supply current.

#### **Capacitive Loading**

Figure 24 and Figure 25 show the capacitive loading characteristics of the ADSP-218xN.

Figure 21. Typical Output Driver Characteristics for  $V_{DDEXT}$  at 3.6 V, 3.3 V, 2.5 V, and 1.8 V

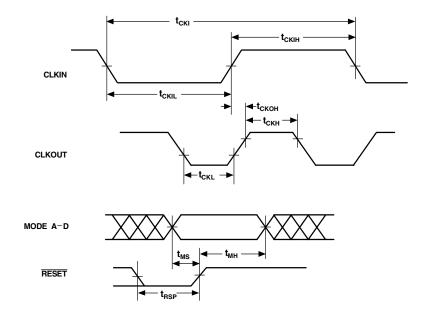

### **Clock Signals and Reset**

Table 15. Clock Signals and Reset

| Paramet           | er                           | Min                           | Max | Unit |

|-------------------|------------------------------|-------------------------------|-----|------|

| Timing Re         | equirements:                 |                               |     |      |

| $t_{\text{CKI}}$  | CLKIN Period                 | 25                            | 40  | ns   |

| $t_{\text{CKIL}}$ | CLKIN Width Low              | 8                             |     | ns   |

| $t_{\text{CKIH}}$ | CLKIN Width High             | 8                             |     | ns   |

| Switching         | Characteristics:             |                               |     |      |

| $t_{\text{CKL}}$  | CLKOUT Width Low             | 0.5t <sub>CK</sub> – 3        |     | ns   |

| $t_{CKH}$         | CLKOUT Width High            | 0.5t <sub>CK</sub> – 3        |     | ns   |

| $t_{CKOH}$        | CLKIN High to CLKOUT High    | 0                             | 8   | ns   |

| Control Si        | gnals Timing Requirements:   |                               |     |      |

| $t_{RSP}$         | RESET Width Low              | 5t <sub>CK</sub> <sup>1</sup> |     | ns   |

| t <sub>MS</sub>   | Mode Setup before RESET High | 7                             |     | ns   |

| t <sub>MH</sub>   | Mode Hold after RESET High   | 5                             |     | ns   |

<sup>&</sup>lt;sup>1</sup> Applies after power-up sequence is complete. Internal phase lock loop requires no more than 2000 CLKIN cycles, assuming stable CLKIN (not including crystal oscillator start-up time).

Figure 26. Clock Signals and Reset

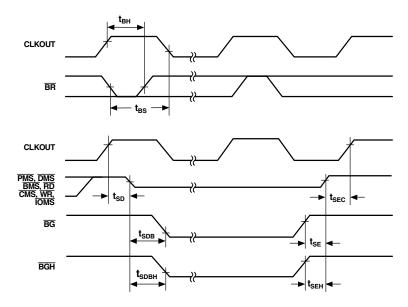

### **Bus Request-Bus Grant**

Table 17. Bus Request-Bus Grant

| Paramet            | er                                                                                                                            | Min                     | Max              | Unit |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|------|

| Timing Re          | equirements:                                                                                                                  |                         |                  |      |

| $t_{BH}$           | BR Hold after CLKOUT High <sup>1</sup>                                                                                        | 0.25t <sub>CK</sub> + 2 |                  | ns   |

| $t_{BS}$           | BR Setup before CLKOUT Low <sup>1</sup>                                                                                       | 0.25t <sub>CK</sub> + 8 |                  | ns   |

| Switching          | g Characteristics:                                                                                                            |                         |                  |      |

| $t_{SD}$           | CLKOUT High to $\overline{xMS}$ , $\overline{RD}$ , $\overline{WR}$ Disable <sup>2</sup>                                      |                         | $0.25t_{CK} + 8$ | ns   |

| $t_{SDB}$          | $\overline{\text{xMS}}$ , $\overline{\text{RD}}$ , $\overline{\text{WR}}$ Disable to $\overline{\text{BG}}$ Low               | 0                       |                  | ns   |

| $t_{SE}$           | $\overline{BG}$ High to $\overline{xMS}$ , $\overline{RD}$ , $\overline{WR}$ Enable                                           | 0                       |                  | ns   |

| $t_{SEC}$          | xMS, RD, WR Enable to CLKOUT High                                                                                             | 0.25t <sub>CK</sub> – 3 |                  | ns   |

| t <sub>SDBH</sub>  | $\overline{XMS}$ , $\overline{RD}$ , $\overline{WR}$ Disable to $\overline{BGH}$ Low <sup>3</sup>                             | О                       |                  | ns   |

| $\mathbf{t}_{SEH}$ | $\overline{\text{BGH}}$ High to $\overline{\text{xMS}}$ , $\overline{\text{RD}}$ , $\overline{\text{WR}}$ Enable <sup>3</sup> | 0                       |                  | ns   |

<sup>&</sup>lt;sup>1</sup> BR is an asynchronous signal. If BR meets the setup/hold requirements, it will be recognized during the current clock cycle; otherwise the signal will be recognized on the following cycle. Refer to the ADSP-2100 Family User's Manual for BR/BG cycle relationships.

$<sup>^3\</sup>overline{ ext{BGH}}$  is asserted when the bus is granted and the processor or BDMA requires control of the bus to continue.

Figure 28. Bus Request-Bus Grant

$<sup>^{2}\</sup>overline{\text{xMS}} = \overline{\text{PMS}}, \overline{\text{DMS}}, \overline{\text{CMS}}, \overline{\text{IOMS}}, \overline{\text{BMS}}.$

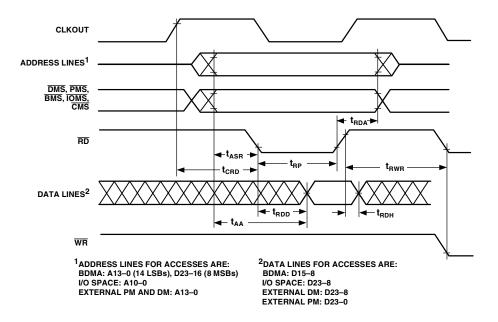

### **Memory Read**

Table 18. Memory Read

| Paramet          | er                                                            | Min                     | Max                  | Unit |

|------------------|---------------------------------------------------------------|-------------------------|----------------------|------|

| Timing Re        | equirements:                                                  |                         |                      |      |

| $t_{RDD}$        | RD Low to Data Valid <sup>1</sup>                             |                         | $0.5t_{CK} - 5 + w$  | ns   |

| t <sub>AA</sub>  | A13-0, $\overline{xMS}$ to Data Valid <sup>2</sup>            |                         | $0.75t_{CK} - 6 + w$ | ns   |

| $t_{RDH}$        | Data Hold from RD High                                        | 0                       |                      | ns   |

| Switching        | Characteristics:                                              |                         |                      |      |

| $t_{RP}$         | RD Pulse Width                                                | $0.5t_{CK} - 3 + w$     |                      | ns   |

| $t_{CRD}$        | CLKOUT High to RD Low                                         | 0.25t <sub>CK</sub> – 2 | $0.25t_{CK} + 4$     | ns   |

| t <sub>ASR</sub> | A13–0, xMS Setup before RD Low                                | 0.25t <sub>CK</sub> – 3 |                      | ns   |

| t <sub>RDA</sub> | A13–0, $\overline{xMS}$ Hold after $\overline{RD}$ Deasserted | 0.25t <sub>CK</sub> – 3 |                      | ns   |

| t <sub>RWR</sub> | RD High to RD or WR Low                                       | 0.5t <sub>CK</sub> - 3  |                      | ns   |

$<sup>^{1} \</sup>frac{\text{w} = \text{wait states 3 t}_{\text{CK}}}{^{2} \overline{\text{xMS}} = \overline{\text{PMS}}, \overline{\text{DMS}}, \overline{\text{CMS}}, \overline{\text{IOMS}}, \overline{\text{BMS}}}.$

Figure 29. Memory Read

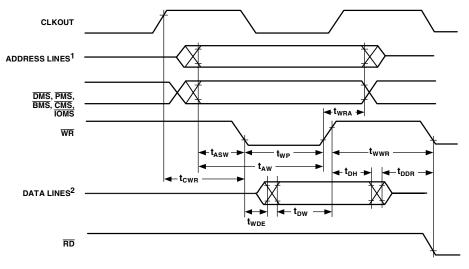

### **Memory Write**

Table 19. Memory Write

| Paramet          | er                                                                    | Min                     | Max              | Unit |

|------------------|-----------------------------------------------------------------------|-------------------------|------------------|------|

| Switching        | g Characteristics:                                                    |                         |                  |      |

| $t_{\text{DW}}$  | Data Setup before WR High <sup>1</sup>                                | $0.5t_{CK} - 4 + w$     |                  | ns   |

| $t_{DH}$         | Data Hold after WR High                                               | 0.25t <sub>CK</sub> – 1 |                  | ns   |

| $t_WP$           | WR Pulse Width                                                        | $0.5t_{CK} - 3 + w$     |                  | ns   |

| $t_{\text{WDE}}$ | WR Low to Data Enabled                                                | 0                       |                  | ns   |

| t <sub>ASW</sub> | A13–0, $\overline{xMS}$ Setup before $\overline{WR}$ Low <sup>2</sup> | 0.25t <sub>CK</sub> – 3 |                  | ns   |

| $t_{DDR}$        | Data Disable before WR or RD Low                                      | 0.25t <sub>CK</sub> – 3 |                  | ns   |

| $t_{CWR}$        | CLKOUT High to WR Low                                                 | 0.25t <sub>CK</sub> – 2 | $0.25t_{CK} + 4$ | ns   |

| t <sub>AW</sub>  | A13-0, xMS Setup before WR Deasserted                                 | $0.75t_{CK} - 5 + w$    |                  | ns   |

| t <sub>WRA</sub> | A13–0, $\overline{xMS}$ Hold after $\overline{WR}$ Deasserted         | 0.25t <sub>CK</sub> – 1 |                  | ns   |

| t <sub>wwR</sub> | WR High to RD or WR Low                                               | 0.5t <sub>CK</sub> – 3  |                  | ns   |

$<sup>^{1}</sup>$  w = wait states  $\frac{3}{5}$  t<sub>CK</sub>.

$<sup>^{2}\</sup>overline{\text{xMS}} = \overline{\text{PMS}}, \overline{\text{DMS}}, \overline{\text{CMS}}, \overline{\text{IOMS}}, \overline{\text{BMS}}.$

<sup>&</sup>lt;sup>1</sup>ADDRESS LINES FOR ACCESSES ARE: BDMA: A13-0 (14 LSBs), D23-16 (8 MSBs) I/O SPACE: A10-0 EXTERNAL PM AND DM: A13-0

<sup>2</sup>DATA LINES FOR ACCESSES ARE: BDMA: D15-8 I/O SPACE: D23-8 EXTERNAL DM: D23-8 EXTERNAL PM: D23-0

Figure 30. Memory Write

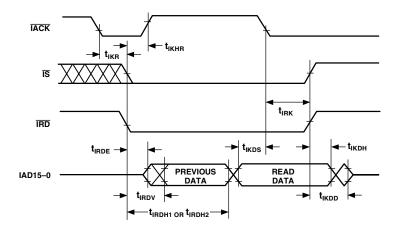

### IDMA Read, Long Read Cycle

Table 24. IDMA Read, Long Read Cycle

| Paramete           | er                                                                   | Min                    | Max | Unit |

|--------------------|----------------------------------------------------------------------|------------------------|-----|------|

| Timing Re          | quirements:                                                          |                        |     |      |

| $t_{\text{IKR}}$   | IACK Low Before Start of Read <sup>1</sup>                           | 0                      |     | ns   |

| t <sub>IRK</sub>   | End of read After IACK Low <sup>2</sup>                              | 2                      |     | ns   |

| Switching          | Characteristics:                                                     |                        |     |      |

| $t_{\text{IKHR}}$  | IACK High After Start of Read <sup>1</sup>                           |                        | 10  | ns   |

| $t_{\text{IKDS}}$  | IAD15-0 Data Setup Before IACK Low                                   | 0.5t <sub>CK</sub> – 3 |     | ns   |

| $t_{\text{IKDH}}$  | IAD15 – 0 Data Hold After End of Read <sup>2</sup>                   | 0                      |     | ns   |

| $t_{\text{IKDD}}$  | IAD15-0 Data Disabled After End of Read <sup>2</sup>                 |                        | 10  | ns   |

| $t_{\text{IRDE}}$  | IAD15-0 Previous Data Enabled After Start of Read                    | 0                      |     | ns   |

| $t_{\text{IRDV}}$  | IAD15-0 Previous Data Valid After Start of Read                      |                        | 11  | ns   |

| t <sub>IRDH1</sub> | IAD15-0 Previous Data Hold After Start of Read (DM/PM1) <sup>3</sup> | 2t <sub>CK</sub> – 5   |     | ns   |

| t <sub>IRDH2</sub> | IAD15-0 Previous Data Hold After Start of Read (PM2) <sup>4</sup>    | t <sub>CK</sub> – 5    |     | ns   |

<sup>&</sup>lt;sup>1</sup> Start of Read =  $\overline{\text{IS}}$  Low and  $\overline{\text{IRD}}$  Low.

$<sup>^4\,\</sup>mathrm{Second}$  half of PM read.

Figure 35. IDMA Read, Long Read Cycle

$<sup>^{2}</sup>$  End of Read =  $\overline{\text{IS}}$  High or  $\overline{\text{IRD}}$  High.

<sup>&</sup>lt;sup>3</sup> DM read or first half of PM read.

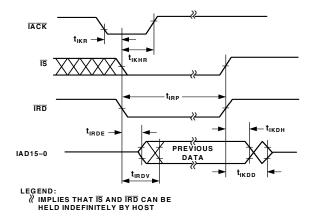

### IDMA Read, Short Read Cycle in Short Read Only Mode

Table 26. IDMA Read, Short Read Cycle in Short Read Only Mode

| Paramete          | er <sup>1</sup>                                               | Min | Max | Unit |

|-------------------|---------------------------------------------------------------|-----|-----|------|

| Timing Re         | quirements:                                                   |     |     |      |

| $t_{IKR}$         | IACK Low Before Start of Read <sup>2</sup>                    | 0   |     | ns   |

| $t_{\text{IRP}}$  | Duration of Read <sup>3</sup>                                 | 10  |     | ns   |

| Switching         | Characteristics:                                              |     |     |      |

| t <sub>IKHR</sub> | IACK High After Start of Read <sup>2</sup>                    |     | 10  | ns   |

| $t_{\text{IKDH}}$ | IAD15-0 Previous Data Hold After End of Read <sup>3</sup>     | 0   |     | ns   |

| $t_{\text{IKDD}}$ | IAD15-0 Previous Data Disabled After End of Read <sup>3</sup> |     | 10  | ns   |

| $t_{\text{IRDE}}$ | IAD15-0 Previous Data Enabled After Start of Read             | 0   |     | ns   |

| $t_{\text{IRDV}}$ | IAD15-0 Previous Data Valid After Start of Read               |     | 10  | ns   |

<sup>&</sup>lt;sup>1</sup> Short Read Only is enabled by setting Bit 14 of the IDMA overlay Register to 1 (0x3FE7). Short Read Only can be enabled by the processor core writing to the register or by an external host writing to the register. Disabled by default.

<sup>&</sup>lt;sup>3</sup> End of Read =  $\overline{IS}$  High or  $\overline{IRD}$  High.

Figure 37. IDMA Read, Short Read Cycle in Short Read Only Mode

<sup>&</sup>lt;sup>2</sup> Start of Read =  $\overline{IS}$  Low and  $\overline{IRD}$  Low. Previous data remains until end of read.

#### **LQFP PACKAGE PINOUT**

The LQFP package pinout is shown Figure 38 and in Table 27. Pin names in bold text in the table replace the plain-text-named functions when Mode C = 1. A + sign separates two functions when either function can be active for either major I/O mode. Signals enclosed in brackets [] are state bits latched from the

value of the pin at the deassertion of  $\overline{RESET}$ . The multiplexed pins DT1/FO, TFS1/ $\overline{IRQ1}$ , RFS1/ $\overline{IRQ0}$ , and DR1/FI, are mode selectable by setting Bit 10 (SPORT1 configure) of the System Control Register. If Bit 10 = 1, these pins have serial port functionality. If Bit 10 = 0, these pins are the external interrupt and flag pins. This bit is set to 1 by default, upon reset.

Figure 38. 100-Lead LQFP Pin Configuration

Table 27. LQFP Package Pinout

Table 27. LQFP Package Pinout (Continued)

| Pin No. | Pin Name           | Pin No.  | Pin Name           |

|---------|--------------------|----------|--------------------|

| 1       | A4/IAD3            | 51       | EBR                |

| 2       | A5/ <b>IAD4</b>    | 52       | BR                 |

| 3       | GND                | 53       | EBG                |

| 4       | A6/ <b>IAD5</b>    | 54       | BG                 |

| 5       | A7/ <b>IAD6</b>    | 55       | D0/IAD13           |

| 6       | A8/ <b>IAD7</b>    | 56       | D1/ <b>IAD14</b>   |

| 7       | A9/ <b>IAD8</b>    | 57       | D2/ <b>IAD15</b>   |

| 8       | A10/ <b>IAD9</b>   | 58       | D3/ <b>IACK</b>    |

| 9       | A11/ <b>IAD10</b>  | 59       | V <sub>DDINT</sub> |

| 10      | A12/ <b>IAD11</b>  | 60       | GND                |

| 11      | A13/ <b>IAD12</b>  | 61       | D4/ <b>IS</b>      |

| 12      | GND                | 62       | D5/IAL             |

|         | CLKIN              | 63       | D6/ <b>IRD</b>     |

| 13      |                    |          |                    |

| 14      | XTAL               | 64       | D7/ <b>IWR</b>     |

| 15      | V <sub>DDEXT</sub> | 65       | D8                 |

| 16      | CLKOUT             | 66       | GND                |

| 17      | GND                | 67       | V <sub>DDEXT</sub> |

| 18      | $V_{\rm DDINT}$    | 68       | D9                 |

| 19      | WR                 | 69       | D10                |

| 20      | RD                 | 70       | D11                |

| 21      | BMS                | 71       | GND                |

| 22      | DMS                | 72       | D12                |

| 23      | PMS                | 73       | D13                |

| 24      | IOMS               | 74       | D14                |

| 25      | CMS                | 75       | D15                |

| 26      | IRQE + PF4         | 76       | D16                |

| 27      | IRQL0 + PF5        | 77       | D17                |

| 28      | GND                | 78       | D18                |

| 29      | IRQL1 + PF6        | 79       | D19                |

| 30      | IRQ2 + PF7         | 80       | GND                |

| 31      | DT0                | 81       | D20                |

| 32      | TFS0               | 82       | D21                |

| 33      | RFS0               | 83       | D22                |

| 34      | DRO                | 84       | D23                |

| 35      | SCLK0              | 85       | FL2                |

| 36      | $V_{\text{DDEXT}}$ | 86       | FL1                |

| 37      | DT1/FO             | 87       | FLO                |

| 38      | TFS1/IRQ1          | 88       | PF3 [Mode D]       |

| 39      | RFS1/IRQ0          | 89       | PF2 [Mode C]       |

| 40      | DR1/FI             | 90       | V <sub>DDEXT</sub> |

| 41      | GND                | 91       | PWD                |

| 42      | SCLK1              | 92       | GND                |

| 43      | ERESET             | 93       | PF1 [Mode B]       |

| 44      | RESET              | 94       | PF0 [Mode A]       |

| 45      | EMS                | 95       | BGH                |

| 46      | EE                 | 96       | PWDACK             |

| 47      | ECLK               | 96<br>97 | A0                 |

|         |                    |          |                    |

| 48      | ELOUT              | 98       | A1/ <b>IAD0</b>    |

| 49      | ELIN               | 99       | A2/ <b>IAD1</b>    |

| 50      | EINT               | 100      | A3/IAD2            |

### **BGA PACKAGE PINOUT**

The BGA package pinout is shown in Figure 39 and in Table 28. Pin names in bold text in the table replace the plain text named functions when Mode C=1. A + sign separates two functions when either function can be active for either major I/O mode. Signals enclosed in brackets [] are state bits latched from the

value of the pin at the deassertion of  $\overline{RESET}$ . The multiplexed pins DT1/FO, TFS1/ $\overline{IRQ1}$ , RFS1/ $\overline{IRQ0}$ , and DR1/FI, are mode selectable by setting Bit 10 (SPORT1 configure) of the System Control Register. If Bit 10 = 1, these pins have serial port functionality. If Bit 10 = 0, these pins are the external interrupt and flag pins. This bit is set to 1 by default upon reset.

| 12                 | 11                 | 10                 | 9       | 8         | 7                  | 6               | 5                  | 4                  | 3           | 2                  | 1                  | _ |

|--------------------|--------------------|--------------------|---------|-----------|--------------------|-----------------|--------------------|--------------------|-------------|--------------------|--------------------|---|

| GND                | GND                | D22                | NC      | NC        | NC                 | GND             | NC                 | Α0                 | GND         | A1/IAD0            | A2/IAD1            | A |

| D16                | D17                | D18                | D20     | D23       | V <sub>DDEXT</sub> | GND             | NC                 | NC                 | GND         | A3/IAD2            | A4/IAD3            | В |

| D14                | NC                 | D15                | D19     | D21       | V <sub>DDEXT</sub> | PWD             | A7/IAD6            | A5/IAD4            | RD          | A6/IAD5            | PWDACK             | С |

| GND                | NC                 | D12                | D13     | NC        | PF2<br>[MODE C]    | PF1<br>[MODE B] | A9/IAD8            | вдн                | NC          | WR                 | NC                 | D |

| D10                | GND                | V <sub>DDEXT</sub> | GND     | GND       | PF3<br>[MODE D]    | FL2             | PF0<br>[MODE A]    | FLO                | A8/IAD7     | V <sub>DDEXT</sub> | V <sub>DDEXT</sub> | E |

| D9                 | NC                 | D8                 | D11     | D7/IWR    | NC                 | NC              | FL1                | A11/IAD10          | A12/IAD11   | NC                 | A13/IAD12          | F |

| D4/ĪS              | NC                 | NC                 | D5/IAL  | D6/ĪRD    | NC                 | NC              | NC                 | A10/IAD9           | GND         | NC                 | XTAL               | G |

| GND                | NC                 | GND                | D3/IACK | D2/IAD15  | TFS0               | DT0             | V <sub>DDINT</sub> | GND                | GND         | GND                | CLKIN              | н |

| V <sub>DDINT</sub> | V <sub>DDINT</sub> | D1/IAD14           | ВG      | RFS1/IRQ0 | D0/IAD13           | SCLK0           | V <sub>DDEXT</sub> | V <sub>DDEXT</sub> | NC          | V <sub>DDINT</sub> | CLKOUT             | J |

| EBG                | BR                 | EBR                | ERESET  | SCLK1     | TFS1/IRQ1          | RFS0            | DMS                | вмѕ                | NC          | NC                 | NC                 | к |

| EINT               | ELOUT              | ELIN               | RESET   | GND       | DR0                | PMS             | GND                | IOMS               | ĪRQL1 + PF6 | NC                 | IRQE + PF4         | L |

| ECLK               | EE                 | EMS                | NC      | GND       | DR1/FI             | DT1/FO          | GND                | смѕ                | NC          | ĪRQ2 + PF7         | IRQL0 + PF5        | М |

Figure 39. 144-Ball BGA Package Pinout (Bottom View)

## **OUTLINE DIMENSIONS**

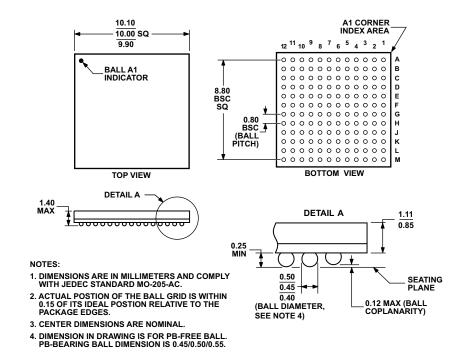

Figure 40. 144-Ball BGA [CSP\_BGA] (BC-144-6)

COMPLIANT TO JEDEC STANDARDS MS-026-BED THE ACTUAL POSITION OF EACH LEAD IS WITHIN 0.08 OF ITS IDEAL POSITION WHEN MEASURED IN THE LATERAL DIRECTION.

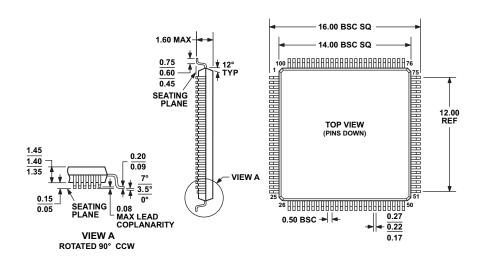

Figure 41. 100-Lead Low Profile Quad Flat Package [LQFP] (ST-100-1)

### **SURFACE MOUNT DESIGN**

Table 29 is provided as an aid to PCB design. For industry-standard design recommendations, refer to IPC-7351, *Generic Requirements for Surface Mount Design and Land Pattern Standard*.

Table 29. BGA Data for Use with Surface Mount Design

| Package      | Ball Attach<br>Type | Solder Mask<br>Opening | Ball Pad Size |

|--------------|---------------------|------------------------|---------------|

| 144-Ball BGA |                     |                        | 0.50 mm       |

| (BC-144-6)   | Defined             | diameter               | diameter      |