# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| 2000                    |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Active                                                                 |

| Туре                    | Fixed Point                                                            |

| Interface               | Host Interface, Serial Port                                            |

| Clock Rate              | 80MHz                                                                  |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 160kB                                                                  |

| Voltage - I/O           | 1.8V, 2.5V, 3.3V                                                       |

| Voltage - Core          | 1.90V                                                                  |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                      |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 100-LQFP                                                               |

| Supplier Device Package | 100-LQFP (14x14)                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-2187nbstz-320 |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 3. | Interrupt | <b>Priority and</b> | Interrupt | Vector Addresses |

|----------|-----------|---------------------|-----------|------------------|

|----------|-----------|---------------------|-----------|------------------|

| Source Of Interrupt               | Interrupt Vector Address<br>(Hex) |

|-----------------------------------|-----------------------------------|

| Reset (or Power-Up with PUCR = 1) | 0x0000 (Highest Priority)         |

| Power-Down (Nonmaskable)          | 0x002C                            |

| IRQ2                              | 0x0004                            |

| IRQL1                             | 0x0008                            |

| IRQLO                             | 0x000C                            |

| SPORT0 Transmit                   | 0x0010                            |

| SPORT0 Receive                    | 0x0014                            |

| IRQE                              | 0x0018                            |

| BDMA Interrupt                    | 0x001C                            |

| SPORT1 Transmit or IRQ1           | 0x0020                            |

| SPORT1 Receive or IRQ0            | 0x0024                            |

| Timer                             | 0x0028 (Lowest Priority)          |

Interrupt routines can either be nested with higher priority interrupts taking precedence or processed sequentially. Interrupts can be masked or unmasked with the IMASK register. Individual interrupt requests are logically ANDed with the bits in IMASK; the highest priority unmasked interrupt is then selected. The power-down interrupt is nonmaskable.

ADSP-218xN series members mask all interrupts for one instruction cycle following the execution of an instruction that modifies the IMASK register. This does not affect serial port autobuffering or DMA transfers.

The interrupt control register, ICNTL, controls interrupt nesting and defines the IRQ0, IRQ1, and IRQ2 external interrupts to be either edge- or level-sensitive. The IRQE pin is an external edge-sensitive interrupt and can be forced and cleared. The IRQL0 and IRQL1 pins are external level sensitive interrupts.

The IFC register is a write-only register used to force and clear interrupts. On-chip stacks preserve the processor status and are automatically maintained during interrupt handling. The stacks are 12 levels deep to allow interrupt, loop, and subroutine nesting. The following instructions allow global enable or disable servicing of the interrupts (including power-down), regardless of the state of IMASK:

ENA INTS;

DIS INTS;

Disabling the interrupts does not affect serial port autobuffering or DMA. When the processor is reset, interrupt servicing is enabled.

#### LOW-POWER OPERATION

ADSP-218xN series members have three low-power modes that significantly reduce the power dissipation when the device operates under standby conditions. These modes are:

- Power-Down

- Idle

- Slow Idle

The CLKOUT pin may also be disabled to reduce external power dissipation.

#### Power-Down

ADSP-218xN series members have a low-power feature that lets the processor enter a very low-power dormant state through hardware or software control. Following is a brief list of powerdown features. Refer to the *ADSP-218x DSP Hardware Reference*, "System Interface" chapter, for detailed information about the power-down feature.

- Quick recovery from power-down. The processor begins executing instructions in as few as 200 CLKIN cycles.

- Support for an externally generated TTL or CMOS processor clock. The external clock can continue running during power-down without affecting the lowest power rating and 200 CLKIN cycle recovery.

- Support for crystal operation includes disabling the oscillator to save power (the processor automatically waits approximately 4096 CLKIN cycles for the crystal oscillator to start or stabilize), and letting the oscillator run to allow 200 CLKIN cycle start-up.

- Power-down is initiated by either the power-down pin (PWD) or the software power-down force bit. Interrupt support allows an unlimited number of instructions to be executed before optionally powering down. The power-down interrupt also can be used as a nonmaskable, edge-sensitive interrupt.

- Context clear/save control allows the processor to continue where it left off or start with a clean context when leaving the power-down state.

- The RESET pin also can be used to terminate power-down.

- Power-down acknowledge pin (PWDACK) indicates when the processor has entered power-down.

#### Idle

When the ADSP-218xN is in the Idle Mode, the processor waits indefinitely in a low-power state until an interrupt occurs. When an unmasked interrupt occurs, it is serviced; execution then continues with the instruction following the IDLE instruction. In Idle mode IDMA, BDMA, and autobuffer cycle steals still occur.

#### Slow Idle

The IDLE instruction is enhanced on ADSP-218xN series members to let the processor's internal clock signal be slowed, further reducing power consumption. The reduced clock frequency, a programmable fraction of the normal clock rate, is specified by a selectable divisor given in the IDLE instruction.

The format of the instruction is:

IDLE (n);

where n = 16, 32, 64, or 128. This instruction keeps the processor fully functional, but operating at the slower clock rate. While it is in this state, the processor's other internal clock signals,

#### **Clock Signals**

ADSP-218xN series members can be clocked by either a crystal or a TTL-compatible clock signal.

The CLKIN input cannot be halted, changed during operation, nor operated below the specified frequency during normal operation. The only exception is while the processor is in the powerdown state. For additional information, refer to the *ADSP-218x DSP Hardware Reference*, for detailed information on this power-down feature.

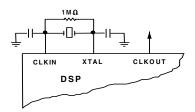

If an external clock is used, it should be a TTL-compatible signal running at half the instruction rate. The signal is connected to the processor's CLKIN input. When an external clock is used, the XTAL pin must be left unconnected.

ADSP-218xN series members use an input clock with a frequency equal to half the instruction rate; a 40 MHz input clock yields a 12.5 ns processor cycle (which is equivalent to 80 MHz). Normally, instructions are executed in a single processor cycle. All device timing is relative to the internal instruction clock rate, which is indicated by the CLKOUT signal when enabled.

Because ADSP-218xN series members include an on-chip oscillator circuit, an external crystal may be used. The crystal should be connected across the CLKIN and XTAL pins, with two capacitors connected as shown in Figure 3. Capacitor values are dependent on crystal type and should be specified by the crystal manufacturer. A parallel-resonant, fundamental frequency, microprocessor-grade crystal should be used. To provide an adequate feedback path around the internal amplifier circuit, place a resistor in parallel with the circuit, as shown in Figure 3.

A clock output (CLKOUT) signal is generated by the processor at the processor's cycle rate. This can be enabled and disabled by the CLKODIS bit in the SPORT0 Autobuffer Control Register.

Figure 3. External Crystal Connections

#### RESET

The RESET signal initiates a master reset of the ADSP-218xN. The RESET signal must be asserted during the power-up sequence to assure proper initialization. RESET during initial power-up must be held long enough to allow the internal clock to stabilize. If RESET is activated any time after power-up, the clock continues to run and does not require stabilization time.

The power-up sequence is defined as the total time required for the crystal oscillator circuit to stabilize after a valid  $V_{\rm DD}$  is applied to the processor, and for the internal phase-locked loop (PLL) to lock onto the specific crystal frequency. A minimum of

2000 CLKIN cycles ensures that the PLL has locked, but does not include the crystal oscillator start-up time. During this power-up sequence the  $\overline{\text{RESET}}$  signal should be held low. On any subsequent resets, the  $\overline{\text{RESET}}$  signal must meet the minimum pulse-width specification ( $t_{RSP}$ ).

The  $\overline{\text{RESET}}$  input contains some hysteresis; however, if an RC circuit is used to generate the  $\overline{\text{RESET}}$  signal, the use of an external Schmitt trigger is recommended.

The master reset sets all internal stack pointers to the empty stack condition, masks all interrupts, and clears the MSTAT register. When  $\overline{\text{RESET}}$  is released, if there is no pending bus request and the chip is configured for booting, the boot-loading sequence is performed. The first instruction is fetched from on-chip program memory location 0x0000 once boot loading completes.

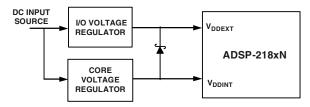

#### **POWER SUPPLIES**

ADSP-218xN series members have separate power supply connections for the internal ( $V_{DDINT}$ ) and external ( $V_{DDEXT}$ ) power supplies. The internal supply must meet the 1.8 V requirement. The external supply can be connected to a 1.8 V, 2.5 V, or 3.3 V supply. All external supply pins must be connected to the same supply. All input and I/O pins can tolerate input voltages up to 3.6 V, regardless of the external supply voltage. This feature provides maximum flexibility in mixing 1.8 V, 2.5 V, or 3.3 V components.

#### MEMORY ARCHITECTURE

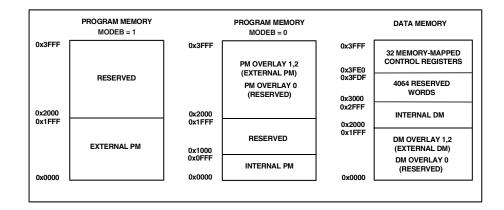

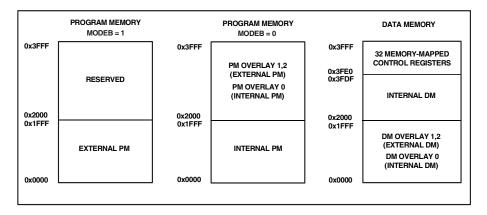

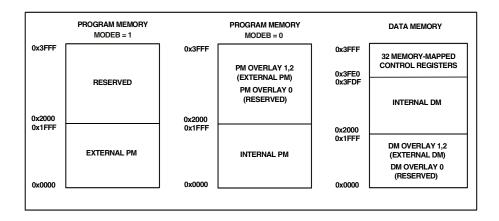

The ADSP-218xN series provides a variety of memory and peripheral interface options. The key functional groups are Program Memory, Data Memory, Byte Memory, and I/O. Refer to Figure 4 through Figure 9, Table 4 on Page 11, and Table 5 on Page 11 for PM and DM memory allocations in the ADSP-218xN series.

Figure 4. ADSP-2184 Memory Architecture

Figure 5. ADSP-2185 Memory Architecture

Figure 6. ADSP-2186 Memory Architecture

Program Memory (Host Mode) allows access to all internal memory. External overlay access is limited by a single external address line (A0). External program execution is not available in host mode due to a restricted data bus that is only 16 bits wide.

#### Table 4. PMOVLAY Bits

| Processor      | PMOVLAY                       | Memory             | A13            | A12-0                                        |

|----------------|-------------------------------|--------------------|----------------|----------------------------------------------|

| ADSP-2184N     | No Internal Overlay<br>Region | Not Applicable     | Not Applicable | Not Applicable                               |

| ADSP-2185N     | 0                             | Internal Overlay   | Not Applicable | Not Applicable                               |

| ADSP-2186N     | No Internal Overlay<br>Region | Not Applicable     | Not Applicable | Not Applicable                               |

| ADSP-2187N     | 0, 4, 5                       | Internal Overlay   | Not Applicable | Not Applicable                               |

| ADSP-2188N     | 0, 4, 5, 6, 7                 | Internal Overlay   | Not Applicable | Not Applicable                               |

| ADSP-2189N     | 0, 4, 5                       | Internal Overlay   | Not Applicable | Not Applicable                               |

| All Processors | 1                             | External Overlay 1 | 0              | 13 LSBs of Address Between 0x2000 and 0x3FFF |

| All Processors | 2                             | External Overlay 2 | 1              | 13 LSBs of Address Between 0x2000 and 0x3FFF |

#### Data Memory

Data Memory (Full Memory Mode) is a 16-bit-wide space used for the storage of data variables and for memory-mapped control registers. The ADSP-218xN series has up to 56K words of Data Memory RAM on-chip. Part of this space is used by 32 memory-mapped registers. Support also exists for up to two 8K external memory overlay spaces through the external data bus. All internal accesses complete in one cycle. Accesses to external memory are timed using the wait states specified by the DWAIT register and the wait state mode bit.

Data Memory (Host Mode) allows access to all internal memory. External overlay access is limited by a single external address line (A0).

#### Table 5. DMOVLAY Bits

| Processor      | DMOVLAY                    | Memory             | A13            | A12-0                                              |

|----------------|----------------------------|--------------------|----------------|----------------------------------------------------|

| ADSP-2184N     | No Internal Overlay Region | Not Applicable     | Not Applicable | Not Applicable                                     |

| ADSP-2185N     | 0                          | Internal Overlay   | Not Applicable | Not Applicable                                     |

| ADSP-2186N     | No Internal Overlay Region | Not Applicable     | Not Applicable | Not Applicable                                     |

| ADSP-2187N     | 0, 4, 5                    | Internal Overlay   | Not Applicable | Not Applicable                                     |

| ADSP-2188N     | 0, 4, 5, 6, 7, 8           | Internal Overlay   | Not Applicable | Not Applicable                                     |

| ADSP-2189N     | 0, 4, 5, 6, 7              | Internal Overlay   | Not Applicable | Not Applicable                                     |

| All Processors | 1                          | External Overlay 1 | 0              | 13 LSBs of Address<br>Between 0x0000 and<br>0x1FFF |

| All Processors | 2                          | External Overlay 2 | 1              | 13 LSBs of Address<br>Between 0x0000 and<br>0x1FFF |

### *Memory-Mapped Registers (New to the ADSP-218xM and N series)*

ADSP-218xN series members have three memory-mapped registers that differ from other ADSP-21xx Family DSPs. The slight modifications to these registers (Wait State Control, Programmable Flag and Composite Select Control, and System Control) provide the ADSP-218xN's wait state and BMS control features. Default bit values at reset are shown; if no value is shown, the bit is undefined at reset. Reserved bits are shown on a grey field. These bits should always be written with zeros.

#### I/O Space (Full Memory Mode)

ADSP-218xN series members support an additional external memory space called I/O space. This space is designed to support simple connections to peripherals (such as data converters and external registers) or to bus interface ASIC data registers. I/O space supports 2048 locations of 16-bit wide data. The lower eleven bits of the external address bus are used; the upper three bits are undefined.

Two instructions were added to the core ADSP-2100 Family instruction set to read from and write to I/O memory space. The I/O space also has four dedicated three-bit wait state registers,

- Fill and dump memory

- Source level debugging

The VisualDSP++ IDE lets programmers define and manage DSP software development. The dialog boxes and property pages let programmers configure and manage all of the ADSP-218xN development tools, including the syntax highlighting in the VisualDSP++ editor. This capability controls how the development tools process inputs and generate outputs.

The ADSP-2189M EZ-KIT Lite<sup>®†</sup> provides developers with a cost-effective method for initial evaluation of the powerful ADSP-218xN DSP family architecture. The ADSP-2189M EZ-KIT Lite includes a stand-alone ADSP-2189M DSP board supported by an evaluation suite of VisualDSP++. With this EZ-KIT Lite, users can learn about DSP hardware and software development and evaluate potential applications of the ADSP-218xN series. The ADSP-2189M EZ-KIT Lite provides an evaluation suite of the VisualDSP++ development environment with the C compiler, assembler, and linker. The size of the DSP executable that can be built using the EZ-KIT Lite tools is limited to 8K words.

The EZ-KIT Lite includes the following features:

- 75 MHz ADSP-2189M

- Full 16-Bit Stereo Audio I/O with AD73322 Codec

- RS-232 Interface

- EZ-ICE Connector for Emulator Control

- DSP Demonstration Programs

- Evaluation Suite of VisualDSP++

The ADSP-218x EZ-ICE<sup>®‡</sup> Emulator provides an easier and more cost-effective method for engineers to develop and optimize DSP systems, shortening product development cycles for faster time-to-market. ADSP-218xN series members integrate on-chip emulation support with a 14-pin ICE-Port interface. This interface provides a simpler target board connection that requires fewer mechanical clearance considerations than other ADSP-2100 Family EZ-ICEs. ADSP-218xN series members need not be removed from the target system when using the EZ-ICE, nor are any adapters needed. Due to the small footprint of the EZ-ICE connector, emulation can be supported in final board designs.The EZ-ICE performs a full range of functions, including:

- In-target operation

- Up to 20 breakpoints

- Single-step or full-speed operation

- Registers and memory values can be examined and altered

- PC upload and download functions

- Instruction-level emulation of program booting and execution

- Complete assembly and disassembly of instructions

- C source-level debugging

#### Designing an EZ-ICE-Compatible System

ADSP-218xN series members have on-chip emulation support and an ICE-Port, a special set of pins that interface to the EZ-ICE. These features allow in-circuit emulation without replacing the target system processor by using only a 14-pin connection from the target system to the EZ-ICE. Target systems must have a 14-pin connector to accept the EZ-ICE's incircuit probe, a 14-pin plug.

**Note:** The EZ-ICE uses the same  $V_{DD}$  voltage as the  $V_{DD}$  voltage used for  $V_{DDEXT}$ . Because the input pins of the ADSP-218xN series members are tolerant to input voltages up to 3.6 V, regardless of the value of  $V_{DDEXT}$ , the voltage setting for the EZ-ICE must not exceed 3.3 V.

Issuing the chip reset command during emulation causes the DSP to perform a full chip reset, including a reset of its memory mode. Therefore, it is vital that the mode pins are set correctly PRIOR to issuing a chip reset command from the emulator user interface. If a passive method of maintaining mode information is being used (as discussed in Setting Memory Mode on Page 5), it does not matter that the mode information is latched by an emulator reset. However, if the RESET pin is being used as a method of setting the value of the mode pins, the effects of an emulator reset must be taken into consideration.

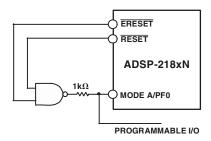

One method of ensuring that the values located on the mode pins are those desired is to construct a circuit like the one shown in Figure 15. This circuit forces the value located on the Mode A pin to logic high, regardless of whether it is latched via the RESET or ERESET pin.

Figure 15. Mode A Pin/EZ-ICE Circuit

The ICE-Port interface consists of the following ADSP-218xN pins: EBR, EINT, EE, EBG, ECLK, ERESET, ELIN, EMS, and ELOUT.

These ADSP-218xN pins must be connected only to the EZ-ICE connector in the target system. These pins have no function except during emulation, and do not require pull-up or pull-down resistors. The traces for these signals between the ADSP-218xN and the connector must be kept as short as possible, no longer than 3 inches.

The following pins are also used by the EZ-ICE:  $\overline{BR}$ ,  $\overline{BG}$ ,  $\overline{RESET}$ , and GND.

$<sup>^{\</sup>dagger}\,\text{EZ-KIT}$  Lite is a registered trademark of Analog Devices, Inc.

<sup>&</sup>lt;sup>‡</sup>EZ-ICE is a registered trademark of Analog Devices, Inc.

Table 9. Common-Mode Pins (Continued)

| Pin Name           | No. of Pins | I/O | Function                                                      |

|--------------------|-------------|-----|---------------------------------------------------------------|

| V <sub>DDINT</sub> | 4           | 1   | Internal V <sub>DD</sub> (1.8 V) Power (BGA)                  |

| V <sub>DDEXT</sub> | 7           | I   | External V <sub>DD</sub> (1.8 V, 2.5 V, or 3.3 V) Power (BGA) |

| GND                | 20          | 1   | Ground (BGA)                                                  |

| EZ-Port            | 9           | I/O | For Emulation Use                                             |

<sup>1</sup> Interrupt/Flag pins retain both functions concurrently. If IMASK is set to enable the corresponding interrupts, the DSP will vector to the appropriate interrupt vector address when the pin is asserted, either by external devices or set as a programmable flag.

<sup>2</sup> SPORT configuration determined by the DSP System Control Register. Software configurable.

#### **MEMORY INTERFACE PINS**

ADSP-218xN series members can be used in one of two modes: Full Memory Mode, which allows BDMA operation with full external overlay memory and I/O capability, or Host Mode, which allows IDMA operation with limited external addressing capabilities. The operating mode is determined by the state of the Mode C pin during RESET and cannot be changed while the processor is running. Table 10 and Table 11 list the active signals at specific pins of the DSP during either of the two operating modes (Full Memory or Host). A signal in one table shares a pin with a signal from the other table, with the active signal determined by the mode that is set. For the shared pins and their alternate signals (e.g., A4/IAD3), refer to the package pinouts in Table 27 on Page 41 and Table 28 on Page 43.

#### Table 10. Full Memory Mode Pins (Mode C = 0)

| Pin Name | No. of Pins | I/O | Function                                                                                               |

|----------|-------------|-----|--------------------------------------------------------------------------------------------------------|

| A13-0    | 14          | 0   | Address Output Pins for Program, Data, Byte, and I/O Spaces                                            |

| D23-0    | 24          | I/O | Data I/O Pins for Program, Data, Byte, and I/O Spaces (8 MSBs are also used as Byte Memory Addresses.) |

| Pin Name | No. of Pins | I/O | Function                                                                 |

|----------|-------------|-----|--------------------------------------------------------------------------|

| IAD15-0  | 16          | I/O | IDMA Port Address/Data Bus                                               |

| A0       | 1           | 0   | Address Pin for External I/O, Program, Data, or Byte Access <sup>1</sup> |

| D23-8    | 16          | I/O | Data I/O Pins for Program, Data, Byte, and I/O Spaces                    |

| IWR      | 1           | 1   | IDMA Write Enable                                                        |

| IRD      | 1           | 1   | IDMA Read Enable                                                         |

| IAL      | 1           | 1   | IDMA Address Latch Pin                                                   |

| ĪS       | 1           | 1   | IDMA Select                                                              |

| IACK     | 1           | 0   | IDMA Port Acknowledge Configurable in Mode D; Open Drain                 |

#### Table 11. Host Mode Pins (Mode C = 1)

<sup>1</sup> In Host Mode, external peripheral addresses can be decoded using the A0, <u>CMS</u>, <u>PMS</u>, <u>DMS</u>, and <u>IOMS</u> signals.

#### **TERMINATING UNUSED PINS**

Table 12 shows the recommendations for terminating unused pins.

| Table 12. Unu | sed Pin Terminations |

|---------------|----------------------|

|---------------|----------------------|

| Pin Name <sup>1</sup> | I/O<br>3-State<br>(Z) <sup>2</sup> | Reset<br>State | Hi-Z <sup>3</sup> Caused By | Unused Configuration |

|-----------------------|------------------------------------|----------------|-----------------------------|----------------------|

| XTAL                  | 0                                  | 0              |                             | Float                |

| CLKOUT                | 0                                  | 0              |                             | Float <sup>4</sup>   |

| A13-1 or              | O (Z)                              | Hi-Z           | BR, EBR                     | Float                |

| IAD12-0               | I/O (Z)                            | Hi-Z           | ĪS                          | Float                |

| A0                    | O (Z)                              | Hi-Z           | BR, EBR                     | Float                |

#### **ESD DIODE PROTECTION**

During the power-up sequence of the DSP, differences in the ramp-up rates and activation time between the two supplies can cause current to flow in the I/O ESD protection circuitry. To prevent damage to the ESD diode protection circuitry, Analog Devices recommends including a bootstrap Schottky diode.

The bootstrap Schottky diode is connected between the core and I/O power supplies, as shown in Figure 17. It protects the ADSP-218xN processor from partially powering the I/O supply. Including a Schottky diode will shorten the delay between the supply ramps and thus prevent damage to the ESD diode protection circuitry. With this technique, if the core rail rises ahead of the I/O rail, the Schottky diode pulls the I/O rail along with the core rail.

Figure 17. Dual Voltage Schottky Diode

#### Table 13. Example Power Dissipation Calculation<sup>1</sup>

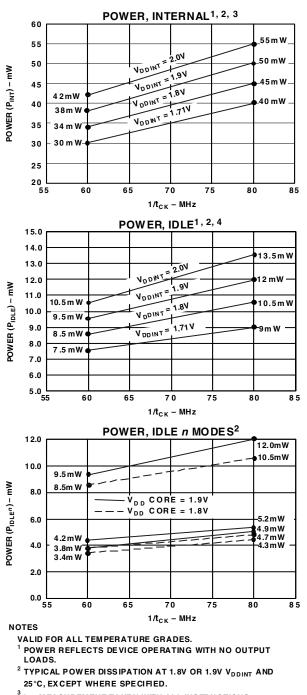

#### **POWER DISSIPATION**

To determine total power dissipation in a specific application, the following equation should be applied for each output:  $C \times V_{DD}^2 \times f$

where:

C =load capacitance.

*f* = output switching frequency.

**Example:** In an application where external data memory is used and no other outputs are active, power dissipation is calculated as follows:

Assumptions:

- External data memory is accessed every cycle with 50% of the address pins switching.

- External data memory writes occur every other cycle with 50% of the data pins switching.

- Each address and data pin has a 10 pF total load at the pin.

- Application operates at  $V_{DDEXT} = 3.3$  V and  $t_{CK} = 30$  ns.

Total Power Dissipation =  $P_{INT} + (C \times V_{DDEXT}^2 \times f)$

$P_{INT}$  = internal power dissipation from Figure 22 on Page 27.

$(C \times V_{DDEXT}^2 \times f)$  is calculated for each output, as in the example in Table 13.

| Parameters      | No. of Pins | ×C(pF) | $\times V_{DDEXT}^{2}(V)$ | $\times f$ (MHz) | PD (mW) |

|-----------------|-------------|--------|---------------------------|------------------|---------|

| Address         | 7           | 10     | 3.3 <sup>2</sup>          | 20.0             | 15.25   |

| Data Output, WR | 9           | 10     | 3.3 <sup>2</sup>          | 20.0             | 19.59   |

| RD              | 1           | 10     | 3.3 <sup>2</sup>          | 20.0             | 2.18    |

| CLKOUT, DMS     | 2           | 10     | 3.3 <sup>2</sup>          | 40.0             | 8.70    |

|                 |             |        |                           |                  | 45.72   |

<sup>1</sup> Total power dissipation for this example is  $P_{INT}$  + 45.72 mW.

#### TIMING SPECIFICATIONS

This section contains timing information for the DSP's external signals.

#### **General Notes**

Use the exact timing information given. Do not attempt to derive parameters from the addition or subtraction of others. While addition or subtraction would yield meaningful results for an individual device, the values given in this data sheet reflect statistical variations and worst cases. Consequently, parameters cannot be added up meaningfully to derive longer times.

#### **Timing Notes**

Switching characteristics specify how the processor changes its signals. Designers have no control over this timing—circuitry external to the processor must be designed for compatibility with these signal characteristics. Switching characteristics tell what the processor will do in a given circumstance. Switching characteristics can also be used to ensure that any timing requirement of a device connected to the processor (such as memory) is satisfied.

Timing requirements apply to signals that are controlled by circuitry external to the processor, such as the data input for a read operation. Timing requirements guarantee that the processor operates correctly with other devices.

#### Frequency Dependency For Timing Specifications

$t_{\rm CK}$  is defined as 0.5  $t_{\rm CKI}.$  The ADSP-218xN uses an input clock with a frequency equal to half the instruction rate. For example, a 40 MHz input clock (which is equivalent to 25 ns) yields a 12.5 ns processor cycle (equivalent to 80 MHz).  $t_{\rm CK}$  values within the range of 0.5  $t_{\rm CKI}$  period should be substituted for all relevant timing parameters to obtain the specification value.

Example:  $t_{CKH} = 0.5 t_{CK} - 2 ns = 0.5 (12.5 ns) - 2 ns = 4.25 ns$

#### **Output Drive Currents**

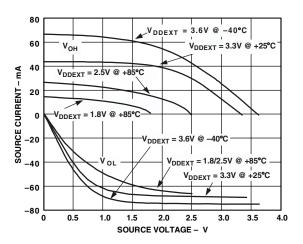

Figure 21 shows typical I-V characteristics for the output drivers on the ADSP-218xN series. The curves represent the current drive capability of the output drivers as a function of output voltage.

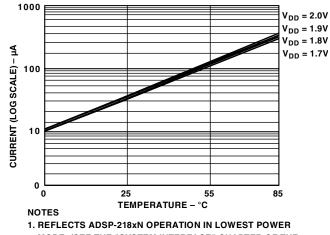

Figure 23 shows the typical power-down supply current.

#### **Capacitive Loading**

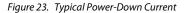

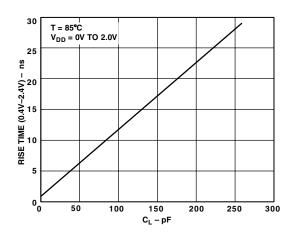

Figure 24 and Figure 25 show the capacitive loading characteristics of the ADSP-218xN.

Figure 21. Typical Output Driver Characteristics for V<sub>DDEXT</sub> at 3.6 V, 3.3 V, 2.5 V, and 1.8 V

- $^3$  I<sub>DD</sub> MEASUREMENT TAKEN WITH ALL INSTRUCTIONS EXECUTING FROM INTERNAL MEMORY. 50% OF THE INSTRUCTIONS ARE MULT IFUNCTION (TYPES 1, 4, 5, 12, 13, 14), 30% ARE TYPE 2 AND TYPE 6, AND 20% ARE IDLE INSTRUCTIONS.

- $^4$  IDLE REFERS TO STATE OF OPERATION DURING EXECUTION OF IDLE INSTRUCTION. DEASSERTED PINS ARE DRIVEN TO EITHER  $V_{\text{DD}}$  OR GND.

Figure 22. Power vs. Frequency

MODE. (SEE THE "SYSTEM INTERFACE" CHAPTER OF THE *ADSP-218x DSP HARDWARE REFERENCE* FOR DETAILS.) 2. CURRENT REFLECTS DEVICE OPERATING WITH NO INPUT LOADS.

Figure 24. Typical Output Rise Time vs. Load Capacitance (at Maximum Ambient Operating Temperature)

Figure 25. Typical Output Valid Delay or Hold vs. Load Capacitance,  $C_L$  (at Maximum Ambient Operating Temperature)

#### **Bus Request–Bus Grant**

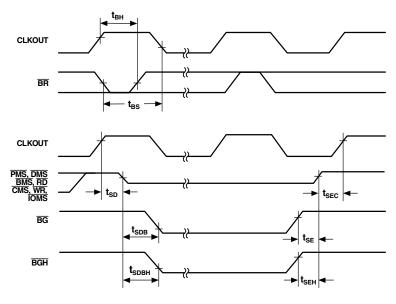

#### Table 17. Bus Request-Bus Grant

| Paramet           | er                                                                                                                            | Min                     | Max                     | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|------|

| Timing Re         | equirements:                                                                                                                  |                         |                         |      |

| t <sub>BH</sub>   | BR Hold after CLKOUT High <sup>1</sup>                                                                                        | 0.25t <sub>CK</sub> + 2 |                         | ns   |

| t <sub>BS</sub>   | BR Setup before CLKOUT Low <sup>1</sup>                                                                                       | 0.25t <sub>CK</sub> + 8 |                         | ns   |

| Switching         | g Characteristics:                                                                                                            |                         |                         |      |

| t <sub>SD</sub>   | CLKOUT High to xMS, RD, WR Disable <sup>2</sup>                                                                               |                         | 0.25t <sub>CK</sub> + 8 | ns   |

| t <sub>SDB</sub>  | xMS, RD, WR Disable to BG Low                                                                                                 | 0                       |                         | ns   |

| t <sub>SE</sub>   | $\overline{BG}$ High to $\overline{xMS}$ , $\overline{RD}$ , $\overline{WR}$ Enable                                           | 0                       |                         | ns   |

| t <sub>SEC</sub>  | xMS, RD, WR Enable to CLKOUT High                                                                                             | 0.25t <sub>CK</sub> – 3 |                         | ns   |

| t <sub>sdbh</sub> | $\overline{\text{xMS}}$ , $\overline{\text{RD}}$ , $\overline{\text{WR}}$ Disable to $\overline{\text{BGH}}$ Low <sup>3</sup> | 0                       |                         | ns   |

| t <sub>SEH</sub>  | $\overline{\text{BGH}}$ High to $\overline{\text{xMS}}$ , $\overline{\text{RD}}$ , $\overline{\text{WR}}$ Enable <sup>3</sup> | 0                       |                         | ns   |

<sup>1</sup> BR is an asynchronous signal. If BR meets the setup/hold requirements, it will be recognized during the current clock cycle; otherwise the signal will be recognized on the following cycle. Refer to the *ADSP-2100 Family User's Manual* for BR/BG cycle relationships.

$^{2}\overline{\text{xMS}} = \overline{\text{PMS}}, \overline{\overline{\text{DMS}}}, \overline{\text{CMS}}, \overline{\text{IOMS}}, \overline{\text{BMS}}.$

${}^{3}\overline{\text{BGH}}$  is asserted when the bus is granted and the processor or BDMA requires control of the bus to continue.

Figure 28. Bus Request-Bus Grant

#### Memory Read

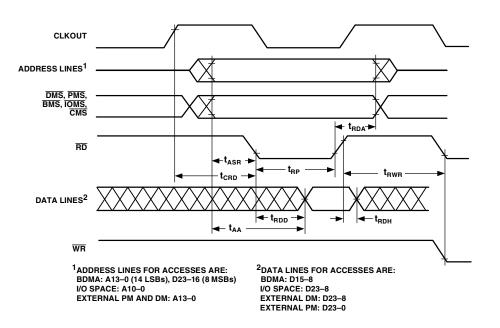

Table 18. Memory Read

| Paramet          | er                                                 | Min                        | Max                         | Unit |

|------------------|----------------------------------------------------|----------------------------|-----------------------------|------|

| Timing Re        | equirements:                                       |                            |                             |      |

| t <sub>RDD</sub> | RD Low to Data Valid <sup>1</sup>                  |                            | $0.5t_{CK} - 5 + w$         | ns   |

| t <sub>AA</sub>  | A13–0, $\overline{xMS}$ to Data Valid <sup>2</sup> |                            | 0.75t <sub>ck</sub> – 6 + w | ns   |

| t <sub>RDH</sub> | Data Hold from RD High                             | 0                          |                             | ns   |

| Switching        | Characteristics:                                   |                            |                             |      |

| t <sub>RP</sub>  | RD Pulse Width                                     | 0.5t <sub>CK</sub> – 3 + w |                             | ns   |

| t <sub>CRD</sub> | CLKOUT High to RD Low                              | 0.25t <sub>CK</sub> – 2    | $0.25t_{CK} + 4$            | ns   |

| t <sub>ASR</sub> | A13–0, xMS Setup before RD Low                     | 0.25t <sub>CK</sub> – 3    |                             | ns   |

| t <sub>RDA</sub> | A13–0, xMS Hold after RD Deasserted                | 0.25t <sub>CK</sub> – 3    |                             | ns   |

| t <sub>RWR</sub> | RD High to RD or WR Low                            | 0.5t <sub>CK</sub> – 3     |                             | ns   |

${}^{1}w$  = wait states 3 t<sub>CK</sub>.  ${}^{2}\overline{\text{xMS}}$  =  $\overline{\text{PMS}}$ ,  $\overline{\text{DMS}}$ ,  $\overline{\text{CMS}}$ ,  $\overline{\text{IOMS}}$ ,  $\overline{\text{BMS}}$ .

Figure 29. Memory Read

#### **Memory Write**

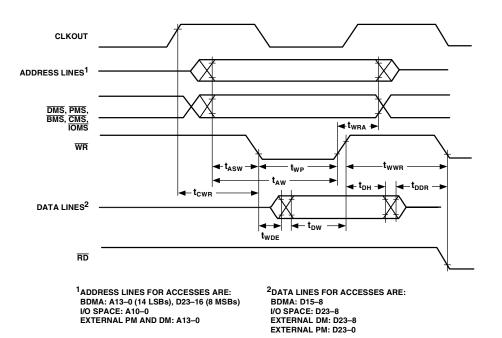

Table 19. Memory Write

| Paramet          | er                                          | Min Max                           | Unit |

|------------------|---------------------------------------------|-----------------------------------|------|

| Switching        | Characteristics:                            |                                   |      |

| t <sub>DW</sub>  | Data Setup before WR High <sup>1</sup>      | $0.5t_{CK} - 4 + w$               | ns   |

| t <sub>DH</sub>  | Data Hold after WR High                     | 0.25t <sub>CK</sub> – 1           | ns   |

| t <sub>WP</sub>  | WR Pulse Width                              | $0.5t_{CK} - 3 + w$               | ns   |

| t <sub>WDE</sub> | WR Low to Data Enabled                      | 0                                 | ns   |

| t <sub>ASW</sub> | A13–0, xMS Setup before WR Low <sup>2</sup> | 0.25t <sub>CK</sub> – 3           | ns   |

| t <sub>DDR</sub> | Data Disable before WR or RD Low            | 0.25t <sub>CK</sub> – 3           | ns   |

| t <sub>CWR</sub> | CLKOUT High to WR Low                       | $0.25t_{CK} - 2$ $0.25t_{CK} + 4$ | ns   |

| t <sub>AW</sub>  | A13–0, xMS Setup before WR Deasserted       | $0.75t_{CK} - 5 + w$              | ns   |

| t <sub>WRA</sub> | A13–0, xMS Hold after WR Deasserted         | 0.25t <sub>CK</sub> – 1           | ns   |

| t <sub>WWR</sub> | WR High to RD or WR Low                     | 0.5t <sub>CK</sub> – 3            | ns   |

$^{1}$  w = wait states 3 t<sub>CK</sub>.

$^{2}\overline{\text{xMS}} = \overline{\text{PMS}}, \overline{\text{DMS}}, \overline{\text{CMS}}, \overline{\text{IOMS}}, \overline{\text{BMS}}.$

Figure 30. Memory Write

#### Serial Ports

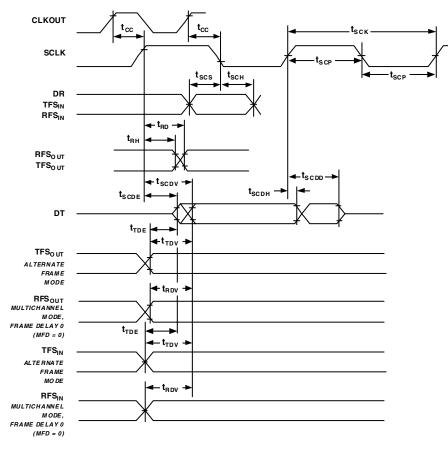

Table 20. Serial Ports

| Paramet           | er                                               | Min                 | Мах                     | Unit |

|-------------------|--------------------------------------------------|---------------------|-------------------------|------|

| Timing Re         | equirements:                                     |                     |                         |      |

| t <sub>SCK</sub>  | SCLK Period                                      | 30                  |                         | ns   |

| t <sub>SCS</sub>  | DR/TFS/RFS Setup Before SCLK Low                 | 4                   |                         | ns   |

| t <sub>SCH</sub>  | DR/TFS/RFS Hold After SCLK Low                   | 7                   |                         | ns   |

| t <sub>SCP</sub>  | SCLKIN Width                                     | 12                  |                         | ns   |

| Switching         | Characteristics:                                 |                     |                         |      |

| t <sub>cc</sub>   | CLKOUT High to SCLKOUT                           | 0.25t <sub>CK</sub> | 0.25t <sub>CK</sub> + 6 | ns   |

| t <sub>SCDE</sub> | SCLK High to DT Enable                           | 0                   |                         | ns   |

| t <sub>SCDV</sub> | SCLK High to DT Valid                            |                     | 7                       | ns   |

| t <sub>RH</sub>   | TFS/RFS <sub>OUT</sub> Hold after SCLK High      | 0                   |                         | ns   |

| t <sub>RD</sub>   | TFS/RFS <sub>OUT</sub> Delay from SCLK High      |                     | 7                       | ns   |

| t <sub>SCDH</sub> | DT Hold after SCLK High                          | 0                   |                         | ns   |

| t <sub>TDE</sub>  | TFS (Alt) to DT Enable                           | 0                   |                         | ns   |

| t <sub>TDV</sub>  | TFS (Alt) to DT Valid                            |                     | 7                       | ns   |

| t <sub>SCDD</sub> | SCLK High to DT Disable                          |                     | 7                       | ns   |

| t <sub>RDV</sub>  | RFS (Multichannel, Frame Delay Zero) to DT Valid |                     | 7                       | ns   |

Figure 31. Serial Ports

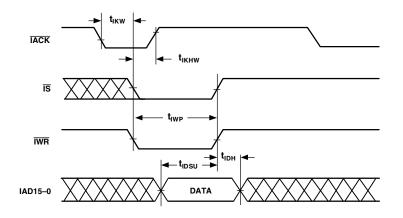

#### IDMA Write, Short Write Cycle

#### Table 22. IDMA Write, Short Write Cycle

| Paramet           | er                                                        | Min | Max | Unit |

|-------------------|-----------------------------------------------------------|-----|-----|------|

| Timing Re         | equirements:                                              |     |     |      |

| t <sub>IKW</sub>  | IACK Low Before Start of Write <sup>1</sup>               | 0   |     | ns   |

| t <sub>IWP</sub>  | Duration of Write <sup>1, 2</sup>                         | 10  |     | ns   |

| t <sub>IDSU</sub> | IAD15-0 Data Setup Before End of Write <sup>2, 3, 4</sup> | 3   |     | ns   |

| t <sub>IDH</sub>  | IAD15-0 Data Hold After End of Write <sup>2, 3, 4</sup>   | 2   |     | ns   |

| Switching         | Characteristic:                                           |     |     |      |

| t <sub>IKHW</sub> | Start of Write to IACK High                               |     | 10  | ns   |

<sup>1</sup> Start of Write =  $\overline{IS}$  Low and  $\overline{IWR}$  Low.

<sup>2</sup> End of Write =  $\overline{IS}$  High or  $\overline{IWR}$  High.

$^3$  If Write Pulse ends before  $\overline{IACK}$  Low, use specifications  $t_{IDSU}, t_{IDH}.$

$^4$  If Write Pulse ends after  $\overline{IACK}$  Low, use specifications  $t_{IKSU},\,t_{IKH}.$

Figure 33. IDMA Write, Short Write Cycle

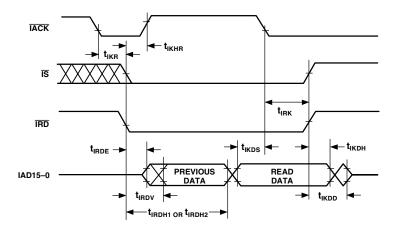

#### IDMA Read, Long Read Cycle

Table 24. IDMA Read, Long Read Cycle

| Paramete           | er                                                                   | Min                    | Max | Unit |

|--------------------|----------------------------------------------------------------------|------------------------|-----|------|

| Timing Re          | quirements:                                                          |                        |     |      |

| t <sub>IKR</sub>   | IACK Low Before Start of Read <sup>1</sup>                           | 0                      |     | ns   |

| t <sub>IRK</sub>   | End of read After IACK Low <sup>2</sup>                              | 2                      |     | ns   |

| Switching          | Characteristics:                                                     |                        |     |      |

| t <sub>IKHR</sub>  | IACK High After Start of Read <sup>1</sup>                           |                        | 10  | ns   |

| t <sub>IKDS</sub>  | IAD15–0 Data Setup Before IACK Low                                   | 0.5t <sub>CK</sub> – 3 |     | ns   |

| t <sub>IKDH</sub>  | IAD15 – 0 Data Hold After End of Read <sup>2</sup>                   | 0                      |     | ns   |

| t <sub>IKDD</sub>  | IAD15-0 Data Disabled After End of Read <sup>2</sup>                 |                        | 10  | ns   |

| t <sub>IRDE</sub>  | IAD15-0 Previous Data Enabled After Start of Read                    | 0                      |     | ns   |

| t <sub>IRDV</sub>  | IAD15-0 Previous Data Valid After Start of Read                      |                        | 11  | ns   |

| t <sub>IRDH1</sub> | IAD15-0 Previous Data Hold After Start of Read (DM/PM1) <sup>3</sup> | 2t <sub>CK</sub> – 5   |     | ns   |

| t <sub>IRDH2</sub> | IAD15–0 Previous Data Hold After Start of Read (PM2) <sup>4</sup>    | t <sub>ск</sub> – 5    |     | ns   |

<sup>1</sup> Start of Read =  $\overline{IS}$  Low and  $\overline{IRD}$  Low.

<sup>2</sup> End of Read =  $\overline{IS}$  High or  $\overline{IRD}$  High.

<sup>3</sup>DM read or first half of PM read.

<sup>4</sup> Second half of PM read.

Figure 35. IDMA Read, Long Read Cycle

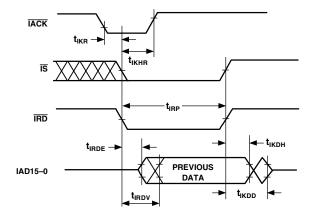

#### IDMA Read, Short Read Cycle

#### Table 25. IDMA Read, Short Read Cycle

| Parameter         | 1,2                                                  | Min | Мах                  | Unit |

|-------------------|------------------------------------------------------|-----|----------------------|------|

| Timing Req        | uirements:                                           |     |                      |      |

| t <sub>IKR</sub>  | IACK Low Before Start of Read <sup>3</sup>           | 0   |                      | ns   |

| t <sub>IRP1</sub> | Duration of Read (DM/PM1) <sup>4</sup>               | 10  | 2t <sub>CK</sub> – 5 | ns   |

| t <sub>IRP2</sub> | Duration of Read (PM2) <sup>5</sup>                  | 10  | t <sub>CK</sub> – 5  | ns   |

| Switching C       | haracteristics:                                      |     |                      |      |

| t <sub>IKHR</sub> | IACK High After Start of Read <sup>3</sup>           |     | 10                   | ns   |

| t <sub>IKDH</sub> | IAD15–0 Data Hold After End of Read <sup>6</sup>     | 0   |                      | ns   |

| t <sub>IKDD</sub> | IAD15-0 Data Disabled After End of Read <sup>6</sup> |     | 10                   | ns   |

| t <sub>IRDE</sub> | IAD15-0 Previous Data Enabled After Start of Read    | 0   |                      | ns   |

| t <sub>IRDV</sub> | IAD15-0 Previous Data Valid After Start of Read      |     | 10                   | ns   |

<sup>1</sup> Short Read Only must be disabled in the IDMA overlay memory mapped register. This mode is disabled by clearing (=0) Bit 14 of the IDMA overlay register, and is disabled by default upon reset.

<sup>2</sup> Consider using the Short Read Only mode, instead, because Short Read mode is not applicable at high clock frequencies.

<sup>3</sup> Start of Read =  $\overline{IS}$  Low and  $\overline{IRD}$  Low.

<sup>4</sup> DM Read or first half of PM Read.

<sup>5</sup> Second half of PM Read.

<sup>6</sup> End of Read =  $\overline{IS}$  High or  $\overline{IRD}$  High.

Figure 36. IDMA Read, Short Read Cycle

#### Table 27. LQFP Package Pinout

Table 27. LQFP Package Pinout (Continued)

| Pin Name          | Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A4/IAD3           | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EBR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A5/ <b>IAD4</b>   | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EBG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A6/ <b>IAD5</b>   | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A7/ <b>IAD6</b>   | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D0/ <b>IAD13</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A8/ <b>IAD7</b>   | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D1/ <b>IAD14</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D2/ <b>IAD15</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A10/ <b>IAD9</b>  | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D3/IACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A11/ <b>IAD10</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DDINT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D4/ <b>IS</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D5/ <b>IAL</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D6/ <b>IRD</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D7/ <b>IWR</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>DDEXT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |