#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT        |

| Number of I/O              | 109                                                                      |

| Program Memory Size        | 384KB (384K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 12K x 8                                                                  |

| RAM Size                   | 48K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                             |

| Data Converters            | A/D 40x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 132-UFBGA                                                                |

| Supplier Device Package    | 132-UFBGA (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l162qdh6dtr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3 Functional overview

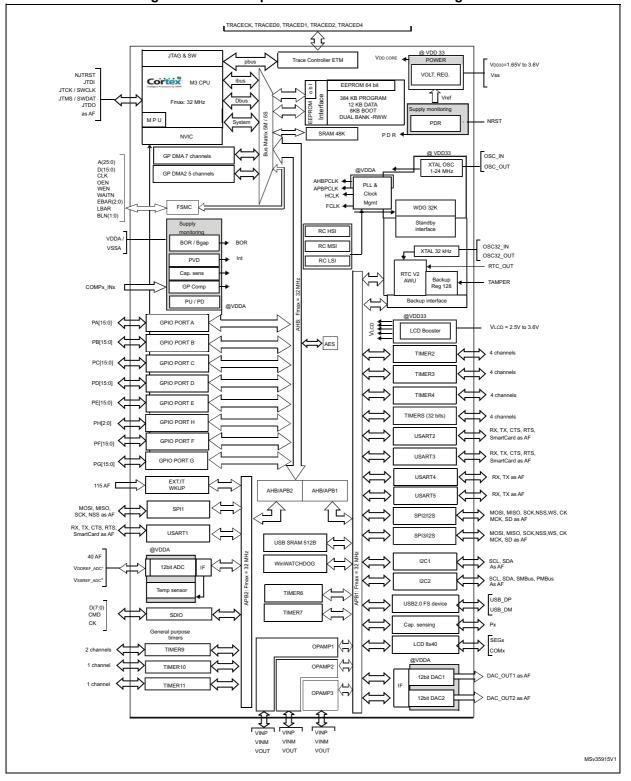

#### Figure 1. Ultra-low-power STM32L162xD block diagram

The DMA can be used with the main peripherals: AES, SPI, I<sup>2</sup>C, USART, SDIO, generalpurpose timers, DAC and ADC.

## 3.10 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

### 3.11 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L162xD devices with up to 40 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs with up to 28 external channels in a group.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low-power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

#### 3.11.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies

|         | F        | Pins    |        |         |                                  |                     |                            | _162XD pin a                                     | Pin functio                              | ns                                         |

|---------|----------|---------|--------|---------|----------------------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------------|--------------------------------------------|

| LQFP144 | UFBGA132 | LQFP100 | LQFP64 | WLCSP64 | Pin name                         | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Alternate functions                      | Additional<br>functions                    |

| 1       | B2       | 1       | -      | -       | PE2                              | I/O                 | FT                         | PE2                                              | TIM3_ETR/LCD_SEG38/<br>FSMC_A23/TRACECLK | -                                          |

| 2       | A1       | 2       | -      | -       | PE3                              | I/O                 | FT                         | PE3                                              | TIM3_CH1/LCD_SEG39/<br>FSMC_A19/TRACED0  | -                                          |

| 3       | B1       | 3       | -      | -       | PE4                              | I/O                 | FT                         | PE4                                              | TIM3_CH2/FSMC_A20/<br>TRACED1            | -                                          |

| 4       | C2       | 4       | -      | -       | PE5                              | I/O                 | FT                         | PE5                                              | TIM9_CH1/TRACED2<br>/FSMC_A21            | -                                          |

| 5       | D2       | 5       | -      | -       | PE6-<br>WKUP3                    | I/O                 | FT                         | PE6                                              | TIM9_CH2/TRACED3                         | WKUP3/<br>RTC_TAMP3                        |

| 6       | E2       | 6       | 1      | C6      | V <sub>LCD</sub>                 | S                   | -                          | $V_{LCD}$                                        | -                                        | -                                          |

| 7       | C1       | 7       | 2      | C8      | PC13-WKUP2                       | I/O                 | FT                         | PC13                                             | -                                        | WKUP2/<br>RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT |

| 8       | D1       | 8       | 3      | B8      | PC14-<br>OSC32_IN <sup>(4)</sup> | I/O                 | -                          | PC14                                             | -                                        | OSC32_IN                                   |

| 9       | E1       | 9       | 4      | B7      | PC15-<br>OSC32_OUT               | I/O                 | -                          | PC15                                             | -                                        | OSC32_OUT                                  |

| 10      | D6       | -       | -      | -       | PF0                              | I/O                 | FT                         | PF0                                              | FSMC_A0                                  | -                                          |

| 11      | D5       | -       | -      | -       | PF1                              | I/O                 | FT                         | PF1                                              | FSMC_A1                                  | -                                          |

| 12      | D4       | -       | -      | -       | PF2                              | I/O                 | FT                         | PF2                                              | FSMC_A2                                  | -                                          |

| 13      | E4       | -       | -      | -       | PF3                              | I/O                 | FT                         | PF3                                              | FSMC_A3                                  | _                                          |

| 14      | F3       | -       | -      | -       | PF4                              | I/O                 | FT                         | PF4                                              | FSMC_A4                                  | -                                          |

| 15      | F4       | -       | -      | -       | PF5                              | I/O                 | FT                         | PF5                                              | FSMC_A5                                  | -                                          |

| 16      | F2       | 10      | -      | -       | V <sub>SS_5</sub>                | s                   | -                          | $V_{SS_5}$                                       | -                                        | -                                          |

| 17      | G2       | 11      | -      | -       | $V_{DD_5}$                       | S                   | -                          | $V_{DD_5}$                                       | -                                        | -                                          |

| 18      | G3       | -       | -      | -       | PF6                              | I/O                 | FT                         | PF6                                              | TIM5_CH1/TIM5_ETR                        | ADC_IN27                                   |

| 19      | G4       | -       | -      | -       | PF7                              | I/O                 | FT                         | PF7                                              | TIM5_CH2                                 | ADC_IN28/<br>COMP1_INP                     |

Table 7. STM32L162xD pin definitions

|         | F        | Pins    |        |         |                    |                     |               |                    | Pin functio                                                         | ns                      |

|---------|----------|---------|--------|---------|--------------------|---------------------|---------------|--------------------|---------------------------------------------------------------------|-------------------------|

| LQFP144 | UFBGA132 | LQFP100 | LQFP64 | WLCSP64 | Pin name           | Type <sup>(1)</sup> | (after reset) |                    | Alternate functions                                                 | Additional<br>functions |

| 116     | C8       | 83      | 54     | A3      | PD2                | I/O                 | FT            | PD2                | TIM3_ETR/UART5_RX/<br>LCD_SEG31/<br>LCD_SEG43/LCD_COM7<br>/SDIO_CMD | -                       |

| 117     | B8       | 84      | -      | -       | PD3                | I/O                 | FT            | PD3                | SPI2_MISO/<br>USART2_CTS<br>/FSMC_CLK                               | -                       |

| 118     | B7       | 85      | -      | -       | PD4                | I/O                 | FT            | PD4                | SPI2_MOSI/I2S2_SD/<br>USART2_RTS<br>/FSMC_NOE                       | -                       |

| 119     | A6       | 86      | -      | -       | PD5                | I/O                 | FT            | PD5                | USART2_TX<br>/FSMC_NWE                                              | -                       |

| 120     | F7       | -       | -      | -       | V <sub>SS_10</sub> | S                   | -             | V <sub>SS_10</sub> | -                                                                   | -                       |

| 121     | G7       | -       | -      | -       | V <sub>DD_10</sub> | S                   | -             | V <sub>DD_10</sub> | -                                                                   | -                       |

| 122     | B6       | 87      | -      | -       | PD6                | I/O                 | FT            | PD6                | USART2_RX<br>/FSMC_NWAIT                                            | -                       |

| 123     | A5       | 88      | -      | -       | PD7                | I/O                 | FT            | PD7                | TIM9_CH2/USART2_CK/<br>FSMC_NE1                                     | -                       |

| 124     | D9       | -       | -      | -       | PG9                | I/O                 | FT            | PG9                | FSMC_NE2                                                            | -                       |

| 125     | D8       | -       | -      | -       | PG10               | I/O                 | FT            | PG10               | FSMC_NE3                                                            | -                       |

| 126     | -        | -       | -      | -       | PG11               | I/O                 | FT            | PG11               | -                                                                   | -                       |

| 127     | D7       | -       | -      | -       | PG12               | I/O                 | FT            | PG12               | FSMC_NE4                                                            | -                       |

| 128     | C7       | _       | -      | -       | PG13               | I/O                 | FT            | PG13               | FSMC_A24                                                            | -                       |

| 129     | C6       | -       | -      | -       | PG14               | I/O                 | FT            | PG14               | FSMC_A25                                                            | -                       |

| 130     | -        | -       | -      | -       | V <sub>SS_11</sub> | S                   | -             | V <sub>SS_11</sub> | -                                                                   | -                       |

| 131     | -        | -       | -      | -       | V <sub>DD_11</sub> | S                   | -             | V <sub>DD_11</sub> | -                                                                   | -                       |

| 132     | -        | -       | -      | -       | PG15               | I/O                 | FT            | PG15               | -                                                                   | -                       |

| 133     | A8       | 89      | 55     | A4      | PB3                | I/O                 | FT            | JTDO               | TIM2_CH2/SPI1_SCK/<br>SPI3_SCK/ I2S3_CK/<br>LCD_SEG7/JTDO           | COMP2_INM               |

| 134     | A7       | 90      | 56     | В4      | PB4                | I/O                 | FT            | NJTRST             | TIM3_CH1/SPI1_MISO/<br>SPI3_MISO/<br>LCD_SEG8/NJTRST                | COMP2_INP               |

#### Table 7. STM32L162xD pin definitions (continued)

#### Alternate functions

|           | 1      |                                   |          | Tabl           |        |           |                     | put/output |         |          |               |          |              |

|-----------|--------|-----------------------------------|----------|----------------|--------|-----------|---------------------|------------|---------|----------|---------------|----------|--------------|

|           |        | Digital alternate function number |          |                |        |           |                     |            |         |          |               |          |              |

|           | AFIO0  | AFIO1                             | AFIO2    | AFIO3          | AFIO4  | AFIO5     | AFIO6               | AFIO7      | AFIO8   | . AFIO11 | AFIO12        | AFIO14   | AFIO15       |

| Port name |        | Alternate function                |          |                |        |           |                     |            |         |          |               |          |              |

|           | SYSTEM | TIM2                              | TIM3/4/5 | TIM9/<br>10/11 | I2C1/2 | SPI1/2    | SPI3                | USART1/2/3 | UART4/5 | LCD      | FSMC/<br>SDIO | CPRI     | SYSTEM       |

| BOOT0     | BOOT0  | -                                 | -        | -              | -      | -         | -                   | -          | -       | -        | -             | -        | EVENT<br>OUT |

| NRST      | NRST   | -                                 | -        | -              | -      | -         | -                   | -          | -       | -        | -             | -        | -            |

| PA0-WKUP1 | -      | TIM2_CH1_ETR                      | TIM5_CH1 | -              | -      | -         | -                   | USART2_CTS | -       | -        | -             | TIMx_IC1 | EVENT<br>OUT |

| PA1       | -      | TIM2_CH2                          | TIM5_CH2 | -              | -      | -         | -                   | USART2_RTS | -       | SEG0     | -             | TIMx_IC2 | EVENT<br>OUT |

| PA2       | -      | TIM2_CH3                          | TIM5_CH3 | TIM9_CH1       | -      | -         | -                   | USART2_TX  | -       | SEG1     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA3       | -      | TIM2_CH4                          | TIM5_CH4 | TIM9_CH2       | -      | -         | -                   | USART2_RX  | -       | SEG2     | -             | TIMx_IC4 | EVENT<br>OUT |

| PA4       | -      | -                                 | -        | -              | -      | SPI1_NSS  | SPI3_NSS<br>I2S3_WS | USART2_CK  | -       | -        | -             | TIMx_IC1 | EVENT<br>OUT |

| PA5       | -      | TIM2_CH1_ETR                      | -        | -              | -      | SPI1_SCK  | -                   | -          | -       | -        | -             | TIMx_IC2 | EVENT<br>OUT |

| PA6       | -      | -                                 | TIM3_CH1 | TIM10_CH1      | -      | SPI1_MISO | -                   | -          | -       | SEG3     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA7       | -      | -                                 | TIM3_CH2 | TIM11_CH1      | -      | SPI1_MOSI | -                   | -          | -       | SEG4     | -             | TIMx_IC4 | EVENT<br>OUT |

| PA8       | мсо    | -                                 | -        | -              | -      | -         | -                   | USART1_CK  | -       | СОМ0     | -             | TIMx_IC1 | EVENT<br>OUT |

| PA9       | -      | -                                 | -        | -              | -      | -         | -                   | USART1_TX  | -       | COM1     | -             | TIMx_IC2 | EVENT<br>OUT |

| PA10      | -      | -                                 | -        | -              | -      | -         | -                   | USART1_RX  | -       | COM2     | -             | TIMx_IC3 | EVENT<br>OUT |

| PA11      | -      | -                                 | -        | -              | -      | SPI1_MISO |                     | USART1_CTS | -       | -        | -             | TIMx_IC4 | EVENT<br>OUT |

# 50/154

| Symbol | Parameter                  | Conditions       | Min | Max | Unit |  |

|--------|----------------------------|------------------|-----|-----|------|--|

| TJ     | lunction tomporature range | 6 suffix version | -40 | 105 | °C   |  |

|        | Junction temperature range | 7 suffix version | -40 | 110 |      |  |

#### Table 12. General operating conditions (continued)

1. When the ADC is used, refer to Table 63: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and operation.

3. To sustain a voltage higher than VDD+0.3V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 79: Thermal characteristics on page 146).

In low-power dissipation state, T<sub>A</sub> can be extended to -40°C to 105°C temperature range as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see *Table 79: Thermal characteristics on page 146*).

#### 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the conditions summarized in *Table 12*.

| Symbol                               | Parameter                      | Conditions                                   | Min  | Тур  | Max                                                    | Unit  |  |

|--------------------------------------|--------------------------------|----------------------------------------------|------|------|--------------------------------------------------------|-------|--|

|                                      | V <sub>DD</sub> rise time rate | BOR detector enabled                         | 0    | -    | ∞                                                      |       |  |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                | BOR detector disabled                        | 0    | -    | 1000                                                   | μs/V  |  |

|                                      | V fall time rate               | BOR detector enabled                         | 20   | -    | ∞                                                      | μ5/ ν |  |

|                                      | V <sub>DD</sub> fall time rate | BOR detector disabled                        | 0    | -    | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |       |  |

| т. (1)                               | Poset temporization            | V <sub>DD</sub> rising, BOR enabled          | -    | 2    | 3.3                                                    | me    |  |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            | $V_{DD}$ rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6                                                    | ms    |  |

| N                                    | Power on/power down reset      | Falling edge                                 | 1    | 1.5  | 1.65                                                   |       |  |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                  | 1.3  | 1.5  | 1.65                                                   |       |  |

| V                                    | Brown-out reset threshold 0    | Falling edge                                 | 1.67 | 1.7  | 1.74                                                   |       |  |

| V <sub>BOR0</sub>                    | Brown-out reset threshold 0    | Rising edge                                  | 1.69 | 1.76 | 1.8                                                    | V     |  |

| N/ -                                 | Brown-out reset threshold 1    | Falling edge                                 | 1.87 | 1.93 | 1.97                                                   | v     |  |

| V <sub>BOR1</sub>                    | brown-out reset threshold 1    | Rising edge                                  | 1.96 | 2.03 | 2.07                                                   |       |  |

| V                                    | Brown-out reset threshold 2    | Falling edge                                 | 2.22 | 2.30 | 2.35                                                   | 1     |  |

| V <sub>BOR2</sub>                    |                                | Rising edge                                  | 2.31 | 2.41 | 2.44                                                   |       |  |

Table 13. Embedded reset and power control block characteristics

#### 6.3.3 Embedded internal reference voltage

The parameters given in *Table 15* are based on characterization results, unless otherwise specified.

| Table 14. Embedded internal reference voltage calibration values |                                                                                     |                           |  |  |  |  |  |  |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|--|

| Calibration value name                                           | Description                                                                         | Memory address            |  |  |  |  |  |  |

| VREFINT_CAL                                                      | Raw data acquired at<br>temperature of 30 °C ±5 °C<br>V <sub>DDA</sub> = 3 V ±10 mV | 0x1FF8 00F8 - 0x1FF8 00F9 |  |  |  |  |  |  |

| Symbol                                  | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Мах   | Unit               |

|-----------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------------------|

| V <sub>REFINT out</sub> <sup>(1)</sup>  | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +110 °C                                                      | 1.202 | 1.224 | 1.242 | V                  |

| I <sub>REFINT</sub>                     | Internal reference current consumption                                                       | -                                                                                       | -     | 1.4   | 2.3   | μA                 |

| T <sub>VREFINT</sub>                    | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms                 |

| V <sub>VREF_MEAS</sub>                  | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V                  |

| A <sub>VREF_MEAS</sub>                  | Accuracy of factory-measured V <sub>REF</sub> value <sup>(2)</sup>                           | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV                 |

| T <sub>Coeff</sub> <sup>(3)</sup>       | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +110 °C                                                       | -     | 25    | 100   | ppm/°<br>C         |

| A <sub>Coeff</sub> <sup>(3)</sup>       | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm                |

| V <sub>DDCoeff</sub> <sup>(3)</sup>     | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V              |

| T <sub>S_vrefint</sub> <sup>(3)</sup>   | ADC sampling time when reading the internal reference voltage                                | -                                                                                       | 4     | -     | -     | μs                 |

| T <sub>ADC_BUF</sub> <sup>(3) (4)</sup> | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs                 |

| I <sub>BUF_ADC</sub> <sup>(3)</sup>     | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA                 |

| I <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output current <sup>(5)</sup>                                                       | -                                                                                       | -     | -     | 1     | μA                 |

| C <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF                 |

| I <sub>LPBUF</sub> <sup>(3)</sup>       | Consumption of reference voltage buffer for VREF_OUT and COMP                                | -                                                                                       | -     | 730   | 1200  | nA                 |

| V <sub>REFINT_DIV1</sub> <sup>(3)</sup> | 1/4 reference voltage                                                                        | -                                                                                       | 24    | 25    | 26    | %                  |

| V <sub>REFINT_DIV2</sub> <sup>(3)</sup> | 1/2 reference voltage                                                                        | -                                                                                       | 49    | 50    | 51    | V <sub>REFIN</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(3)</sup> | 3/4 reference voltage                                                                        | -                                                                                       | 74    | 75    | 76    | Т                  |

#### Table 15. Embedded internal reference voltage

1. Guaranteed by test in production.

2. The internal  $V_{REF}$  value is individually measured in production and stored in dedicated EEPROM bytes.

3. Guaranteed by characterization results.

4. Shortest sampling time can be determined in the application by multiple iterations.

| Symbol                                  | Parameter                                                 | Condit                                                                               | tions                                                       | Тур             | Max <sup>(1)</sup> | Unit |

|-----------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------|--------------------|------|

|                                         |                                                           |                                                                                      | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 0.82            | -                  |      |

|                                         |                                                           | RTC clocked by LSI (no                                                               | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 1.15            | 1.9                |      |

|                                         |                                                           | independent watchdog)                                                                | T <sub>A</sub> = 55 °C                                      | 1.15            | 2.2                |      |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 85 °C                                      | 1.65            | 4                  |      |

| (Standby                                | Supply current in                                         |                                                                                      | T <sub>A</sub> = 105 °C                                     | 2.75            | 8.3 <sup>(2)</sup> |      |

|                                         | -                                                         | RTC clocked by LSE<br>external quartz (no<br>independent<br>watchdog) <sup>(3)</sup> | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 1.05            | -                  |      |

|                                         |                                                           |                                                                                      | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 1.35            | -                  | μA   |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 55 °C                                      | 1.55            | -                  |      |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 85 °C                                      | 2.1             | -                  |      |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 105 °C                                     | 3.3             | -                  |      |

|                                         |                                                           | Independent watchdog and LSI enabled                                                 | $T_A = -40 \text{ °C to } 25 \text{ °C}$                    | 1               | 1.7                |      |

| I <sub>DD</sub>                         | Supply current in                                         |                                                                                      | $T_A$ = -40 °C to 25 °C                                     | 0.305           | 0.6                |      |

| (Standby)                               | Standby mode (RTC disabled)                               | Independent watchdog                                                                 | T <sub>A</sub> = 55 °C                                      | 0.365           | 0.9                |      |

|                                         |                                                           | and LSI OFF                                                                          | T <sub>A</sub> = 85 °C                                      | 0.66            | 2.75               |      |

|                                         |                                                           |                                                                                      | T <sub>A</sub> = 105 °C                                     | 85 °C 0.66 2.75 |                    |      |

| I <sub>DD</sub><br>(WU from<br>Standby) | Supply current during<br>wakeup time from<br>Standby mode | -                                                                                    | $T_A = -40 \ ^\circ C \text{ to } 25 \ ^\circ C$            | 1               | -                  | mA   |

| Table 22. Typical and maximum curren | t consumptions in Standby mode |

|--------------------------------------|--------------------------------|

|--------------------------------------|--------------------------------|

1. Guaranteed by characterization results, unless otherwise specified.

2. Guaranteed by test in production.

3. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in the following table. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

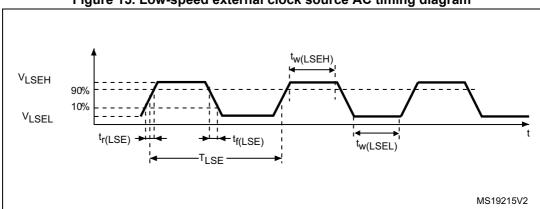

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a low-speed external clock source, and under the conditions summarized in *Table 12*.

| Symbol                                       | Parameter                               | Conditions | Min                | Тур    | Max                | Unit |

|----------------------------------------------|-----------------------------------------|------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source<br>frequency |            | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage   |            | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage    | -          | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time               |            | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time              |            | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                         | OSC32_IN input capacitance              | -          | -                  | 0.6    | -                  | pF   |

Table 26. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

Figure 15. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 27*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

#### 6.3.7 Internal clock source characteristics

The parameters given in *Table 29* are derived from tests performed under the conditions summarized in *Table 12*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                                               | Conditions                                              | Min               | Тур  | Max              | Unit |

|-------------------------------------|---------------------------------------------------------|---------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI</sub>                    | Frequency                                               | V <sub>DD</sub> = 3.0 V                                 | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>              | HSI user-trimmed                                        | Trimming code is not a multiple of 16                   | -                 | ±0.4 | 0.7              | %    |

| TRIM                                | resolution                                              | Trimming code is a multiple of 16                       | -                 | -    | -                | %    |

|                                     |                                                         | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C        | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

| ACC <sub>HSI</sub> <sup>(2)</sup>   | Accuracy of the<br>factory-calibrated<br>HSI oscillator | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 0 to 55 °C   | -1.5              | -    | 1.5              | %    |

|                                     |                                                         | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                 | -2                | -    | 2                | %    |

|                                     |                                                         | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 85 °C | -2.5              | -    | 2                | %    |

|                                     |                                                         | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                | -4                | -    | 2                | %    |

| HSI oscillator                      | -4                                                      | -                                                       | 3                 | %    |                  |      |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time                          | -                                                       | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption                     | -                                                       | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

#### Low-speed internal (LSI) RC oscillator

#### Table 30. LSI oscillator characteristics

| Symbol                              | Parameter                                                                | Min | Тур | Max | Unit |

|-------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                            | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \leq T_{A} \leq 105^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                              | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                         | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

#### 6.3.8 PLL characteristics

The parameters given in *Table 32* are derived from tests performed under the conditions summarized in *Table 12*.

| Symbol                 | Parameter                                               |     | Unit |                    |      |

|------------------------|---------------------------------------------------------|-----|------|--------------------|------|

| Cymbol                 |                                                         | Min | Тур  | Max <sup>(1)</sup> | Unit |

| f                      | PLL input clock <sup>(2)</sup>                          | 2   | -    | 24                 | MHz  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle                              | 45  | -    | 55                 | %    |

| f <sub>PLL_OUT</sub>   | PLL output clock                                        | 2   | -    | 32                 | MHz  |

| t <sub>LOCK</sub>      | PLL lock time<br>PLL input = 16 MHz<br>PLL VCO = 96 MHz | -   | 115  | 160                | μs   |

| Jitter                 | Cycle-to-cycle jitter                                   | -   | -    | ±600               | ps   |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub>                 | -   | 220  | 450                |      |

| I <sub>DD</sub> (PLL)  | Current consumption on $V_{DD}$                         | -   | 120  | 150                | μA   |

| Table 32. PLL characteristics | Table 32. PLL cha | aracteristics |

|-------------------------------|-------------------|---------------|

|-------------------------------|-------------------|---------------|

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

#### 6.3.9 Memory characteristics

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

#### **RAM** memory

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

#### Flash memory and data EEPROM

| Symbol            | Parameter                                                                      | Conditions                                      | Min    | Conditions Min Typ Max <sup>(1)</sup> |        |      |  |  |  |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|--------|---------------------------------------|--------|------|--|--|--|

| Symbol            | Parameter                                                                      | Conditions                                      | IVIIII | Тур                                   | Widx ' | Unit |  |  |  |

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65   | -                                     | 3.6    | V    |  |  |  |

|                   | Programming/ erasing                                                           | Erasing                                         | -      | 3.28                                  | 3.94   |      |  |  |  |

| t <sub>prog</sub> | time for byte / word /<br>double word / half-page                              | Programming                                     | -      | 3.28                                  | 3.94   | ms   |  |  |  |

|                   | Average current during<br>the whole programming /<br>erase operation           |                                                 | -      | 600                                   | 900    | μA   |  |  |  |

| I <sub>DD</sub>   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -      | 1.5                                   | 2.5    | mA   |  |  |  |

Table 34. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Cumhal                          | Parameter                                                                                                | O and little and                    | Value              |     |     | Unit    |

|---------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|-----|-----|---------|

| Symbol                          |                                                                                                          | Conditions                          | Min <sup>(1)</sup> | Тур | Max | Onit    |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>Program memory                                                                | T <sub>A</sub> = -40°C to<br>105 °C | 10                 | -   | -   | kovelos |

|                                 | Cycling (erase / write)<br>EEPROM data memory                                                            |                                     | 300                | -   | -   | kcycles |

|                                 | Data retention (program memory) after<br>10 kcycles at $T_A = 85 \degree C$<br>$T_{RET} = +85 \degree C$ | 30                                  | -                  | -   |     |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 85 °C                                   | 1 <sub>RET</sub> - +03 C            | 30                 | -   | -   |         |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C                           | - T <sub>RET</sub> = +105 °C        | 10                 | -   | -   | years   |

|                                 | Data retention (EEPROM data memory)<br>after 300 kcycles at T <sub>A</sub> = 105 °C                      |                                     | 10                 | -   | -   |         |

| Table 25 Electromere   | wand data EEDBOM and uranaa and ratantia | -  |

|------------------------|------------------------------------------|----|

| Table 35. Flash memory | y and data EEPROM endurance and retentio | n. |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

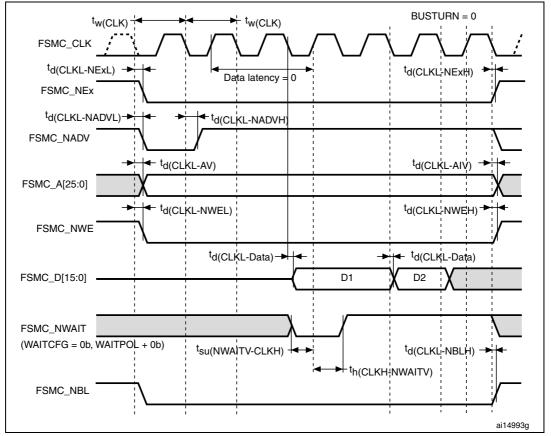

|                              | •                                     | <u> </u> | <b>`</b> | ,    |

|------------------------------|---------------------------------------|----------|----------|------|

| Symbol                       | Parameter                             | Min      | Мах      | Unit |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high | 6        | -        | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high  | 0        | -        | ns   |

| 1. C <sub>L</sub> = 30 pF.   |                                       |          |          |      |

### Table 42. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)</sup> (continued)

#### Figure 25. Synchronous non-multiplexed PSRAM write timings

| Table 43. Synchronous non-multiplexed PSRAM write tim | ings <sup>(1)</sup> |

|-------------------------------------------------------|---------------------|

|-------------------------------------------------------|---------------------|

| Symbol                     | Parameter                                  | Min                    | Max | Unit |

|----------------------------|--------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                            | 2*T <sub>HCLK</sub> -3 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x = 02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x = 02)     | 1                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low              | -                      | 5   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high             | 7                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x = 1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x = 1625) | T <sub>HCLK</sub> + 4  | -   | ns   |

| $t_{d(CLKL-NWEL)}$         | FSMC_CLK low to FSMC_NWE low               | -                      | 2   | ns   |

#### 6.3.17 Communications interfaces

#### I<sup>2</sup>C interface characteristics

The device I<sup>2</sup>C interface meets the requirements of the standard I<sup>2</sup>C communication protocol with the following restrictions: SDA and SCL are not "true" open-drain I/O pins. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 54*. Refer also to *Section 6.3.14: I/O port characteristics* for more details on the input/output ction characteristics (SDA and SCL).

| Symbol                                     | Parameter                                                            | Standard mode<br>I <sup>2</sup> C <sup>(1)(2)</sup> |                     | Fast mode I <sup>2</sup> C <sup>(1)(2)</sup> |                    | Unit |  |

|--------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------|---------------------|----------------------------------------------|--------------------|------|--|

|                                            |                                                                      | Min                                                 | Max                 | Min                                          | Max                |      |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                   | 4.7                                                 | -                   | 1.3                                          | -                  |      |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                  | 4.0                                                 | -                   | 0.6                                          | -                  | — μs |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                       | 250                                                 | -                   | 100                                          | -                  |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                   | -                                                   | 3450 <sup>(3)</sup> | -                                            | 900 <sup>(3)</sup> |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                | -                                                   | 1000                | -                                            | 300                | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                | -                                                   | 300                 | -                                            | 300                |      |  |

| t <sub>h(STA)</sub>                        | Start condition hold time                                            | 4.0                                                 | -                   | 0.6                                          | -                  |      |  |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                  | 4.7                                                 | -                   | 0.6                                          | -                  | μs   |  |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                            | 4.0                                                 | -                   | 0.6                                          | -                  | μs   |  |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                              | 4.7                                                 | -                   | 1.3                                          | -                  | μs   |  |

| Cb                                         | Capacitive load for each bus line                                    | -                                                   | 400                 | -                                            | 400                | pF   |  |

| t <sub>SP</sub>                            | Pulse width of spikes that<br>are suppressed by the<br>analog filter | 0                                                   | 50 <sup>(4)</sup>   | 0                                            | 50 <sup>(4)</sup>  | ns   |  |

Table 54. I<sup>2</sup>C characteristics

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The minimum width of the spikes filtered by the analog filter is above t<sub>SP(max)</sub>.

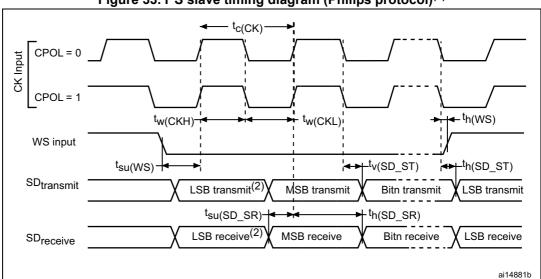

ODD bit value, digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max of (I2SDIV+ODD)/(2\*I2SDIV+ODD). Fs max is supported for each mode/condition.

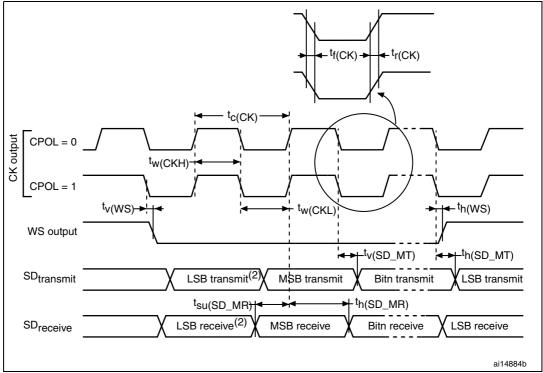

Figure 33. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels: 0.3 × V<sub>DD</sub> and 0.7 × V<sub>DD</sub>.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Figure 34. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

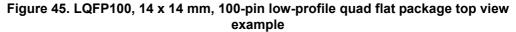

### 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

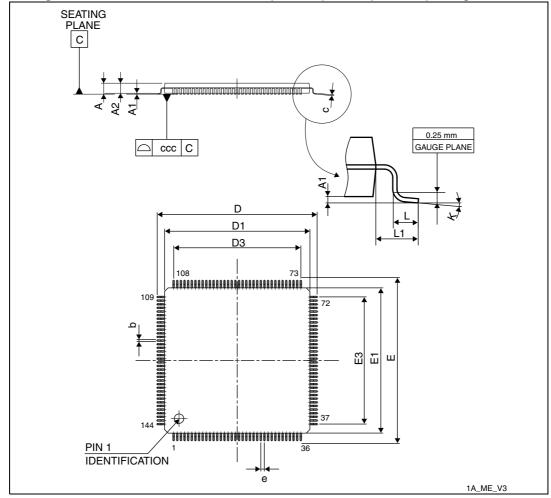

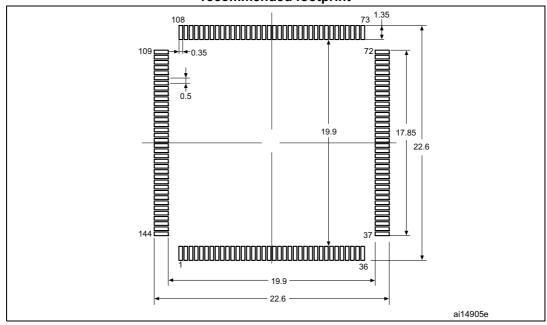

## 7.1 LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package information

Figure 40. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline

1. Drawing is not to scale.

1. Dimensions are in millimeters.

#### Marking of engineering samples

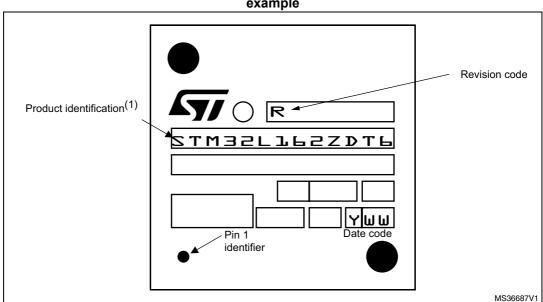

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 42. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

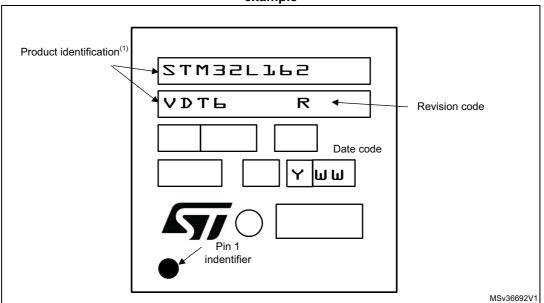

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

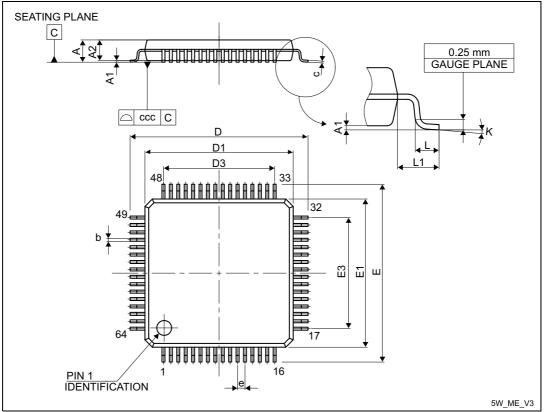

## 7.3 LQFP64, 10 x 10 mm, 64-pin low-profile quad flat package information

Figure 46. LQFP64, 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 75. LQFP64, 10 x 10 mm 64-pin low-profile quad flat package mechanical |

|------------------------------------------------------------------------------|

| data                                                                         |

|        |             |        | uata  |                       |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|        | Min         | Тур    | Мах   | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| Е      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

## 9 Revision History

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24-Oct-2011 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 28-Feb-2012 | 2        | Status of the document changed (datasheet instead of preliminary data).<br>Added STM32L162RD part number.<br>Added LQFP64 and WLCSP64 packages.<br>Updated "Low power " and "Memory" feature on page 1.<br><i>Introduction</i> and <i>Description</i> : added 'high density'.<br>GPIOF replaced with GIOPH.<br>Added SDIO in <i>Table 5: Ultralow power STM32L162xD device features</i><br><i>and peripheral counts on page 13</i> .<br><i>Section 3: Functional overview</i> : changed '128 kHz' to '131 kHz' in<br>section "Low power run mode".<br><i>Section 3.16: AES</i> : updated '214' to '213' clock cycles.<br><i>Section 3.17: 1: General-purpose timers (TIM2, TIM3, TIM4, TIM5,<br/>TIM9, TIM10 and TIM11)</i> : changed 'six' to 'seven' synchronizable<br>general-purpose timers.<br>Added SDIO in <i>Table 19: Alternate function input/output on page 86</i><br>(FSMC/SDIO instead of FSMC); modified alternate function for PA13<br>and PA14; removed EVENT OUT for PH2.<br>Modified <i>Section 3.4: Clock management on page 20</i> .<br><i>Table 15: STM32L162xD pin definitions on page 60</i> : updated name of<br>reference manual in footnote 4.<br>Modified <i>Figure 8: Power supply scheme on page 46</i> .<br>Modified <i>Table 2: Functionalities depending on the operating power</i><br><i>supply range on page 15</i> .<br><i>Table 18: Current consumption in Run mode, code with data</i><br><i>processing running from RAM</i> : added footnote 3.<br><i>Table 19: Current consumption in Sleep mode</i> : updated condition for<br>f <sub>HSE;</sub> added footnote 3.<br><i>Table 23: Typical and maximum current consumptions in Standby</i><br><i>mode</i> : modified max values.<br><i>Table 28: Peripheral current consumption</i> : added AES.<br><i>Table 28: Peripheral current consumption</i> : added AES.<br><i>Table 64: USB DC electrical characteristics</i> : removed two footnotes.<br>Modified Table 38: Flash memory and data EEPROM characteristics<br><i>on page 54</i> . |

| Table 81. | Document | revision | history |

|-----------|----------|----------|---------|

|-----------|----------|----------|---------|