Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

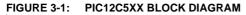

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

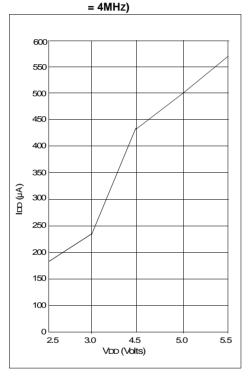

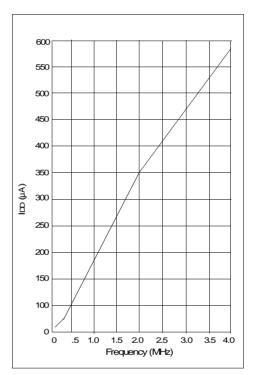

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 25 x 8                                                                    |

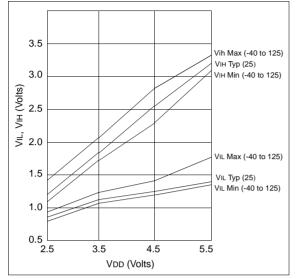

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 8-SOIJ                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c508-04-sm |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

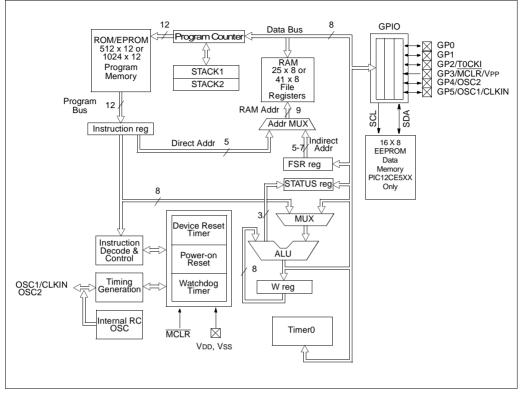

# 5.0 I/O PORT

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

### 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the output data latches. That is, if an output      |

|-------|---------------------------------------------------------------------------------------------|

|       | driver on a pin is enabled and driven high,                                                 |

|       | but the external system is holding it low, a read of the port will indicate that the pin is |

|       | low.                                                                                        |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

### FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

### 7.0 EEPROM PERIPHERAL OPERATION

# This section applies to PIC12CE518 and PIC12CE519 only.

The PIC12CE518 and PIC12CE519 each have 16 bytes of EEPROM data memory. The EEPROM memory has an endurance of 1,000,000 erase/write cycles and a data retention of greater than 40 years. The EEPROM data memory supports a bi-directional 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), that are mapped to bit6 and bit7, respectively, of the GPIO register (SFR 06h). Unlike the GP0-GP5 that are connected to the internal EEPROM peripheral. For most applications, all that is required is calls to the following functions:

; Byte\_Write: Byte write routine Inputs: EEPROM Address EEADDR : ; EEPROM Data EEDATA Outputs: Return 01 in W if OK, else ; return 00 in W ; ; Read\_Current: Read EEPROM at address currently held by EE device. Inputs: NONE ; Outputs: EEPROM Data EEDATA ; Return 01 in W if OK, else ; return 00 in W ; ; Read\_Random: Read EEPROM byte at supplied address Inputs: EEPROM Address : FFADDR ; Outputs: EEPROM Data EEDATA Return 01 in W if OK, ; else return 00 in W

The code for these functions is available on our website www.microchip.com. The code will be accessed by either including the source code FL51XINC.ASM or by linking FLASH5IX.ASM.

It is very important to check the return codes when using these calls, and retry the operation if unsuccessful. Unsuccessful return codes occur when the EE data memory is busy with the previous write, which can take up to 4 mS.

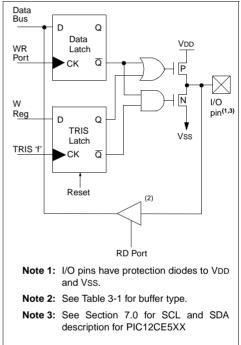

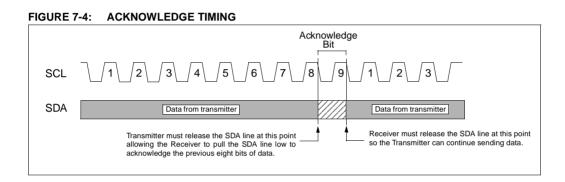

### 7.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the device.

For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

The EEPROM interface is a 2-wire bus protocol consisting of data (SDA) and a clock (SCL). Although these lines are mapped into the GPIO register, they are not accessible as external pins; only to the internal EEPROM peripheral. SDA and SCL operation is also slightly different than GPO-GP5 as listed below. Namely, to avoid code overhead in modifying the TRIS register, both SDA and SCL are always outputs. To read data from the EEPROM peripheral requires outputting a '1' on SDA placing it in high-Z state, where only the internal 100K pull-up is active on the SDA line.

SDA:

Built-in 100K (typical) pull-up to VDD Open-drain (pull-down only) Always an output Outputs a '1' on reset

SCL: Full CMOS output Always an output Outputs a '1' on reset

The following example requires:

- · Code Space: 77 words

- RAM Space: 5 bytes (4 are overlayable)

- Stack Levels:1 (The call to the function itself. The functions do not call any lower level functions.)

- Timing:

- WRITE\_BYTE takes 328 cycles

- READ\_CURRENT takes 212 cycles

- READ\_RANDOM takes 416 cycles.

- IO Pins: 0 (No external IO pins are used)

This code must reside in the lower half of a page. The code achieves it's small size without additional calls through the use of a sequencing table. The table is a list of procedures that must be called in order. The table uses an ADDWF PCL,F instruction, effectively a computed goto, to sequence to the next procedure. However the ADDWF PCL,F instruction yields an 8 bit address, forcing the code to reside in the first 256 addresses of a page.

<sup>© 1999</sup> Microchip Technology Inc.

### FIGURE 7-3: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

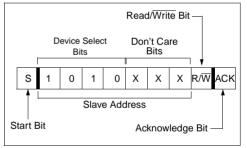

### 7.2 Device Addressing

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed. The slave address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

### FIGURE 7-5: CONTROL BYTE FORMAT

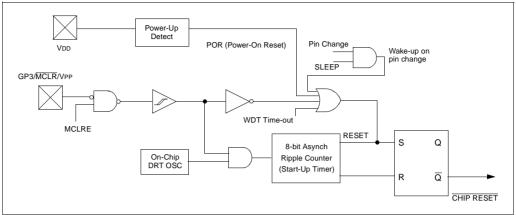

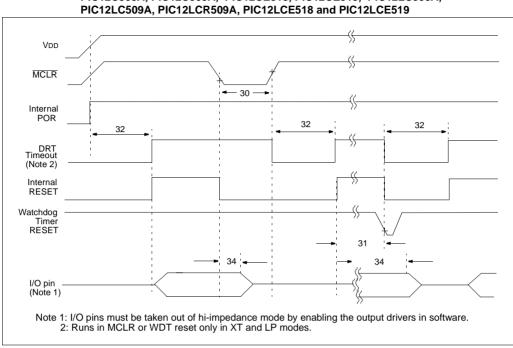

#### FIGURE 8-8: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

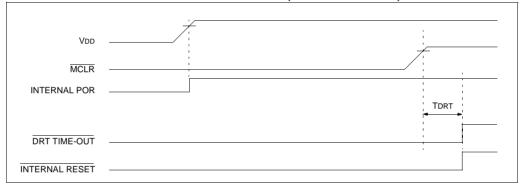

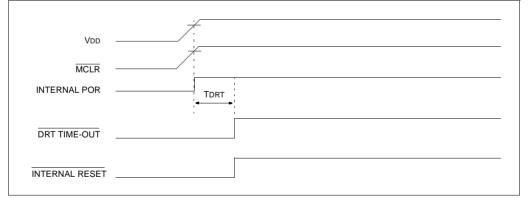

FIGURE 8-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR PULLED LOW)

# 9.0 INSTRUCTION SET SUMMARY

Each PIC12C5XX instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC12C5XX instruction set summary in Table 9-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

### TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is<br>the recommended form of use for compatibility<br>with all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| WDT           | Watchdog Timer Counter                                                                                                                                                         |

| TO            | Time-Out bit                                                                                                                                                                   |

| PD            | Power-Down bit                                                                                                                                                                 |

| dest          | Destination, either the W register or the specified register file location                                                                                                     |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1 µs. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2 µs.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

# FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                                   |                                                                                       |      |        |        |             |   |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|--------|--------|-------------|---|--|--|

|                                                                                                          | 11                                                                                    | 6    | 5      | 4      |             | 0 |  |  |

|                                                                                                          | OPCODE                                                                                |      | d      |        | f (FILE #)  |   |  |  |

|                                                                                                          | d = 0 for destination W<br>d = 1 for destination f<br>f = 5-bit file register address |      |        |        |             |   |  |  |

| Bi                                                                                                       | t-oriented file regi                                                                  | iste | er ope | eratio | ins         |   |  |  |

|                                                                                                          | 11                                                                                    | 8    | 7      | 5      | 4           | 0 |  |  |

|                                                                                                          | OPCODE                                                                                |      | b (B   | IT #)  | f (FILE #)  |   |  |  |

| b = 3-bit bit address<br>f = 5-bit file register address<br>Literal and control operations (except GOTO) |                                                                                       |      |        |        |             |   |  |  |

|                                                                                                          | 11 8 7 0                                                                              |      |        |        |             |   |  |  |

|                                                                                                          | OPCODE k (literal)                                                                    |      |        |        |             |   |  |  |

| k = 8-bit immediate value                                                                                |                                                                                       |      |        |        |             |   |  |  |

| Literal and control operations - GOTO instruction                                                        |                                                                                       |      |        |        |             |   |  |  |

| r                                                                                                        | 11                                                                                    |      | 9      | 8      |             | 0 |  |  |

|                                                                                                          | OPCODE                                                                                |      |        |        | k (literal) |   |  |  |

|                                                                                                          |                                                                                       |      |        |        |             |   |  |  |

k = 9-bit immediate value

| CALL                  | Subroutine Call                                                                                                                                                                                                                                                   |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:               | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                           |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                                                                                                 |  |  |  |  |

| Operation:            | $\begin{array}{l} (PC) + 1 \rightarrow \text{Top of Stack;} \\ k \rightarrow PC < 7:0>; \\ (STATUS < 6:5>) \rightarrow PC < 10:9>; \\ 0 \rightarrow PC < 8> \end{array}$                                                                                          |  |  |  |  |

| Status Affected:      | None                                                                                                                                                                                                                                                              |  |  |  |  |

| Encoding:             | 1001 kkkk kkkk                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:          | Subroutine call. First, return address<br>(PC+1) is pushed onto the stack. The<br>eight bit immediate address is loaded<br>into PC bits <7:0>. The upper bits<br>PC<10:9> are loaded from STA-<br>TUS<6:5>, PC<8> is cleared. CALL is<br>a two cycle instruction. |  |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                                                 |  |  |  |  |

| Cycles:               | 2                                                                                                                                                                                                                                                                 |  |  |  |  |

| Example:              | HERE CALL THERE                                                                                                                                                                                                                                                   |  |  |  |  |

| Before Instru<br>PC = |                                                                                                                                                                                                                                                                   |  |  |  |  |

|                       | tion<br>address (THERE)<br>address (HERE + 1)                                                                                                                                                                                                                     |  |  |  |  |

### CLRF

| Syntax:                               | [label] CLRF f                                                         |           |   |  |  |  |

|---------------------------------------|------------------------------------------------------------------------|-----------|---|--|--|--|

| Operands:                             | $0 \le f \le 31$                                                       |           |   |  |  |  |

| Operation:                            | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |           |   |  |  |  |

| Status Affected:                      | Z                                                                      |           |   |  |  |  |

| Encoding:                             | 0000 011f ffff                                                         |           |   |  |  |  |

| Description:                          | The contents of register 'f' are cleared and the Z bit is set.         |           |   |  |  |  |

| Words:                                | 1                                                                      |           |   |  |  |  |

| Cycles:                               | 1                                                                      |           |   |  |  |  |

| Example:                              | CLRF                                                                   | FLAG_REC  | 3 |  |  |  |

| Before Instruction<br>FLAG_REG = 0x5A |                                                                        |           |   |  |  |  |

| After Instruct<br>FLAG_RE<br>Z        |                                                                        | 0x00<br>1 |   |  |  |  |

Clear f

| CLRW                                                                                                     | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation:                                                                                               | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}); \\ 1 \rightarrow \text{Z} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                                                                                             | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                                 | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Before Instru<br>W =                                                                                     | uction<br>0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| After Instruct<br>W =<br>Z =                                                                             | tion<br>0x00<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLRWDT<br>Syntax:                                                                                        | Clear Watchdog Timer<br>[label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Syntax:                                                                                                  | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Syntax:<br>Operands:                                                                                     | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Syntax:<br>Operands:<br>Operation:                                                                       | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |