Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

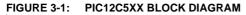

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 768B (512 x 12)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c508-04i-sm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The special registers can be classified into two sets. The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

# TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

|                    |                                                                                     |                             |                                      |             |           |                        |              |           |           | Value on<br>Power-On | Value on<br>All Other    |

|--------------------|-------------------------------------------------------------------------------------|-----------------------------|--------------------------------------|-------------|-----------|------------------------|--------------|-----------|-----------|----------------------|--------------------------|

| Address            | Name                                                                                | Bit 7                       | Bit 6                                | Bit 5       | Bit 4     | Bit 3                  | Bit 2        | Bit 1     | Bit 0     | Reset                | Resets <sup>(2)</sup>    |

| N/A                | TRIS                                                                                | —                           | I                                    |             |           |                        |              |           |           | 11 1111              | 11 1111                  |

| N/A                | OPTION                                                                              | Contains co<br>prescaler, v |                                      |             |           | Timer0/WD1<br>pull-ups | Γ            |           |           | 1111 1111            | 1111 1111                |

| 00h                | INDF                                                                                | Uses conte                  | ents of FSR                          | R to addres | s data me | mory (not a            | physical reg | jister)   |           | xxxx xxxx            | uuuu uuuu                |

| 01h                | TMR0                                                                                | 8-bit real-ti               | me clock/c                           | ounter      |           |                        |              |           |           | xxxx xxxx            | uuuu uuuu                |

| 02h <sup>(1)</sup> | PCL                                                                                 | Low order                   | B bits of PC                         | c           |           |                        |              |           |           | 1111 1111            | 1111 1111                |

| 03h                | STATUS                                                                              | GPWUF                       | -                                    | PA0         | TO        | PD                     | Z            | DC        | С         | 0001 1xxx            | q00q quuu <sup>(3)</sup> |

| 04h                | FSR<br>(PIC12C508/<br>PIC12C508A/<br>PIC12C518)                                     | Indirect dat                | ndirect data memory address pointer  |             |           |                        |              | 1         | 111x xxxx | 111u uuuu            |                          |

| 04h                | FSR<br>(PIC12C509/<br>PIC12C509A/<br>PIC12CR509A/<br>PIC12CE519)                    | Indirect dat                | Indirect data memory address pointer |             |           |                        |              | 110x xxxx | 11uu uuuu |                      |                          |

| 05h                | OSCCAL<br>(PIC12C508/<br>PIC12C509)                                                 | CAL3                        | CAL2                                 | CAL1        | CAL0      | _                      | _            | _         | _         | 0111                 | uuuu                     |

| 05h                | OSCCAL<br>(PIC12C508A/<br>PIC12C509A/<br>PIC12CE518/<br>PIC12CE519/<br>PIC12CR509A) | CAL5                        | CAL4                                 | CAL3        | CAL2      | CAL1                   | CAL0         |           | _         | 1000 00              | uuuu uu                  |

| 06h                | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CC509A)     | _                           | _                                    | GP5         | GP4       | GP3                    | GP2          | GP1       | GP0       | xx xxxx              | uu uuuu                  |

| 06h                | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                                 | SCL                         | SDA                                  | GP5         | GP4       | GP3                    | GP2          | GP1       | GP0       | 11xx xxxx            | 11uu uuuu                |

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as '0' (if applicable)

x = unknown, u = unchanged, q = see the tables in Section 8.7 for possible values.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 for an explanation of how to access these bits.

2: Other (non power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

3: If reset was due to wake-up on pin change then bit 7 = 1. All other resets will cause bit 7 = 0.

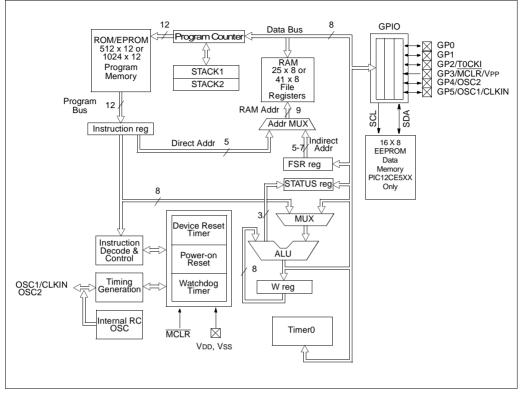

# 5.0 I/O PORT

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

# 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the output data latches. That is, if an output      |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------|--|--|--|--|

|       | driver on a pin is enabled and driven high,                                                 |  |  |  |  |

|       | but the external system is holding it low, a read of the port will indicate that the pin is |  |  |  |  |

|       | low.                                                                                        |  |  |  |  |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

# 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

# FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

#### 7.0.2 SERIAL CLOCK

This SCL input is used to synchronize the data transfer from and to the device.

#### 7.1 BUS CHARACTERISTICS

The following **bus protocol** is to be used with the EEPROM data memory.

• Data transfer may be initiated only when the bus is not busy.

During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 7-3).

7.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

7.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### 7.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### 7.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the master device and is theoretically unlimited.

#### 7.1.5 ACKNOWLEDGE

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.

Note: Acknowledge bits are not generated if an internal programming cycle is in progress.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition (Figure 7-4).

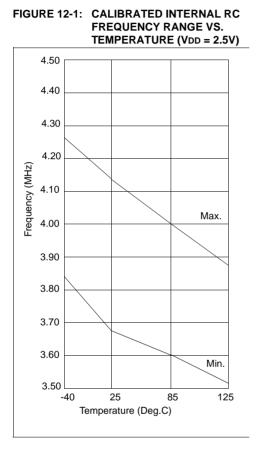

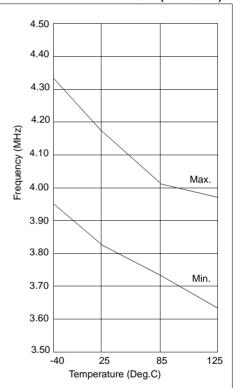

#### 8.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and 25°C, see "Electrical Specifications" section for information on variation over voltage and temperature.

In addition, a calibration instruction is programmed into the top of memory which contains the calibration value for the internal RC oscillator. This location is never code protected regardless of the code protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the reset vector. This will load the W register with the calibration value upon reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part. so it can be reprogrammed correctly later.

For the PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, and PIC12CR509A, bits <7:2>, CAL5-CAL0 are used for calibration. Adjusting CAL5-0 from 000000 to 111111 yields a higher clock speed. Note that bits 1 and 0 of OSCCAL are unimplemented and should be written as 0 when modifying OSCCAL for compatibility with future devices.

For the PIC12C508 and PIC12C509, the upper 4 bits of the register are used. Writing a larger value in this location yields a higher clock speed.

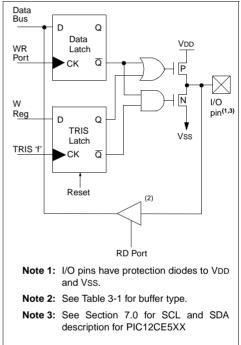

#### 8.3 <u>RESET</u>

The device differentiates between various kinds of reset:

- a) Power on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT time-out reset during normal operation

- e) WDT time-out reset during SLEEP

- f) Wake-up from SLEEP on pin change

Some registers are not reset in any way; they are unknown on POR and unchanged in any other reset. Most other registers are reset to "reset state" on poweron reset (POR),  $\overline{MCLR}$ , WDT or wake-up on pin change reset during normal operation. They are not affected by a WDT reset during SLEEP or  $\overline{MCLR}$  reset during SLEEP, since these resets are viewed as resumption of normal operation. The exceptions to this are  $\overline{TO}$ ,  $\overline{PD}$ , and GPWUF bits. They are set or cleared differently in different reset situations. These bits are used in software to determine the nature of reset. See Table 8-3 for a full description of reset states of all registers.

# FIGURE 8-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### 8.5 Device Reset Timer (DRT)

In the PIC12C5XX, DRT runs from RESET and varies based on oscillator selection (see Table 8-5.)

The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min., and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after MCLR has reached a logic high (VIHMCLR) level. Thus, programming GP3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the GP3/MCLR/VPP pin as a general purpose input.

The Device Reset time delay will vary from chip to chip due to VDD, temperature, and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake from SLEEP mode automatically.

#### 8.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the external RC oscillator of the GP5/OSC1/CLKIN pin and the internal 4 MHz oscillator. That means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT reset or wake-up reset generates a device RESET.

The  $\overline{TO}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer reset.

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 8.1). Refer to the PIC12C5XX Programming Specifications to determine how to access the configuration word.

TABLE 8-5: DRT (DEVICE RESET TIMER PERIOD)

| Oscillator<br>Configuration | POR Reset       | Subsequent<br>Resets |  |  |

|-----------------------------|-----------------|----------------------|--|--|

| IntRC &<br>ExtRC            | 18 ms (typical) | 300 µs (typical)     |  |  |

| XT & LP                     | 18 ms (typical) | 18 ms (typical)      |  |  |

#### 8.7 <u>Time-Out Sequence, Power Down,</u> and Wake-up from SLEEP Status Bits (TO/PD/GPWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits in the STATUS register can be tested to determine if a RESET condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) reset.

| TABLE 8-7: | TO/PD/GPWUF STATUS |  |  |

|------------|--------------------|--|--|

|            | AFTER RESET        |  |  |

| GPWUF | то | PD | RESET caused by                           |  |  |

|-------|----|----|-------------------------------------------|--|--|

| 0     | 0  | 0  | WDT wake-up from<br>SLEEP                 |  |  |

| 0     | 0  | u  | SLEEP<br>WDT time-out (not from<br>SLEEP) |  |  |

| 0     | 1  | 0  | MCLR wake-up from<br>SLEEP                |  |  |

| 0     | 1  | 1  | Power-up                                  |  |  |

| 0     | u  | u  | MCLR not during SLEEP                     |  |  |

| 1     | 1  | 0  | Wake-up from SLEEP on<br>pin change       |  |  |

Legend: u = unchanged

Note 1: The TO, PD, and GPWUF bits maintain their status (u) until a reset occurs. A lowpulse on the MCLR input does not change the TO, PD, and GPWUF status bits.

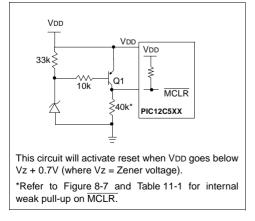

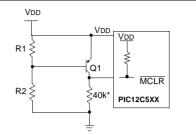

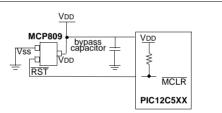

### 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset PIC12C5XX devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-13 , Figure 8-14 and Figure 8-15

#### FIGURE 8-13: BROWN-OUT PROTECTION CIRCUIT 1

### FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

\*Refer to Figure 8-7 and Table 11-1 for internal weak pull-up on MCLR.

### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX family of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accomodate 5V and 3V systems.

| ADDWF                                                           | Add W and f                                                                                                                                                       |  |  |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                         | [ label ] ADDWF f,d                                                                                                                                               |  |  |  |  |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                    |  |  |  |  |

| Operation:                                                      | (W) + (f) $\rightarrow$ (dest)                                                                                                                                    |  |  |  |  |

| Status Affected:                                                | C, DC, Z                                                                                                                                                          |  |  |  |  |

| Encoding:                                                       | 0001 11df ffff                                                                                                                                                    |  |  |  |  |

| Description:                                                    | Add the contents of the W register and register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. |  |  |  |  |

| Words:                                                          | 1                                                                                                                                                                 |  |  |  |  |

| Cycles:                                                         | 1                                                                                                                                                                 |  |  |  |  |

| Example:                                                        | ADDWF FSR, 0                                                                                                                                                      |  |  |  |  |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>tion<br>0xD9                                                                                                                                      |  |  |  |  |

| ANDWF                          | AND W with f                                                                                                                                                                       |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] ANDWF f,d                                                                                                                                                                  |

| Operands:                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                                        |

| Operation:                     | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                 |

| Status Affected:               | Z                                                                                                                                                                                  |

| Encoding:                      | 0001 01df ffff                                                                                                                                                                     |

| Description:                   | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>'1' the result is stored back in register 'f'. |

| Words:                         | 1                                                                                                                                                                                  |

| Cycles:                        | 1                                                                                                                                                                                  |

| Example:                       | ANDWF FSR, 1                                                                                                                                                                       |

| Before Instru<br>W =<br>FSR =  | 0x17                                                                                                                                                                               |

| After Instruct<br>W =<br>FSR = | 0x17                                                                                                                                                                               |

| ANDLW                 | And literal with W                                                                                                      |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:               | [ <i>label</i> ] ANDLW k                                                                                                |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                       |  |  |  |  |

| Operation:            | (W).AND. (k) $\rightarrow$ (W)                                                                                          |  |  |  |  |

| Status Affected:      | Z                                                                                                                       |  |  |  |  |

| Encoding:             | 1110 kkkk kkkk                                                                                                          |  |  |  |  |

| Description:          | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |

| Words:                | 1                                                                                                                       |  |  |  |  |

| Cycles:               | 1                                                                                                                       |  |  |  |  |

| Example:              | ANDLW 0x5F                                                                                                              |  |  |  |  |

| Before Instru<br>W =  | iction<br>0xA3                                                                                                          |  |  |  |  |

| After Instruct<br>W = | tion<br>0x03                                                                                                            |  |  |  |  |

| BCF                                   | Bit Clear                                                          | f               |      |  |  |  |

|---------------------------------------|--------------------------------------------------------------------|-----------------|------|--|--|--|

| Syntax:                               | [label] E                                                          | [label] BCF f,b |      |  |  |  |

| Operands:                             | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |                 |      |  |  |  |

| Operation:                            | $0 \rightarrow (f < b;$                                            | >)              |      |  |  |  |

| Status Affected:                      | None                                                               |                 |      |  |  |  |

| Encoding:                             | 0100                                                               | bbbf            | ffff |  |  |  |

| Description:                          | Bit 'b' in register 'f' is cleared.                                |                 |      |  |  |  |

| Words:                                | 1                                                                  |                 |      |  |  |  |

| Cycles:                               | 1                                                                  |                 |      |  |  |  |

| Example:                              | BCF                                                                | FLAG_REC        | 3, 7 |  |  |  |

| Before Instruction<br>FLAG_REG = 0xC7 |                                                                    |                 |      |  |  |  |

| After Instruction<br>FLAG_REG = 0x47  |                                                                    |                 |      |  |  |  |

| MOVF                 | Move f                                                                                                                                                                                                                               |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:              | [label] MOVF f,d                                                                                                                                                                                                                     |  |  |  |  |

| Operands:            | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                            |  |  |  |  |

| Operation:           | $(f) \rightarrow (dest)$                                                                                                                                                                                                             |  |  |  |  |

| Status Affected:     | Z                                                                                                                                                                                                                                    |  |  |  |  |

| Encoding:            | 0010 00df ffff                                                                                                                                                                                                                       |  |  |  |  |

| Description:         | The contents of register 'f' is moved to destination 'd'. If 'd' is 0, destination is the W register. If 'd' is 1, the destination is file register 'f'. 'd' is 1 is useful to test a file register since status flag Z is affected. |  |  |  |  |

| Words:               | 1                                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:              | 1                                                                                                                                                                                                                                    |  |  |  |  |

| Example:             | MOVF FSR, 0                                                                                                                                                                                                                          |  |  |  |  |

| After Instruc<br>W = | After Instruction<br>W = value in FSR register                                                                                                                                                                                       |  |  |  |  |

| MOVLW                | Move Literal to W                                                                             |       |      |  |  |

|----------------------|-----------------------------------------------------------------------------------------------|-------|------|--|--|

| Syntax:              | [ label ]                                                                                     | MOVLW | k    |  |  |

| Operands:            | $0 \le k \le 2$                                                                               | 55    |      |  |  |

| Operation:           | $k \to (W)$                                                                                   |       |      |  |  |

| Status Affected:     | None                                                                                          |       |      |  |  |

| Encoding:            | 1100                                                                                          | kkkk  | kkkk |  |  |

| Description:         | The eight bit literal 'k' is loaded into the W register. The don't cares will assemble as 0s. |       |      |  |  |

| Words:               | 1                                                                                             |       |      |  |  |

| Cycles:              | 1                                                                                             |       |      |  |  |

| Example:             | MOVLW                                                                                         | 0x5A  |      |  |  |

| After Instruc<br>W = | tion<br>0x5A                                                                                  |       |      |  |  |

| MOVWF                         | Move W                | to f         |            |           |

|-------------------------------|-----------------------|--------------|------------|-----------|

| Syntax:                       | [ label ]             | MOVWF        | f          |           |

| Operands:                     | $0 \le f \le 3^{-1}$  | 1            |            |           |

| Operation:                    | $(W) \to (f$          | )            |            |           |

| Status Affected:              | None                  |              |            |           |

| Encoding:                     | 0000                  | 001f         | ffff       |           |

| Description:                  | Move data<br>ter 'f'. | a from the V | W register | to regis- |

| Words:                        | 1                     |              |            |           |

| Cycles:                       | 1                     |              |            |           |

| Example:                      | MOVWF                 | TEMP_REC     | 3          |           |

| Before Instru<br>TEMP_R<br>W  |                       | 0xFF<br>0x4F |            |           |

| After Instruct<br>TEMP_R<br>W |                       | 0x4F<br>0x4F |            |           |

| NOP              | No Oper      | ration |      |  |  |  |  |

|------------------|--------------|--------|------|--|--|--|--|

| Syntax:          | [ label ]    | NOP    |      |  |  |  |  |

| Operands:        | None         |        |      |  |  |  |  |

| Operation:       | No operation |        |      |  |  |  |  |

| Status Affected: | None         |        |      |  |  |  |  |

| Encoding:        | 0000         | 0000   | 0000 |  |  |  |  |

| Description:     | No opera     | ation. |      |  |  |  |  |

| Words:           | 1            |        |      |  |  |  |  |

| Cycles:          | 1            |        |      |  |  |  |  |

| Example:         | NOP          |        |      |  |  |  |  |

# **10.0 DEVELOPMENT SUPPORT**

# 10.1 <u>Development Tools</u>

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- MPLAB<sup>™</sup>-ICE Real-Time In-Circuit Emulator

- ICEPIC<sup>™</sup> Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- SIMICE

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

- KEELOQ<sup>®</sup> Evaluation Kits and Programmer

# 10.2 MPLAB-ICE: High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro<sup>®</sup> microcontrollers (MCUs). MPLAB-ICE is supplied with the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support all new Microchip microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x or Windows 95 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE is available in two versions. MPLAB-ICE 1000 is a basic, low-cost emulator system with simple trace capabilities. It shares processor modules with the MPLAB-ICE 2000. This is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems will operate across the entire operating speed range of the PICmicro<sup>®</sup> MCU.

### 10.3 ICEPIC: Low-Cost PICmicro<sup>®</sup> In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 386 through Pentium<sup>™</sup> based machines under Windows 3.x, Windows 95, or Windows NT environment. ICEPIC features real time, non-intrusive emulation.

# 10.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

### 10.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

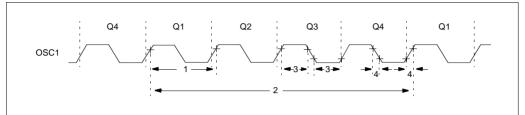

# 11.3 Timing Parameter Symbology and Load Conditions - PIC12C508/C509

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

| 2. 1990 |                                          |     |                |

|---------|------------------------------------------|-----|----------------|

| т       |                                          |     |                |

| F       | Frequency                                | Т   | Time           |

| Lowerc  | case subscripts (pp) and their meanings: |     |                |

| рр      |                                          |     |                |

| 2       | to                                       | mc  | MCLR           |

| ck      | CLKOUT                                   | osc | oscillator     |

| су      | cycle time                               | os  | OSC1           |

| drt     | device reset timer                       | tO  | TOCKI          |

| io      | I/O port                                 | wdt | watchdog timer |

| Upperc  | case letters and their meanings:         |     |                |

| S       |                                          |     |                |

| F       | Fall                                     | Р   | Period         |

| н       | High                                     | R   | Rise           |

| I       | Invalid (Hi-impedance)                   | V   | Valid          |

| L       | Low                                      | Z   | Hi-impedance   |

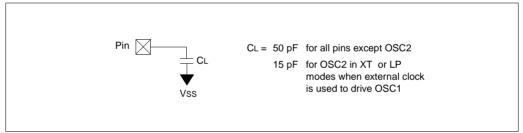

# FIGURE 11-1: LOAD CONDITIONS - PIC12C508/C509

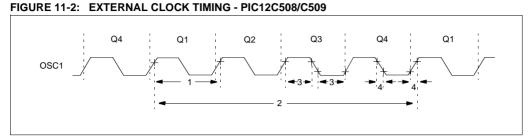

# 11.4 Timing Diagrams and Specifications

| AC Chara         | cteristics |                                         |     |                    |        |       |                |  |  |  |

|------------------|------------|-----------------------------------------|-----|--------------------|--------|-------|----------------|--|--|--|

| Parameter<br>No. | Sym        | Characteristic                          | Min | Typ <sup>(1)</sup> | Мах    | Units | Conditions     |  |  |  |

|                  | Fosc       | External CLKIN Frequency <sup>(2)</sup> |     |                    |        |       |                |  |  |  |

|                  |            |                                         | DC  | —                  | 4      | MHz   | XT osc mode    |  |  |  |

|                  |            |                                         | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |  |

|                  |            | Oscillator Frequency <sup>(2)</sup>     |     |                    |        |       |                |  |  |  |

|                  |            |                                         | 0.1 | —                  | 4      | MHz   | XT osc mode    |  |  |  |

|                  |            |                                         | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |  |

| 1                | Tosc       | External CLKIN Period <sup>(2)</sup>    | 250 | —                  | _      | ns    | EXTRC osc mode |  |  |  |

|                  |            |                                         | 250 | —                  | —      | ns    | XT osc mode    |  |  |  |

|                  |            |                                         | 5   | —                  | —      | ms    | LP osc mode    |  |  |  |

|                  |            | Oscillator Period <sup>(2)</sup>        | 250 | _                  | _      | ns    | EXTRC osc mode |  |  |  |

|                  |            |                                         | 250 | —                  | 10,000 | ns    | XT osc mode    |  |  |  |

|                  |            |                                         | 5   | —                  | —      | ms    | LP osc mode    |  |  |  |

| 2                | Тсу        | Instruction Cycle Time <sup>(3)</sup>   | —   | 4/Fosc             | —      |       |                |  |  |  |

| 3                | TosL, TosH | Clock in (OSC1) Low or High Time        | 50* | —                  | —      | ns    | XT oscillator  |  |  |  |

|                  |            |                                         | 2*  | —                  | —      | ms    | LP oscillator  |  |  |  |

| 4                | TosR, TosF | Clock in (OSC1) Rise or Fall Time       | —   | —                  | 25*    | ns    | XT oscillator  |  |  |  |

|                  |            |                                         | -   | _                  | 50*    | ns    | LP oscillator  |  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

Instruction cycle period (Tcy) equals four times the input oscillator time base period.

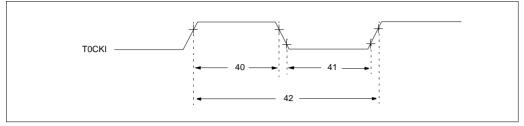

# FIGURE 11-5: TIMER0 CLOCK TIMINGS - PIC12C508/C509

# TABLE 11-7: TIMER0 CLOCK REQUIREMENTS - PIC12C508/C509

| AC               | g Conditions (<br>ture 0°C ≤<br>-40°C ≤<br>-40°C ≤<br>/DD range is des | ≦ TA ≤ +<br>≦ TA ≤ +<br>≦ TA ≤ + | 70°C (<br>85°C (<br>125°C | comme<br>(industr<br>(exten  | ercial)<br>ial)<br>ded) |       |            |                                                                |

|------------------|------------------------------------------------------------------------|----------------------------------|---------------------------|------------------------------|-------------------------|-------|------------|----------------------------------------------------------------|

| Parameter<br>No. | Sym                                                                    | Characteristic                   | Min                       | Тур <sup>(1)</sup>           | Max                     | Units | Conditions |                                                                |

| 40               | Tt0H                                                                   | T0CKI High Pulse V               | 0.5 TCY + 20*             | —                            |                         | ns    |            |                                                                |

|                  |                                                                        |                                  | 10*                       | —                            |                         | ns    |            |                                                                |

| 41               | Tt0L                                                                   | T0CKI Low Pulse W                | 0.5 TCY + 20*             | —                            |                         | ns    |            |                                                                |

|                  |                                                                        |                                  | 10*                       | _                            |                         | ns    |            |                                                                |

| 42               | Tt0P                                                                   | T0CKI Period                     |                           | 20 or <u>Tcy + 40</u> *<br>N | _                       | -     | ns         | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

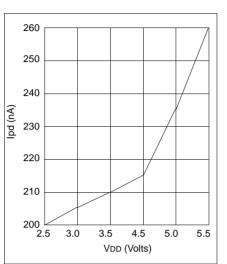

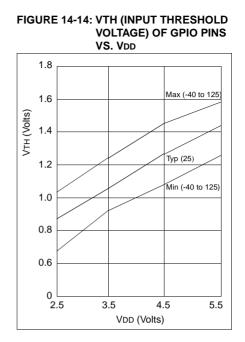

# 12.0 DC AND AC CHARACTERISTICS - PIC12C508/PIC12C509

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables the data presented are outside specified operating range (e.g., outside specified VDD range). This is for information only and devices will operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

# 13.2 DC CHARACTERISTICS:

#### PIC12LC508A/509A (Commercial, Industrial) PIC12LCE518/519 (Commercial, Industrial) PIC12LCR509A (Commercial, Industrial)

|               | DC Characteristics<br>Power Supply Pins       |       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \end{array}$ |                    |        |          |                                                                              |  |  |  |

|---------------|-----------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|----------|------------------------------------------------------------------------------|--|--|--|

| Parm<br>No.   | Characteristic                                | Sym   | Min                                                                                                                                                                                                                                                          | Typ <sup>(1)</sup> | Max    | Units    | Conditions                                                                   |  |  |  |

| D001          | Supply Voltage                                | Vdd   | 2.5                                                                                                                                                                                                                                                          |                    | 5.5    | V        | Fosc = DC to 4 MHz (Commercial/<br>Industrial)                               |  |  |  |

| D002          | RAM Data Retention<br>Voltage <sup>(2)</sup>  | Vdr   |                                                                                                                                                                                                                                                              | 1.5*               |        | V        | Device in SLEEP mode                                                         |  |  |  |

| D003          | VDD Start Voltage to ensure<br>Power-on Reset | VPOR  |                                                                                                                                                                                                                                                              | Vss                |        | V        | See section on Power-on Reset for details                                    |  |  |  |

| D004          | VDD Rise Rate to ensure<br>Power-on Reset     | SVDD  | 0.05*                                                                                                                                                                                                                                                        |                    |        | V/ms     | See section on Power-on Reset for details                                    |  |  |  |

| D010          | Supply Current <sup>(3)</sup>                 | IDD   | —                                                                                                                                                                                                                                                            | 0.4                | 0.8    | mA       | XT and EXTRC options (Note 4)<br>Fosc = 4 MHz, VDD = 2.5V                    |  |  |  |

| D010C         |                                               |       | —                                                                                                                                                                                                                                                            | 0.4                | 0.8    | mA       | INTRC Option<br>Fosc = 4 MHz, VDD = 2.5V                                     |  |  |  |

| D010A         |                                               |       | —                                                                                                                                                                                                                                                            | 15                 | 23     | μA       | LP OPTION, Commercial Temperature<br>Fosc = 32 kHz, VDD = 2.5V, WDT disabled |  |  |  |

|               |                                               |       | _                                                                                                                                                                                                                                                            | 15                 | 31     | μA       | LP OPTION, Industrial Temperature<br>FOSC = 32 kHz, VDD = 2.5V, WDT disabled |  |  |  |

| D020          | Power-Down Current (5)                        | IPD   |                                                                                                                                                                                                                                                              |                    |        |          |                                                                              |  |  |  |

| D021<br>D021B |                                               |       |                                                                                                                                                                                                                                                              | 0.2<br>0.2         | 3<br>4 | μΑ<br>μΑ | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                             |  |  |  |

|               |                                               | ΔIWDT | -                                                                                                                                                                                                                                                            | 2.0<br>2.0         | 4<br>5 | mA<br>mA | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                             |  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: Does not include current through Rext. The current through the resistor can be estimated by the formula: IR = VDD/2Rext (mA) with Rext in kOhm.

- 5: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

# 13.3 DC CHARACTERISTICS:

#### PIC12C508A/509A (Commercial, Industrial, Extended) PIC12C518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

| -40°C $\leq$ TA $\leq$ +85°C (industrial)<br>-40°C $\leq$ TA $\leq$ +125°C (industrial)<br>-40°C $\leq$ TA $\leq$ +125°C (extended)<br>Operating voltage VDD range as described in DC spec Sec<br>Section 13.2.Param<br>No.CharacteristicSymMinTyp†MaxUnitsConditInput Low Voltage<br>I/O portsVILVss-0.8VVFor 4.5V $\leq$ VDD $\leq$ 5D030with TTL bufferVILVss-0.8VVFor 4.5V $\leq$ VDD $\leq$ 5D031with Schmitt Trigger bufferVss-0.2VDDVD032MCLR, GP2/T0CKI (in EXTRC mode)Vss-0.2VDDVD033OSC1 (in XT and LP)Vss-0.2VDDVD040with Schmitt Trigger buffer0.25VDD +-VDDVD040with TTL buffer0.25VDD +-VDDVD040with TTL buffer0.25VDD +-VDDVD0404with Schmitt Trigger buffer0.8VDD-VDDVD041with Schmitt Trigger buffer0.8VDD-VDDVD042MCLR, GP2/T0CKI0.8VDD-VDDVD043OSC1 (in EXTRC mode)0.9VDD-VDDVD044MCLR, GP2/T0CKI0.8VDD-VDDVD043MCLR, GP2/T0CKI0.8VDD-VDDVD044MCLR, GP2/T0CKI0.8VDD-VDDVD045MCLR, GP2/T0CKI0.9VDD-VDDVD046MCLR,            | )             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Operating voltage VDD range as described in DC spec Sector 13.2.Param<br>No.CharacteristicSymMinTyp†MaxUnitsConditNo.Input Low Voltage<br>I/O portsViLViLVss-0.8VVFor 4.5V $\leq$ VDD $\leq$ 5D030with TTL bufferViLVss-0.15VDDVVD031with Schmitt Trigger bufferVss-0.2VDDVVD032MCLR, GP2/T0CKI (in EXTRC mode)Vss-0.2VDDVNote 1D033OSC1 (in TA rad LP)Vss-0.3VDDVNote 1D040Input High Voltage<br>with TTL bufferVIHD0404with Schmitt Trigger buffer0.8VDD-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD0404with Schmitt Trigger buffer0.8VDD-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD0404with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD0404MCLR, GP2/T0CKI0.8VDD-VDDVVDD042OSC1 (in EXTRC mode)0.9VDD-VDDVVDVD042OSC1 (in EXTRC mode)0.9VDD-VDDVVDVD043OSC1 (in EXTRC mode)0.9VDD-VDDVVDVD044MCLR, GP2/T0CKI0.9VDD-VDDVVDVD045OSC1 (in EXTRC mode)0.9VDD-<                                                                                             |               |

| No.Input Low Voltage<br>I/O portsVILVILVILVILD030with TTL bufferVILVSS-0.8VVFor 4.5V $\leq$ VDD $\leq$ 5D031with Schmitt Trigger bufferVSS-0.15VDDVotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)VSS-0.2VDDVD033OSC1 (in EXTRC mode)VSS-0.2VDDVD033OSC1 (in XT and LP)VSS-0.2VDDVD040with TTL bufferVIHD040with Schmitt Trigger buffer0.8VD-VDDVD040with Schmitt Trigger buffer0.8VDD-VDDVD041with Schmitt Trigger buffer0.8VDD-VDDVD042AMCLR, GP2/T0CKI0.7VDD-VDDVD043OSC1 (XT and LP)0.7VDD-VDDVD043OSC1 (in EXTRC mode)IPUR30250400 $\mu$ AD043OSC1 (in EXTRC mode)IPUR30250400 $\mu$ AD043OSC1 (in EXTRC mode)IPUR30250400 $\mu$ AD044OportsIIL30 $\mu$ AD050I/O portsIIL+1 $\mu$ AVSS $\leq$ VPIN $\leq$ VDDD060I/O portsIIL+5 $\mu$ AVSS $\leq$ VPIN $\leq$ VDDD063OSC1+5 $\mu$ A <td< th=""><th>ion 13.1 and</th></td<>                                                                                                                  | ion 13.1 and  |

| Input Low Voltage<br>I/O portsVILVILVILVILVILVILVILD030with TTL bufferVILVSS- $0.8V$ VFor $4.5V \le VDD \le 5$ D031with Schmitt Trigger bufferVSS- $0.2VDD$ VotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)VSS- $0.2VDD$ VNote 1D033OSC1 (in XT and LP)VSS- $0.2VDD$ VNote 1D040with TTL bufferVIH0.3VDDVNote 1D040with TTL buffer0.25VDD +-VDDV $4.5V \le VDD \le 5.5V$ D040with TTL buffer0.8VDD-VDDVFor entire VDD ranD041with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD042MCLR, GP2/T0CKI0.8VDD-VDDVNote 1D043OSC1 (In EXTRC mode)0.9VDD-VDDVNote 1D043OSC1 (In EXTRC mode)0.9VDD-VDDVNote 1D043OSC1 (In EXTRC mode)IPUR30250400 $\mu A$ VDD = 5V, VPIN = VD070GPIO weak pull-up current (Notes 2, 3)IIL $\pm 1$ $\mu A$ VSS $\le VPIN \le VDD,$ D060I/O portsIIL $\pm 5$ $\mu A$ VSS $\le VPIN \le VDD,$ configurationD061TOCKI $\pm 5$ $\mu A$ VSS $\le VPIN \le VDD,$ configuration<                                          | ons           |

| I/O portsVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVIL <th></th>                                                                                                                                                                                                                                                                                                                                                                                                   |               |

| D030with TTL bufferVss- $0.8V$ VFor $4.5V \le Vbo \le 5$ D031with Schmitt Trigger bufferVss- $0.15Vbd$ VotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)Vss- $0.2Vbd$ VD033OSC1 (in EXTRC mode)Vss- $0.2Vbd$ VD033OSC1 (in XT and LP)Vss- $0.2Vbd$ Note 1D040Input High VoltageVIHVN0404 $0.25Vbd + 1$ VDDV $V$ $4.5V \le Vbd \le 5.5V$ D0404with Schmitt Trigger buffer $0.8Vbd + 2.0V$ VDDV $V$ D0404With Schmitt Trigger buffer $0.8Vbd + 2.0V$ VDDVFor entire VbD ranD0405With Schmitt Trigger buffer $0.8Vbd + 2.0V$ VDDVFor entire VbD ranD042MCLR, GP2/T0CKI $0.8Vbd + 2.0V$ VDDVFor entire VbD ranD043OSC1 (XT and LP) $0.7Vbd + 2.0V$ VDDVVD043OSC1 (in EXTRC mode) $0.9Vbd + 2.0V$ VDDVD070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu A$ VDD = 5V, VPIN = VD060I/O portsIIL30 $\mu A$ VDD = 5V, VPIN = VD060I/O portsIIL+5 $\mu A$ Vss $\leq VPIN \leq Vdd$ D061TOCKI+5 $\mu A$ Vss $\leq VPIN \leq Vdd$ D063OSC1Low Voltage-< |               |

| D031with Schmitt Trigger bufferVSS-0.15VDDVotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)VSS-0.2VDDVVD033OSC1 (in EXTRC mode)VSS-0.2VDDVNote 1D033OSC1 (in XT and LP)VSS-0.3VDDVNote 1D040with TTL bufferVIHD040with TTL buffer0.25VDD +-VDDV4.5V ≤ VDD ≤ 5.5VD040AWith Schmitt Trigger buffer0.8VDD-VDDV4.5V ≤ VDD ≤ 5.5VD041with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD042MCLR, GP2/T0CKI0.8VDD-VDDVNote 1D043OSC1 (in EXTRC mode)0.7VDD-VDDVNote 1D043OSC1 (in EXTRC mode)0.9VDD-VDDVNote 1D070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu$ AVDD = 5V, VPIN = VD060I/O portsIIL30 $\mu$ AVDS ≤ VPIN ≤ VDD, configurationD061T0CKI+5 $\mu$ AVSS ≤ VPIN ≤ VDD, configurationD080I/O portsVOL0.6VIoL = 8.5 mA, VDD                                                                                                                                                                                                        |               |

| D031with Schmitt Trigger buffer<br>MCLR, GP2/T0CKI (in EXTRC mode)Vss-0.2VDDVD033OSC1 (in EXTRC mode)Vss-0.2VDDVD033OSC1 (in XT and LP)Vss-0.2VDDVD040with TL bufferVIHD040with Schmitt Trigger buffer0.25VDD +-VDDVD040with Schmitt Trigger buffer0.8VDD-VDDVD041with Schmitt Trigger buffer0.8VDD-VDDVD042MCLR, GP2/T0CKI0.8VDD-VDDVD043OSC1 (in EXTRC mode)0.7VDD-VDDVD043OSC1 (in EXTRC mode)0.9VDD-VDDVD043OSC1 (in EXTRC mode)0.9VDD-VDDVD070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu$ AVDD = 5V, VPIN = VD060I/O portsIIL30 $\mu$ AVDS ≤ VPIN ≤ VDD, impedanceD061T0CKI $\pm 5$ $\mu$ AVss ≤ VPIN ≤ VDD, configurationD080I/O portsVOL $0.6$ VIoL = 8.5 mA, VDD                                                                                                                                                                                                                                                             | .5V           |

| D032 $\overline{MCLR}$ , GP2/T0CKI (in EXTRC mode)Vss-0.2VDDVD033OSC1 (in EXTRC mode)Vss-0.2VDDNote 1D033OSC1 (in XT and LP)Vss-0.3VDDVNote 1Input High Voltage<br>I/O portsVIHD040with TTL buffer0.25VDD +-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD040with Schmitt Trigger buffer0.8VDD-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD041with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD042MCLR, GP2/T0CKI0.8VDD-VDDVFor entire VDD ranD043OSC1 (XT and LP)0.7VDD-VDDVNote 1D043OSC1 (in EXTRC mode)1PUR30250400 $\mu$ AVDD $=$ 5V, VPIN $=$ ND070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu$ AVDD $=$ 5V, VPIN $=$ ND060I/O portsIIL $\pm$ 1 $\mu$ AVss $\leq$ VPIN $\leq$ VDD, impedanceD061T0CKI $\pm$ 5 $\mu$ AVss $\leq$ VPIN $\leq$ VDD, configurationD080I/O portsVolt $\pm$ 5 $\mu$ AVss $\leq$ VPIN $\leq$ VDD, configuration                                                                                                          |               |

| D033OSC1 (in EXTRC mode)Viss-0.2VDDNote 1D033OSC1 (in XT and LP)Vss-0.3VDDVNote 1Input High Voltage<br>I/O portsVIHVDDV4.5V $\leq$ VDD $\leq$ 5.5VD040with TTL buffer0.25VDD +<br>0.8V-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD040with Schmitt Trigger buffer0.20V-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD041with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD042MCLR, GP2/TOCKI0.8VDD-VDDVFor entire VDD ranD043OSC1 (XT and LP)0.7VDD-VDDVNote 1D043OSC1 (in EXTRC mode)0.9VDD-VDDVNote 1D070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu$ AVDE $=$ 5V, VPIN $=$ ND060I/O portsIIIL30 $\mu$ AVDE $=$ 5V, VPIN $\leq$ NDDD060I/O portsIIIL $\pm$ 5 $\mu$ AVss $\leq$ VPIN $\leq$ VDDD061TOCKI $\pm$ 5 $\mu$ AVss $\leq$ VPIN $\leq$ VDDD063OSC1 $\pm$ 5 $\mu$ AVss $\leq$ VPIN $\leq$ VDDD080I/O portsVolt0.6VIOI/O portsVOL0.6VIoL = 8.5 mA, VDD                                                                                            |               |

| D033OSC1 (in XT and LP)Vss-0.3VDDVNote 1Input High Voltage<br>I/O portsVIHD040with TTL buffer0.25VDD +<br>0.8V-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD040with Schmitt Trigger buffer0.8VD-VDDVotherwiseD041with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD042MCLR, GP2/T0CKI0.8VDD-VDDVFor entire VDD ranD043OSC1 (XT and LP)0.7VDD-VDDVNote 1D043OSC1 (in EXTRC mode)0.9VDD-VDDVVD070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu$ AVDE = 5V, VPIN = ND060I/O portsIIIL30 $\mu$ AVDS $\leq$ VPIN $\leq$ VDDD061T0CKI $\pm 5$ $\mu$ AVss $\leq$ VPIN $\leq$ VDDconfigurationD063OSC1 $\pm 5$ $\mu$ AVss $\leq$ VPIN $\leq$ VDDD080I/O portsVOL $\pm 5$ $\mu$ AVss $\leq$ VPIN $\leq$ VDD                                                                                                                                                                                                                                            |               |

| Input High Voltage<br>I/O portsVIHD040with TTL buffer $0.25VDD + -$ VDDVD040A $2.0V -$ VDDVD041with Schmitt Trigger buffer $0.8VDD -$ VDDVD042MCLR, GP2/T0CKI $0.8VDD -$ VDDVD043OSC1 (XT and LP) $0.7VDD -$ VDDVD043OSC1 (in EXTRC mode) $0.9VDD -$ VDDVD070GPIO weak pull-up current (Note 4)IPUR30250400 $\muA$ MCLR pull-up current30 $\muA$ VDD = 5V, VPIN = VD060I/O portsIIL $\pm 1$ $\muA$ Vss $\leq$ VPIN $\leq$ VDD, impedanceD061T0CKI $\pm 5$ $\muA$ Vss $\leq$ VPIN $\leq$ VDD, impedanceD063OSC1 $\pm 5$ $\muA$ Vss $\leq$ VPIN $\leq$ VDD, impedanceD080I/O portsVOL $0.6$ VIOL = 8.5 mA, VDD                                                                                                                                                                                                                                                                                                                                  |               |

| I/O portsVIHD040with TTL buffer0.25VDD +-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD040A2.0V-VDDV0 otherwiseD041with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD042MCLR, GP2/T0CKI0.8VDD-VDDVFor entire VDD ranD043OSC1 (XT and LP)0.7VDD-VDDVNote 1D043OSC1 (in EXTRC mode)0.9VDD-VDDVVD070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu$ AVDD = 5V, VPIN = VD070Input Leakage Current (Notes 2, 3)IIL30 $\mu$ AVDD = 5V, VPIN = VD061T0CKI $\pm 5$ $\mu$ AVss $\leq$ VPIN $\leq$ VDD,impedanceD061T0CKI $\pm 5$ $\mu$ AVss $\leq$ VPIN $\leq$ VDD,impedanceD080I/O portsVOL $\pm 5$ $\mu$ AVss $\leq$ VPIN $\leq$ VDD,D080I/O portsVOL $\pm 5$ $\mu$ AVss $\leq$ VPIN $\leq$ VDD,                                                                                                                                                                                                                                                       |               |

| D040with TTL buffer $0.25VDD + 0.8V$ $ VDD$ $V$ $4.5V \le VDD \le 5.5V$ D040A $2.0V$ $ VDD$ $V$ otherwiseD041with Schmitt Trigger buffer $0.8VDD$ $ VDD$ $V$ For entire VDD ranD042 $MCLR, GP2/TOCKI$ $0.8VDD$ $ VDD$ $V$ For entire VDD ranD043OSC1 (XT and LP) $0.7VDD$ $ VDD$ $V$ D043OSC1 (in EXTRC mode) $0.9VDD$ $ VDD$ $V$ D070GPIO weak pull-up current (Note 4)IPUR $30$ $250$ $400$ $\muA$ $VDD = 5V, VPIN = V$ D060I/O portsIIL $   30$ $\muA$ $VDD = 5V, VPIN = V$ D061TOCKI $  \pm 5$ $\muA$ $Vss \le VPIN \le VDD,$ D063OSC1 $  \pm 5$ $\muA$ $Vss \le VPIN \le VDD,$ D080I/O ports $VDL$ $  0.6$ $V$ D080I/O ports $VOL$ $  0.6$ $V$                                                                                                                                                                                                                                                                                           |               |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | je            |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |