Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 768B (512 x 12)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 25 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 8-SOIJ                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c508at-04-sm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

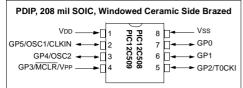

### Pin Diagram - PIC12C508/509

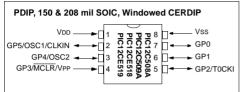

### Pin Diagram - PIC12C508A/509A, PIC12CE518/519

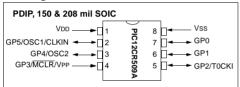

### Pin Diagram - PIC12CR509A

### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12C5XX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C5XX uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12-bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (1µs @ 4MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), ROM memory, and non-volatile (EEPROM) for each device.

|             | Memory           |                |             |                |  |  |  |  |

|-------------|------------------|----------------|-------------|----------------|--|--|--|--|

| Device      | EPROM<br>Program | ROM<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |

| PIC12C508   | 512 x 12         |                | 25          |                |  |  |  |  |

| PIC12C509   | 1024 x 12        |                | 41          |                |  |  |  |  |

| PIC12C508A  | 512 x 12         |                | 25          |                |  |  |  |  |

| PIC12C509A  | 1024 x 12        |                | 41          |                |  |  |  |  |

| PIC12CR509A |                  | 1024 x 12      | 41          |                |  |  |  |  |

| PIC12CE518  | 512 x 12         |                | 25 x 8      | 16 x 8         |  |  |  |  |

| PIC12CE519  | 1024 x 12        |                | 41 x 8      | 16 x 8         |  |  |  |  |

The PIC12C5XX can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC12C5XX has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C5XX simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC12C5XX device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1.

| Name           | DIP<br>Pin # | SOIC<br>Pin # | l/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|--------------|---------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0            | 7            | 7             | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming data. Can<br>be software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming<br>mode.                                                                                                                                                                                                               |

| GP1            | 6            | 6             | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming clock. Can<br>be software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming<br>mode.                                                                                                                                                                                                              |

| GP2/T0CKI      | 5            | 5             | I/O           | ST             | Bi-directional I/O port. Can be configured as T0CKI.                                                                                                                                                                                                                                                                                                                                                                                                |

| GP3/MCLR/Vpp   | 4            | 4             | Ι             | TTL/ST         | Input port/master clear (reset) input/programming volt-<br>age input. When configured as MCLR, this pin is an<br>active low reset to the device. Voltage on MCLR/VPP<br>must not exceed VDD during normal device operation<br>or the device will enter programming mode. Can be<br>software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. Weak pull-up<br>always on if configured as MCLR. ST when in MCLR<br>mode. |

| GP4/OSC2       | 3            | 3             | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output. Con-<br>nections to crystal or resonator in crystal oscillator<br>mode (XT and LP modes only, GPIO in other modes).                                                                                                                                                                                                                                                                              |

| GP5/OSC1/CLKIN | 2            | 2             | I/O           | TTL/ST         | Bidirectional IO port/oscillator crystal input/external<br>clock source input (GPIO in Internal RC mode only,<br>OSC1 in all other oscillator modes). TTL input when<br>GPIO, ST input in external RC oscillator mode.                                                                                                                                                                                                                              |

| Vdd            | 1            | 1             | Р             | _              | Positive supply for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vss            | 8            | 8             | Р             | _              | Ground reference for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                                             |

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input

### 3.1 Clocking Scheme/Instruction Cycle

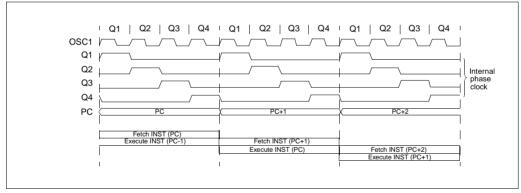

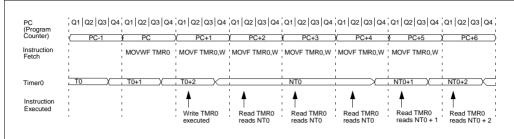

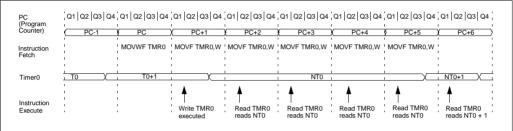

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

### 3.2 Instruction Flow/Pipelining

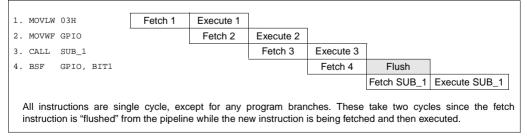

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The special registers can be classified into two sets. The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

### TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

|                    |                                                                                     |                             |                                     |             |           |                        |              |         |       | Value on<br>Power-On | Value on<br>All Other    |

|--------------------|-------------------------------------------------------------------------------------|-----------------------------|-------------------------------------|-------------|-----------|------------------------|--------------|---------|-------|----------------------|--------------------------|

| Address            | Name                                                                                | Bit 7                       | Bit 6                               | Bit 5       | Bit 4     | Bit 3                  | Bit 2        | Bit 1   | Bit 0 | Reset                | Resets <sup>(2)</sup>    |

| N/A                | TRIS                                                                                | —                           | I                                   |             |           |                        |              |         |       | 11 1111              | 11 1111                  |

| N/A                | OPTION                                                                              | Contains co<br>prescaler, v |                                     |             |           | Timer0/WD1<br>pull-ups | Г            |         |       | 1111 1111            | 1111 1111                |

| 00h                | INDF                                                                                | Uses conte                  | ents of FSR                         | R to addres | s data me | mory (not a            | physical reg | jister) |       | xxxx xxxx            | uuuu uuuu                |

| 01h                | TMR0                                                                                | 8-bit real-ti               | me clock/c                          | ounter      |           |                        |              |         |       | xxxx xxxx            | uuuu uuuu                |

| 02h <sup>(1)</sup> | PCL                                                                                 | Low order                   | B bits of PC                        | c           |           |                        |              |         |       | 1111 1111            | 1111 1111                |

| 03h                | STATUS                                                                              | GPWUF                       | -                                   | PA0         | TO        | PD                     | Z            | DC      | С     | 0001 1xxx            | q00q quuu <sup>(3)</sup> |

| 04h                | FSR<br>(PIC12C508/<br>PIC12C508A/<br>PIC12C518)                                     | Indirect dat                | a memory                            | address p   | pointer   | L                      | L            | 1       | 1     | 111x xxxx            | 111u uuuu                |

| 04h                | FSR<br>(PIC12C509/<br>PIC12C509A/<br>PIC12CR509A/<br>PIC12CE519)                    | Indirect dat                | ndirect data memory address pointer |             |           |                        |              |         |       | 110x xxxx            | 11uu uuuu                |

| 05h                | OSCCAL<br>(PIC12C508/<br>PIC12C509)                                                 | CAL3                        | CAL2                                | CAL1        | CAL0      | _                      | _            | _       | _     | 0111                 | uuuu                     |

| 05h                | OSCCAL<br>(PIC12C508A/<br>PIC12C509A/<br>PIC12CE518/<br>PIC12CE519/<br>PIC12CR509A) | CAL5                        | CAL4                                | CAL3        | CAL2      | CAL1                   | CAL0         |         | _     | 1000 00              | uuuu uu                  |

| 06h                | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12C509A)      | _                           | _                                   | GP5         | GP4       | GP3                    | GP2          | GP1     | GP0   | xx xxxx              | uu uuuu                  |

| 06h                | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                                 | SCL                         | SDA                                 | GP5         | GP4       | GP3                    | GP2          | GP1     | GP0   | 11xx xxxx            | 11uu uuuu                |

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as '0' (if applicable)

x = unknown, u = unchanged, q = see the tables in Section 8.7 for possible values.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 for an explanation of how to access these bits.

2: Other (non power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

3: If reset was due to wake-up on pin change then bit 7 = 1. All other resets will cause bit 7 = 0.

### 4.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status, and the page preselect bit for program memories larger than 512 words.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS register because these instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions, which do affect STATUS bits, see Instruction Set Summary.

### FIGURE 4-4: STATUS REGISTER (ADDRESS:03h)

| <u>R/W-0</u><br>GPWUF | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0<br>PA0                                           | <u>R-1</u><br>TO                               | R-1<br>PD                          | R/W-x<br>Z                                     | R/W-x<br>DC | R/W-x<br>C                    | R = Readable bit                                   |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|------------------------------------|------------------------------------------------|-------------|-------------------------------|----------------------------------------------------|

| t7                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                      | 4                                              | 3                                  | 2                                              | 1           | bit0                          | W = Writable bit<br>- n = Value at POR reset       |

|                       | <b>GPWUF</b> : G<br>1 = Reset o<br>0 = After po                                                                                                                                                                                                                                                                                                                                                                              | due to wake                                            | -up from S                                     | LEEP on pi                         | n change                                       |             |                               |                                                    |

| it 6:                 | Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                     | ented                                                  |                                                |                                    |                                                |             |                               |                                                    |

|                       | 0 = Page 0<br>Each page<br>Using the F                                                                                                                                                                                                                                                                                                                                                                                       | (200h - 3F<br>(000h - 1F<br>is 512 byte<br>A0 bit as a | Fh) - PIC12<br>Fh) - PIC12<br>s.<br>general pu | 2C509, PIC<br>2C5XX<br>irpose read |                                                | evices whic | h do not use                  | 2CE519<br>e it for program<br>ith future products. |

|                       | <b>TO</b> : Time-o<br>1 = After po<br>0 = A WDT                                                                                                                                                                                                                                                                                                                                                                              | ower-up, CL                                            |                                                | uction, or S                       | LEEP instruc                                   | tion        |                               |                                                    |

|                       | PD: Power-down bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                                                                                           |                                                        |                                                |                                    |                                                |             |                               |                                                    |

|                       | <ul> <li>Z: Zero bit</li> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                                                                                                                                                                                                                  |                                                        |                                                |                                    |                                                |             |                               |                                                    |

|                       | <ul> <li>DC: Digit carry/borrow bit (for ADDWF and SUBWF instructions)</li> <li>ADDWF</li> <li>1 = A carry from the 4th low order bit of the result occurred</li> <li>0 = A carry from the 4th low order bit of the result did not occur</li> <li>SUBWF</li> <li>1 = A borrow from the 4th low order bit of the result did not occur</li> <li>0 = A borrow from the 4th low order bit of the result did not occur</li> </ul> |                                                        |                                                |                                    |                                                |             |                               |                                                    |

|                       | ADDWF<br>1 = A carry                                                                                                                                                                                                                                                                                                                                                                                                         |                                                        |                                                | SUBWF<br>1 = A bor                 | RF, RLF instr<br>row did not c<br>row occurred | occur       | <b>RRF or R</b><br>Load bit w | LF<br>vith LSB or MSB, respectively                |

### 5.0 I/O PORT

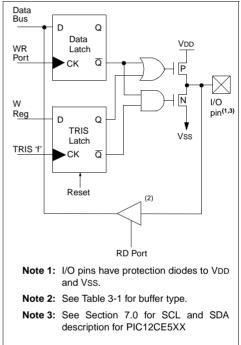

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

### 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the output data latches. That is, if an output      |

|-------|---------------------------------------------------------------------------------------------|

|       | driver on a pin is enabled and driven high,                                                 |

|       | but the external system is holding it low, a read of the port will indicate that the pin is |

|       | low.                                                                                        |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

### FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6      | Bit 5     | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|----------|------------|-----------|----------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 01h     | TMR0   | Timer0 - | 8-bit real | -time clo | ck/count | er    |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| N/A     | OPTION | GPWU     | GPPU       | T0CS      | T0SE     | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | TRIS   | —        |            | GP5       | GP4      | GP3   | GP2   | GP1   | GP0   | 11 1111                       | 11 1111                         |

Legend: Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged,

### 7.3 WRITE OPERATIONS

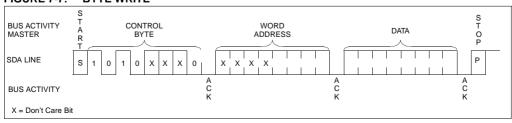

### 7.3.1 BYTE WRITE

Following the start signal from the master, the device code (4 bits), the don't care bits (3 bits), and the R/Wbit (which is a logic low) are placed onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the master is the word address and will be written into the address pointer. Only the lower four address bits are used by the device, and the upper four bits are don't cares. The address byte is acknowledgeable and the master device will then transmit the data word to be written into the addressed memory location. The memorv acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time will not generate acknowledge signals (Figure 7-7). After a byte write command, the internal address counter will not be incremented and will point to the same address location that was just written. If a stop bit is transmitted to the device at any point in the write command sequence before the entire sequence is complete, then the command will abort and no data will be written. If more than 8 data bits are transmitted before the stop bit is sent, then the device will clear the previously loaded byte and begin loading the data buffer again. If more than one data byte is transmitted to the device and a stop bit is sent before a full eight data bits have been transmitted, then the write command will abort and no data will be written. The EEPROM memory employs a Vcc threshold detector circuit which disables the internal erase/write logic if the Vcc is below minimum VDD.

Byte write operations must be preceded and immediately followed by a bus not busy bus cycle where both SDA and SCL are held high.

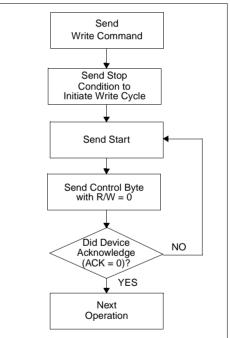

### 7.4 ACKNOWLEDGE POLLING

Since the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the master, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master sending a start condition followed by the control byte for a write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-6 for flow diagram.

### FIGURE 7-6: ACKNOWLEDGE POLLING FLOW

FIGURE 7-7: BYTE WRITE

### 8.2 Oscillator Configurations

### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

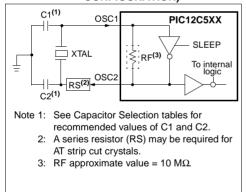

### 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

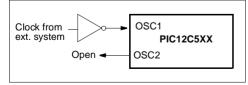

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 8-4 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

### FIGURE 8-4: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

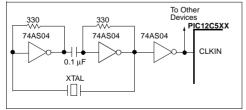

Figure 8-5 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 8-5: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

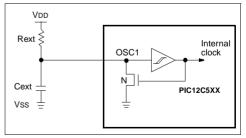

### 8.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 8-6 shows how the R/C combination is connected to the PIC12C5XX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

## FIGURE 8-6: EXTERNAL RC OSCILLATOR MODE

# PIC12C5XX

| MOVF                 | Move f                                                                                                                                                                                                                               |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:              | [label] MOVF f,d                                                                                                                                                                                                                     |  |  |  |  |

| Operands:            | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                            |  |  |  |  |

| Operation:           | $(f) \rightarrow (dest)$                                                                                                                                                                                                             |  |  |  |  |

| Status Affected:     | Z                                                                                                                                                                                                                                    |  |  |  |  |

| Encoding:            | 0010 00df ffff                                                                                                                                                                                                                       |  |  |  |  |

| Description:         | The contents of register 'f' is moved to destination 'd'. If 'd' is 0, destination is the W register. If 'd' is 1, the destination is file register 'f'. 'd' is 1 is useful to test a file register since status flag Z is affected. |  |  |  |  |

| Words:               | 1                                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:              | 1                                                                                                                                                                                                                                    |  |  |  |  |

| Example:             | MOVF FSR, 0                                                                                                                                                                                                                          |  |  |  |  |

| After Instruc<br>W = | tion<br>value in FSR register                                                                                                                                                                                                        |  |  |  |  |

| MOVLW                | Move Literal to W                                                                             |       |      |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------|-------|------|--|--|--|--|--|

| Syntax:              | [ label ]                                                                                     | MOVLW | k    |  |  |  |  |  |

| Operands:            | $0 \le k \le 255$                                                                             |       |      |  |  |  |  |  |

| Operation:           | $k \rightarrow (W)$<br>None                                                                   |       |      |  |  |  |  |  |

| Status Affected:     |                                                                                               |       |      |  |  |  |  |  |

| Encoding:            | 1100                                                                                          | kkkk  | kkkk |  |  |  |  |  |

| Description:         | The eight bit literal 'k' is loaded into the W register. The don't cares will assemble as 0s. |       |      |  |  |  |  |  |

| Words:               | 1                                                                                             |       |      |  |  |  |  |  |

| Cycles:              | 1                                                                                             |       |      |  |  |  |  |  |

| Example:             | MOVLW                                                                                         | 0x5A  |      |  |  |  |  |  |

| After Instruc<br>W = | tion<br>0x5A                                                                                  |       |      |  |  |  |  |  |

| MOVWF                         | Move W to f           |              |            |           |  |  |  |

|-------------------------------|-----------------------|--------------|------------|-----------|--|--|--|

| Syntax:                       | [label] MOVWF f       |              |            |           |  |  |  |

| Operands:                     | $0 \le f \le 31$      |              |            |           |  |  |  |

| Operation:                    | $(W) \rightarrow (f)$ |              |            |           |  |  |  |

| Status Affected:              | None                  |              |            |           |  |  |  |

| Encoding:                     | 0000                  | 001f         | ffff       |           |  |  |  |

| Description:                  | Move data<br>ter 'f'. | a from the V | W register | to regis- |  |  |  |

| Words:                        | 1                     |              |            |           |  |  |  |

| Cycles:                       | 1                     |              |            |           |  |  |  |

| Example:                      | MOVWF                 | TEMP_REC     | 3          |           |  |  |  |

| Before Instru<br>TEMP_R<br>W  |                       | 0xFF<br>0x4F |            |           |  |  |  |

| After Instruct<br>TEMP_R<br>W |                       | 0x4F<br>0x4F |            |           |  |  |  |

| NOP              | No Operation |        |      |  |  |  |  |

|------------------|--------------|--------|------|--|--|--|--|

| Syntax:          | [label] NOP  |        |      |  |  |  |  |

| Operands:        | None         |        |      |  |  |  |  |

| Operation:       | No operation |        |      |  |  |  |  |

| Status Affected: | None         |        |      |  |  |  |  |

| Encoding:        | 0000         | 0000   | 0000 |  |  |  |  |

| Description:     | No opera     | ation. |      |  |  |  |  |

| Words:           | 1            |        |      |  |  |  |  |

| Cycles:          | 1            |        |      |  |  |  |  |

| Example:         | NOP          |        |      |  |  |  |  |

# PIC12C5XX

| OPTION                   | Load OPTION Register                                            |        |      |  |  |  |

|--------------------------|-----------------------------------------------------------------|--------|------|--|--|--|

| Syntax:                  | [ label ]                                                       | OPTION | l    |  |  |  |

| Operands:                | None                                                            |        |      |  |  |  |

| Operation:               | $(W)\toO$                                                       | PTION  |      |  |  |  |

| Status Affected:         | None                                                            |        |      |  |  |  |

| Encoding:                | 0000                                                            | 0000   | 0010 |  |  |  |

| Description:             | The content of the W register is load into the OPTION register. |        |      |  |  |  |

| Words:                   | 1                                                               |        |      |  |  |  |

| Cycles:                  | 1                                                               |        |      |  |  |  |

| Example                  | OPTION                                                          |        |      |  |  |  |

| Before Instru<br>W       | ction<br>= 0x07                                                 |        |      |  |  |  |

| After Instruct<br>OPTION |                                                                 |        |      |  |  |  |

| RETLW                 | Return with Literal in W                                               |                  |                                                                                 |  |  |  |  |

|-----------------------|------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|--|--|--|--|

| Syntax:               | [label] RE                                                             | TLW              | k                                                                               |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                      |                  |                                                                                 |  |  |  |  |

| Operation:            | $\begin{array}{l} k \rightarrow (W);\\ TOS \rightarrow PC \end{array}$ |                  |                                                                                 |  |  |  |  |

| Status Affected:      | None                                                                   |                  |                                                                                 |  |  |  |  |

| Encoding:             | 1000 kł                                                                | kk               | kkkk                                                                            |  |  |  |  |

| Description:          | bit literal 'k'. T<br>loaded from th                                   | he pro<br>ne top | aded with the eight<br>gram counter is<br>of the stack (the<br>s is a two cycle |  |  |  |  |

| Words:                | 1                                                                      |                  |                                                                                 |  |  |  |  |

| Cycles:               | 2                                                                      |                  |                                                                                 |  |  |  |  |

| Example:              | CALL TABLE                                                             | ;tab<br>;val     | le offset<br>ue.<br>ow has table                                                |  |  |  |  |

| TABLE                 | ADDWF PC<br>RETLW k1<br>RETLW k2                                       | ; Beg            | offset<br>in table<br>d of table                                                |  |  |  |  |

| Before Instru<br>W =  | ox07                                                                   |                  |                                                                                 |  |  |  |  |

| After Instruct<br>W = | tion<br>value of k8                                                    |                  |                                                                                 |  |  |  |  |

| RLF                                                                                                                                                | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                            | [label] RLF f,d                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                                                                          | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                               |

| Operation:                                                                                                                                         | See description below                                                                                                                                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                                                                                   | С                                                                                                                                                                                                                                                                                                                                                                                                          |

| Encoding:                                                                                                                                          | 0011 01df ffff                                                                                                                                                                                                                                                                                                                                                                                             |

| Description:                                                                                                                                       | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is stored<br>back in register 'f'.                                                                                                                                                                                                |

| Words:                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                          |

| Cycles:                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                          |

| Example:                                                                                                                                           | RLF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                 |

| Before Instru                                                                                                                                      | iction                                                                                                                                                                                                                                                                                                                                                                                                     |

| REG1<br>C                                                                                                                                          | = 1110 0110<br>= 0                                                                                                                                                                                                                                                                                                                                                                                         |

| After Instruct                                                                                                                                     | tion                                                                                                                                                                                                                                                                                                                                                                                                       |

| REG1<br>W                                                                                                                                          | = 1110 0110<br>= 1100 1100                                                                                                                                                                                                                                                                                                                                                                                 |

| C                                                                                                                                                  | = 1                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRF                                                                                                                                                | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                               |

| RRF<br>Syntax:                                                                                                                                     | Rotate Right f through Carry<br>[ label ] RRF f,d                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Syntax:                                                                                                                                            | [ <i>label</i> ] RRF f,d<br>0 ≤ f ≤ 31                                                                                                                                                                                                                                                                                                                                                                     |

| Syntax:<br>Operands:                                                                                                                               | $\begin{bmatrix} label \end{bmatrix} RRF f,d$<br>$0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                         |

| Syntax:<br>Operands:<br>Operation:                                                                                                                 | $ \begin{bmatrix} label \end{bmatrix} RRF f,d \\ 0 \le f \le 31 \\ d \in [0,1] \\ See description below $                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                                             | $ [label] RRF f,d  0 \le f \le 31  d \in [0,1]  See description below  C  0011 00df ffff  The contents of register 'f' are rotated  one bit to the right through the Carry  Flag. If 'd' is 0 the result is placed in the  W register. If 'd' is 1 the result is placed  back in register 'f'.$                                                                                                            |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                                | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                    |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                      | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>T                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                           | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011  00df  ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>$c \rightarrow register 'f' \rightarrow 1$<br>1                         |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                      | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>T                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                           | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1,0                                                       |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instru-<br>REG1     | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>C register 'f'<br>1<br>1<br>RRF REG1,0<br>interimed<br>= 1110 0110<br>= 0 |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instru<br>REG1<br>C | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1,0<br>interimed<br>= 1110 0110<br>= 0                    |

### 11.0 ELECTRICAL CHARACTERISTICS - PIC12C508/PIC12C509

### Absolute Maximum Ratings†

| Ambient Temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40°C to +125°C                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|