Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 768B (512 x 12)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 25 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                               |

| Supplier Device Package    | 8-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c508at-04-sn |

#### 2.0 PIC12C5XX DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12C5XX Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in ceramic side brazed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

Microchip's PICSTART® PLUS and PRO MATE® programmers all support programming of the PIC12C5XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> Production (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

#### 2.5 Read Only Memory (ROM) Device

Microchip offers masked ROM to give the customer a low cost option for high volume, mature products.

**NOTES:**

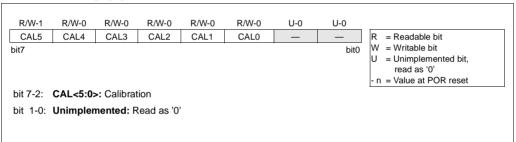

#### 4.5 OSCCAL Register

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal 4 MHz oscillator. It contains four to six bits for calibration. Increasing the cal value increases the frequency. See Section 7.2.5 for more information on the internal oscillator.

#### FIGURE 4-6: OSCCAL REGISTER (ADDRESS 05h) FOR PIC12C508 AND PIC12C509

| R/W-0<br>CAL3 | R/W-1<br>CAL2 | R/W-1<br>CAL1 | R/W-1<br>CAL0 | R/W-0 | R/W-0 | U-0 | U-0  | R = Readable bit                                                             |

|---------------|---------------|---------------|---------------|-------|-------|-----|------|------------------------------------------------------------------------------|

| oit7          |               | 1             | 1             |       |       |     | bit0 | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7-4:      | CAL<3:0       | >: Calibrat   | tion          |       |       |     |      |                                                                              |

|               | Unimpler      | mantad. F     | ) and an 'O'  |       |       |     |      |                                                                              |

#### FIGURE 4-7: OSCCAL REGISTER (ADDRESS 05h) FOR PIC12C508A/C509A/CR509A/12CE518/ 12CE519

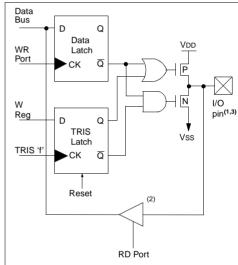

#### 5.0 I/O PORT

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CF5XX

#### 5.1 **GPIO**

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

Note: A read of the ports reads the pins, not the output data latches. That is, if an output driver on a pin is enabled and driven high, but the external system is holding it low, a read of the port will indicate that the pin is low.

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

#### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

- Note 1: I/O pins have protection diodes to VDD and Vss.

- Note 2: See Table 3-1 for buffer type.

- Note 3: See Section 7.0 for SCL and SDA description for PIC12CE5XX

NOTES:

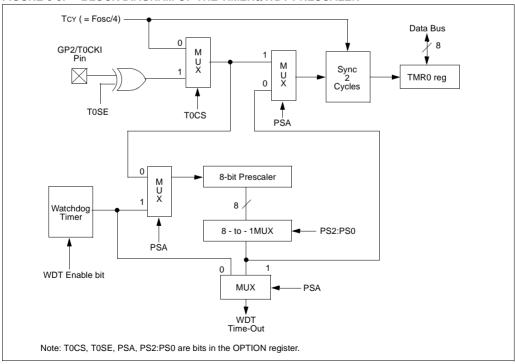

#### 6.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 8.6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1,x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

#### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

## EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

1.CLRWDT ;Clear WDT

2.CLRF TMR0 ;Clear TMR0 & Prescaler

3.MOVLW '00xx1111'b ;These 3 lines (5, 6, 7)

4.OPTION ; are required only if ; desired

5.CLRWDT ;PS<2:0> are 000 or 001

6.MOVLW '00xx1xxx'b ;Set Postscaler to 7.OPTION ; desired WDT rate

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

## EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

CLRWDT ;Clear WDT and ;prescaler

MOVLW 'xxxx0xxx' ;Select TMR0, new ;prescale value and ;clock source

OPTION

FIGURE 6-5: BLOCK DIAGRAM OF THE TIMERO/WDT PRESCALER

# 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC12C5XX family of microcontrollers has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- · Oscillator selection

- Reset

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from SLEEP on pin change

- · Watchdog Timer (WDT)

- SLEEP

- · Code protection

- · ID locations

- · In-circuit Serial Programming

The PIC12C5XX has a Watchdog Timer which can be shut off only through configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in reset until the crystal oscillator is stable. If using INTRC or EXTRC there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 8.1 Configuration Bits

The PIC12C5XX configuration word consists of 12 bits. Configuration bits can be programmed to select various device configurations. Two bits are for the selection of the oscillator type, one bit is the Watchdog Timer enable bit, and one bit is the MCLR enable bit.

#### FIGURE 8-1: CONFIGURATION WORD FOR PIC12C5XX

| _         | _                          | _                                                                               | _                            | _        | _     | _ | MCLRE                        | CP | WDTE | FOSC1 | FOSC0 | Register:                | CONFIC |

|-----------|----------------------------|---------------------------------------------------------------------------------|------------------------------|----------|-------|---|------------------------------|----|------|-------|-------|--------------------------|--------|

| bit11     | 10                         | 9                                                                               | 8                            | 7        | 6     | 5 | 4                            | 3  | 2    | 1     | bit0  | Address <sup>(1)</sup> : | FFF    |

| bit 11-5: | Unim                       | plemente                                                                        | ed                           |          |       |   |                              |    |      |       |       |                          |        |

| bit 4:    | 1 = M                      | MCLRE: MCLR enable bit. 1 = MCLR pin enabled 0 = MCLR tied to VDD, (Internally) |                              |          |       |   |                              |    |      |       |       |                          |        |

| bit 3:    | 1 = C                      | CP: Code protection bit.  I = Code protection off  D = Code protection on       |                              |          |       |   |                              |    |      |       |       |                          |        |

| bit 2:    | 1 = W                      | WDTE: Watchdog timer enable bit  1 = WDT enabled  0 = WDT disabled              |                              |          |       |   |                              |    |      |       |       |                          |        |

| bit 1-0:  | 11 = E<br>10 = I<br>01 = 2 | <b>1:FOSC</b><br>EXTRC -<br>NTRC - i<br>(T oscilla<br>.P oscilla                | external<br>nternal F<br>tor | RC oscil | lator |   |                              |    |      |       |       |                          |        |

| Note 1:   |                            |                                                                                 |                              | _        | _     |   | ations to de<br>Iressable du |    |      |       | ie    |                          |        |

#### 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

LP: Low Power Crystal

XT: Crystal/Resonator

INTRC: Internal 4 MHz Oscillator

EXTRC: External Resistor/Capacitor

## 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

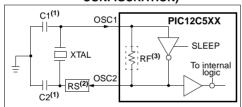

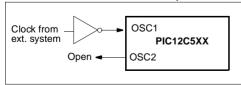

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/OSC1/CLKIN pin (Figure 8-3).

FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

Note 1: See Capacitor Selection tables for recommended values of C1 and C2.

- 2: A series resistor (RS) may be required for AT strip cut crystals.

- 3: RF approximate value = 10 M $\Omega$ .

FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      |            |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 8.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and 25°C, see "Electrical Specifications" section for information on variation over voltage and temperature.

In addition, a calibration instruction is programmed into the top of memory which contains the calibration value for the internal RC oscillator. This location is never code protected regardless of the code protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the reset vector. This will load the W register with the calibration value upon reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

Note

Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part. so it can be reprogrammed correctly later.

For the PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, and PIC12CR509A, bits <7:2>, CAL5-CAL0 are used for calibration. Adjusting CAL5-0 from 00000 to 111111 yields a higher clock speed. Note that bits 1 and 0 of OSCCAL are unimplemented and should be written as 0 when modifying OSCCAL for compatibility with future devices.

For the PIC12C508 and PIC12C509, the upper 4 bits of the register are used. Writing a larger value in this location yields a higher clock speed.

#### 8.3 RESET

The device differentiates between various kinds of reset:

- a) Power on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT time-out reset during normal operation

- e) WDT time-out reset during SLEEP

- f) Wake-up from SLEEP on pin change

Some registers are not reset in any way; they are unknown on POR and unchanged in any other reset. Most other registers are reset to "reset state" on poweron reset (POR),  $\overline{\text{MCLR}}$ , WDT or wake-up on pin change reset during normal operation. They are not affected by a WDT reset during SLEEP or  $\overline{\text{MCLR}}$  reset during SLEEP, since these resets are viewed as resumption of normal operation. The exceptions to this are  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits. They are set or cleared differently in different reset situations. These bits are used in software to determine the nature of reset. See Table 8-3 for a full description of reset states of all registers.

#### 9.0 INSTRUCTION SET SUMMARY

Each PIC12C5XX instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC12C5XX instruction set summary in Table 9-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                        |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| f             | Register file address (0x00 to 0x7F)                                                                                                                               |  |  |  |  |  |  |

| W             | Working register (accumulator)                                                                                                                                     |  |  |  |  |  |  |

| b             | Bit address within an 8-bit file register                                                                                                                          |  |  |  |  |  |  |

| k             | Literal field, constant data or label                                                                                                                              |  |  |  |  |  |  |

| x             | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |  |  |

| d             | Destination select; d = 0 (store result in W) d = 1 (store result in file register 'f') Default is d = 1                                                           |  |  |  |  |  |  |

| label         | Label name                                                                                                                                                         |  |  |  |  |  |  |

| TOS           | Top of Stack                                                                                                                                                       |  |  |  |  |  |  |

| PC            | Program Counter                                                                                                                                                    |  |  |  |  |  |  |

| WDT           | Watchdog Timer Counter                                                                                                                                             |  |  |  |  |  |  |

| TO            | Time-Out bit                                                                                                                                                       |  |  |  |  |  |  |

| PD            | Power-Down bit                                                                                                                                                     |  |  |  |  |  |  |

| dest          | Destination, either the W register or the specified register file location                                                                                         |  |  |  |  |  |  |

| []            | Options                                                                                                                                                            |  |  |  |  |  |  |

| ( )           | Contents                                                                                                                                                           |  |  |  |  |  |  |

| $\rightarrow$ | Assigned to                                                                                                                                                        |  |  |  |  |  |  |

| <>            | Register bit field                                                                                                                                                 |  |  |  |  |  |  |

| €             | In the set of                                                                                                                                                      |  |  |  |  |  |  |

| italics       | User defined term (font is courier)                                                                                                                                |  |  |  |  |  |  |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

## FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

ADDWF Add W and f [ label ] ADDWF Syntax: f,d Operands: 0 < f < 31 $d \in [0,1]$ Operation:  $(W) + (f) \rightarrow (dest)$ Status Affected: C, DC, Z Encodina: 0001 11df ffff Description: Add the contents of the W register and register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. Words: Cycles: Example: ADDWF FSR, 0 Before Instruction

W = 0x17 FSR = 0xC2After Instruction W = 0xD9 FSR = 0xC2

ANDLW And literal with W [label] ANDLW k Syntax: Operands:  $0 \le k \le 255$ Operation: (W).AND. (k)  $\rightarrow$  (W) Status Affected: Ζ Encoding: 1110 kkkk kkkk Description: The contents of the W register are AND'ed with the eight-bit literal 'k'. The result is placed in the W register. Words: 1 Cycles: 1 Example: ANDLW 0x5FBefore Instruction W 0xA3

ANDWF AND W with f [label] ANDWF Syntax: f,d Operands:  $0 \le f \le 31$  $d \in [0,1]$ Operation: (W) .AND. (f)  $\rightarrow$  (dest) Status Affected: Ζ Encodina: 0001 01df ffff Description: The contents of the W register are AND'ed with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. Words: Cycles: Example: ANDWF FSR. 1 Before Instruction W = 0x17FSR = 0xC2 After Instruction W 0x17 0x02 FSR =

**BCF** Bit Clear f Syntax: [label] BCF f,b Operands:  $0 \le f \le 31$  $0 \le b \le 7$ Operation:  $0 \rightarrow (f < b >)$ Status Affected: None Encoding: 0100 bbbf ffff Bit 'b' in register 'f' is cleared. Description: Words: Cycles: Example: BCF FLAG REG, 7 Before Instruction

$FLAG_REG = 0xC7$

$FLAG_REG = 0x47$

After Instruction

After Instruction

0x03

W =

#### 11.4 Timing Diagrams and Specifications

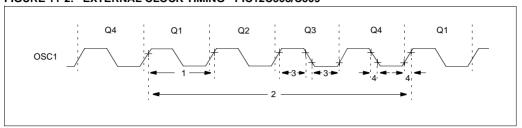

#### FIGURE 11-2: EXTERNAL CLOCK TIMING - PIC12C508/C509

TABLE 11-2: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC12C508/C509

| AC Characteristics | Standard Operating Cond    | litions (unless otherwise specified)                                            |

|--------------------|----------------------------|---------------------------------------------------------------------------------|

|                    | Operating Temperature      | $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial),                            |

|                    |                            | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ (industrial),       |

|                    |                            | $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C} \text{ (extended)}$ |

|                    | Operating Voltage VDD rang | ge is described in Section 11.1                                                 |

| Parameter No. | Sym        | Characteristic                          | Min | Typ <sup>(1)</sup> | Max    | Units | Conditions     |

|---------------|------------|-----------------------------------------|-----|--------------------|--------|-------|----------------|

|               | Fosc       | External CLKIN Frequency <sup>(2)</sup> |     |                    |        |       |                |

|               |            |                                         | DC  | _                  | 4      | MHz   | XT osc mode    |

|               |            |                                         | DC  | _                  | 200    | kHz   | LP osc mode    |

|               |            | Oscillator Frequency <sup>(2)</sup>     |     |                    |        |       |                |

|               |            |                                         | 0.1 | _                  | 4      | MHz   | XT osc mode    |

|               |            |                                         | DC  | _                  | 200    | kHz   | LP osc mode    |

| 1             | Tosc       | External CLKIN Period <sup>(2)</sup>    | 250 | _                  | _      | ns    | EXTRC osc mode |

|               |            |                                         | 250 | _                  | _      | ns    | XT osc mode    |

|               |            |                                         | 5   | _                  | _      | ms    | LP osc mode    |

|               |            | Oscillator Period <sup>(2)</sup>        | 250 | _                  | _      | ns    | EXTRC osc mode |

|               |            |                                         | 250 | _                  | 10,000 | ns    | XT osc mode    |

|               |            |                                         | 5   | _                  | _      | ms    | LP osc mode    |

| 2             | Tcy        | Instruction Cycle Time <sup>(3)</sup>   | _   | 4/Fosc             | _      | -     |                |

| 3             | TosL, TosH | Clock in (OSC1) Low or High Time        | 50* | _                  | _      | ns    | XT oscillator  |

|               |            |                                         | 2*  | _                  | _      | ms    | LP oscillator  |

| 4             | TosR, TosF | Clock in (OSC1) Rise or Fall Time       | _   | _                  | 25*    | ns    | XT oscillator  |

|               |            |                                         | _   | _                  | 50*    | ns    | LP oscillator  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

<sup>3:</sup> Instruction cycle period (TcY) equals four times the input oscillator time base period.

**AC Characteristics**

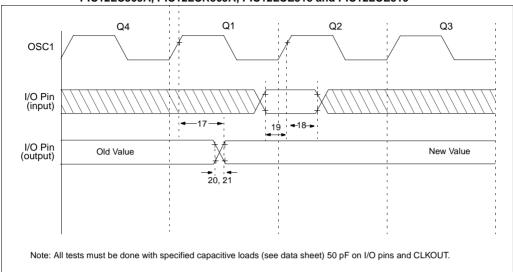

FIGURE 13-3: I/O TIMING - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LC509A, PIC12LCE518 and PIC12LCE519

TABLE 13-4: TIMING REQUIREMENTS - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCF509A, PIC12LCF519 and PIC12LCE519

|                  |          | -40°C ≤ TA                                        | $\leq$ +70°C (comme<br>$\leq$ +85°C (industrial)<br>$\leq$ +125°C (external)<br>ped in Section 13 | rial)<br>ided)     |      |       |

|------------------|----------|---------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|------|-------|

| Parameter<br>No. | Sym      | Characteristic                                    | Min                                                                                               | Typ <sup>(1)</sup> | Max  | Units |

| 17               | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid <sup>(3)</sup> | _                                                                                                 | _                  | 100* | ns    |

| 18               | TosH2ioI | OSC1↑ (Q2 cycle) to Port input invalid            | TBD                                                                                               | _                  | _    | ns    |

Standard Operating Conditions (unless otherwise specified)

| No. | Sym      | Characteristic                                                | Min | Typ <sup>(1)</sup> | Max  | Units |

|-----|----------|---------------------------------------------------------------|-----|--------------------|------|-------|

| 17  | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(3)</sup> | _   | _                  | 100* | ns    |

| 18  | TosH2ioI | OSC1↑ (Q2 cycle) to Port input invalid (I/O in hold time)     | TBD | _                  | _    | ns    |

| 19  | TioV2osH | Port input valid to OSC1↑ (I/O in setup time)                 | TBD |                    | _    | ns    |

| 20  | TioR     | Port output rise time <sup>(2, 3)</sup>                       | _   | 10                 | 25** | ns    |

| 21  | TioF     | Port output fall time <sup>(2, 3)</sup>                       | _   | 10                 | 25** | ns    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>\*\*</sup> These parameters are design targets and are not tested. No characterization data available at this time.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> Measurements are taken in EXTRC mode.

<sup>3:</sup> See Figure 13-1 for loading conditions.

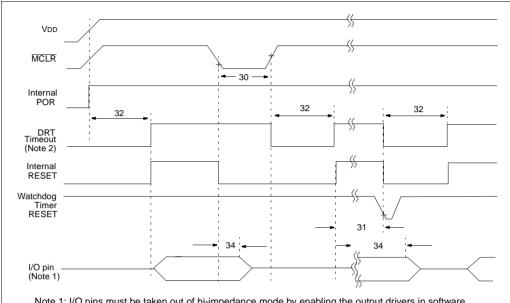

FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCF518 and PIC12LCE519

Note 1: I/O pins must be taken out of hi-impedance mode by enabling the output drivers in software. 2: Runs in MCLR or WDT reset only in XT and LP modes.

TABLE 13-5: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC12C508A, PIC12C509A, PIC12C509A, PIC12C509A, PIC12LC509A, PIC12LCF509A, PIC12LCF518 and PIC12LCF519

#### AC Characteristics Standard Operating Conditions (unless otherwise specified)

Operating Temperature  $0^{\circ}C \le TA \le +70^{\circ}C$  (commercial)

$-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C} \text{ (industrial)}$

$-40^{\circ}C \leq T \text{A} \leq +125^{\circ}C$  (extended)

Operating Voltage VDD range is described in Section 13.1

| Parameter No. | Sym  | Characteristic                                | Min   | Typ <sup>(1)</sup> | Max   | Units | Conditions             |

|---------------|------|-----------------------------------------------|-------|--------------------|-------|-------|------------------------|

| 30            | TmcL | MCLR Pulse Width (low)                        | 2000* | _                  |       | ns    | VDD = 5 V              |

| 31            | Twdt | Watchdog Timer Time-out Period (No Prescaler) | 9*    | 18*                | 30*   | ms    | VDD = 5 V (Commercial) |

| 32            | TDRT | Device Reset Timer Period <sup>(2)</sup>      | 9*    | 18*                | 30*   | ms    | VDD = 5 V (Commercial) |

| 34            | Tioz | I/O Hi-impedance from MCLR Low                | _     | _                  | 2000* | ns    |                        |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design quidance only and are not tested.

Note 2: See Table 13-6.

TABLE 14-1: DYNAMIC IDD (TYPICAL) - WDT ENABLED, 25°C

| Oscillator  | Frequency | VDD =3.0V | VDD = 5.5V |

|-------------|-----------|-----------|------------|

| External RC | 4 MHz     | 240 µA*   | 800 μA*    |

| Internal RC | 4 MHz     | 320 µA    | 800 μΑ     |

| XT          | 4 MHz     | 300 μΑ    | 800 μΑ     |

| LP          | 32 KHz    | 19 µA     | 50 μA      |

<sup>\*</sup>Does not include current through external R&C.

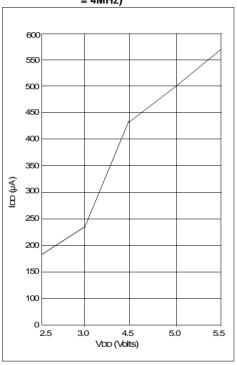

FIGURE 14-3: TYPICAL IDD VS. VDD (WDT DIS, 25°C, FREQUENCY = 4MHz)

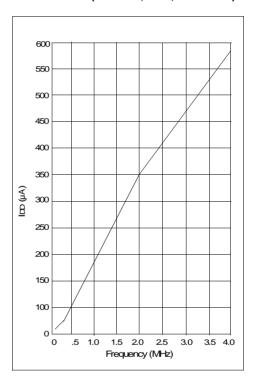

FIGURE 14-4: TYPICAL IDD VS. FREQUENCY (WDT DIS, 25°C, VDD = 5.5V)

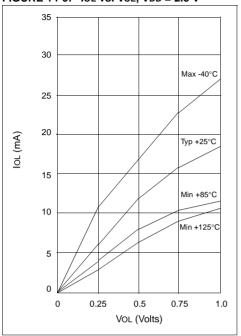

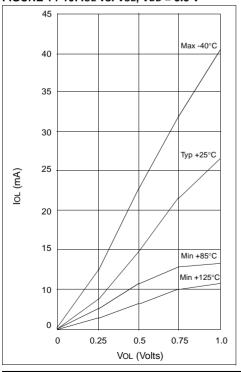

FIGURE 14-9: IOL vs. Vol, VDD = 2.5 V

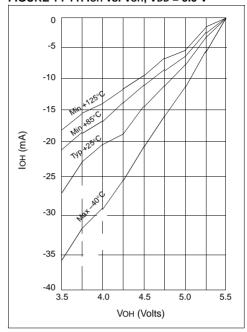

FIGURE 14-11: IOH vs. VOH, VDD = 5.5 V

FIGURE 14-10: IOL vs. Vol, VDD = 3.5 V

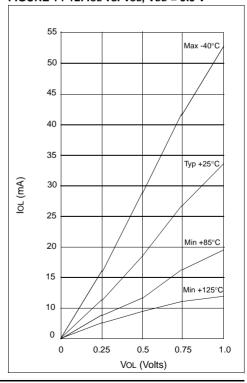

FIGURE 14-12: IoL vs. Vol, VDD = 5.5 V

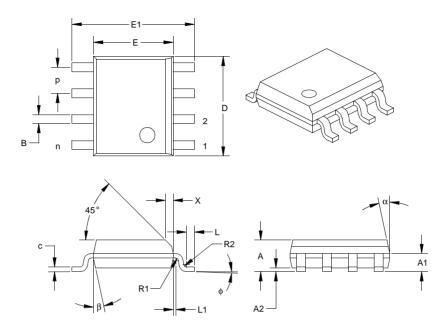

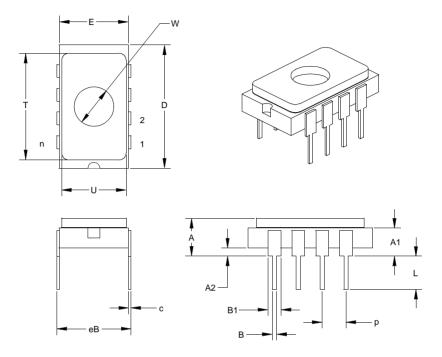

Package Type: K04-057 8-Lead Plastic Small Outline (SN) - Narrow, 150 mil

| Units                   |                | INCHES* |       |       | MILLIMETERS |      |      |

|-------------------------|----------------|---------|-------|-------|-------------|------|------|

| Dimension Limits        |                | MIN     | NOM   | MAX   | MIN         | NOM  | MAX  |

| Pitch                   | р              |         | 0.050 |       |             | 1.27 |      |

| Number of Pins          | n              |         | 8     |       |             | 8    |      |

| Overall Pack. Height    | Α              | 0.054   | 0.061 | 0.069 | 1.37        | 1.56 | 1.75 |

| Shoulder Height         | A1             | 0.027   | 0.035 | 0.044 | 0.69        | 0.90 | 1.11 |

| Standoff                | A2             | 0.004   | 0.007 | 0.010 | 0.10        | 0.18 | 0.25 |

| Molded Package Length   | D <sup>‡</sup> | 0.189   | 0.193 | 0.196 | 4.80        | 4.89 | 4.98 |

| Molded Package Width    | E <sup>‡</sup> | 0.150   | 0.154 | 0.157 | 3.81        | 3.90 | 3.99 |

| Outside Dimension       | E1             | 0.229   | 0.237 | 0.244 | 5.82        | 6.01 | 6.20 |

| Chamfer Distance        | X              | 0.010   | 0.015 | 0.020 | 0.25        | 0.38 | 0.51 |

| Shoulder Radius         | R1             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13 | 0.25 |

| Gull Wing Radius        | R2             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13 | 0.25 |

| Foot Length             | L              | 0.011   | 0.016 | 0.021 | 0.28        | 0.41 | 0.53 |

| Foot Angle              | φ              | 0       | 4     | 8     | 0           | 4    | 8    |

| Radius Centerline       | L1             | 0.000   | 0.005 | 0.010 | 0.00        | 0.13 | 0.25 |

| Lead Thickness          | С              | 0.008   | 0.009 | 0.010 | 0.19        | 0.22 | 0.25 |

| Lower Lead Width        | Β <sup>†</sup> | 0.014   | 0.017 | 0.020 | 0.36        | 0.43 | 0.51 |

| Mold Draft Angle Top    | α              | 0       | 12    | 15    | 0           | 12   | 15   |

| Mold Draft Angle Bottom | β              | 0       | 12    | 15    | 0           | 12   | 15   |

<sup>\*</sup> Controlling Parameter.

<sup>&</sup>lt;sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>&</sup>lt;sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

### Package Type: K04-084 8-Lead Ceramic Side Brazed Dual In-line with Window (JW) - 300 mil

| Units                        |    | INCHES* |       |       | MILLIMETERS |       |       |

|------------------------------|----|---------|-------|-------|-------------|-------|-------|

| Dimension Limits             |    | MIN     | MON   | MAX   | MIN         | MON   | MAX   |

| PCB Row Spacing              |    |         | 0.300 |       |             | 7.62  |       |

| Number of Pins               | n  |         | 8     |       |             | 8     |       |

| Pitch                        | р  | 0.098   | 0.100 | 0.102 | 2.49        | 2.54  | 2.59  |

| Lower Lead Width             | В  | 0.016   | 0.018 | 0.020 | 0.41        | 0.46  | 0.51  |

| Upper Lead Width             | B1 | 0.050   | 0.055 | 0.060 | 1.27        | 1.40  | 1.52  |

| Lead Thickness               | С  | 0.008   | 0.010 | 0.012 | 0.20        | 0.25  | 0.30  |

| Top to Seating Plane         | Α  | 0.145   | 0.165 | 0.185 | 3.68        | 4.19  | 4.70  |

| Top of Body to Seating Plane | A1 | 0.103   | 0.123 | 0.143 | 2.62        | 3.12  | 3.63  |

| Base to Seating Plane        | A2 | 0.025   | 0.035 | 0.045 | 0.64        | 0.89  | 1.14  |

| Tip to Seating Plane         | L  | 0.130   | 0.140 | 0.150 | 3.30        | 3.56  | 3.81  |

| Package Length               | D  | 0.510   | 0.520 | 0.530 | 12.95       | 13.21 | 13.46 |

| Package Width                | E  | 0.280   | 0.290 | 0.300 | 7.11        | 7.37  | 7.62  |

| Overall Row Spacing          | eB | 0.310   | 0.338 | 0.365 | 7.87        | 8.57  | 9.27  |

| Window Diameter              | W  | 0.161   | 0.166 | 0.171 | 4.09        | 4.22  | 4.34  |

| Lid Length                   | Т  | 0.440   | 0.450 | 0.460 | 11.18       | 11.43 | 11.68 |

| Lid Width                    | U  | 0.260   | 0.270 | 0.280 | 6.60        | 6.86  | 7.11  |

<sup>\*</sup> Controlling Parameter.

NOTES:

#### **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- · Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- Design Tips

- · Device Errata

- Job Postings

- · Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- · Listing of seminars and events

#### Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits. The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and 1-602-786-7302 for the rest of the world

981103

**Trademarks:** The Microchip name, logo, PIC, PICmicro, PICSTART, PICMASTER and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. *Flex*ROM, MPLAB and *fuzzy*-LAB are trademarks and SQTP is a service mark of Microchip in the U.S.A.

All other trademarks mentioned herein are the property of their respective companies.