Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

E·XFI

| 2 0 0 0 0 0                |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 5                                                                            |

| Program Memory Size        | 768B (512 x 12)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                |                                                                              |

| RAM Size                   | 25 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 8-SOIJ                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c508at-04i-sm |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE OF CONTENTS

| 1.0   | General Description                                                                   | 4   |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | PIC12C5XX Device Varieties                                                            |     |

| 3.0   | Architectural Overview                                                                |     |

| 4.0   | Memory Organization                                                                   | 13  |

| 5.0   | I/O Port                                                                              |     |

| 6.0   | Timer0 Module and TMR0 Register                                                       | 25  |

| 7.0   | EEPROM Peripheral Operation                                                           | 29  |

| 8.0   | Special Features of the CPU                                                           | 35  |

| 9.0   | Instruction Set Summary                                                               | 47  |

| 10.0  | Development Support                                                                   |     |

| 11.0  | Electrical Characteristics - PIC12C508/PIC12C509                                      | 65  |

| 12.0  | DC and AC Characteristics - PIC12C508/PIC12C509                                       | 75  |

| 13.0  | Electrical Characteristics PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CR509A/ |     |

|       | PIC12CE518/PIC12CE519/                                                                |     |

|       | PIC12LCE518/PIC12LCE519/PIC12LCR509A                                                  | 79  |

| 14.0  | DC and AC Characteristics                                                             |     |

|       | PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CE518/PIC12CE519/PIC12CR509A/      |     |

|       | PIC12LCE518/PIC12LCE519/ PIC12LCR509A                                                 | 93  |

| 15.0  | Packaging Information                                                                 | 99  |

| Index | ۲                                                                                     | 105 |

|       | 2C5XX Product Identification System                                                   |     |

| Sales | and Support:                                                                          | 109 |

### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

NOTES:

# 4.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status, and the page preselect bit for program memories larger than 512 words.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS register because these instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions, which do affect STATUS bits, see Instruction Set Summary.

# FIGURE 4-4: STATUS REGISTER (ADDRESS:03h)

| <u>R/W-0</u><br>GPWUF | R/W-0                                                                     | R/W-0<br>PA0                                           | <u>R-1</u><br>TO                               | R-1<br>PD                                          | R/W-x<br>Z                                                                         | R/W-x<br>DC             | R/W-x<br>C                    | R = Readable bit                                   |

|-----------------------|---------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------|-------------------------|-------------------------------|----------------------------------------------------|

| t7                    | 6                                                                         | 5                                                      | 4                                              | 3                                                  | 2                                                                                  | 1                       | bit0                          | W = Writable bit<br>- n = Value at POR reset       |

|                       | <b>GPWUF</b> : G<br>1 = Reset o<br>0 = After po                           | due to wake                                            | -up from S                                     | LEEP on pi                                         | n change                                                                           |                         |                               |                                                    |

| it 6:                 | Unimplem                                                                  | ented                                                  |                                                |                                                    |                                                                                    |                         |                               |                                                    |

|                       | 0 = Page 0<br>Each page<br>Using the F                                    | (200h - 3F<br>(000h - 1F<br>is 512 byte<br>A0 bit as a | Fh) - PIC12<br>Fh) - PIC12<br>s.<br>general pu | 2C509, PIC<br>2C5XX<br>irpose read                 |                                                                                    | evices whic             | h do not use                  | 2CE519<br>e it for program<br>ith future products. |

|                       | <b>TO</b> : Time-o<br>1 = After po<br>0 = A WDT                           | ower-up, CL                                            |                                                | uction, or S                                       | LEEP instruc                                                                       | tion                    |                               |                                                    |

|                       | <b>PD</b> : Power-<br>1 = After po<br>0 = By exec                         | ower-up or l                                           |                                                |                                                    | tion                                                                               |                         |                               |                                                    |

|                       | <b>Z</b> : Zero bit<br>1 = The res<br>0 = The res                         |                                                        |                                                | •                                                  | tion is zero<br>tion is not ze                                                     | ro                      |                               |                                                    |

|                       | <b>ADDWF</b><br>1 = A carry<br>0 = A carry<br><b>SUBWF</b><br>1 = A borro | from the 4t<br>from the 4t<br>w from the the           | th low orde<br>th low orde<br>4th low ord      | r bit of the r<br>r bit of the r<br>ler bit of the | BWF instructi<br>esult occurre<br>esult did not<br>result did not<br>result did no | ed<br>occur<br>ot occur |                               |                                                    |

|                       | ADDWF<br>1 = A carry                                                      |                                                        |                                                | SUBWF<br>1 = A bor                                 | RF, RLF instr<br>row did not c<br>row occurred                                     | occur                   | <b>RRF or R</b><br>Load bit w | LF<br>vith LSB or MSB, respectively                |

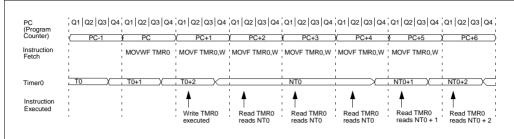

# FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

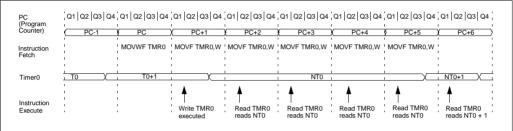

# FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

# TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6      | Bit 5     | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|----------|------------|-----------|----------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 01h     | TMR0   | Timer0 - | 8-bit real | -time clo | ck/count | er    |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| N/A     | OPTION | GPWU     | GPPU       | T0CS      | T0SE     | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | TRIS   | —        |            | GP5       | GP4      | GP3   | GP2   | GP1   | GP0   | 11 1111                       | 11 1111                         |

Legend: Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged,

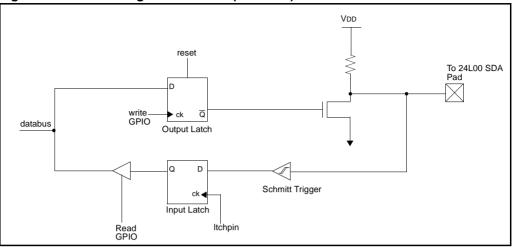

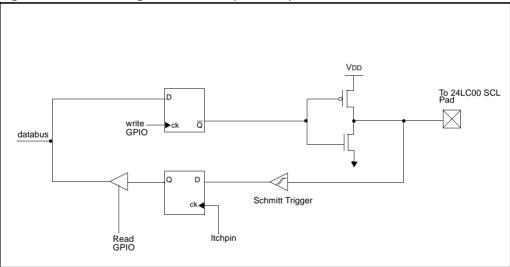

Figure 7-2: Block diagram of GPIO7 (SCL line)

# 7.5 READ OPERATIONS

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

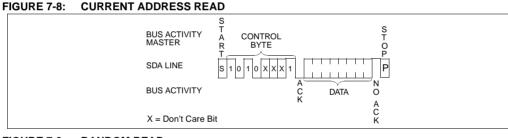

#### 7.5.1 CURRENT ADDRESS READ

It contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous read access was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with the R/W bit set to one, the device issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-8).

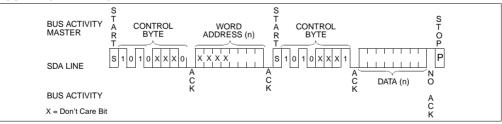

#### 7.5.2 RANDOM READ

Random read operations allow the master to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the device as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the  $R/\overline{W}$  bit set to a one. It will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-9). After this command, the internal address counter will point to the address location following the one that was just read.

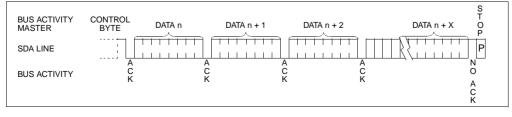

#### 7.5.3 SEQUENTIAL READ

Sequential reads are initiated in the same way as a random read except that after the device transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the device to transmit the next sequentially addressed 8-bit word (Figure 7-10).

To provide sequential reads, it contains an internal address pointer which is incremented by one at the completion of each read operation. This address pointer allows the entire memory contents to be serially read during one operation.

#### FIGURE 7-9: RANDOM READ

# FIGURE 7-10: SEQUENTIAL READ

# 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC12C5XX family of microcontrollers has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- · Oscillator selection

- Reset

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from SLEEP on pin change

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- · ID locations

- · In-circuit Serial Programming

The PIC12C5XX has a Watchdog Timer which can be shut off only through configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in reset until the crystal oscillator is stable. If using INTRC or EXTRC there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

# 8.1 Configuration Bits

The PIC12C5XX configuration word consists of 12 bits. Configuration bits can be programmed to select various device configurations. Two bits are for the selection of the oscillator type, one bit is the Watchdog Timer enable bit, and one bit is the MCLR enable bit.

# FIGURE 8-1: CONFIGURATION WORD FOR PIC12C5XX

| _         | —                           | _                                                                             | —                              | —        | —     | — | MCLRE                       | CP | WDTE | FOSC1 | FOSC0 | Register:                | CONFIG |

|-----------|-----------------------------|-------------------------------------------------------------------------------|--------------------------------|----------|-------|---|-----------------------------|----|------|-------|-------|--------------------------|--------|

| bit11     | 10                          | 9                                                                             | 8                              | 7        | 6     | 5 | 4                           | 3  | 2    | 1     | bit0  | Address <sup>(1)</sup> : | FFFh   |

| bit 11-5: | Unim                        | olement                                                                       | ed                             |          |       |   |                             |    |      |       |       |                          |        |

| bit 4:    | 1 = M                       | CLR pin                                                                       | R enable<br>enabled<br>to VDD, |          | у)    |   |                             |    |      |       |       |                          |        |

| bit 3:    | 1 = Co                      | CP: Code protection bit.<br>1 = Code protection off<br>0 = Code protection on |                                |          |       |   |                             |    |      |       |       |                          |        |

| bit 2:    | 1 = W                       | : Watch<br>DT enab<br>DT disat                                                |                                | r enable | bit   |   |                             |    |      |       |       |                          |        |

| bit 1-0:  | 11 = E<br>10 = II<br>01 = X | XTRC -                                                                        |                                | RC oscil | lator |   |                             |    |      |       |       |                          |        |

| Note 1:   |                             |                                                                               |                                | •        | •     |   | ations to de<br>Iressable d |    |      |       | he    |                          |        |

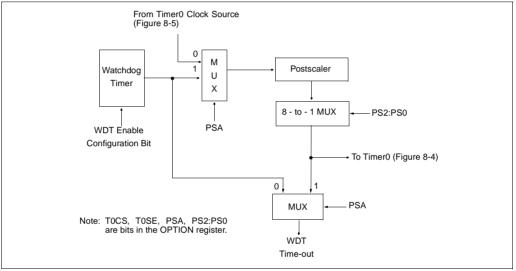

#### 8.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 8.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT wake-up reset.

#### FIGURE 8-12: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 8-6: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer, - = unimplemented, read as '0', u = unchanged

#### 8.9 Power-Down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

#### 8.9.1 SLEEP

The Power-Down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{TO}$  bit (STATUS<4>) is set, the  $\overline{PD}$  bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low, or hi-impedance).

It should be noted that a RESET generated by a WDT time-out does not drive the  $\overline{\text{MCLR}}$  pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the GP3/ MCLR/VPP pin must be at a logic high level (VIHMC) if MCLR is enabled.

#### 8.9.2 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. An external reset input on GP3/MCLR/VPP pin, when configured as MCLR.

- 2. A Watchdog Timer time-out reset (if WDT was enabled).

- A change on input pin GP0, GP1, or GP3/ MCLR/VPP when wake-up on change is enabled.

These events cause a device reset. The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits can be used to determine the cause of device reset. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF bit indicates a change in state while in SLEEP at pins GP0, GP1, or GP3 (since the last time there was a file or bit operation on GP port).

Caution: Right before entering SLEEP, read the input pins. When in SLEEP, wake up occurs when the values at the pins change from the state they were in at the last reading. If a wake-up on change occurs and the pins are not read before reentering SLEEP, a wake up will occur immediately even if no pins change while in SLEEP mode.

The WDT is cleared when the device wakes from sleep, regardless of the wake-up source.

#### 8.10 Program Verification/Code Protection

If the code protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations can be read by the PIC12C5XX regardless of the code protection bit setting.

The last memory location cannot be read if code protection is enabled on the PIC12C508/509.

The last memory location can be read regardless of the code protection bit setting on the PIC12C508A/509A/CR509A/CE518/CE519.

### 8.11 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other codeidentification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '0's.

#### 8.12 In-Circuit Serial Programming

The PIC12C5XX microcontrollers with EPROM program memory can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the GP1 and GP0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1 becomes the programming clock and GP0 becomes the programming data. Both GP1 and GP0 are Schmitt Trigger inputs in this mode.

After reset, a 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC12C5XX Programming Specifications.

A typical in-circuit serial programming connection is shown in Figure 8-16.

#### FIGURE 8-16: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| INCF                      | Increment f                                                                                                                                                         |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                   | [label] INCF f,d                                                                                                                                                    |

| Operands:                 | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                           |

| Operation:                | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected:          | Z                                                                                                                                                                   |

| Encoding:                 | 0010 10df ffff                                                                                                                                                      |

| Description:              | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |

| Words:                    | 1                                                                                                                                                                   |

| Cycles:                   | 1                                                                                                                                                                   |

| Example:                  | INCF CNT, 1                                                                                                                                                         |

| Before Instru<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                       |

| After Instruct            |                                                                                                                                                                     |

| CNT<br>Z                  | = 0x00<br>= 1                                                                                                                                                       |

|                           |                                                                                                                                                                     |

| INCFSZ                    | Increment f, Skip if 0                                                                                                                                              |

| Syntax:                   | [label] INCFSZ f,d                                                                                                                                                  |

| Operands:                 | $0 \le f \le 31$                                                                                                                                                    |

| Syntax:                                             | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:                                           | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                 |

| Operation:                                          | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                                 |

| Status Affected:                                    | None                                                                                                                                                                                                                                                                                                                                             |

| Encoding:                                           | 0011 11df ffff                                                                                                                                                                                                                                                                                                                                   |

| Description:                                        | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, then the next instruc-<br>tion, which is already fetched, is dis-<br>carded and an NOP is executed<br>instead making it a two cycle instruc-<br>tion. |

| Words:                                              | 1                                                                                                                                                                                                                                                                                                                                                |

| Cycles:                                             | 1(2)                                                                                                                                                                                                                                                                                                                                             |

| Example:                                            | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                                  |

|                                                     | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                                  |

| Before Inst<br>PC                                   | ruction<br>= address (HERE)                                                                                                                                                                                                                                                                                                                      |

| After Instru<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | = CNT + 1;                                                                                                                                                                                                                                                                                                                                       |

| IORLW                       | Inclusive OR literal with W                                                                                            |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | [ <i>label</i> ] IORLW k                                                                                               |

| Operands:                   | $0 \le k \le 255$                                                                                                      |

| Operation:                  | (W) .OR. (k) $\rightarrow$ (W)                                                                                         |

| Status Affected:            | Z                                                                                                                      |

| Encoding:                   | 1101 kkkk kkkk                                                                                                         |

| Description:                | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:                      | 1                                                                                                                      |

| Cycles:                     | 1                                                                                                                      |

| Example:                    | IORLW 0x35                                                                                                             |

| Before Instru<br>W =        | uction<br>0x9A                                                                                                         |

| After Instruc<br>W =<br>Z = | tion<br>0xBF<br>0                                                                                                      |

| IORWF                                     | Inclusive OR W with f                                                                                                                                                |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                   | [ label ] IORWF f,d                                                                                                                                                  |

| Operands:                                 | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                     |

| Operation:                                | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                     |

| Status Affected                           | I: Z                                                                                                                                                                 |

| Encoding:                                 | 0001 00df ffff                                                                                                                                                       |

| Description:                              | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |

| Words:                                    | 1                                                                                                                                                                    |

| Cycles:                                   | 1                                                                                                                                                                    |

| Example:                                  | IORWF RESULT, 0                                                                                                                                                      |

| Before Inst<br>RESUL<br>W<br>After Instru | LT = 0x13<br>= 0x91                                                                                                                                                  |

| RESUL<br>W<br>Z                           |                                                                                                                                                                      |

| OPTION                   | Load OP                                                           | TION Re | gister |  |  |  |

|--------------------------|-------------------------------------------------------------------|---------|--------|--|--|--|

| Syntax:                  | [ label ]                                                         | OPTION  | l      |  |  |  |

| Operands:                | None                                                              |         |        |  |  |  |

| Operation:               | $(W)\toO$                                                         | PTION   |        |  |  |  |

| Status Affected:         | None                                                              |         |        |  |  |  |

| Encoding:                | 0000                                                              | 0000    | 0010   |  |  |  |

| Description:             | The content of the W register is loaded into the OPTION register. |         |        |  |  |  |

| Words:                   | 1                                                                 |         |        |  |  |  |

| Cycles:                  | 1                                                                 |         |        |  |  |  |

| Example                  | OPTION                                                            |         |        |  |  |  |

| Before Instru<br>W       | ction<br>= 0x07                                                   |         |        |  |  |  |

| After Instruct<br>OPTION |                                                                   |         |        |  |  |  |

| RETLW                 | Return with                                                                                                                                                                         | Liter             | al in W                          |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------|--|--|--|--|

| Syntax:               | [label] RE                                                                                                                                                                          | TLW               | k                                |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                   | $0 \le k \le 255$ |                                  |  |  |  |  |

| Operation:            | $\begin{array}{l} k \rightarrow (W);\\ TOS \rightarrow PC \end{array}$                                                                                                              |                   |                                  |  |  |  |  |

| Status Affected:      | None                                                                                                                                                                                |                   |                                  |  |  |  |  |

| Encoding:             | 1000 kł                                                                                                                                                                             | kk                | kkkk                             |  |  |  |  |

| Description:          | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two cycle<br>instruction. |                   |                                  |  |  |  |  |

| Words:                | 1                                                                                                                                                                                   |                   |                                  |  |  |  |  |

| Cycles:               | 2                                                                                                                                                                                   |                   |                                  |  |  |  |  |

| Example:              | CALL TABLE                                                                                                                                                                          | ;tab<br>;val      | le offset<br>ue.<br>ow has table |  |  |  |  |

| TABLE                 | ADDWF PC<br>RETLW k1<br>RETLW k2                                                                                                                                                    | ; Beg             | offset<br>in table<br>d of table |  |  |  |  |

| Before Instru<br>W =  | ox07                                                                                                                                                                                |                   |                                  |  |  |  |  |

| After Instruct<br>W = | tion<br>value of k8                                                                                                                                                                 |                   |                                  |  |  |  |  |

| RLF                                                                                                                                                                          | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                                                      | [label] RLF f,d                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                                                                                                    | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                               |

| Operation:                                                                                                                                                                   | See description below                                                                                                                                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                                                                                                             | С                                                                                                                                                                                                                                                                                                                                                                                                          |

| Encoding:                                                                                                                                                                    | 0011 01df ffff                                                                                                                                                                                                                                                                                                                                                                                             |

| Description:                                                                                                                                                                 | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is stored<br>back in register 'f'.                                                                                                                                                                                                |

| Words:                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                          |

| Cycles:                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                          |

| Example:                                                                                                                                                                     | RLF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                 |

| Before Instru                                                                                                                                                                | iction                                                                                                                                                                                                                                                                                                                                                                                                     |

| REG1<br>C                                                                                                                                                                    | = 1110 0110<br>= 0                                                                                                                                                                                                                                                                                                                                                                                         |

| After Instruc                                                                                                                                                                | tion                                                                                                                                                                                                                                                                                                                                                                                                       |

| REG1<br>W                                                                                                                                                                    | = 1110 0110<br>= 1100 1100                                                                                                                                                                                                                                                                                                                                                                                 |

| C                                                                                                                                                                            | = 1                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRF                                                                                                                                                                          | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                               |

| RRF<br>Syntax:                                                                                                                                                               | Rotate Right f through Carry<br>[ label ] RRF f,d                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Syntax:                                                                                                                                                                      | [ <i>label</i> ] RRF f,d<br>0 ≤ f ≤ 31                                                                                                                                                                                                                                                                                                                                                                     |

| Syntax:<br>Operands:                                                                                                                                                         | $\begin{bmatrix} label \end{bmatrix} RRF f,d$<br>$0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                         |

| Syntax:<br>Operands:<br>Operation:                                                                                                                                           | $ \begin{bmatrix} label \end{bmatrix} RRF f,d \\ 0 \le f \le 31 \\ d \in [0,1] \\ See description below $                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                                                                       | $ [label] RRF f,d  0 \le f \le 31  d \in [0,1]  See description below  C  0011 00df ffff  The contents of register 'f' are rotated  one bit to the right through the Carry  Flag. If 'd' is 0 the result is placed in the  W register. If 'd' is 1 the result is placed  back in register 'f'.$                                                                                                            |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                                                          | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                    |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                                                          | $ [label] RRF f,d  0 \le f \le 31  d \in [0,1]  See description below  C  0011 00df ffff  The contents of register 'f' are rotated  one bit to the right through the Carry  Flag. If 'd' is 0 the result is placed in the  W register. If 'd' is 1 the result is placed  back in register 'f'.$                                                                                                            |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                                                                                          | $\begin{bmatrix} label \end{bmatrix} RRF f,d$<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>$\boxed{0011  00df  ffff}$<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>$\boxed{C} \qquad register 'f'}$         |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                                                | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>T                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                                                     | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1,0                                                       |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instru<br>REG1                                | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>C register 'f'<br>1<br>1<br>RRF REG1,0<br>interimed<br>= 1110 0110<br>= 0 |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instruc<br>REG1<br>C<br>After Instruc<br>REG1 | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1,0<br>intion<br>= 1110 0110<br>= 0<br>tion<br>= 1110 0110 |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instruc<br>REG1<br>C<br>After Instruct        | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011  00df  ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REGI, 0<br>interval<br>1 100110<br>= 0<br>tion             |

#### 10.10 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- A full featured editor

- Three operating modes

- editor

- emulator

- simulator

- A project manager

- Customizable tool bar and key mapping

- A status bar with project information

- · Extensive on-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PICmicro<sup>®</sup> tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

# 10.11 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PChosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from MPLAB-ICE, Microchip's Universal Emulator System.

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PICmicro<sup>®</sup>. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

## 10.12 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PICmicro<sup>®</sup> series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

### 10.13 MPLAB-C17 Compiler

The MPLAB-C17 Code Development System is a complete ANSI 'C' compiler and integrated development environment for Microchip's PIC17CXXX family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

#### 10.14 <u>Fuzzy Logic Development System</u> (fuzzyTECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, Edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

# 10.15 <u>SEEVAL® Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

NOTES:

# TABLE 11-5: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC12C508/C509

| AC Charac        | teristics |                                                                                               |    |     |       |            |                        |

|------------------|-----------|-----------------------------------------------------------------------------------------------|----|-----|-------|------------|------------------------|

| Parameter<br>No. | Sym       | Characteristic Min Typ <sup>(1)</sup> Max Units                                               |    |     |       | Conditions |                        |

| 30               | TmcL      | MCLR         Pulse Width (low)         2000*         —         —         ns         VDD = 5 V |    |     |       | VDD = 5 V  |                        |

| 31               | Twdt      | Watchdog Timer Time-out Period 9* 18* 30* ms<br>(No Prescaler)                                |    |     |       | ms         | VDD = 5 V (Commercial) |

| 32               | TDRT      | Device Reset Timer Period <sup>(2)</sup>                                                      | 9* | 18* | 30*   | ms         | VDD = 5 V (Commercial) |

| 34               | Tioz      | I/O Hi-impedance from MCLR Low                                                                | —  | —   | 2000* | ns         |                        |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 2: See Table 11-6.

## TABLE 11-6: DRT (DEVICE RESET TIMER PERIOD - PIC12C508/C509)

| Oscillator Configuration | POR Reset       | Subsequent Resets |

|--------------------------|-----------------|-------------------|

| IntRC & ExtRC            | 18 ms (typical) | 300 µs (typical)  |

| XT & LP                  | 18 ms (typical) | 18 ms (typical)   |

# TABLE 13-1: PULL-UP RESISTOR RANGES\* - PIC12C508A, PIC12C509A, PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Max  | Units |  |  |  |  |

|-------------|------------------|------|------|------|-------|--|--|--|--|

| GP0/GP1     |                  |      |      |      |       |  |  |  |  |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |  |  |  |  |

|             | 25               | 42K  | 48K  | 63K  | Ω     |  |  |  |  |

|             | 85               | 42K  | 49K  | 63K  | Ω     |  |  |  |  |

|             | 125              | 50K  | 55K  | 63K  | Ω     |  |  |  |  |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |  |  |  |  |

|             | 25               | 18K  | 20K  | 23K  | Ω     |  |  |  |  |

|             | 85               | 19K  | 22K  | 25K  | Ω     |  |  |  |  |

|             | 125              | 22K  | 24K  | 28K  | Ω     |  |  |  |  |

|             | GP3              |      |      |      |       |  |  |  |  |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |  |  |  |  |

|             | 25               | 343K | 414K | 532K | Ω     |  |  |  |  |

|             | 85               | 368K | 457K | 532K | Ω     |  |  |  |  |

|             | 125              | 431K | 504K | 593K | Ω     |  |  |  |  |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |  |  |  |  |

|             | 25               | 288K | 341K | 437K | Ω     |  |  |  |  |

|             | 85               | 306K | 371K | 448K | Ω     |  |  |  |  |

|             | 125              | 351K | 407K | 500K | Ω     |  |  |  |  |

\* These parameters are characterized but not tested.

#### TABLE 13-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| AC Chara         | cteristics |                                                   |      |      |      |            |            |

|------------------|------------|---------------------------------------------------|------|------|------|------------|------------|

| Parameter<br>No. | Sym        | Characteristic Min* Typ <sup>(1)</sup> Max* Units |      |      |      | Conditions |            |

|                  |            | Internal Calibrated RC Frequency                  | 3.65 | 4.00 | 4.28 | MHz        | VDD = 5.0V |

|                  |            | Internal Calibrated RC Frequency                  | 3.55 | —    | 4.31 | MHz        | VDD = 2.5V |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 13-8: EEPROM MEMORY BUS TIMING REQUIREMENTS - PIC12CE5XX ONLY.

| AC Characteristics                                                                   |         |                      |                     |        |                                                                                                                                              |  |  |

|--------------------------------------------------------------------------------------|---------|----------------------|---------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                                                            | Symbol  | Min                  | Max                 | Units  | Conditions                                                                                                                                   |  |  |

| Clock frequency                                                                      | FCLK    |                      | 100<br>100<br>400   | kHz    | 4.5V ≤ Vcc ≤ 5.5V (E Temp range)<br>3.0V ≤ Vcc ≤ 4.5V<br>4.5V ≤ Vcc ≤ 5.5V                                                                   |  |  |

| Clock high time                                                                      | Тнідн   | 4000<br>4000<br>600  |                     | ns     |                                                                                                                                              |  |  |

| Clock low time                                                                       | TLOW    | 4700<br>4700<br>1300 |                     | ns     |                                                                                                                                              |  |  |

| SDA and SCL rise time<br>(Note 1)                                                    | TR      |                      | 1000<br>1000<br>300 | ns     |                                                                                                                                              |  |  |

| SDA and SCL fall time                                                                | TF      | _                    | 300                 | ns     | (Note 1)                                                                                                                                     |  |  |

| START condition hold time                                                            | THD:STA | 4000<br>4000<br>600  |                     | ns     |                                                                                                                                              |  |  |

| START condition setup time                                                           | TSU:STA | 4700<br>4700<br>600  |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \mbox{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |

| Data input hold time                                                                 | THD:DAT | 0                    |                     | ns     | (Note 2)                                                                                                                                     |  |  |

| Data input setup time                                                                | TSU:DAT | 250<br>250<br>100    |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \mbox{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |