Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 768B (512 x 12)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 25 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 8-SOIJ                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c508t-04i-sm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE OF CONTENTS

| 1.0   | General Description                                                                   | 4   |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | PIC12C5XX Device Varieties                                                            |     |

| 3.0   | Architectural Overview                                                                |     |

| 4.0   | Memory Organization                                                                   | 13  |

| 5.0   | I/O Port                                                                              |     |

| 6.0   | Timer0 Module and TMR0 Register                                                       | 25  |

| 7.0   | EEPROM Peripheral Operation                                                           | 29  |

| 8.0   | Special Features of the CPU                                                           | 35  |

| 9.0   | Instruction Set Summary                                                               | 47  |

| 10.0  | Development Support                                                                   |     |

| 11.0  | Electrical Characteristics - PIC12C508/PIC12C509                                      | 65  |

| 12.0  | DC and AC Characteristics - PIC12C508/PIC12C509                                       | 75  |

| 13.0  | Electrical Characteristics PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CR509A/ |     |

|       | PIC12CE518/PIC12CE519/                                                                |     |

|       | PIC12LCE518/PIC12LCE519/PIC12LCR509A                                                  | 79  |

| 14.0  | DC and AC Characteristics                                                             |     |

|       | PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CE518/PIC12CE519/PIC12CR509A/      |     |

|       | PIC12LCE518/PIC12LCE519/ PIC12LCR509A                                                 | 93  |

| 15.0  | Packaging Information                                                                 | 99  |

| Index | ۲                                                                                     | 105 |

|       | 2C5XX Product Identification System                                                   |     |

| Sales | and Support:                                                                          | 109 |

#### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

#### 4.4 OPTION Register

The OPTION register is a 8-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A RESET sets the OPTION<7:0> bits.

#### FIGURE 4-5: OPTION REGISTER

Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin; i.e., note that TRIS overrides OPTION control of GPPU and GPWU.

**Note:** If the TOCS bit is set to '1', GP2 is forced to be an input even if TRIS GP2 = '0'.

| W-1      | W-1                                                  | W-1           | W-1         | W-1          | W-1         | W-1 | W-1  |                                                                                               |

|----------|------------------------------------------------------|---------------|-------------|--------------|-------------|-----|------|-----------------------------------------------------------------------------------------------|

| GPWU     | GPPU                                                 | TOCS          | T0SE        | PSA          | PS2         | PS1 | PS0  | W = Writable bit                                                                              |

| oit7     | 6                                                    | 5             | 4           | 3            | 2           | 1   | bit0 | U = Unimplemented bit<br>- n = Value at POR reset<br>Reference Table 4-1 for<br>other resets. |

| bit 7:   | <b>GPWU</b> : Ena<br>1 = Disable<br>0 = Enable       | d             | p on pin cl | hange (GP    | 0, GP1, GP3 | )   |      |                                                                                               |

| bit 6:   | <b>GPPU</b> : Ena<br>1 = Disable<br>0 = Enablec      | d .           | III-ups (GF | 90, GP1, G   | P3)         |     |      |                                                                                               |

| bit 5:   | <b>TOCS</b> : Time<br>1 = Transitio<br>0 = Transitio | on on TOCK    | l pin       |              | ock, Fosc/4 |     |      |                                                                                               |

| bit 4:   | TOSE: Time<br>1 = Increme<br>0 = Increme             | ent on high t | o low trans | sition on th |             |     |      |                                                                                               |

| bit 3:   | <b>PSA</b> : Presc<br>1 = Prescale<br>0 = Prescale   | er assigned   | to the WD   |              |             |     |      |                                                                                               |

| bit 2-0: | PS2:PS0: P                                           | Prescaler rat | e select bi | its          |             |     |      |                                                                                               |

|          | Bit Value                                            | Timer0 R      | ate WDT     | Rate         |             |     |      |                                                                                               |

|          | 000                                                  | 1:2<br>1:4    | 1:          | 2            |             |     |      |                                                                                               |

|          | 010<br>011                                           | 1:8           | 1:          |              |             |     |      |                                                                                               |

|          | 100                                                  | 1:32          |             | 0<br>16      |             |     |      |                                                                                               |

|          | 101                                                  | 1:64          |             | 32           |             |     |      |                                                                                               |

|          | 110                                                  | 1:128         |             | 64           |             |     |      |                                                                                               |

|          | 111                                                  | 1:256         | : 1.        | 128          |             |     |      |                                                                                               |

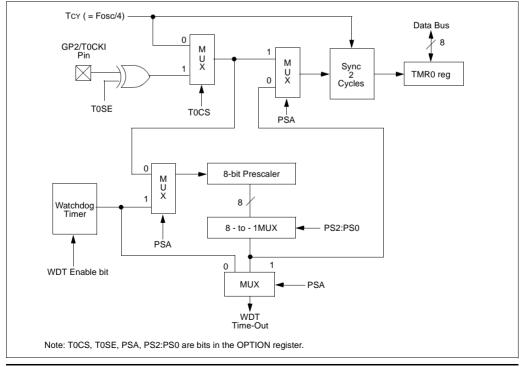

#### 6.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 8.6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

#### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

| 1.CLRWDT            | ;Clear WDT               |

|---------------------|--------------------------|

| 2.CLRF TMR0         | ;Clear TMR0 & Prescaler  |

| 3.MOVLW '00xx1111'b | ;These 3 lines (5, 6, 7) |

| 4.OPTION            | ; are required only if   |

|                     | ; desired                |

| 5.CLRWDT            | ;PS<2:0> are 000 or 001  |

| 6.MOVLW '00xx1xxx'b | ;Set Postscaler to       |

| 7.OPTION            | ; desired WDT rate       |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT | •          | Clear WDT and       |

|--------|------------|---------------------|

|        |            | ;prescaler          |

| MOVLW  | 'xxxx0xxx' | ;Select TMR0, new   |

|        |            | ;prescale value and |

|        |            | ;clock source       |

| OPTION |            |                     |

## FIGURE 6-5: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

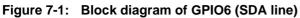

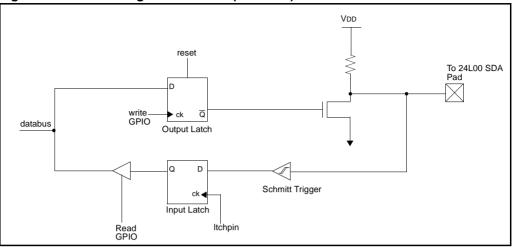

Figure 7-2: Block diagram of GPIO7 (SCL line)

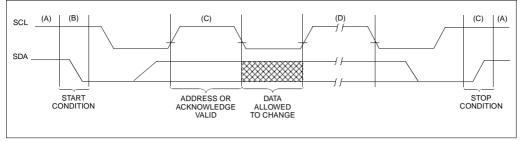

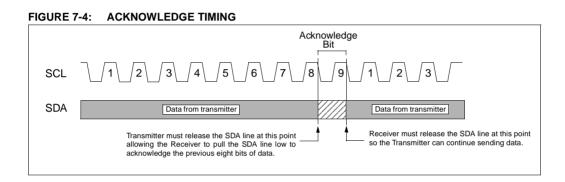

## FIGURE 7-3: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

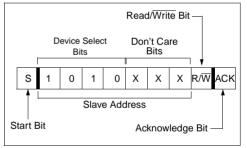

## 7.2 Device Addressing

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed. The slave address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

#### FIGURE 7-5: CONTROL BYTE FORMAT

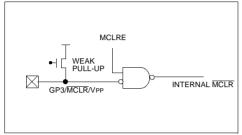

#### 8.3.1 MCLR ENABLE

This configuration bit when unprogrammed (left in the '1' state) enables the external  $\overline{MCLR}$  function. When programmed, the  $\overline{MCLR}$  function is tied to the internal VDD, and the pin is assigned to be a GPIO. See Figure 8-7. When pin GP3/ $\overline{MCLR}$ /VPP is configured as  $\overline{MCLR}$ , the internal pull-up is always on.

#### FIGURE 8-7: MCLR SELECT

#### 8.4 Power-On Reset (POR)

The PIC12C5XX family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip reset for most power-up situations.

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD or program the pin as GP3. An internal weak pull-up resistor is implemented using a transistor. Refer to Table 11-1 for the pull-up resistor ranges. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 8-8.

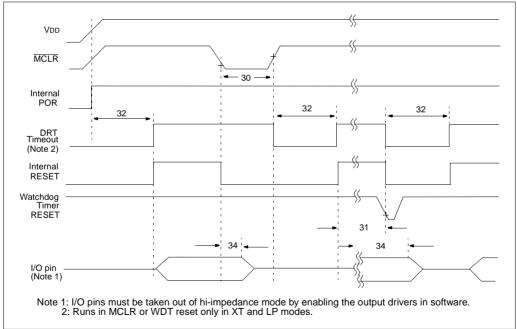

The Power-On Reset circuit and the Device Reset Timer (Section 8.5) circuit are closely related. On power-up, the reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will reset the reset latch and thus end the onchip reset signal.

A power-up example where  $\overline{\text{MCLR}}$  is held low is shown in Figure 8-9. VDD is allowed to rise and stabilize before bringing  $\overline{\text{MCLR}}$  high. The chip will actually come out of reset TDRT msec after  $\overline{\text{MCLR}}$  goes high.

In Figure 8-10, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3.). The VDD is stable before the start-up timer times out and there is no problem in getting a proper reset. However, Figure 8-11 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 8-10).

| Note: | When the device starts normal operation (exits the reset condition), device operating |

|-------|---------------------------------------------------------------------------------------|

|       | parameters (voltage, frequency, tempera-                                              |

|       | ture, etc.) must be meet to ensure opera-                                             |

|       | tion. If these conditions are not met, the                                            |

|       | device must be held in reset until the oper-                                          |

|       | ating conditions are met.                                                             |

For additional information refer to Application Notes "Power-Up Considerations" - AN522 and "Power-up Trouble Shooting" - AN607.

## 10.16 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

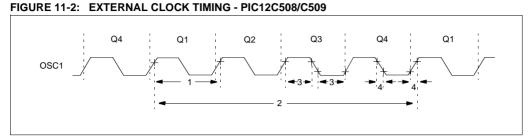

### 11.4 Timing Diagrams and Specifications

| AC Chara         | cteristics | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                    |        |       |                |  |  |

|------------------|------------|------------------------------------------------------|-----|--------------------|--------|-------|----------------|--|--|

| Parameter<br>No. | Sym        | Characteristic                                       | Min | Typ <sup>(1)</sup> | Мах    | Units | Conditions     |  |  |

|                  | Fosc       | External CLKIN Frequency <sup>(2)</sup>              |     |                    |        |       |                |  |  |

|                  |            |                                                      | DC  | —                  | 4      | MHz   | XT osc mode    |  |  |

|                  |            |                                                      | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

|                  |            | Oscillator Frequency <sup>(2)</sup>                  |     |                    |        |       |                |  |  |

|                  |            |                                                      | 0.1 | _                  | 4      | MHz   | XT osc mode    |  |  |

|                  |            |                                                      | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

| 1                | Tosc       | External CLKIN Period <sup>(2)</sup>                 | 250 | —                  | _      | ns    | EXTRC osc mode |  |  |

|                  |            |                                                      | 250 | _                  | _      | ns    | XT osc mode    |  |  |

|                  |            |                                                      | 5   | —                  | —      | ms    | LP osc mode    |  |  |

|                  |            | Oscillator Period <sup>(2)</sup>                     | 250 | _                  | _      | ns    | EXTRC osc mode |  |  |

|                  |            |                                                      | 250 | _                  | 10,000 | ns    | XT osc mode    |  |  |

|                  |            |                                                      | 5   | —                  | —      | ms    | LP osc mode    |  |  |

| 2                | Тсу        | Instruction Cycle Time <sup>(3)</sup>                | —   | 4/Fosc             | —      |       |                |  |  |

| 3                | TosL, TosH | Clock in (OSC1) Low or High Time                     |     | —                  | —      | ns    | XT oscillator  |  |  |

|                  |            |                                                      | 2*  | _                  | —      | ms    | LP oscillator  |  |  |

| 4                | TosR, TosF | Clock in (OSC1) Rise or Fall Time                    | —   | -                  | 25*    | ns    | XT oscillator  |  |  |

|                  |            |                                                      | —   | —                  | 50*    | ns    | LP oscillator  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

3: Instruction cycle period (TCY) equals four times the input oscillator time base period.

## TABLE 11-4: TIMING REQUIREMENTS - PIC12C508/C509

| AC Chara         | AC Characteristics Standard Operating Conditions (unless otherwise specified)   Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)   Operating Voltage VDD range is described in Section 11.1 |                                                                          |     |                    |      |       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|--------------------|------|-------|

| Parameter<br>No. | Sym                                                                                                                                                                                                                                                                                                                       | Characteristic                                                           | Min | Typ <sup>(1)</sup> | Max  | Units |

| 17               | TosH2ioV                                                                                                                                                                                                                                                                                                                  | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(3)</sup>            | _   | -                  | 100* | ns    |

| 18               | TosH2iol                                                                                                                                                                                                                                                                                                                  | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) | TBD | —                  | _    | ns    |

| 19               | TioV2osH                                                                                                                                                                                                                                                                                                                  | Port input valid to OSC1↑<br>(I/O in setup time)                         | TBD | —                  | _    | ns    |

| 20               | TioR                                                                                                                                                                                                                                                                                                                      | Port output rise time <sup>(2, 3)</sup>                                  | _   | 10                 | 25** | ns    |

| 21               | TioF                                                                                                                                                                                                                                                                                                                      | Port output fall time <sup>(2, 3)</sup>                                  | _   | 10                 | 25** | ns    |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: Measurements are taken in EXTRC mode.

- 3: See Figure 11-1 for loading conditions.

### FIGURE 11-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC12C508/C509

## 13.1 DC CHARACTERISTICS:

#### PIC12C508A/509A (Commercial, Industrial, Extended) PIC12CE518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

|             | DC Characteristics<br>Power Supply Pins                                    |                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |                                                                              |  |  |

|-------------|----------------------------------------------------------------------------|----------------|------------------------------------------------------|--------------------|-----|-------|------------------------------------------------------------------------------|--|--|

| Parm<br>No. | Characteristic                                                             | Sym            | Min                                                  | Typ <sup>(1)</sup> | Max | Units | Conditions                                                                   |  |  |

| D001        | Supply Voltage                                                             | Vdd            | 3.0                                                  |                    | 5.5 | V     | Fosc = DC to 4 MHz (Commercial/<br>Industrial, Extended)                     |  |  |

| D002        | RAM Data Retention<br>Voltage <sup>(2)</sup>                               | Vdr            |                                                      | 1.5*               |     | V     | Device in SLEEP mode                                                         |  |  |

| D003        | VDD Start Voltage to ensure<br>Power-on Reset                              | VPOR           |                                                      | Vss                |     | V     | See section on Power-on Reset for details                                    |  |  |

| D004        | VDD Rise Rate to ensure<br>Power-on Reset                                  | SVDD           | 0.05*                                                |                    |     | V/ms  | See section on Power-on Reset for details                                    |  |  |

| D010        | Supply Current <sup>(3)</sup>                                              | IDD            | —                                                    | 0.8                | 1.4 | mA    | XT and EXTRC options (Note 4)<br>Fosc = 4 MHz, VDD = 5.5V                    |  |  |

| D010C       |                                                                            |                | —                                                    | 0.8                | 1.4 | mA    | INTRC Option<br>Fosc = 4 MHz, VDD = 5.5V                                     |  |  |

| D010A       |                                                                            |                | _                                                    | 19                 | 27  | μA    | LP OPTION, Commercial Temperature<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled |  |  |

|             |                                                                            |                | _                                                    | 19                 | 35  | μA    | LP OPTION, Industrial Temperature<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled |  |  |

|             |                                                                            |                | _                                                    | 30                 | 55  | μA    | LP OPTION, Extended Temperature<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled   |  |  |

| D020        | Power-Down Current <sup>(5)</sup>                                          | IPD            | —                                                    | 0.25               | 4   | μA    | VDD = 3.0V, Commercial WDT disabled                                          |  |  |

| D021        |                                                                            |                | -                                                    | 0.25               | 5   | μA    | VDD = 3.0V, Industrial WDT disabled                                          |  |  |

| D021B       |                                                                            |                | -                                                    | 2                  | 12  | μA    | VDD = 3.0V, Extended WDT disabled                                            |  |  |

| D022        | Power-Down Current                                                         | $\Delta I$ WDT | —                                                    | 2.2                | 5   | μA    | VDD = 3.0V, Commercial                                                       |  |  |

|             |                                                                            |                | -                                                    | 2.2                | 6   | μA    | VDD = 3.0V, Industrial                                                       |  |  |

|             |                                                                            |                | -                                                    | 4                  | 11  | μA    | VDD = 3.0V, Extended                                                         |  |  |

|             | Supply Current <sup>(3)</sup><br>During read/write to<br>EEPROM peripheral | ΔIEE           | -                                                    | 0.1                | 0.2 | mA    | FOSC = 4 MHz, Vdd = 5.5V,<br>SCL = 400kHz                                    |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to

- Vss, T0CKI = VDD,  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: Does not include current through Rext. The current through the resistor can be estimated by the formula: IR = VDD/2Rext (mA) with Rext in kOhm.

- 5: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

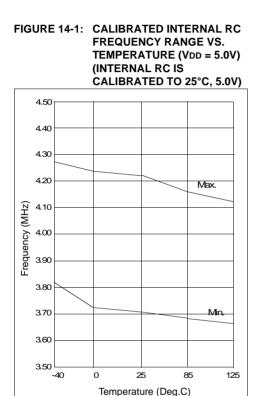

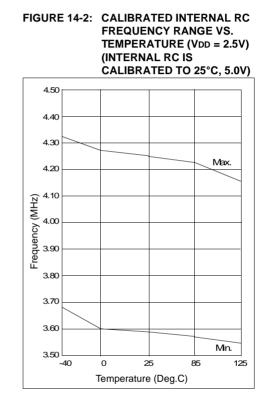

# 14.0 DC AND AC CHARACTERISTICS - PIC12C508A/PIC12C509A/ PIC12LC508A/PIC12LC509A, PIC12CE518/PIC12CE519/PIC12CR509A/ PIC12LCE518/PIC12LCE519/ PIC12LCR509A

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables the data presented are outside specified operating range (e.g., outside specified VDD range). This is for information only and devices will operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

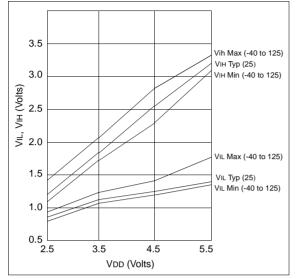

## FIGURE 14-15: VIL, VIH OF NMCLR, AND TOCKI VS. VDD

# **15.0 PACKAGING INFORMATION**

## 15.1 Package Marking Information

## 8-Lead PDIP (300 mil)

## 8-Lead SOIC (150 mil)

#### 8-Lead SOIC (208 mil)

| XXXXXXX<br>XXXXXXX<br>AABBCDE |  |

|-------------------------------|--|

|                               |  |

|                               |  |

# Example 12C508A 04I/PSAZ \$\$ 9825

## Example

## Example

## 8-Lead Windowed Ceramic Side Brazed (300 mil)

#### Example

| Legen | d: MMM     | Microchip part number information                                       |

|-------|------------|-------------------------------------------------------------------------|

|       | XXX        | Customer specific information*                                          |

|       | AA         | Year code (last 2 digits of calendar year)                              |

|       | BB         | Week code (week of January 1 is week '01')                              |

|       | С          | Facility code of the plant at which wafer is manufactured               |

|       |            | O = Outside Vendor                                                      |

|       |            | C = 5" Line                                                             |

|       |            | S = 6" Line                                                             |

|       |            | H = 8" Line                                                             |

|       | D          | Mask revision number                                                    |

|       | E          | Assembly code of the plant or country of origin in which                |

|       |            | part was assembled                                                      |

| Note: | In the eve | nt the full Microchip part number cannot be marked on one line, it will |

|       | be carried | over to the next line thus limiting the number of available characters  |

|       | for custon | ner specific information.                                               |

|       |            |                                                                         |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

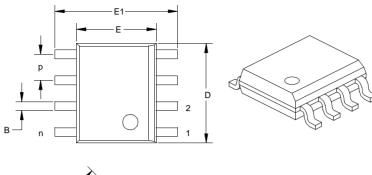

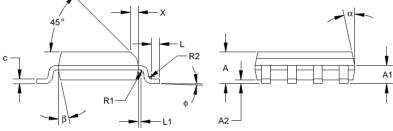

## Package Type: K04-057 8-Lead Plastic Small Outline (SN) - Narrow, 150 mil

| Units                   |                | INCHES* |       |       | MILLIMETERS |      |      |

|-------------------------|----------------|---------|-------|-------|-------------|------|------|

| Dimension Limits        |                | MIN     | NOM   | MAX   | MIN         | NOM  | MAX  |

| Pitch                   | р              |         | 0.050 |       |             | 1.27 |      |

| Number of Pins          | n              |         | 8     |       |             | 8    |      |

| Overall Pack. Height    | A              | 0.054   | 0.061 | 0.069 | 1.37        | 1.56 | 1.75 |

| Shoulder Height         | A1             | 0.027   | 0.035 | 0.044 | 0.69        | 0.90 | 1.11 |

| Standoff                | A2             | 0.004   | 0.007 | 0.010 | 0.10        | 0.18 | 0.25 |

| Molded Package Length   | D‡             | 0.189   | 0.193 | 0.196 | 4.80        | 4.89 | 4.98 |

| Molded Package Width    | E‡             | 0.150   | 0.154 | 0.157 | 3.81        | 3.90 | 3.99 |

| Outside Dimension       | E1             | 0.229   | 0.237 | 0.244 | 5.82        | 6.01 | 6.20 |

| Chamfer Distance        | х              | 0.010   | 0.015 | 0.020 | 0.25        | 0.38 | 0.51 |

| Shoulder Radius         | R1             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13 | 0.25 |

| Gull Wing Radius        | R2             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13 | 0.25 |

| Foot Length             | L              | 0.011   | 0.016 | 0.021 | 0.28        | 0.41 | 0.53 |

| Foot Angle              | φ              | 0       | 4     | 8     | 0           | 4    | 8    |

| Radius Centerline       | L1             | 0.000   | 0.005 | 0.010 | 0.00        | 0.13 | 0.25 |

| Lead Thickness          | с              | 0.008   | 0.009 | 0.010 | 0.19        | 0.22 | 0.25 |

| Lower Lead Width        | B <sup>†</sup> | 0.014   | 0.017 | 0.020 | 0.36        | 0.43 | 0.51 |

| Mold Draft Angle Top    | α              | 0       | 12    | 15    | 0           | 12   | 15   |

| Mold Draft Angle Bottom | β              | 0       | 12    | 15    | 0           | 12   | 15   |

\* Controlling Parameter.

- <sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

- <sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

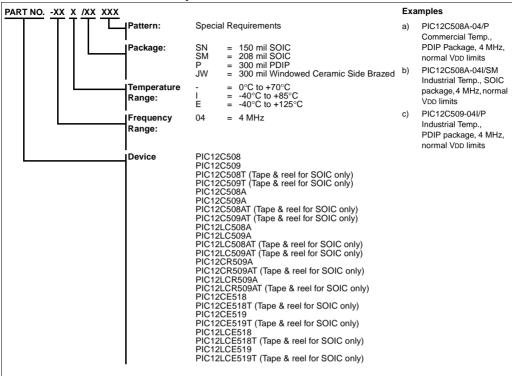

#### PIC12C5XX Product Identification System

Please contact your local sales office for exact ordering procedures.

#### Sales and Support:

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoq® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.