Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 41 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c509-04e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS

| 1.0   | General Description                                                                   | 4   |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | PIC12C5XX Device Varieties                                                            |     |

| 3.0   | Architectural Overview                                                                |     |

| 4.0   | Memory Organization                                                                   | 13  |

| 5.0   | I/O Port                                                                              |     |

| 6.0   | Timer0 Module and TMR0 Register                                                       | 25  |

| 7.0   | EEPROM Peripheral Operation                                                           | 29  |

| 8.0   | Special Features of the CPU                                                           | 35  |

| 9.0   | Instruction Set Summary                                                               | 47  |

| 10.0  | Development Support                                                                   |     |

| 11.0  | Electrical Characteristics - PIC12C508/PIC12C509                                      | 65  |

| 12.0  | DC and AC Characteristics - PIC12C508/PIC12C509                                       | 75  |

| 13.0  | Electrical Characteristics PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CR509A/ |     |

|       | PIC12CE518/PIC12CE519/                                                                |     |

|       | PIC12LCE518/PIC12LCE519/PIC12LCR509A                                                  | 79  |

| 14.0  | DC and AC Characteristics                                                             |     |

|       | PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CE518/PIC12CE519/PIC12CR509A/      |     |

|       | PIC12LCE518/PIC12LCE519/ PIC12LCR509A                                                 | 93  |

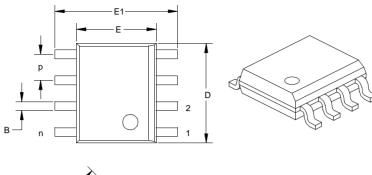

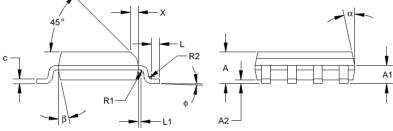

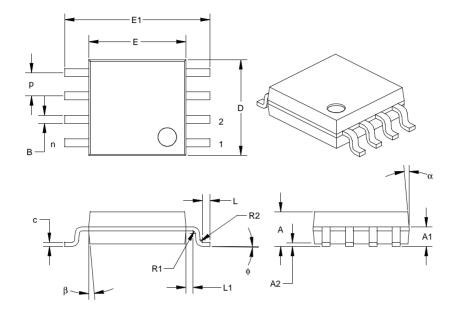

| 15.0  | Packaging Information                                                                 | 99  |

| Index | ۲                                                                                     | 105 |

|       | 2C5XX Product Identification System                                                   |     |

| Sales | and Support:                                                                          | 109 |

# To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

# PIC12C5XX

NOTES:

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The special registers can be classified into two sets. The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

# TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

|                    |                                                                                     |                             |                                      |             |           |                        |              |         |       | Value on<br>Power-On | Value on<br>All Other    |

|--------------------|-------------------------------------------------------------------------------------|-----------------------------|--------------------------------------|-------------|-----------|------------------------|--------------|---------|-------|----------------------|--------------------------|

| Address            | Name                                                                                | Bit 7                       | Bit 6                                | Bit 5       | Bit 4     | Bit 3                  | Bit 2        | Bit 1   | Bit 0 | Reset                | Resets <sup>(2)</sup>    |

| N/A                | TRIS                                                                                | —                           | I                                    |             |           |                        |              |         |       | 11 1111              | 11 1111                  |

| N/A                | OPTION                                                                              | Contains co<br>prescaler, v |                                      |             |           | Timer0/WD1<br>pull-ups | Г            |         |       | 1111 1111            | 1111 1111                |

| 00h                | INDF                                                                                | Uses conte                  | ents of FSR                          | R to addres | s data me | mory (not a            | physical reg | jister) |       | xxxx xxxx            | uuuu uuuu                |

| 01h                | TMR0                                                                                | 8-bit real-ti               | me clock/c                           | ounter      |           |                        |              |         |       | xxxx xxxx            | uuuu uuuu                |

| 02h <sup>(1)</sup> | PCL                                                                                 | Low order                   | B bits of PC                         | c           |           |                        |              |         |       | 1111 1111            | 1111 1111                |

| 03h                | STATUS                                                                              | GPWUF                       | -                                    | PA0         | TO        | PD                     | Z            | DC      | С     | 0001 1xxx            | q00q quuu <sup>(3)</sup> |

| 04h                | FSR<br>(PIC12C508/<br>PIC12C508A/<br>PIC12C518)                                     | Indirect dat                | ndirect data memory address pointer  |             |           |                        |              |         | 1     | 111x xxxx            | 111u uuuu                |

| 04h                | FSR<br>(PIC12C509/<br>PIC12C509A/<br>PIC12CR509A/<br>PIC12CE519)                    | Indirect dat                | Indirect data memory address pointer |             |           |                        |              |         |       | 110x xxxx            | 11uu uuuu                |

| 05h                | OSCCAL<br>(PIC12C508/<br>PIC12C509)                                                 | CAL3                        | CAL2                                 | CAL1        | CAL0      | _                      | _            | _       | _     | 0111                 | uuuu                     |

| 05h                | OSCCAL<br>(PIC12C508A/<br>PIC12C509A/<br>PIC12CE518/<br>PIC12CE519/<br>PIC12CR509A) | CAL5                        | CAL4                                 | CAL3        | CAL2      | CAL1                   | CAL0         |         | _     | 1000 00              | uuuu uu                  |

| 06h                | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CC509A)     | _                           | _                                    | GP5         | GP4       | GP3                    | GP2          | GP1     | GP0   | xx xxxx              | uu uuuu                  |

| 06h                | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                                 | SCL                         | SDA                                  | GP5         | GP4       | GP3                    | GP2          | GP1     | GP0   | 11xx xxxx            | 11uu uuuu                |

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as '0' (if applicable)

x = unknown, u = unchanged, q = see the tables in Section 8.7 for possible values.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 for an explanation of how to access these bits.

2: Other (non power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

3: If reset was due to wake-up on pin change then bit 7 = 1. All other resets will cause bit 7 = 0.

#### 4.4 OPTION Register

The OPTION register is a 8-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A RESET sets the OPTION<7:0> bits.

# FIGURE 4-5: OPTION REGISTER

Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin; i.e., note that TRIS overrides OPTION control of GPPU and GPWU.

**Note:** If the TOCS bit is set to '1', GP2 is forced to be an input even if TRIS GP2 = '0'.

| W-1      | W-1                                                                                                                                                                 | W-1                                                                                                                                      | W-1         | W-1        | W-1         | W-1 | W-1  |                                                                                               |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-----|------|-----------------------------------------------------------------------------------------------|--|--|--|

| GPWU     | GPPU                                                                                                                                                                | TOCS                                                                                                                                     | T0SE        | PSA        | PS2         | PS1 | PS0  | W = Writable bit                                                                              |  |  |  |

| oit7     | 6                                                                                                                                                                   | 5                                                                                                                                        | 4           | 3          | 2           | 1   | bit0 | U = Unimplemented bit<br>- n = Value at POR reset<br>Reference Table 4-1 for<br>other resets. |  |  |  |

| bit 7:   | <b>GPWU</b> : Ena<br>1 = Disable<br>0 = Enable                                                                                                                      | d                                                                                                                                        | p on pin cl | hange (GP  | 0, GP1, GP3 | )   |      |                                                                                               |  |  |  |

| bit 6:   | <b>GPPU</b> : Ena<br>1 = Disable<br>0 = Enablec                                                                                                                     | d .                                                                                                                                      | III-ups (GF | 90, GP1, G | P3)         |     |      |                                                                                               |  |  |  |

| bit 5:   | 1 = Transitio                                                                                                                                                       | <b>TOCS:</b> Timer0 clock source select bit<br>1 = Transition on T0CKI pin<br>0 = Transition on internal instruction cycle clock, Fosc/4 |             |            |             |     |      |                                                                                               |  |  |  |

| bit 4:   | <b>TOSE</b> : Timer0 source edge select bit<br>1 = Increment on high to low transition on the TOCKI pin<br>0 = Increment on low to high transition on the TOCKI pin |                                                                                                                                          |             |            |             |     |      |                                                                                               |  |  |  |

| bit 3:   | PSA: Prescaler assignment bit<br>1 = Prescaler assigned to the WDT<br>0 = Prescaler assigned to Timer0                                                              |                                                                                                                                          |             |            |             |     |      |                                                                                               |  |  |  |

| bit 2-0: | PS2:PS0: P                                                                                                                                                          | Prescaler rat                                                                                                                            | e select bi | its        |             |     |      |                                                                                               |  |  |  |

|          | Bit Value                                                                                                                                                           | Timer0 R                                                                                                                                 | ate WDT     | Rate       |             |     |      |                                                                                               |  |  |  |

|          | 000                                                                                                                                                                 | 1:2<br>1:4                                                                                                                               | 1:          | 2          |             |     |      |                                                                                               |  |  |  |

|          | 010<br>011                                                                                                                                                          | 1:8                                                                                                                                      | 1:          |            |             |     |      |                                                                                               |  |  |  |

|          | 100                                                                                                                                                                 | 1:32                                                                                                                                     |             | 0<br>16    |             |     |      |                                                                                               |  |  |  |

|          | 101                                                                                                                                                                 | 1:64                                                                                                                                     |             | 32         |             |     |      |                                                                                               |  |  |  |

|          | 110                                                                                                                                                                 | 1:128                                                                                                                                    |             | 64         |             |     |      |                                                                                               |  |  |  |

|          | 111                                                                                                                                                                 | 1:256                                                                                                                                    | : 1.        | 128        |             |     |      |                                                                                               |  |  |  |

# 4.6 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

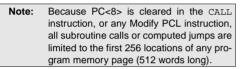

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4-8).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-8).

Instructions where the PCL is the destination, or Modify PCL instructions, include <code>MOVWF PC</code>, <code>ADDWF PC</code>, and <code>BSF PC</code>, <code>5</code>.

# FIGURE 4-8: LOADING OF PC BRANCH INSTRUCTIONS -PIC12C5XX

### 4.6.1 EFFECTS OF RESET

The Program Counter is set upon a RESET, which means that the PC addresses the last location in the last page i.e., the oscillator calibration instruction. After executing MOVLW XX, the PC will roll over to location 00h, and begin executing user code.

The STATUS register page preselect bits are cleared upon a RESET, which means that page 0 is pre-selected.

Therefore, upon a RESET, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

# 4.7 Stack

PIC12C5XX devices have a 12-bit wide L.I.F.O. hardware push/pop stack.

A CALL instruction will *push* the current value of stack 1 into stack 2 and then push the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will *pop* the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

Upon any reset, the contents of the stack remain unchanged, however the program counter (PCL) will also be reset to 0.

- Note 1: There are no STATUS bits to indicate stack overflows or stack underflow conditions.

- Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL and RETLW instructions.

| TABLE 5-1: S | UMMARY OF PORT | <b>REGISTERS</b> |

|--------------|----------------|------------------|

|--------------|----------------|------------------|

| Address | Name                                                                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|---------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------|

| N/A     | TRIS                                                                            | —     | -     |       |       |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | OPTION                                                                          | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                    |

| 03H     | STATUS                                                                          | GPWUF | -     | PAO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>     |

| 06h     | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CR509A) |       | _     | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                      |

| 06h     | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                             | SCL   | SDA   | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 11xx xxxx                     | 11uu uuuu                    |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, g = see tables in Section 8.7 for possible values.

Note 1: If reset was due to wake-up on change, then bit 7 = 1. All other resets will cause bit 7 = 0.

#### 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of GPIO will cause all eight bits of GPIO to be read into the CPU, bit5 to be set and the GPIO value to be written to the output latches. If another bit of GPIO is used as a bidirectional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}$  ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wiredand"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ; | ;Initial GPIO Settings |         |       |      |         |     |        |  |

|---|------------------------|---------|-------|------|---------|-----|--------|--|

| ; | GPIO<5                 | 5:3> In | puts  | 3    |         |     |        |  |

| ; | GPIO<2                 | 2:0> Ou | itput | s    |         |     |        |  |

| ; |                        |         |       |      |         |     |        |  |

| ; |                        |         |       | GPIC | ) latch | GPI | ) pins |  |

| ; |                        |         |       |      |         |     |        |  |

|   | BCF                    | GPIO,   | 5     | ;01  | -ppp    | 11  | pppp   |  |

|   | BCF                    | GPIO,   | 4     | ;10  | -ppp    | 11  | pppp   |  |

|   | MOVLW                  | 007h    |       | ;    |         |     |        |  |

|   | TRIS                   | GPIO    |       | ;10  | -ppp    | 11  | pppp   |  |

|   |                        |         |       |      |         |     |        |  |

;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;GP5 to be latched as the pin value (High).

# 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

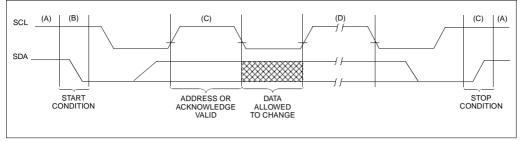

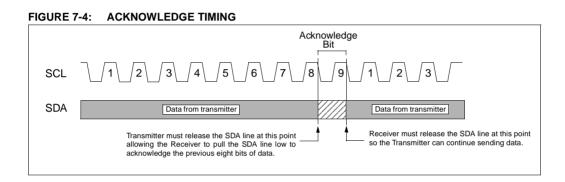

# FIGURE 7-3: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

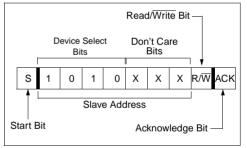

# 7.2 Device Addressing

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed. The slave address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

#### FIGURE 7-5: CONTROL BYTE FORMAT

# 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

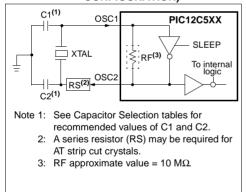

# 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

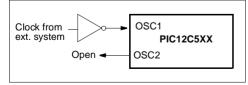

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

#### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

#### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

#### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

# TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq C1  |          | Cap. Range<br>C2 |

|-------------|-----------------------|----------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF    | 15 pF            |

| XT          | 200 kHz               | 47-68 pF | 47-68 pF         |

|             | 1 MHz                 | 15 pF    | 15 pF            |

|             | 4 MHz                 | 15 pF    | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 8.7 <u>Time-Out Sequence, Power Down,</u> and Wake-up from SLEEP Status Bits (TO/PD/GPWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits in the STATUS register can be tested to determine if a RESET condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) reset.

| TABLE 8-7: | TO/PD/GPWUF STATUS |

|------------|--------------------|

|            | AFTER RESET        |

| GPWUF | то | PD | RESET caused by                     |  |  |  |

|-------|----|----|-------------------------------------|--|--|--|

| 0     | 0  | 0  | WDT wake-up from<br>SLEEP           |  |  |  |

| 0     | 0  | u  | WDT time-out (not from<br>SLEEP)    |  |  |  |

| 0     | 1  | 0  | MCLR wake-up from<br>SLEEP          |  |  |  |

| 0     | 1  | 1  | Power-up                            |  |  |  |

| 0     | u  | u  | MCLR not during SLEEP               |  |  |  |

| 1     | 1  | 0  | Wake-up from SLEEP on<br>pin change |  |  |  |

Legend: u = unchanged

Note 1: The TO, PD, and GPWUF bits maintain their status (u) until a reset occurs. A lowpulse on the MCLR input does not change the TO, PD, and GPWUF status bits.

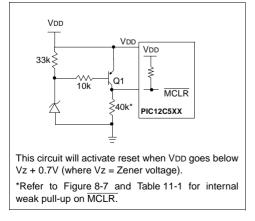

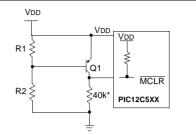

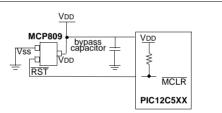

# 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset PIC12C5XX devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-13 , Figure 8-14 and Figure 8-15

#### FIGURE 8-13: BROWN-OUT PROTECTION CIRCUIT 1

# FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

\*Refer to Figure 8-7 and Table 11-1 for internal weak pull-up on MCLR.

# FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX family of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accomodate 5V and 3V systems.

#### 8.9 Power-Down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

#### 8.9.1 SLEEP

The Power-Down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{TO}$  bit (STATUS<4>) is set, the  $\overline{PD}$  bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low, or hi-impedance).

It should be noted that a RESET generated by a WDT time-out does not drive the  $\overline{\text{MCLR}}$  pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or VSs and the GP3/ MCLR/VPP pin must be at a logic high level (VIHMC) if MCLR is enabled.

#### 8.9.2 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. An external reset input on GP3/MCLR/VPP pin, when configured as MCLR.

- 2. A Watchdog Timer time-out reset (if WDT was enabled).

- A change on input pin GP0, GP1, or GP3/ MCLR/VPP when wake-up on change is enabled.

These events cause a device reset. The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits can be used to determine the cause of device reset. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF bit indicates a change in state while in SLEEP at pins GP0, GP1, or GP3 (since the last time there was a file or bit operation on GP port).

Caution: Right before entering SLEEP, read the input pins. When in SLEEP, wake up occurs when the values at the pins change from the state they were in at the last reading. If a wake-up on change occurs and the pins are not read before reentering SLEEP, a wake up will occur immediately even if no pins change while in SLEEP mode.

The WDT is cleared when the device wakes from sleep, regardless of the wake-up source.

### 8.10 Program Verification/Code Protection

If the code protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations can be read by the PIC12C5XX regardless of the code protection bit setting.

The last memory location cannot be read if code protection is enabled on the PIC12C508/509.

The last memory location can be read regardless of the code protection bit setting on the PIC12C508A/509A/CR509A/CE518/CE519.

# 8.11 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other codeidentification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '0's.

# PIC12C5XX

| CALL                  | Subroutine Call                                                                                                                                                                                                                                |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:               | [ <i>label</i> ] CALL k                                                                                                                                                                                                                        |  |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                                                                              |  |  |  |  |  |

| Operation:            | $\begin{array}{l} (PC) + 1 \rightarrow \text{Top of Stack}; \\ k \rightarrow PC < 7:0>; \\ (STATUS < 6:5>) \rightarrow PC < 10:9>; \\ 0 \rightarrow PC < 8> \end{array}$                                                                       |  |  |  |  |  |

| Status Affected:      | None                                                                                                                                                                                                                                           |  |  |  |  |  |

| Encoding:             | 1001 kkkk kkkk                                                                                                                                                                                                                                 |  |  |  |  |  |

| Description:          | Subroutine call. First, return address (PC+1) is pushed onto the stack. The eight bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STA-TUS<6:5>, PC<8> is cleared. CALL is a two cycle instruction. |  |  |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                              |  |  |  |  |  |

| Cycles:               | 2                                                                                                                                                                                                                                              |  |  |  |  |  |

| Example:              | HERE CALL THERE                                                                                                                                                                                                                                |  |  |  |  |  |

| Before Instru<br>PC = |                                                                                                                                                                                                                                                |  |  |  |  |  |

|                       | tion<br>address (THERE)<br>address (HERE + 1)                                                                                                                                                                                                  |  |  |  |  |  |

# CLRF

| Syntax:                               | [label] CLRF f                                                         |           |      |  |  |  |  |

|---------------------------------------|------------------------------------------------------------------------|-----------|------|--|--|--|--|

| Operands:                             | $0 \le f \le 31$                                                       |           |      |  |  |  |  |

| Operation:                            | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |           |      |  |  |  |  |

| Status Affected: Z                    |                                                                        |           |      |  |  |  |  |

| Encoding:                             | 0000                                                                   | 011f      | ffff |  |  |  |  |

| Description:                          | The contents of register 'f' are cleared and the Z bit is set.         |           |      |  |  |  |  |

| Words: 1                              |                                                                        |           |      |  |  |  |  |

| Cycles:                               | 1                                                                      |           |      |  |  |  |  |

| Example:                              | CLRF                                                                   | FLAG_REG  |      |  |  |  |  |

| Before Instruction<br>FLAG_REG = 0x5A |                                                                        |           |      |  |  |  |  |

| After Instruct<br>FLAG_RE<br>Z        |                                                                        | 0x00<br>1 |      |  |  |  |  |

Clear f

| CLRW                                                                                                     | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation:                                                                                               | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}); \\ 1 \rightarrow \text{Z} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                                                                                             | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                                 | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Before Instru<br>W =                                                                                     | uction<br>0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| After Instruct<br>W =<br>Z =                                                                             | tion<br>0x00<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |