Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.5KB (1K × 12)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 41 × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 8-SOIJ                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c509a-04e-sm |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

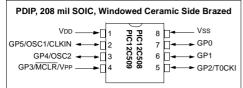

### Pin Diagram - PIC12C508/509

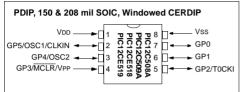

### Pin Diagram - PIC12C508A/509A, PIC12CE518/519

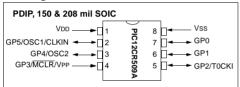

### Pin Diagram - PIC12CR509A

### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

### TABLE OF CONTENTS

| 1.0   | General Description                                                                   | 4   |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | PIC12C5XX Device Varieties                                                            |     |

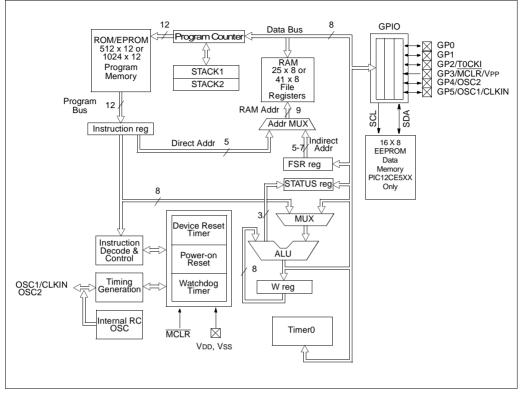

| 3.0   | Architectural Overview                                                                |     |

| 4.0   | Memory Organization                                                                   | 13  |

| 5.0   | I/O Port                                                                              |     |

| 6.0   | Timer0 Module and TMR0 Register                                                       | 25  |

| 7.0   | EEPROM Peripheral Operation                                                           | 29  |

| 8.0   | Special Features of the CPU                                                           | 35  |

| 9.0   | Instruction Set Summary                                                               | 47  |

| 10.0  | Development Support                                                                   |     |

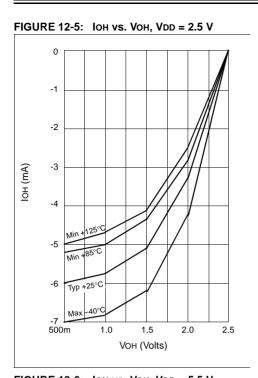

| 11.0  | Electrical Characteristics - PIC12C508/PIC12C509                                      | 65  |

| 12.0  | DC and AC Characteristics - PIC12C508/PIC12C509                                       | 75  |

| 13.0  | Electrical Characteristics PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CR509A/ |     |

|       | PIC12CE518/PIC12CE519/                                                                |     |

|       | PIC12LCE518/PIC12LCE519/PIC12LCR509A                                                  | 79  |

| 14.0  | DC and AC Characteristics                                                             |     |

|       | PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CE518/PIC12CE519/PIC12CR509A/      |     |

|       | PIC12LCE518/PIC12LCE519/ PIC12LCR509A                                                 | 93  |

| 15.0  | Packaging Information                                                                 | 99  |

| Index | ۲                                                                                     | 105 |

|       | 2C5XX Product Identification System                                                   |     |

| Sales | and Support:                                                                          | 109 |

### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

| TABLE 5-1: S | UMMARY OF PORT | <b>REGISTERS</b> |

|--------------|----------------|------------------|

|--------------|----------------|------------------|

| Address | Name                                                                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|---------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------|

| N/A     | TRIS                                                                            | —     | -     |       |       |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | OPTION                                                                          | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                    |

| 03H     | STATUS                                                                          | GPWUF | -     | PAO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>     |

| 06h     | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CR509A) |       | _     | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                      |

| 06h     | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                             | SCL   | SDA   | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 11xx xxxx                     | 11uu uuuu                    |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, g = see tables in Section 8.7 for possible values.

Note 1: If reset was due to wake-up on change, then bit 7 = 1. All other resets will cause bit 7 = 0.

### 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of GPIO will cause all eight bits of GPIO to be read into the CPU, bit5 to be set and the GPIO value to be written to the output latches. If another bit of GPIO is used as a bidirectional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}$  ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wiredand"). The resulting high output currents may damage the chip.

### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ; | Initia | L GPIO  | Sett  | ings |         |     |        |

|---|--------|---------|-------|------|---------|-----|--------|

| ; | GPIO<5 | 5:3> In | puts  | 3    |         |     |        |

| ; | GPIO<2 | 2:0> Ou | itput | s    |         |     |        |

| ; |        |         |       |      |         |     |        |

| ; |        |         |       | GPIC | ) latch | GPI | ) pins |

| ; |        |         |       |      |         |     |        |

|   | BCF    | GPIO,   | 5     | ;01  | -ppp    | 11  | pppp   |

|   | BCF    | GPIO,   | 4     | ;10  | -ppp    | 11  | pppp   |

|   | MOVLW  | 007h    |       | ;    |         |     |        |

|   | TRIS   | GPIO    |       | ;10  | -ppp    | 11  | pppp   |

|   |        |         |       |      |         |     |        |

;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;GP5 to be latched as the pin value (High).

### 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

### FIGURE 5-2: SUCCESSIVE I/O OPERATION

| PC         | Y PC + 1                         | X PC + 2                                                                         | X PC + 3                                                                                | This example shows a write to GPIO follower                                                                 |  |

|------------|----------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| MOVWF GPIO | MOVF GPIO,W                      | NOP                                                                              | NOP                                                                                     | by a read from GPIO.<br>Data setup time = (0.25 Tcy – TpD)                                                  |  |

|            | 1<br>1<br>1                      | X                                                                                | 1                                                                                       | where: TCY = instruction cycle.<br>TPD = propagation delay                                                  |  |

|            | Port pin<br>written here         | Port pin<br>sampled here                                                         | ,<br>,<br>,<br>,                                                                        | Therefore, at higher clock frequencies, a write followed by a read may be problematic                       |  |

|            | MOVWF GPIO<br>(Write to<br>GPIO) | MOVF GPIO,W<br>(Read<br>GPIO)                                                    | NOP                                                                                     |                                                                                                             |  |

|            |                                  | MOVWF GPIO<br>MOVF GPIO,W<br>Port pin<br>written here<br>MOVWF GPIO<br>(Write to | MOVWF GPIO MOVF GPIO,W NOP Port pin written here MOVWF GPIO MOVF GPIO,W (Write to (Read | MOVWF GPIO MOVF GPIO,W NOP NOP<br>Port pin<br>written here<br>MOVWF GPIO MOVF GPIO,W NOP<br>(Write to (Read |  |

### 8.2 Oscillator Configurations

### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

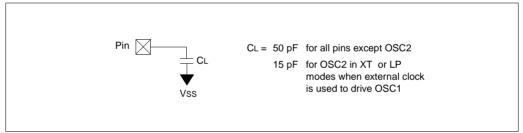

### 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

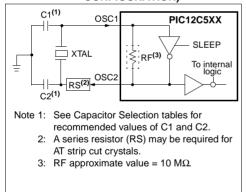

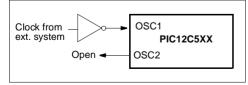

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |  |

|------|-----------|------------|------------|--|

| Type | Freq      | C1         | C2         |  |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |  |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

### 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 8-4 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

### FIGURE 8-4: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

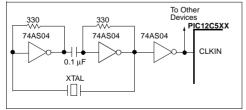

Figure 8-5 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 8-5: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

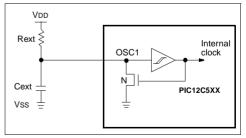

### 8.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 8-6 shows how the R/C combination is connected to the PIC12C5XX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

### FIGURE 8-6: EXTERNAL RC OSCILLATOR MODE

TABLE 8-3: RESET CONDITIONS FOR REGISTERS

| Register                                                                    | Address | Power-on Reset | MCLR Reset<br>WDT time-out<br>Wake-up on Pin Change |

|-----------------------------------------------------------------------------|---------|----------------|-----------------------------------------------------|

| W (PIC12C508/509)                                                           | _       | qqqq xxxx (1)  | qqqq uuuu (1)                                       |

| W (PIC12C508A/509A/<br>PIC12CE518/519/<br>PIC12CE509A)                      | _       | qqqq qqxx (1)  | qqqq qquu (1)                                       |

| INDF                                                                        | 00h     | xxxx xxxx      | uuuu uuuu                                           |

| TMR0                                                                        | 01h     | xxxx xxxx      | uuuu uuuu                                           |

| PC                                                                          | 02h     | 1111 1111      | 1111 1111                                           |

| STATUS                                                                      | 03h     | 0001 1xxx      | q00q quuu (2,3)                                     |

| FSR (PIC12C508/<br>PIC12C508A/<br>PIC12CE518)                               | 04h     | 111x xxxx      | 111u uuuu                                           |

| FSR (PIC12C509/<br>PIC12C509A/<br>PIC12CE519/<br>PIC12CR509A)               | 04h     | 110x xxxx      | 11uu uuuu                                           |

| OSCCAL<br>(PIC12C508/509)                                                   | 05h     | 0111           | uuuu                                                |

| OSCCAL<br>(PIC12C508A/509A/<br>PIC12CE518/512/<br>PIC12CR509A)              | 05h     | 1000 00        | uuuu uu                                             |

| GPIO<br>(PIC12C508/PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CR509A) | 06h     | xx xxxx        | uu uuuu                                             |

| GPIO<br>(PIC12CE518/                                                        | 06h     | 11             | 11                                                  |

| PIC12CE519)<br>OPTION                                                       |         | 11xx xxxx      | 11uu uuuu                                           |

| TRIS                                                                        | —       | 1111 1111      | 1111 1111                                           |

| IKIS                                                                        |         | 11 1111        | 11 1111                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

Note 2: See Table 8-7 for reset value for specific conditions

**Note 3:** If reset was due to wake-up on pin change, then bit 7 = 1. All other resets will cause bit 7 = 0.

### TABLE 8-4: RESET CONDITION FOR SPECIAL REGISTERS

|                                    | STATUS Addr: 03h | PCL Addr: 02h |

|------------------------------------|------------------|---------------|

| Power on reset                     | 0001 1xxx        | 1111 1111     |

| MCLR reset during normal operation | 000u uuuu        | 1111 1111     |

| MCLR reset during SLEEP            | 0001 0uuu        | 1111 1111     |

| WDT reset during SLEEP             | 0000 Ouuu        | 1111 1111     |

| WDT reset normal operation         | 0000 uuuu        | 1111 1111     |

| Wake-up from SLEEP on pin change   | 1001 Ouuu        | 1111 1111     |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

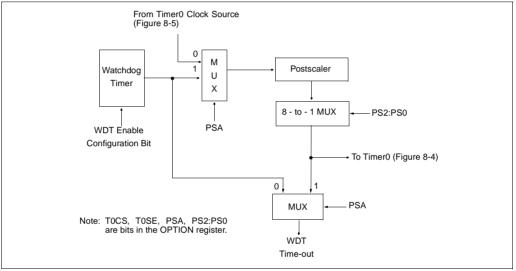

### 8.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

### 8.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT wake-up reset.

### FIGURE 8-12: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 8-6: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer, - = unimplemented, read as '0', u = unchanged

## PIC12C5XX

| CALL                  | Subroutine Call                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:               | [ <i>label</i> ] CALL k                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Operation:            | $\begin{array}{l} (PC) + 1 \rightarrow \text{Top of Stack;} \\ k \rightarrow PC < 7:0>; \\ (STATUS < 6:5>) \rightarrow PC < 10:9>; \\ 0 \rightarrow PC < 8> \end{array}$                                                                       |  |  |  |  |  |  |  |

| Status Affected:      | None                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Encoding:             | 1001 kkkk kkkk                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:          | Subroutine call. First, return address (PC+1) is pushed onto the stack. The eight bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STA-TUS<6:5>, PC<8> is cleared. CALL is a two cycle instruction. |  |  |  |  |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Cycles:               | 2                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Example:              | HERE CALL THERE                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Before Instru<br>PC = |                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

### CLRF

| Syntax:                        | [label] CLRF f                                                         |                             |              |         |  |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------|-----------------------------|--------------|---------|--|--|--|--|--|

| Operands:                      | $0 \le f \le 31$                                                       |                             |              |         |  |  |  |  |  |

| Operation:                     | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |                             |              |         |  |  |  |  |  |

| Status Affected: Z             |                                                                        |                             |              |         |  |  |  |  |  |

| Encoding:                      | 0000 011f ffff                                                         |                             |              |         |  |  |  |  |  |

| Description:                   | The conte<br>and the Z                                                 | nts of regis<br>bit is set. | ster 'f' are | cleared |  |  |  |  |  |

| Words:                         | 1                                                                      |                             |              |         |  |  |  |  |  |

| Cycles:                        | 1                                                                      |                             |              |         |  |  |  |  |  |

| Example:                       | CLRF                                                                   | FLAG_REC                    | 3            |         |  |  |  |  |  |

| Before Instru<br>FLAG_RE       |                                                                        | 0x5A                        |              |         |  |  |  |  |  |

| After Instruct<br>FLAG_RE<br>Z |                                                                        | 0x00<br>1                   |              |         |  |  |  |  |  |

Clear f

| CLRW                                                                                                     | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                                                                  | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operation:                                                                                               | $\begin{array}{l} \text{00h} \rightarrow (\text{W}); \\ 1 \rightarrow \text{Z} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Encoding:                                                                                                | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Description:                                                                                             | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Example:                                                                                                 | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Before Instru<br>W =                                                                                     | uction<br>0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| After Instruct<br>W =<br>Z =                                                                             | tion<br>0x00<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| CLRWDT<br>Syntax:                                                                                        | Clear Watchdog Timer<br>[label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| -                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Syntax:                                                                                                  | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                     | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |