Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               |                                                                             |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.5KB (1K x 12)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                |                                                                             |

| RAM Size                   | 41 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 8-SOIJ                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c509at-04-sm |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC12C5XX

NOTES:

## PIC12C5XX

NOTES:

| Name           | DIP<br>Pin # | SOIC<br>Pin # | l/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|--------------|---------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0            | 7            | 7             | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming data. Can<br>be software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming<br>mode.                                                                                                                                                                                                               |

| GP1            | 6            | 6             | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming clock. Can<br>be software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming<br>mode.                                                                                                                                                                                                              |

| GP2/T0CKI      | 5            | 5             | I/O           | ST             | Bi-directional I/O port. Can be configured as T0CKI.                                                                                                                                                                                                                                                                                                                                                                                                |

| GP3/MCLR/Vpp   | 4            | 4             | Ι             | TTL/ST         | Input port/master clear (reset) input/programming volt-<br>age input. When configured as MCLR, this pin is an<br>active low reset to the device. Voltage on MCLR/VPP<br>must not exceed VDD during normal device operation<br>or the device will enter programming mode. Can be<br>software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. Weak pull-up<br>always on if configured as MCLR. ST when in MCLR<br>mode. |

| GP4/OSC2       | 3            | 3             | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output. Con-<br>nections to crystal or resonator in crystal oscillator<br>mode (XT and LP modes only, GPIO in other modes).                                                                                                                                                                                                                                                                              |

| GP5/OSC1/CLKIN | 2            | 2             | I/O           | TTL/ST         | Bidirectional IO port/oscillator crystal input/external<br>clock source input (GPIO in Internal RC mode only,<br>OSC1 in all other oscillator modes). TTL input when<br>GPIO, ST input in external RC oscillator mode.                                                                                                                                                                                                                              |

| Vdd            | 1            | 1             | Р             | _              | Positive supply for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vss            | 8            | 8             | Р             | _              | Ground reference for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                                             |

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input

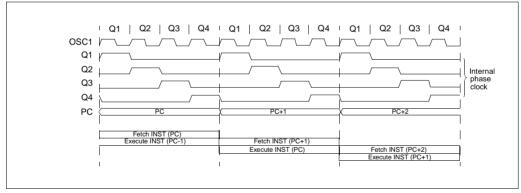

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

## FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

## 4.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status, and the page preselect bit for program memories larger than 512 words.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS register because these instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions, which do affect STATUS bits, see Instruction Set Summary.

## FIGURE 4-4: STATUS REGISTER (ADDRESS:03h)

| <u>R/W-0</u><br>GPWUF | R/W-0                                                                                                                                                                                                                                                                                                                                                                | R/W-0<br>PA0                                           | <u>R-1</u><br>TO                               | R-1<br>PD                          | R/W-x<br>Z                                     | R/W-x<br>DC | R/W-x<br>C                    | R = Readable bit                                   |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|------------------------------------|------------------------------------------------|-------------|-------------------------------|----------------------------------------------------|--|--|--|

| t7                    | 6                                                                                                                                                                                                                                                                                                                                                                    | 5                                                      | 4                                              | 3                                  | 2                                              | 1           | bit0                          | W = Writable bit<br>- n = Value at POR reset       |  |  |  |

|                       | GPWUF: GPIO reset bit         1 = Reset due to wake-up from SLEEP on pin change         0 = After power up or other reset                                                                                                                                                                                                                                            |                                                        |                                                |                                    |                                                |             |                               |                                                    |  |  |  |

| it 6:                 | Unimplem                                                                                                                                                                                                                                                                                                                                                             | ented                                                  |                                                |                                    |                                                |             |                               |                                                    |  |  |  |

|                       | 0 = Page 0<br>Each page<br>Using the F                                                                                                                                                                                                                                                                                                                               | (200h - 3F<br>(000h - 1F<br>is 512 byte<br>A0 bit as a | Fh) - PIC12<br>Fh) - PIC12<br>s.<br>general pu | 2C509, PIC<br>2C5XX<br>irpose read |                                                | evices whic | h do not use                  | 2CE519<br>e it for program<br>ith future products. |  |  |  |

|                       | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                                                                                                                      |                                                        |                                                |                                    |                                                |             |                               |                                                    |  |  |  |

|                       | <b>PD</b> : Power-down bit         1 = After power-up or by the CLRWDT instruction         0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                 |                                                        |                                                |                                    |                                                |             |                               |                                                    |  |  |  |

|                       | Z: Zero bit<br>1 = The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                                                                                          |                                                        |                                                |                                    |                                                |             |                               |                                                    |  |  |  |

|                       | DC: Digit carry/borrow bit (for ADDWF and SUBWF instructions)<br>ADDWF<br>1 = A carry from the 4th low order bit of the result occurred<br>0 = A carry from the 4th low order bit of the result did not occur<br>SUBWF<br>1 = A borrow from the 4th low order bit of the result did not occur<br>0 = A borrow from the 4th low order bit of the result did not occur |                                                        |                                                |                                    |                                                |             |                               |                                                    |  |  |  |

|                       | ADDWF<br>1 = A carry                                                                                                                                                                                                                                                                                                                                                 |                                                        |                                                | SUBWF<br>1 = A bor                 | RF, RLF instr<br>row did not c<br>row occurred | occur       | <b>RRF or R</b><br>Load bit w | LF<br>vith LSB or MSB, respectively                |  |  |  |

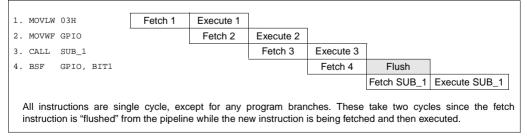

## 5.0 I/O PORT

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

## 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the output data latches. That is, if an output      |

|-------|---------------------------------------------------------------------------------------------|

|       | driver on a pin is enabled and driven high,                                                 |

|       | but the external system is holding it low, a read of the port will indicate that the pin is |

|       | low.                                                                                        |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

## 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

## FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

## FIGURE 5-2: SUCCESSIVE I/O OPERATION

| PC         | Y PC + 1                         | X PC + 2                                                                         | X PC + 3                                                                                | This example shows a write to GPIO follower                                                                 |

|------------|----------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| MOVWF GPIO | MOVF GPIO,W                      | NOP                                                                              | NOP                                                                                     | by a read from GPIO.<br>Data setup time = (0.25 Tcy – TpD)                                                  |

|            | 1<br>1<br>1                      | X                                                                                | 1                                                                                       | where: TCY = instruction cycle.<br>TPD = propagation delay                                                  |

|            | Port pin<br>written here         | Port pin<br>sampled here                                                         | ,<br>,<br>,<br>,                                                                        | Therefore, at higher clock frequencies, a write followed by a read may be problematic                       |

|            | MOVWF GPIO<br>(Write to<br>GPIO) | MOVF GPIO,W<br>(Read<br>GPIO)                                                    | NOP                                                                                     |                                                                                                             |

|            |                                  | MOVWF GPIO<br>MOVF GPIO,W<br>Port pin<br>written here<br>MOVWF GPIO<br>(Write to | MOVWF GPIO MOVF GPIO,W NOP Port pin written here MOVWF GPIO MOVF GPIO,W (Write to (Read | MOVWF GPIO MOVF GPIO,W NOP NOP<br>Port pin<br>written here<br>MOVWF GPIO MOVF GPIO,W NOP<br>(Write to (Read |

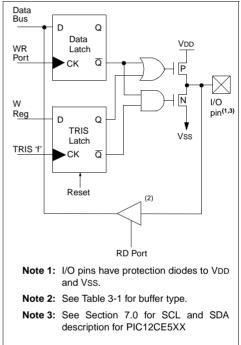

## 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

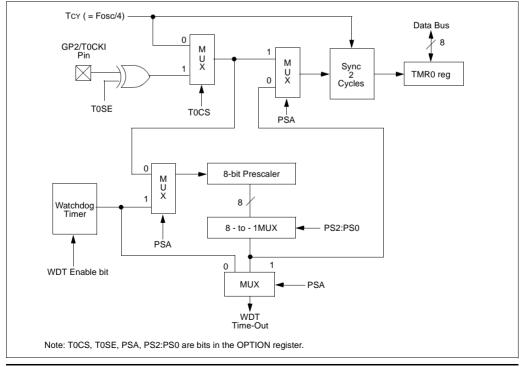

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 6.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

#### FIGURE 6-1: TIMER0 BLOCK DIAGRAM

#### 6.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 8.6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

#### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

| 1.CLRWDT            | ;Clear WDT               |

|---------------------|--------------------------|

| 2.CLRF TMR0         | ;Clear TMR0 & Prescaler  |

| 3.MOVLW '00xx1111'b | ;These 3 lines (5, 6, 7) |

| 4.OPTION            | ; are required only if   |

|                     | ; desired                |

| 5.CLRWDT            | ;PS<2:0> are 000 or 001  |

| 6.MOVLW '00xx1xxx'b | ;Set Postscaler to       |

| 7.OPTION            | ; desired WDT rate       |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT | •          | Clear WDT and       |

|--------|------------|---------------------|

|        |            | ;prescaler          |

| MOVLW  | 'xxxx0xxx' | ;Select TMR0, new   |

|        |            | ;prescale value and |

|        |            | ;clock source       |

| OPTION |            |                     |

## FIGURE 6-5: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

## 7.5 READ OPERATIONS

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

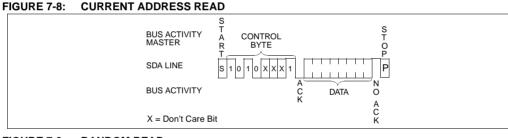

#### 7.5.1 CURRENT ADDRESS READ

It contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous read access was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with the R/W bit set to one, the device issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-8).

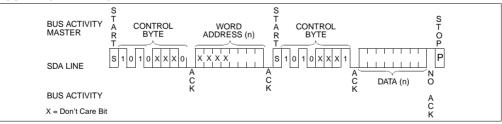

#### 7.5.2 RANDOM READ

Random read operations allow the master to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the device as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the  $R/\overline{W}$  bit set to a one. It will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-9). After this command, the internal address counter will point to the address location following the one that was just read.

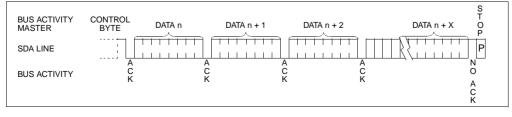

#### 7.5.3 SEQUENTIAL READ

Sequential reads are initiated in the same way as a random read except that after the device transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the device to transmit the next sequentially addressed 8-bit word (Figure 7-10).

To provide sequential reads, it contains an internal address pointer which is incremented by one at the completion of each read operation. This address pointer allows the entire memory contents to be serially read during one operation.

#### FIGURE 7-9: RANDOM READ

## FIGURE 7-10: SEQUENTIAL READ

## 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC12C5XX family of microcontrollers has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- · Oscillator selection

- Reset

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from SLEEP on pin change

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- · ID locations

- · In-circuit Serial Programming

The PIC12C5XX has a Watchdog Timer which can be shut off only through configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in reset until the crystal oscillator is stable. If using INTRC or EXTRC there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 8.1 Configuration Bits

The PIC12C5XX configuration word consists of 12 bits. Configuration bits can be programmed to select various device configurations. Two bits are for the selection of the oscillator type, one bit is the Watchdog Timer enable bit, and one bit is the MCLR enable bit.

## FIGURE 8-1: CONFIGURATION WORD FOR PIC12C5XX

| _         | —                                                                                                                                                                | _                                                                             | —  | — | — | — | MCLRE                       | CP | WDTE | FOSC1 | FOSC0 | Register:                | CONFIG |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----|---|---|---|-----------------------------|----|------|-------|-------|--------------------------|--------|

| bit11     | 10                                                                                                                                                               | 9                                                                             | 8  | 7 | 6 | 5 | 4                           | 3  | 2    | 1     | bit0  | Address <sup>(1)</sup> : | FFFh   |

| bit 11-5: | Unim                                                                                                                                                             | olement                                                                       | ed |   |   |   |                             |    |      |       |       |                          |        |

| bit 4:    | MCLRE: MCLR enable bit.<br>1 = MCLR pin enabled<br>0 = MCLR tied to VDD, (Internally)                                                                            |                                                                               |    |   |   |   |                             |    |      |       |       |                          |        |

| bit 3:    | 1 = Co                                                                                                                                                           | CP: Code protection bit.<br>1 = Code protection off<br>0 = Code protection on |    |   |   |   |                             |    |      |       |       |                          |        |

| bit 2:    | 1 = W                                                                                                                                                            | WDTE: Watchdog timer enable bit<br>1 = WDT enabled<br>0 = WDT disabled        |    |   |   |   |                             |    |      |       |       |                          |        |

| bit 1-0:  | FOSC1:FOSC0: Oscillator selection bits<br>11 = EXTRC - external RC oscillator<br>10 = INTRC - internal RC oscillator<br>01 = XT oscillator<br>00 = LP oscillator |                                                                               |    |   |   |   |                             |    |      |       |       |                          |        |

| Note 1:   |                                                                                                                                                                  |                                                                               |    | • | • |   | ations to de<br>Iressable d |    |      |       | he    |                          |        |

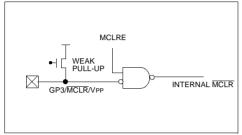

#### 8.3.1 MCLR ENABLE

This configuration bit when unprogrammed (left in the '1' state) enables the external  $\overline{MCLR}$  function. When programmed, the  $\overline{MCLR}$  function is tied to the internal VDD, and the pin is assigned to be a GPIO. See Figure 8-7. When pin GP3/ $\overline{MCLR}$ /VPP is configured as  $\overline{MCLR}$ , the internal pull-up is always on.

#### FIGURE 8-7: MCLR SELECT

#### 8.4 Power-On Reset (POR)

The PIC12C5XX family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip reset for most power-up situations.

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD or program the pin as GP3. An internal weak pull-up resistor is implemented using a transistor. Refer to Table 11-1 for the pull-up resistor ranges. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 8-8.

The Power-On Reset circuit and the Device Reset Timer (Section 8.5) circuit are closely related. On power-up, the reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will reset the reset latch and thus end the onchip reset signal.

A power-up example where  $\overline{\text{MCLR}}$  is held low is shown in Figure 8-9. VDD is allowed to rise and stabilize before bringing  $\overline{\text{MCLR}}$  high. The chip will actually come out of reset TDRT msec after  $\overline{\text{MCLR}}$  goes high.

In Figure 8-10, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3.). The VDD is stable before the start-up timer times out and there is no problem in getting a proper reset. However, Figure 8-11 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 8-10).

| Note: | When the device starts normal operation (exits the reset condition), device operating |

|-------|---------------------------------------------------------------------------------------|

|       | parameters (voltage, frequency, tempera-                                              |

|       | ture, etc.) must be meet to ensure opera-                                             |

|       | tion. If these conditions are not met, the                                            |

|       | device must be held in reset until the oper-                                          |

|       | ating conditions are met.                                                             |

For additional information refer to Application Notes "Power-Up Considerations" - AN522 and "Power-up Trouble Shooting" - AN607.

# PIC12C5XX

| BSF                | Bit Set f                                                                                                                    | BTFSS            | Bit Test f, Skip if Set                                                                                                         |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:            | [label] BSF f,b                                                                                                              | Syntax:          | [label] BTFSS f,b                                                                                                               |  |  |  |

| Operands:          | $0 \le f \le 31$ $0 \le b \le 7$                                                                                             | Operands:        | $0 \le f \le 31$<br>$0 \le b < 7$                                                                                               |  |  |  |

| Operation:         | $1 \rightarrow (f < b >)$                                                                                                    | Operation:       | skip if (f <b>) = 1</b>                                                                                                         |  |  |  |

| Status Affected:   | None                                                                                                                         | Status Affected: | None                                                                                                                            |  |  |  |

| Encoding:          | 0101 bbbf ffff                                                                                                               | Encoding:        | 0111 bbbf ffff                                                                                                                  |  |  |  |

| Description:       | Bit 'b' in register 'f' is set.                                                                                              | Description:     | If bit 'b' in register 'f' is '1' then the next                                                                                 |  |  |  |

| Words:             | 1                                                                                                                            |                  | instruction is skipped.                                                                                                         |  |  |  |

| Cycles:            | 1                                                                                                                            |                  | If bit 'b' is '1', then the next instruction<br>fetched during the current instruction<br>execution, is discarded and an NOP is |  |  |  |

| Example:           | BSF FLAG_REG, 7                                                                                                              |                  |                                                                                                                                 |  |  |  |

| Before Instruction |                                                                                                                              |                  | executed instead, making this a 2 cycle instruction.                                                                            |  |  |  |

| $FLAG_REG = 0x0A$  |                                                                                                                              | Words:           | 1                                                                                                                               |  |  |  |

| After Instruc      | tion<br>EG = 0x8A                                                                                                            | Cycles:          | 1(2)                                                                                                                            |  |  |  |

| FLAG_K             |                                                                                                                              | Example:         | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CODE                                                                                    |  |  |  |

| BTFSC              | Bit Test f, Skip if Clear                                                                                                    |                  | TRUE •                                                                                                                          |  |  |  |

| Syntax:            | [ label ] BTFSC f,b                                                                                                          |                  | •                                                                                                                               |  |  |  |

| Operands:          | $0 \le f \le 31$                                                                                                             | Before Instr     | uction                                                                                                                          |  |  |  |

|                    | $0 \le b \le 7$                                                                                                              | PC               | = address (HERE)                                                                                                                |  |  |  |

| Operation:         | skip if $(f < b >) = 0$                                                                                                      | After Instruc    |                                                                                                                                 |  |  |  |

| Status Affected:   | None                                                                                                                         | If FLAG<br>PC    | <1> = 0,<br>= address (FALSE);                                                                                                  |  |  |  |

| Encoding:          | 0110 bbbf ffff                                                                                                               | if FLAG<br>PC    | <1> = 1,                                                                                                                        |  |  |  |

| Description:       |                                                                                                                              |                  | = address (TRUE)                                                                                                                |  |  |  |

|                    | If bit 'b' is 0 then the next instruction<br>fetched during the current instruction<br>execution is discarded, and an NOP is |                  |                                                                                                                                 |  |  |  |

executed instead, making this a 2 cycle

BTFSC FLAG,1

address (HERE)

address (TRUE);

address(FALSE)

PROCESS\_CODE

GOTO

٠ •

0, =

1, =

instruction.

1

1(2)

HERE

TRUE

Before Instruction PC

After Instruction if FLAG<1>

if FLAG<1>

PC

PC

FALSE

=

=

=

Words:

Cycles:

Example:

## PIC12C5XX

NOTES:

#### 10.6 <u>SIMICE Entry-Level Hardware</u> <u>Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB<sup>™</sup>-SIM. Both SIM-ICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PICmicro® 8-bit microcontrollers. SIMICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entrylevel system development.

## 10.7 <u>PICDEM-1 Low-Cost PICmicro®</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

#### 10.8 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

## 10.9 PICDEM-3 Low-Cost PIC16CXXX Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 seqments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 11.2 DC CHARACTERISTICS:

#### PIC12C508/509 (Commercial, Industrial, Extended)

|        |                                         | Standard Operating Conditions (unless otherwise specified)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) $0^{\circ}C \le TA \le +70^{\circ}C$ (induction) |                  |      |            |       |                                                                     |  |  |  |

|--------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------------|-------|---------------------------------------------------------------------|--|--|--|

| DC CHA | ARACTERISTICS                           | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)                                                                          |                  |      |            |       |                                                                     |  |  |  |

|        |                                         | Operating voltage VDD range as described in DC spec Section 11.1 and                                                                                                               |                  |      |            |       |                                                                     |  |  |  |

|        |                                         | Section 11.2.                                                                                                                                                                      |                  |      |            |       |                                                                     |  |  |  |

| Param  | Characteristic                          | Sym                                                                                                                                                                                | Min              | Тур† | Max        | Units | Conditions                                                          |  |  |  |

| No.    |                                         |                                                                                                                                                                                    |                  |      |            |       |                                                                     |  |  |  |

|        | Input Low Voltage                       |                                                                                                                                                                                    |                  |      |            |       |                                                                     |  |  |  |

|        | I/O ports                               | VIL                                                                                                                                                                                |                  | -    |            |       |                                                                     |  |  |  |

| D030   | with TTL buffer                         |                                                                                                                                                                                    | Vss              | -    | 0.8V       |       | 4.5 < VDD ≤ 5.5V                                                    |  |  |  |

|        |                                         |                                                                                                                                                                                    |                  | -    | 0.15VDD    | V     | otherwise                                                           |  |  |  |

| D031   | with Schmitt Trigger buffer             |                                                                                                                                                                                    | Vss              | -    | 0.15VDD    | V     |                                                                     |  |  |  |

| D032   | MCLR, GP2/T0CKI (in EXTRC mode)         |                                                                                                                                                                                    | Vss              | -    | 0.15VDD    | V     |                                                                     |  |  |  |

| D033   | OSC1 (EXTRC) <sup>(1)</sup>             |                                                                                                                                                                                    | Vss              | -    | 0.15Vdd    |       |                                                                     |  |  |  |

| D033   | OSC1 (in XT and LP)                     |                                                                                                                                                                                    | Vss              | -    | 0.3Vdd     | V     | Note1                                                               |  |  |  |

|        | Input High Voltage                      |                                                                                                                                                                                    |                  |      |            |       |                                                                     |  |  |  |

|        | I/O ports                               | Vih                                                                                                                                                                                |                  | -    |            |       |                                                                     |  |  |  |

| D040   | with TTL buffer                         | Vss                                                                                                                                                                                | 2.0V             | -    | Vdd        | V     | $4.5 \le VDD \le 5.5V$                                              |  |  |  |

| D040A  |                                         |                                                                                                                                                                                    | 0.25VDD+<br>0.8V | -    | Vdd        | V     | otherwise                                                           |  |  |  |

| D041   | with Schmitt Trigger buffer             |                                                                                                                                                                                    | 0.85Vdd          | -    | Vdd        | V     | For entire VDD range                                                |  |  |  |

| D042   | MCLR/GP2/T0CKI                          |                                                                                                                                                                                    | 0.85Vdd          | -    | Vdd        | V     | _                                                                   |  |  |  |

| D042A  | OSC1 (XT and LP)                        |                                                                                                                                                                                    | 0.7Vdd           | -    | Vdd        | V     | Note1                                                               |  |  |  |

| D043   | OSC1 (in EXTRC mode)                    |                                                                                                                                                                                    | 0.85Vdd          | -    | Vdd        | V     |                                                                     |  |  |  |

| D070   | GPIO weak pull-up current               | IPUR                                                                                                                                                                               | 50               | 250  | 400        | μΑ    | VDD = 5V, VPIN = VSS                                                |  |  |  |

|        | Input Leakage Current <sup>(2, 3)</sup> |                                                                                                                                                                                    |                  |      |            |       | For VDD ≤5.5V                                                       |  |  |  |

| D060   | I/O ports                               | ١L                                                                                                                                                                                 | -1               | 0.5  | <u>+</u> 1 | μA    | Vss ≤ VPIN ≤ VDD,<br>Pin at hi-impedance                            |  |  |  |

| D061   | MCLR, GP2/T0CKI                         |                                                                                                                                                                                    | 20               | 130  | 250        | μA    | VPIN = VSS + 0.25V <sup>(2)</sup>                                   |  |  |  |

|        |                                         |                                                                                                                                                                                    |                  | 0.5  | +5         | μA    | VPIN = VDD                                                          |  |  |  |

| D063   | OSC1                                    |                                                                                                                                                                                    | -3               | 0.5  | +3         | μA    | Vss $\leq$ VPIN $\leq$ VDD,<br>XT and LP options                    |  |  |  |

|        | Output Low Voltage                      |                                                                                                                                                                                    |                  |      |            |       |                                                                     |  |  |  |

| D080   | I/O ports/CLKOUT                        | Vol                                                                                                                                                                                | -                | -    | 0.6        | V     | IOL = 8.7 mA, VDD = 4.5V                                            |  |  |  |

|        | Output High Voltage                     |                                                                                                                                                                                    |                  |      |            |       | •                                                                   |  |  |  |

| D090   | I/O ports/CLKOUT <sup>(3)</sup>         | Voh                                                                                                                                                                                | Vdd - 0.7        | -    | -          | V     | IOH = -5.4 mA, VDD = 4.5V                                           |  |  |  |

|        | Capacitive Loading Specs on             |                                                                                                                                                                                    |                  |      |            |       |                                                                     |  |  |  |

|        | Output Pins                             |                                                                                                                                                                                    |                  |      |            |       |                                                                     |  |  |  |

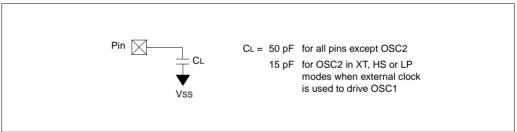

| D100   | OSC2 pin                                | Cosc2                                                                                                                                                                              | -                | -    | 15         | pF    | In XT and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101   | All I/O pins                            | Cio                                                                                                                                                                                | -                | -    | 50         | pF    |                                                                     |  |  |  |

| -      | Data in "Typ" column is at 5V 25°C ur   |                                                                                                                                                                                    |                  |      |            |       |                                                                     |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C5XX be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

## TABLE 11-4: TIMING REQUIREMENTS - PIC12C508/C509

| AC Chara             | cteristics |                                                                          |     |                    |      |       |  |

|----------------------|------------|--------------------------------------------------------------------------|-----|--------------------|------|-------|--|

| Parameter<br>No. Sym |            | Characteristic                                                           | Min | Typ <sup>(1)</sup> | Max  | Units |  |

| 17                   | TosH2ioV   | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(3)</sup>            | _   | -                  | 100* | ns    |  |

| 18                   | TosH2iol   | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) | TBD | —                  | _    | ns    |  |

| 19                   | TioV2osH   | Port input valid to OSC1 <sup>↑</sup><br>(I/O in setup time)             | TBD | —                  | _    | ns    |  |

| 20                   | TioR       | Port output rise time <sup>(2, 3)</sup>                                  | _   | 10                 | 25** | ns    |  |

| 21                   | TioF       | Port output fall time <sup>(2, 3)</sup>                                  | _   | 10                 | 25** | ns    |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: Measurements are taken in EXTRC mode.

- 3: See Figure 11-1 for loading conditions.

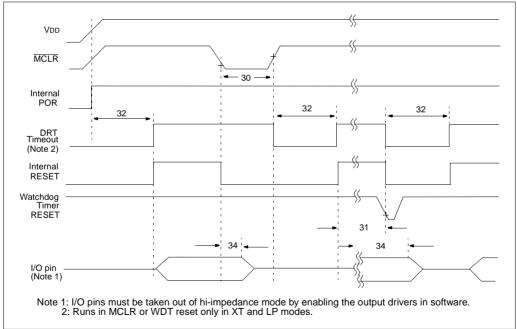

## FIGURE 11-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC12C508/C509

| Oscillator  | Frequency | VDD = 2.5V | VDD = 5.5V |  |

|-------------|-----------|------------|------------|--|

| External RC | 4 MHz     | 250 µA*    | 780 µA*    |  |

| Internal RC | 4 MHz     | 420 µA     | 1.1 mA     |  |

| XT          | 4 MHz     | 251 µA     | 780 µA     |  |

| LP          | 32 KHz    | 15 µA      | 37 µA      |  |

## TABLE 12-1: DYNAMIC IDD (TYPICAL) - WDT ENABLED, 25°C

\*Does not include current through external R&C.

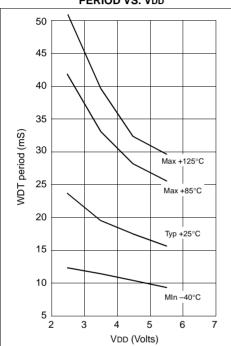

#### FIGURE 12-3: WDT TIMER TIME-OUT PERIOD VS. VDD

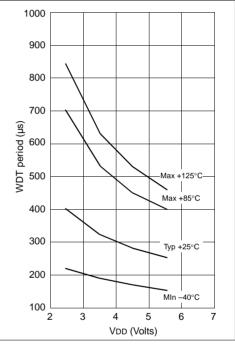

## FIGURE 12-4: SHORT DRT PERIOD VS. VDD

#### 13.5 <u>Timing Parameter Symbology and Load Conditions - PIC12C508A, PIC12C509A,</u> PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

The timing parameter symbols have been created following one of the following formats:

| 1. Tp | oS2ppS |

|-------|--------|

|-------|--------|

2. TppS

| 2. TppS                               |                                               |     |                |  |  |  |

|---------------------------------------|-----------------------------------------------|-----|----------------|--|--|--|

| т                                     |                                               |     |                |  |  |  |

| F                                     | Frequency                                     | Т   | Time           |  |  |  |

| Lowerc                                | Lowercase subscripts (pp) and their meanings: |     |                |  |  |  |

| рр                                    |                                               |     |                |  |  |  |

| 2                                     | to                                            | mc  | MCLR           |  |  |  |

| ck                                    | CLKOUT                                        | osc | oscillator     |  |  |  |

| су                                    | cycle time                                    | os  | OSC1           |  |  |  |

| drt                                   | device reset timer                            | tO  | TOCKI          |  |  |  |

| io                                    | I/O port                                      | wdt | watchdog timer |  |  |  |

| Uppercase letters and their meanings: |                                               |     |                |  |  |  |

| S                                     |                                               |     |                |  |  |  |

| F                                     | Fall                                          | Р   | Period         |  |  |  |

| н                                     | High                                          | R   | Rise           |  |  |  |

| I                                     | Invalid (Hi-impedance)                        | V   | Valid          |  |  |  |

| L                                     | Low                                           | Z   | Hi-impedance   |  |  |  |

## FIGURE 13-1: LOAD CONDITIONS - PIC12C508A/C509A, PIC12CE518/519, PIC12LC508A/509A, PIC12LCE518/519, PIC12LCR509A

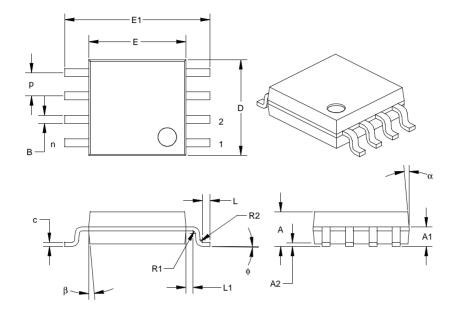

Package Type: K04-056 8-Lead Plastic Small Outline (SM) - Medium, 208 mil

| Units                   |    | INCHES* |       |       | MILLIMETERS |      |      |

|-------------------------|----|---------|-------|-------|-------------|------|------|

| Dimension Limits        |    | MIN     | NOM   | MAX   | MIN         | NOM  | MAX  |

| Pitch                   | р  |         | 0.050 |       |             | 1.27 |      |

| Number of Pins          | n  |         | 8     |       |             | 8    |      |

| Overall Pack. Height    | A  | 0.070   | 0.074 | 0.079 | 1.78        | 1.89 | 2.00 |

| Shoulder Height         | A1 | 0.037   | 0.042 | 0.048 | 0.94        | 1.08 | 1.21 |

| Standoff                | A2 | 0.002   | 0.005 | 0.009 | 0.05        | 0.14 | 0.22 |

| Molded Package Length   | D‡ | 0.200   | 0.205 | 0.210 | 5.08        | 5.21 | 5.33 |

| Molded Package Width    | E‡ | 0.203   | 0.208 | 0.213 | 5.16        | 5.28 | 5.41 |

| Outside Dimension       | E1 | 0.300   | 0.313 | 0.325 | 7.62        | 7.94 | 8.26 |

| Shoulder Radius         | R1 | 0.005   | 0.005 | 0.010 | 0.13        | 0.13 | 0.25 |

| Gull Wing Radius        | R2 | 0.005   | 0.005 | 0.010 | 0.13        | 0.13 | 0.25 |

| Foot Length             | L  | 0.011   | 0.016 | 0.021 | 0.28        | 0.41 | 0.53 |

| Foot Angle              | φ  | 0       | 4     | 8     | 0           | 4    | 8    |

| Radius Centerline       | L1 | 0.010   | 0.015 | 0.020 | 0.25        | 0.38 | 0.51 |

| Lead Thickness          | с  | 0.008   | 0.009 | 0.010 | 0.19        | 0.22 | 0.25 |

| Lower Lead Width        | B† | 0.014   | 0.017 | 0.020 | 0.36        | 0.43 | 0.51 |

| Mold Draft Angle Top    | α  | 0       | 12    | 15    | 0           | 12   | 15   |

| Mold Draft Angle Bottom | β  | 0       | 12    | 15    | 0           | 12   | 15   |

\* Controlling Parameter.

<sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."