Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.5KB (1K x 12)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 41 × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                               |

| Supplier Device Package    | 8-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c509at-04-sn |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE OF CONTENTS

| 1.0   | General Description                                                                   | 4   |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | PIC12C5XX Device Varieties                                                            |     |

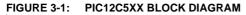

| 3.0   | Architectural Overview                                                                |     |

| 4.0   | Memory Organization                                                                   | 13  |

| 5.0   | I/O Port                                                                              |     |

| 6.0   | Timer0 Module and TMR0 Register                                                       | 25  |

| 7.0   | EEPROM Peripheral Operation                                                           | 29  |

| 8.0   | Special Features of the CPU                                                           | 35  |

| 9.0   | Instruction Set Summary                                                               | 47  |

| 10.0  | Development Support                                                                   |     |

| 11.0  | Electrical Characteristics - PIC12C508/PIC12C509                                      | 65  |

| 12.0  | DC and AC Characteristics - PIC12C508/PIC12C509                                       | 75  |

| 13.0  | Electrical Characteristics PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CR509A/ |     |

|       | PIC12CE518/PIC12CE519/                                                                |     |

|       | PIC12LCE518/PIC12LCE519/PIC12LCR509A                                                  | 79  |

| 14.0  | DC and AC Characteristics                                                             |     |

|       | PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CE518/PIC12CE519/PIC12CR509A/      |     |

|       | PIC12LCE518/PIC12LCE519/ PIC12LCR509A                                                 | 93  |

| 15.0  | Packaging Information                                                                 | 99  |

| Index | ۲                                                                                     | 105 |

|       | 2C5XX Product Identification System                                                   |     |

| Sales | and Support:                                                                          | 109 |

## To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

NOTES:

## 2.0 PIC12C5XX DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12C5XX Product Identification System at the back of this data sheet to specify the correct part number.

## 2.1 UV Erasable Devices

The UV erasable version, offered in ceramic side brazed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

Microchip's PICSTART<sup>®</sup> PLUS and PRO MATE<sup>®</sup> programmers all support programming of the PIC12C5XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

## 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

## 2.5 Read Only Memory (ROM) Device

Microchip offers masked ROM to give the customer a low cost option for high volume, mature products.

## 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The special registers can be classified into two sets. The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

## TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

|                    |                                                                                     |                             |              |             |           |                        |              |         |       | Value on<br>Power-On | Value on<br>All Other    |

|--------------------|-------------------------------------------------------------------------------------|-----------------------------|--------------|-------------|-----------|------------------------|--------------|---------|-------|----------------------|--------------------------|

| Address            | Name                                                                                | Bit 7                       | Bit 6        | Bit 5       | Bit 4     | Bit 3                  | Bit 2        | Bit 1   | Bit 0 | Reset                | Resets <sup>(2)</sup>    |

| N/A                | TRIS                                                                                | —                           | I            |             |           |                        |              |         |       | 11 1111              | 11 1111                  |

| N/A                | OPTION                                                                              | Contains co<br>prescaler, v |              |             |           | Timer0/WD1<br>pull-ups | Г            |         |       | 1111 1111            | 1111 1111                |

| 00h                | INDF                                                                                | Uses conte                  | ents of FSR  | R to addres | s data me | mory (not a            | physical reg | jister) |       | xxxx xxxx            | uuuu uuuu                |

| 01h                | TMR0                                                                                | 8-bit real-ti               | me clock/c   | ounter      |           |                        |              |         |       | xxxx xxxx            | uuuu uuuu                |

| 02h <sup>(1)</sup> | PCL                                                                                 | Low order                   | B bits of PC | c           |           |                        |              |         |       | 1111 1111            | 1111 1111                |

| 03h                | STATUS                                                                              | GPWUF                       | -            | PA0         | TO        | PD                     | Z            | DC      | С     | 0001 1xxx            | q00q quuu <sup>(3)</sup> |

| 04h                | FSR<br>(PIC12C508/<br>PIC12C508A/<br>PIC12C518)                                     | Indirect dat                | a memory     | address p   | pointer   | L                      | L            | 1       | 1     | 111x xxxx            | 111u uuuu                |

| 04h                | FSR<br>(PIC12C509/<br>PIC12C509A/<br>PIC12CR509A/<br>PIC12CE519)                    | Indirect dat                | a memory     | address p   | oointer   |                        |              |         |       | 110x xxxx            | 11uu uuuu                |

| 05h                | OSCCAL<br>(PIC12C508/<br>PIC12C509)                                                 | CAL3                        | CAL2         | CAL1        | CAL0      | _                      | _            | _       | _     | 0111                 | uuuu                     |

| 05h                | OSCCAL<br>(PIC12C508A/<br>PIC12C509A/<br>PIC12CE518/<br>PIC12CE519/<br>PIC12CR509A) | CAL5                        | CAL4         | CAL3        | CAL2      | CAL1                   | CAL0         |         | _     | 1000 00              | uuuu uu                  |

| 06h                | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CC509A)     | _                           | _            | GP5         | GP4       | GP3                    | GP2          | GP1     | GP0   | xx xxxx              | uu uuuu                  |

| 06h                | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                                 | SCL                         | SDA          | GP5         | GP4       | GP3                    | GP2          | GP1     | GP0   | 11xx xxxx            | 11uu uuuu                |

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as '0' (if applicable)

x = unknown, u = unchanged, q = see the tables in Section 8.7 for possible values.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 for an explanation of how to access these bits.

2: Other (non power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

3: If reset was due to wake-up on pin change then bit 7 = 1. All other resets will cause bit 7 = 0.

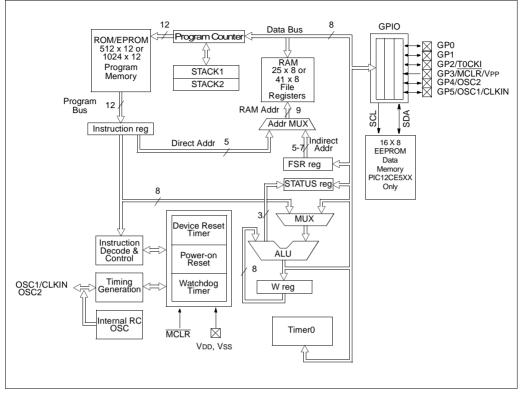

#### 4.8 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 07 contains the value 10h

- · Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-2.

#### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw | 0x10  | ;initialize pointer |

|----------|-------|-------|---------------------|

|          | movwf | FSR   | ; to RAM            |

| NEXT     | clrf  | INDF  | clear INDF register |

|          | incf  | FSR,F | ;inc pointer        |

|          | btfsc | FSR,4 | ;all done?          |

|          | goto  | NEXT  | ;NO, clear next     |

| CONTINUE | 9     |       | -,                  |

|          | :     |       | ;YES, continue      |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC12C508/PIC12C508A/PIC12CE518:** Does not use banking. FSR<7:5> are unimplemented and read as '1's.

#### PIC12C509/PIC12C509A/PIC12CR509A/

**PIC12CE519:** Uses FSR<5>. Selects between bank 0 and bank 1. FSR<7:6> is unimplemented, read as '1'.

## FIGURE 4-9: DIRECT/INDIRECT ADDRESSING

| TABLE 5-1: S | UMMARY OF PORT | <b>REGISTERS</b> |

|--------------|----------------|------------------|

|--------------|----------------|------------------|

| Address | Name                                                                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|---------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------|

| N/A     | TRIS                                                                            | —     | -     |       |       |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | OPTION                                                                          | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                    |

| 03H     | STATUS                                                                          | GPWUF | -     | PAO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>     |

| 06h     | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CR509A) |       | _     | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                      |

| 06h     | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                             | SCL   | SDA   | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 11xx xxxx                     | 11uu uuuu                    |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, g = see tables in Section 8.7 for possible values.

Note 1: If reset was due to wake-up on change, then bit 7 = 1. All other resets will cause bit 7 = 0.

#### 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of GPIO will cause all eight bits of GPIO to be read into the CPU, bit5 to be set and the GPIO value to be written to the output latches. If another bit of GPIO is used as a bidirectional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}$  ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wiredand"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ; | Initia | L GPIO  | Sett  | ings |         |     |        |

|---|--------|---------|-------|------|---------|-----|--------|

| ; | GPIO<5 | 5:3> In | puts  | 3    |         |     |        |

| ; | GPIO<2 | 2:0> Ou | itput | s    |         |     |        |

| ; |        |         |       |      |         |     |        |

| ; |        |         |       | GPIC | ) latch | GPI | ) pins |

| ; |        |         |       |      |         |     |        |

|   | BCF    | GPIO,   | 5     | ;01  | -ppp    | 11  | pppp   |

|   | BCF    | GPIO,   | 4     | ;10  | -ppp    | 11  | pppp   |

|   | MOVLW  | 007h    |       | ;    |         |     |        |

|   | TRIS   | GPIO    |       | ;10  | -ppp    | 11  | pppp   |

|   |        |         |       |      |         |     |        |

;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;GP5 to be latched as the pin value (High).

## 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

NOTES:

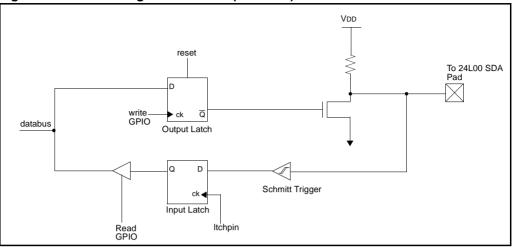

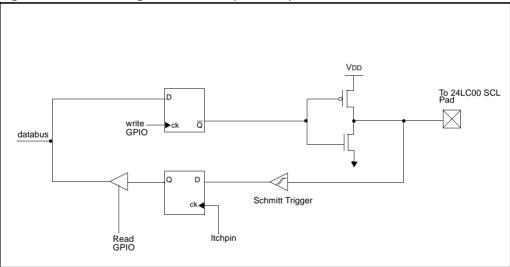

Figure 7-2: Block diagram of GPIO7 (SCL line)

#### 7.0.2 SERIAL CLOCK

This SCL input is used to synchronize the data transfer from and to the device.

### 7.1 BUS CHARACTERISTICS

The following **bus protocol** is to be used with the EEPROM data memory.

• Data transfer may be initiated only when the bus is not busy.

During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 7-3).

7.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

7.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### 7.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

### 7.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the master device and is theoretically unlimited.

#### 7.1.5 ACKNOWLEDGE

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.

Note: Acknowledge bits are not generated if an internal programming cycle is in progress.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition (Figure 7-4).

## 7.5 READ OPERATIONS

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

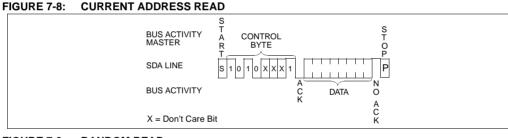

#### 7.5.1 CURRENT ADDRESS READ

It contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous read access was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with the R/W bit set to one, the device issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-8).

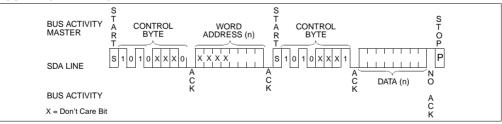

#### 7.5.2 RANDOM READ

Random read operations allow the master to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the device as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the  $R/\overline{W}$  bit set to a one. It will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-9). After this command, the internal address counter will point to the address location following the one that was just read.

#### 7.5.3 SEQUENTIAL READ

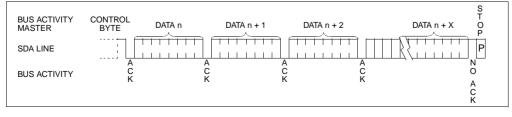

Sequential reads are initiated in the same way as a random read except that after the device transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the device to transmit the next sequentially addressed 8-bit word (Figure 7-10).

To provide sequential reads, it contains an internal address pointer which is incremented by one at the completion of each read operation. This address pointer allows the entire memory contents to be serially read during one operation.

#### FIGURE 7-9: RANDOM READ

## FIGURE 7-10: SEQUENTIAL READ

## 9.0 INSTRUCTION SET SUMMARY

Each PIC12C5XX instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC12C5XX instruction set summary in Table 9-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

### TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is<br>the recommended form of use for compatibility<br>with all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| WDT           | Watchdog Timer Counter                                                                                                                                                         |

| TO            | Time-Out bit                                                                                                                                                                   |

| PD            | Power-Down bit                                                                                                                                                                 |

| dest          | Destination, either the W register or the specified register file location                                                                                                     |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1 µs. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2 µs.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

## FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byt  | e-oriented file req                                           | giste | r o  | perat  | tions           |   |

|------|---------------------------------------------------------------|-------|------|--------|-----------------|---|

| 1    | 1                                                             | 6     | 5    | 4      |                 | 0 |

|      | OPCODE                                                        |       | d    |        | f (FILE #)      |   |

|      | d = 0 for destina<br>d = 1 for destina<br>f = 5-bit file regi | ation | f    | dress  | 6               |   |

| Bit- | oriented file regis                                           | ster  | ope  | eratio | ns              |   |

| 1    | 1                                                             | 87    |      | 5      | 4               | 0 |

|      | OPCODE                                                        | b     | (B   | T #)   | f (FILE #)      |   |

| Lite | b = 3-bit bit add<br>f = 5-bit file reg<br>ral and control o  | ister | ac   |        |                 |   |

| 1    | 1                                                             |       | 8    | 7      |                 | 0 |

|      | OPCODE                                                        |       |      |        | k (literal)     |   |

|      | k = 8-bit immed                                               | diate | va   | lue    |                 |   |

| Lite | ral and control of                                            | pera  | atio | ns -   | GOTO instructio | n |

| 1    | 1                                                             |       | 9    | 8      |                 | 0 |

|      | OPCODE                                                        |       |      |        | k (literal)     |   |

|      |                                                               |       |      |        |                 |   |

k = 9-bit immediate value

| CALL                  | Subroutine Call                                                                                                                                                                                                                                |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:               | [ <i>label</i> ] CALL k                                                                                                                                                                                                                        |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                                                                              |

| Operation:            | $\begin{array}{l} (PC) + 1 \rightarrow \text{Top of Stack;} \\ k \rightarrow PC < 7:0>; \\ (STATUS < 6:5>) \rightarrow PC < 10:9>; \\ 0 \rightarrow PC < 8> \end{array}$                                                                       |

| Status Affected:      | None                                                                                                                                                                                                                                           |

| Encoding:             | 1001 kkkk kkkk                                                                                                                                                                                                                                 |

| Description:          | Subroutine call. First, return address (PC+1) is pushed onto the stack. The eight bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STA-TUS<6:5>, PC<8> is cleared. CALL is a two cycle instruction. |

| Words:                | 1                                                                                                                                                                                                                                              |

| Cycles:               | 2                                                                                                                                                                                                                                              |

| Example:              | HERE CALL THERE                                                                                                                                                                                                                                |

| Before Instru<br>PC = |                                                                                                                                                                                                                                                |

|                       | tion<br>address (THERE)<br>address (HERE + 1)                                                                                                                                                                                                  |

## CLRF

| Syntax:                        | [label]                                                              | CLRF f                      |              |         |

|--------------------------------|----------------------------------------------------------------------|-----------------------------|--------------|---------|

| Operands:                      | $0 \le f \le 31$                                                     | I                           |              |         |

| Operation:                     | $\begin{array}{c} 00h \rightarrow (f \\ 1 \rightarrow Z \end{array}$ | );                          |              |         |

| Status Affected:               | Z                                                                    |                             |              |         |

| Encoding:                      | 0000                                                                 | 011f                        | ffff         |         |

| Description:                   | The conte<br>and the Z                                               | nts of regis<br>bit is set. | ster 'f' are | cleared |

| Words:                         | 1                                                                    |                             |              |         |

| Cycles:                        | 1                                                                    |                             |              |         |

| Example:                       | CLRF                                                                 | FLAG_REC                    | 3            |         |

| Before Instru<br>FLAG_RE       |                                                                      | 0x5A                        |              |         |

| After Instruct<br>FLAG_RE<br>Z |                                                                      | 0x00<br>1                   |              |         |

Clear f

| CLRW                                                                                                     | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Operation:                                                                                               | $\begin{array}{l} \text{00h} \rightarrow (\text{W}); \\ 1 \rightarrow \text{Z} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                                                | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Description:                                                                                             | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Example:                                                                                                 | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Before Instru<br>W =                                                                                     | uction<br>0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| After Instruc<br>W =<br>Z =                                                                              | tion<br>0x00<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLRWDT<br>Syntax:                                                                                        | Clear Watchdog Timer<br>[label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Syntax:                                                                                                  | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Syntax:<br>Operands:                                                                                     | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Syntax:<br>Operands:<br>Operation:                                                                       | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $ \begin{array}{l l} \textit{[label]} & \textit{CLRWDT} \\ \hline None \\ 00h \rightarrow WDT; \\ 0 \rightarrow WDT \ prescaler \ (if \ assigned); \\ 1 \rightarrow \overline{TO}; \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \ \overline{PD} \\ \hline \hline 0000 & 0000 & 0100 \\ \hline \hline The \ \textit{CLRWDT} \ instruction \ resets \ the \\ WDT. \ It \ also \ resets \ the \ prescaler, \ if \ the \\ prescaler \ is \ assigned \ to \ the \ WDT \ and \\ not \ Timer0. \ Status \ bits \ \overline{TO} \ and \ \overline{PD} \ are \\ \end{array} $                                                                                                                                                                                                                                                     |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $ \begin{array}{l l} \textit{[label]} & \textit{CLRWDT} \\ \hline None \\ 00h \rightarrow \textit{WDT}; \\ 0 \rightarrow \textit{WDT} \textit{ prescaler} (if assigned); \\ 1 \rightarrow \overrightarrow{\textit{TO}}; \\ 1 \rightarrow \overrightarrow{\textit{PD}} \\ \hline \overrightarrow{\textit{TO}}, \overrightarrow{\textit{PD}} \\ \hline \hline \overrightarrow{\textit{TO}}, \overrightarrow{\textit{PD}} \\ \hline \hline \hline \textit{O000} & 0000 & 0100 \\ \hline \hline \hline \textit{The } \textit{CLRWDT} \textit{ instruction resets the} \\ \textit{WDT. It also resets the prescaler, if the} \\ \textit{prescaler is assigned to the WDT and} \\ \textit{not Timer0. Status bits } \overrightarrow{\textit{TO}} \textit{ and } \overrightarrow{\textit{PD}} \textit{ are} \\ \textit{set.} \end{array} $ |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT prescaler (if assigned);$<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$<br>0000  0000  0100<br>The CLRWDT instruction resets the<br>WDT. It also resets the prescaler, if the<br>prescaler is assigned to the WDT and<br>not Timer0. Status bits $\overline{TO}$ and $\overline{PD}$ are<br>set.<br>1<br>1<br>CLRWDT<br>uction                                                                                                                                                                                                                                                                                                                                                               |

## **10.0 DEVELOPMENT SUPPORT**

## 10.1 <u>Development Tools</u>

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- MPLAB<sup>™</sup>-ICE Real-Time In-Circuit Emulator

- ICEPIC<sup>™</sup> Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- SIMICE

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

- KEELOQ<sup>®</sup> Evaluation Kits and Programmer

## 10.2 MPLAB-ICE: High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro<sup>®</sup> microcontrollers (MCUs). MPLAB-ICE is supplied with the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support all new Microchip microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x or Windows 95 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE is available in two versions. MPLAB-ICE 1000 is a basic, low-cost emulator system with simple trace capabilities. It shares processor modules with the MPLAB-ICE 2000. This is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems will operate across the entire operating speed range of the PICmicro<sup>®</sup> MCU.

## 10.3 ICEPIC: Low-Cost PICmicro<sup>®</sup> In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 386 through Pentium<sup>™</sup> based machines under Windows 3.x, Windows 95, or Windows NT environment. ICEPIC features real time, non-intrusive emulation.

## 10.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

## 10.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

## 13.1 DC CHARACTERISTICS:

## PIC12C508A/509A (Commercial, Industrial, Extended) PIC12CE518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

|             | DC Characteristics<br>Power Supply Pins                                    |                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |                                                                              |  |

|-------------|----------------------------------------------------------------------------|----------------|------------------------------------------------------|--------------------|-----|-------|------------------------------------------------------------------------------|--|

| Parm<br>No. | Characteristic                                                             | Sym            | Min                                                  | Typ <sup>(1)</sup> | Max | Units | Conditions                                                                   |  |

| D001        | Supply Voltage                                                             | Vdd            | 3.0                                                  |                    | 5.5 | V     | Fosc = DC to 4 MHz (Commercial/<br>Industrial, Extended)                     |  |

| D002        | RAM Data Retention<br>Voltage <sup>(2)</sup>                               | Vdr            |                                                      | 1.5*               |     | V     | Device in SLEEP mode                                                         |  |

| D003        | VDD Start Voltage to ensure<br>Power-on Reset                              | VPOR           |                                                      | Vss                |     | V     | See section on Power-on Reset for details                                    |  |

| D004        | VDD Rise Rate to ensure<br>Power-on Reset                                  | SVDD           | 0.05*                                                |                    |     | V/ms  | See section on Power-on Reset for details                                    |  |

| D010        | Supply Current <sup>(3)</sup>                                              | IDD            | —                                                    | 0.8                | 1.4 | mA    | XT and EXTRC options (Note 4)<br>Fosc = 4 MHz, VDD = 5.5V                    |  |

| D010C       |                                                                            |                | _                                                    | 0.8                | 1.4 | mA    | INTRC Option<br>Fosc = 4 MHz, VDD = 5.5V                                     |  |

| D010A       |                                                                            |                | -                                                    | 19                 | 27  | μA    | LP OPTION, Commercial Temperature<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled |  |

|             |                                                                            |                | _                                                    | 19                 | 35  | μA    | LP OPTION, Industrial Temperature<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled |  |

|             |                                                                            |                | _                                                    | 30                 | 55  | μA    | LP OPTION, Extended Temperature<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled   |  |

| D020        | Power-Down Current <sup>(5)</sup>                                          | IPD            | —                                                    | 0.25               | 4   | μA    | VDD = 3.0V, Commercial WDT disabled                                          |  |

| D021        |                                                                            |                | —                                                    | 0.25               | 5   | μA    | VDD = 3.0V, Industrial WDT disabled                                          |  |

| D021B       |                                                                            |                | -                                                    | 2                  | 12  | μA    | VDD = 3.0V, Extended WDT disabled                                            |  |

| D022        | Power-Down Current                                                         | $\Delta I$ WDT | —                                                    | 2.2                | 5   | μA    | VDD = 3.0V, Commercial                                                       |  |

|             |                                                                            |                | -                                                    | 2.2                | 6   | μA    | VDD = 3.0V, Industrial                                                       |  |

|             |                                                                            |                | -                                                    | 4                  | 11  | μA    | VDD = 3.0V, Extended                                                         |  |

|             | Supply Current <sup>(3)</sup><br>During read/write to<br>EEPROM peripheral | ΔIEE           | -                                                    | 0.1                | 0.2 | mA    | FOSC = 4 MHz, Vdd = 5.5V,<br>SCL = 400kHz                                    |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to

- Vss, T0CKI = VDD,  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: Does not include current through Rext. The current through the resistor can be estimated by the formula: IR = VDD/2Rext (mA) with Rext in kOhm.

- 5: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

## 13.3 DC CHARACTERISTICS:

## PIC12C508A/509A (Commercial, Industrial, Extended) PIC12C518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

|       |                                    |                                                                                                           | r <b>d Operati</b><br>ng tempera |        | 0°C ≤      | TA ≤ + | s otherwise specified)<br>70°C (commercial)                        |  |  |

|-------|------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|--------|------------|--------|--------------------------------------------------------------------|--|--|

| DC CH | ARACTERISTICS                      | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |                                  |        |            |        |                                                                    |  |  |

|       |                                    | Operatii<br>Section                                                                                       |                                  | Vdd ra |            |        | d in DC spec Section 13.1 and                                      |  |  |

| Param | Characteristic                     | Sym                                                                                                       | Min                              | Typ†   | Max        | Units  | Conditions                                                         |  |  |

| No.   |                                    |                                                                                                           |                                  |        |            |        |                                                                    |  |  |

|       | Input Low Voltage                  |                                                                                                           |                                  |        |            |        |                                                                    |  |  |

|       | I/O ports                          | VIL                                                                                                       |                                  |        |            |        |                                                                    |  |  |

| D030  | with TTL buffer                    |                                                                                                           | Vss                              | -      | 0.8V       | V      | For $4.5V \le VDD \le 5.5V$                                        |  |  |

|       |                                    |                                                                                                           | Vss                              | -      | 0.15Vdd    | V      | otherwise                                                          |  |  |

| D031  | with Schmitt Trigger buffer        |                                                                                                           | Vss                              | -      | 0.2VDD     | V      |                                                                    |  |  |

| D032  | MCLR, GP2/T0CKI (in EXTRC mode)    |                                                                                                           | Vss                              | -      | 0.2VDD     | V      |                                                                    |  |  |

| D033  | OSC1 (in EXTRC mode)               |                                                                                                           | Vss                              | -      | 0.2VDD     |        | Note 1                                                             |  |  |