Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.5KB (1K x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 41 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

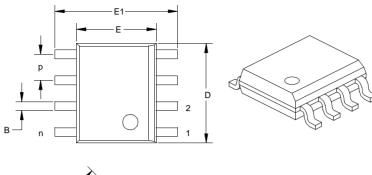

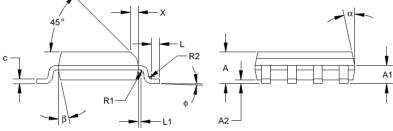

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c509t-04-sm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |                                               | PIC12C508(A)           | PIC12C509(A)           | PIC12CR509A        | PIC12CE518             | PIC12CE519             | PIC12C671              | PIC12C672              | PIC12CE673       | PIC12CE674       |

|-------------|-----------------------------------------------|------------------------|------------------------|--------------------|------------------------|------------------------|------------------------|------------------------|------------------|------------------|

| Clock       | Maximum<br>Frequency<br>of Operation<br>(MHz) | 4                      | 4                      | 4                  | 4                      | 4                      | 10                     | 10                     | 10               | 10               |

| M           | EPROM<br>Program<br>Memory                    | 512 x 12               | 1024 x 12              | 1024 x 12<br>(ROM) | 512 x 12               | 1024 x 12              | 1024 x 14              | 2048 x 14              | 1024 x 14        | 2048 x 14        |

| Memory      | RAM Data<br>Memory<br>(bytes)                 | 25                     | 41                     | 41                 | 25                     | 41                     | 128                    | 128                    | 128              | 128              |

|             | EEPROM<br>Data Memory<br>(bytes)              | —                      | -                      | —                  | 16                     | 16                     | —                      | —                      | 16               | 16               |

| Peripherals | Timer<br>Module(s)                            | TMR0                   | TMR0                   | TMR0               | TMR0                   | TMR0                   | TMR0                   | TMR0                   | TMR0             | TMR0             |

|             | A/D Con-<br>verter (8-bit)<br>Channels        | —                      | _                      | —                  | —                      | —                      | 4                      | 4                      | 4                | 4                |

|             | Wake-up<br>from SLEEP<br>on pin<br>change     | Yes                    | Yes                    | Yes                | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | Interrupt<br>Sources                          | —                      | -                      | _                  |                        |                        | 4                      | 4                      | 4                | 4                |

| Features    | I/O Pins                                      | 5                      | 5                      | 5                  | 5                      | 5                      | 5                      | 5                      | 5                | 5                |

|             | Input Pins                                    | 1                      | 1                      | 1                  | 1                      | 1                      | 1                      | 1                      | 1                | 1                |

|             | Internal<br>Pull-ups                          | Yes                    | Yes                    | Yes                | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | In-Circuit<br>Serial<br>Programming           | Yes                    | Yes                    | —                  | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | Number of<br>Instructions                     | 33                     | 33                     | 33                 | 33                     | 33                     | 35                     | 35                     | 35               | 35               |

|             | Packages                                      | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW | 8-pin DIP,<br>JW |

## TABLE 1-1: PIC12CXXX & PIC12CEXXX FAMILY OF DEVICES

All PIC12CXXX & PIC12CEXXX devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability.

All PIC12CXXX & PIC12CEXXX devices use serial programming with data pin GP0 and clock pin GP1.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12C5XX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C5XX uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12-bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (1µs @ 4MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), ROM memory, and non-volatile (EEPROM) for each device.

|             | Memory           |                |             |                |  |  |  |

|-------------|------------------|----------------|-------------|----------------|--|--|--|

| Device      | EPROM<br>Program | ROM<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |

| PIC12C508   | 512 x 12         |                | 25          |                |  |  |  |

| PIC12C509   | 1024 x 12        |                | 41          |                |  |  |  |

| PIC12C508A  | 512 x 12         |                | 25          |                |  |  |  |

| PIC12C509A  | 1024 x 12        |                | 41          |                |  |  |  |

| PIC12CR509A |                  | 1024 x 12      | 41          |                |  |  |  |

| PIC12CE518  | 512 x 12         |                | 25 x 8      | 16 x 8         |  |  |  |

| PIC12CE519  | 1024 x 12        |                | 41 x 8      | 16 x 8         |  |  |  |

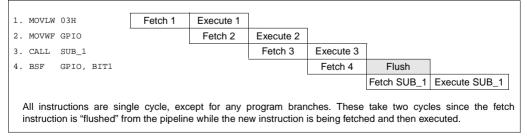

The PIC12C5XX can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC12C5XX has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C5XX simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC12C5XX device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1.

### 3.1 Clocking Scheme/Instruction Cycle

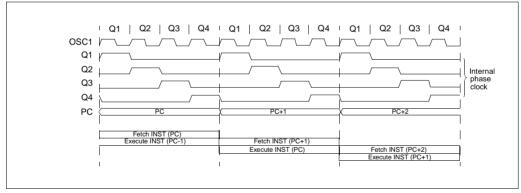

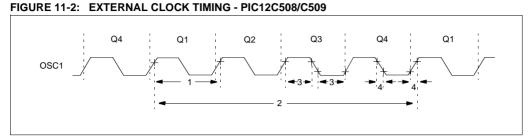

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

### 3.2 Instruction Flow/Pipelining

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.8 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 07 contains the value 10h

- · Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-2.

#### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw | 0x10  | ;initialize pointer |

|----------|-------|-------|---------------------|

|          | movwf | FSR   | ; to RAM            |

| NEXT     | clrf  | INDF  | clear INDF register |

|          | incf  | FSR,F | ;inc pointer        |

|          | btfsc | FSR,4 | ;all done?          |

|          | goto  | NEXT  | ;NO, clear next     |

| CONTINUE | 9     |       | -,                  |

|          | :     |       | ;YES, continue      |

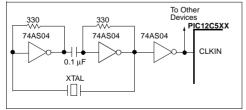

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC12C508/PIC12C508A/PIC12CE518:** Does not use banking. FSR<7:5> are unimplemented and read as '1's.

### PIC12C509/PIC12C509A/PIC12CR509A/

**PIC12CE519:** Uses FSR<5>. Selects between bank 0 and bank 1. FSR<7:6> is unimplemented, read as '1'.

### FIGURE 4-9: DIRECT/INDIRECT ADDRESSING

### FIGURE 5-2: SUCCESSIVE I/O OPERATION

| PC         | Y PC + 1                         | X PC + 2                                                                         | X PC + 3                                                                                | This example shows a write to GPIO follower                                                                 |

|------------|----------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| MOVWF GPIO | MOVF GPIO,W                      | NOP                                                                              | NOP                                                                                     | by a read from GPIO.<br>Data setup time = (0.25 Tcy – TpD)                                                  |

|            | 1<br>1<br>1                      | X                                                                                | 1                                                                                       | where: TCY = instruction cycle.<br>TPD = propagation delay                                                  |

|            | Port pin<br>written here         | Port pin<br>sampled here                                                         | ,<br>,<br>,<br>,                                                                        | Therefore, at higher clock frequencies, a write followed by a read may be problematic                       |

|            | MOVWF GPIO<br>(Write to<br>GPIO) | MOVF GPIO,W<br>(Read<br>GPIO)                                                    | NOP                                                                                     |                                                                                                             |

|            |                                  | MOVWF GPIO<br>MOVF GPIO,W<br>Port pin<br>written here<br>MOVWF GPIO<br>(Write to | MOVWF GPIO MOVF GPIO,W NOP Port pin written here MOVWF GPIO MOVF GPIO,W (Write to (Read | MOVWF GPIO MOVF GPIO,W NOP NOP<br>Port pin<br>written here<br>MOVWF GPIO MOVF GPIO,W NOP<br>(Write to (Read |

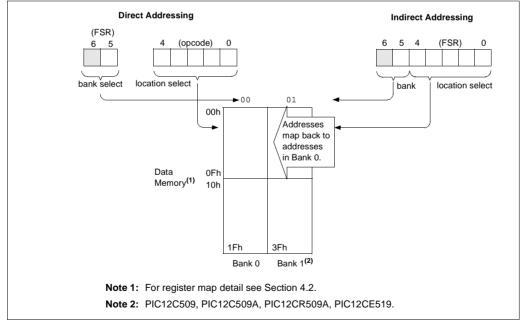

#### 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 8-4 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

### FIGURE 8-4: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

Figure 8-5 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 8-5: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

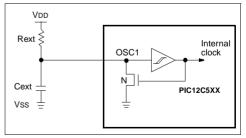

### 8.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 8-6 shows how the R/C combination is connected to the PIC12C5XX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

# FIGURE 8-6: EXTERNAL RC OSCILLATOR MODE

### 8.7 <u>Time-Out Sequence, Power Down,</u> and Wake-up from SLEEP Status Bits (TO/PD/GPWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits in the STATUS register can be tested to determine if a RESET condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) reset.

| TABLE 8-7: | TO/PD/GPWUF STATUS |

|------------|--------------------|

|            | AFTER RESET        |

| GPWUF | то | PD | RESET caused by                     |

|-------|----|----|-------------------------------------|

| 0     | 0  | 0  | WDT wake-up from<br>SLEEP           |

| 0     | 0  | u  | WDT time-out (not from<br>SLEEP)    |

| 0     | 1  | 0  | MCLR wake-up from<br>SLEEP          |

| 0     | 1  | 1  | Power-up                            |

| 0     | u  | u  | MCLR not during SLEEP               |

| 1     | 1  | 0  | Wake-up from SLEEP on<br>pin change |

Legend: u = unchanged

Note 1: The TO, PD, and GPWUF bits maintain their status (u) until a reset occurs. A lowpulse on the MCLR input does not change the TO, PD, and GPWUF status bits.

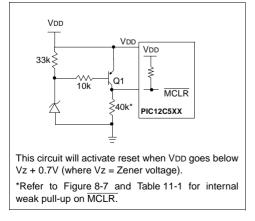

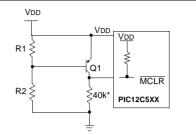

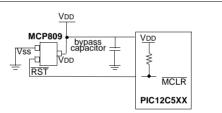

### 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset PIC12C5XX devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-13 , Figure 8-14 and Figure 8-15

#### FIGURE 8-13: BROWN-OUT PROTECTION CIRCUIT 1

### FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

\*Refer to Figure 8-7 and Table 11-1 for internal weak pull-up on MCLR.

### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX family of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accomodate 5V and 3V systems.

| INCF                      | Increment f                                                                                                                                                         |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                   | [label] INCF f,d                                                                                                                                                    |

| Operands:                 | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                           |

| Operation:                | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected:          | Z                                                                                                                                                                   |

| Encoding:                 | 0010 10df ffff                                                                                                                                                      |

| Description:              | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |

| Words:                    | 1                                                                                                                                                                   |

| Cycles:                   | 1                                                                                                                                                                   |

| Example:                  | INCF CNT, 1                                                                                                                                                         |

| Before Instru<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                       |

| After Instruct            |                                                                                                                                                                     |

| CNT<br>Z                  | = 0x00<br>= 1                                                                                                                                                       |

|                           |                                                                                                                                                                     |

| INCFSZ                    | Increment f, Skip if 0                                                                                                                                              |

| Syntax:                   | [label] INCFSZ f,d                                                                                                                                                  |

| Operands:                 | $0 \le f \le 31$                                                                                                                                                    |

| Syntax:                                             | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:                                           | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                 |

| Operation:                                          | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                                 |

| Status Affected:                                    | None                                                                                                                                                                                                                                                                                                                                             |

| Encoding:                                           | 0011 11df ffff                                                                                                                                                                                                                                                                                                                                   |

| Description:                                        | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, then the next instruc-<br>tion, which is already fetched, is dis-<br>carded and an NOP is executed<br>instead making it a two cycle instruc-<br>tion. |

| Words:                                              | 1                                                                                                                                                                                                                                                                                                                                                |

| Cycles:                                             | 1(2)                                                                                                                                                                                                                                                                                                                                             |

| Example:                                            | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                                  |

|                                                     | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                                  |

| Before Inst<br>PC                                   | ruction<br>= address (HERE)                                                                                                                                                                                                                                                                                                                      |

| After Instru<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | = CNT + 1;                                                                                                                                                                                                                                                                                                                                       |

| IORLW                       | Inclusive OR literal with W                                                                                            |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | [ <i>label</i> ] IORLW k                                                                                               |

| Operands:                   | $0 \le k \le 255$                                                                                                      |

| Operation:                  | (W) .OR. (k) $\rightarrow$ (W)                                                                                         |

| Status Affected:            | Z                                                                                                                      |

| Encoding:                   | 1101 kkkk kkkk                                                                                                         |

| Description:                | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:                      | 1                                                                                                                      |

| Cycles:                     | 1                                                                                                                      |

| Example:                    | IORLW 0x35                                                                                                             |

| Before Instru<br>W =        | uction<br>0x9A                                                                                                         |

| After Instruc<br>W =<br>Z = | tion<br>0xBF<br>0                                                                                                      |

| IORWF Inclusive OR W with f               |                                                                                                                                                                      |  |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                   | [ label ] IORWF f,d                                                                                                                                                  |  |  |  |

| Operands:                                 | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                     |  |  |  |

| Operation:                                | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                     |  |  |  |

| Status Affected                           | I: Z                                                                                                                                                                 |  |  |  |

| Encoding:                                 | 0001 00df ffff                                                                                                                                                       |  |  |  |

| Description:                              | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |  |  |  |

| Words:                                    | 1                                                                                                                                                                    |  |  |  |

| Cycles:                                   | 1                                                                                                                                                                    |  |  |  |

| Example:                                  | IORWF RESULT, 0                                                                                                                                                      |  |  |  |

| Before Inst<br>RESUL<br>W<br>After Instru | LT = 0x13<br>= 0x91                                                                                                                                                  |  |  |  |

| RESUL<br>W<br>Z                           |                                                                                                                                                                      |  |  |  |

| SWAPF                       | Swap Nibbles in f                                                                                                                                                     |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | [label] SWAPF f,d                                                                                                                                                     |

| Operands:                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                      |

| Operation:                  | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                             |

| Status Affected:            | None                                                                                                                                                                  |

| Encoding:                   | 0011 10df ffff                                                                                                                                                        |

| Description:                | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |

| Words:                      | 1                                                                                                                                                                     |

| Cycles:                     | 1                                                                                                                                                                     |

| Example                     | SWAPF REG1, 0                                                                                                                                                         |

| Before Instru<br>REG1       | iction<br>= 0xA5                                                                                                                                                      |

| After Instruct<br>REG1<br>W | tion<br>= 0xA5<br>= 0X5A                                                                                                                                              |

| TRIS                   | Load TRIS Register                                                      |  |  |  |  |  |

|------------------------|-------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                | [label] TRIS f                                                          |  |  |  |  |  |

| Operands:              | f = 6                                                                   |  |  |  |  |  |

| Operation:             | (W) $\rightarrow$ TRIS register f                                       |  |  |  |  |  |

| Status Affected:       | None                                                                    |  |  |  |  |  |

| Encoding:              | 0000 0000 0fff                                                          |  |  |  |  |  |

| Description:           | TRIS register 'f' (f = 6) is loaded with the contents of the W register |  |  |  |  |  |

| Words:                 | 1                                                                       |  |  |  |  |  |

| Cycles:                | 1                                                                       |  |  |  |  |  |

| Example                | TRIS GPIO                                                               |  |  |  |  |  |

| Before Instru<br>W     | iction<br>= 0XA5                                                        |  |  |  |  |  |

| After Instruct<br>TRIS |                                                                         |  |  |  |  |  |

| <b>Note:</b> f = 6 f   | or PIC12C5XX only.                                                      |  |  |  |  |  |

| XORLW                          | XORLW Exclusive OR literal with W |                                                                                                                         |      |  |  |  |  |  |

|--------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|

| Syntax:                        | [ <i>label</i> ]                  | XORLW                                                                                                                   | k    |  |  |  |  |  |

| Operands:                      | $0 \le k \le 2$                   | 55                                                                                                                      |      |  |  |  |  |  |

| Operation:                     | (W) .XO                           | $R. k \to (W)$                                                                                                          | /)   |  |  |  |  |  |

| Status Affected:               | Z                                 | Z                                                                                                                       |      |  |  |  |  |  |

| Encoding:                      | 1111                              | kkkk                                                                                                                    | kkkk |  |  |  |  |  |

| Description:                   | XOR'ed w                          | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |      |  |  |  |  |  |

| Words:                         | 1                                 |                                                                                                                         |      |  |  |  |  |  |

| Cycles:                        | 1                                 |                                                                                                                         |      |  |  |  |  |  |

| Example:                       | XORLW                             | 0xAF                                                                                                                    |      |  |  |  |  |  |

| Before Instruction<br>W = 0xB5 |                                   |                                                                                                                         |      |  |  |  |  |  |

| After Instruc<br>W =           | tion<br>0x1A                      |                                                                                                                         |      |  |  |  |  |  |

| XORWF                                              | Exclusive OR W with f                                                                                                                                                              |  |  |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                            | [label] XORWF f,d                                                                                                                                                                  |  |  |  |  |  |  |

| Operands:                                          | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                   |  |  |  |  |  |  |

| Operation:                                         | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected:                                   | Z                                                                                                                                                                                  |  |  |  |  |  |  |

| Encoding:                                          | 0001 10df ffff                                                                                                                                                                     |  |  |  |  |  |  |

| Description:                                       | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |  |  |  |  |  |  |

| Words:                                             | 1                                                                                                                                                                                  |  |  |  |  |  |  |

| Cycles:                                            | 1                                                                                                                                                                                  |  |  |  |  |  |  |

| Example                                            | XORWF REG,1                                                                                                                                                                        |  |  |  |  |  |  |

| Before Instru<br>REG<br>W<br>After Instruct<br>REG | = 0xAF<br>= 0xB5<br>ion<br>= 0x1A                                                                                                                                                  |  |  |  |  |  |  |

| W                                                  | = 0xB5                                                                                                                                                                             |  |  |  |  |  |  |

### 10.6 <u>SIMICE Entry-Level Hardware</u> <u>Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB<sup>™</sup>-SIM. Both SIM-ICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PICmicro® 8-bit microcontrollers. SIMICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entrylevel system development.

### 10.7 <u>PICDEM-1 Low-Cost PICmicro®</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

### 10.8 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

### 10.9 PICDEM-3 Low-Cost PIC16CXXX Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 seqments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

### 11.2 DC CHARACTERISTICS:

### PIC12C508/509 (Commercial, Industrial, Extended)

|              |                                                                |                                                                                                           | <b>rd Operati</b><br>ng tempera | -      | 0°C ≤              | TA ≤ + | s otherwise specified)<br>70°C (commercial)                         |  |  |  |

|--------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------|--------|--------------------|--------|---------------------------------------------------------------------|--|--|--|

| DC CHA       | ARACTERISTICS                                                  | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |                                 |        |                    |        |                                                                     |  |  |  |

|              |                                                                | Operati<br>Section                                                                                        |                                 | Vdd ra |                    |        | d in DC spec Section 11.1 and                                       |  |  |  |

| Param<br>No. | Characteristic                                                 | Sym                                                                                                       | Min                             | Тур†   | Max                | Units  | Conditions                                                          |  |  |  |

| NO.          |                                                                |                                                                                                           |                                 |        |                    |        |                                                                     |  |  |  |

|              | Input Low Voltage                                              | VIL                                                                                                       |                                 |        |                    |        |                                                                     |  |  |  |

| <b>D</b> 000 | •                                                              | VIL                                                                                                       | Vee                             | -      | 0.01/              | V      |                                                                     |  |  |  |

| D030         | with TTL buffer                                                |                                                                                                           | Vss                             | -      | 0.8V               | V      | 4.5 < VDD ≤ 5.5V                                                    |  |  |  |

| D031         | with Coheritt Trigger huffer                                   |                                                                                                           | Vee                             | -      | 0.15VDD<br>0.15VDD | V<br>V | otherwise                                                           |  |  |  |

| D031<br>D032 | with Schmitt Trigger buffer<br>MCLR, GP2/T0CKI (in EXTRC mode) |                                                                                                           | Vss<br>Vss                      | -      | 0.15VDD<br>0.15VDD | V      |                                                                     |  |  |  |

|              |                                                                |                                                                                                           | VSS<br>VSS                      | -      | 0.15VDD            | v      |                                                                     |  |  |  |

| D033         | OSC1 (EXTRC) <sup>(1)</sup>                                    |                                                                                                           |                                 | -      |                    |        |                                                                     |  |  |  |

| D033         | OSC1 (in XT and LP)                                            |                                                                                                           | Vss                             | -      | 0.3Vdd             | V      | Note1                                                               |  |  |  |

|              | Input High Voltage                                             |                                                                                                           |                                 |        |                    |        |                                                                     |  |  |  |

|              | I/O ports                                                      | VIH                                                                                                       |                                 | -      |                    |        |                                                                     |  |  |  |

| D040         | with TTL buffer                                                | Vss                                                                                                       | 2.0V                            | -      | Vdd                | V      | $4.5 \leq VDD \leq 5.5V$                                            |  |  |  |

| D040A        |                                                                |                                                                                                           | 0.25VDD+<br>0.8V                | -      | Vdd                | V      | otherwise                                                           |  |  |  |

| D041         | with Schmitt Trigger buffer                                    |                                                                                                           | 0.85VDD                         | -      | VDD                | v      | For entire VDD range                                                |  |  |  |

| D042         | MCLR/GP2/T0CKI                                                 |                                                                                                           | 0.85VDD                         | -      | VDD                | v      |                                                                     |  |  |  |

| -            |                                                                |                                                                                                           | 0.7VDD                          | -      | VDD                | V      | Note1                                                               |  |  |  |

| D043         | OSC1 (in EXTRC mode)                                           |                                                                                                           | 0.85VDD                         | -      | VDD                | V      |                                                                     |  |  |  |

| D070         | GPIO weak pull-up current                                      | IPUR                                                                                                      | 50                              | 250    | 400                | μA     | VDD = 5V, VPIN = VSS                                                |  |  |  |

|              | Input Leakage Current <sup>(2, 3)</sup>                        |                                                                                                           |                                 |        |                    | 1.     | For VDD ≤5.5V                                                       |  |  |  |

| D060         | I/O ports                                                      | ١L                                                                                                        | -1                              | 0.5    | <u>+</u> 1         | μΑ     | Vss ≤ VPIN ≤ VDD,<br>Pin at hi-impedance                            |  |  |  |

| D061         | MCLR, GP2/T0CKI                                                |                                                                                                           | 20                              | 130    | 250                | μA     | $V_{PIN} = V_{SS} + 0.25 V^{(2)}$                                   |  |  |  |

| 2001         |                                                                |                                                                                                           |                                 | 0.5    | +5                 | μΑ     | VPIN = VDD                                                          |  |  |  |

| D063         | OSC1                                                           |                                                                                                           | -3                              | 0.5    | +3                 | μΑ     | $Vss \leq VPIN \leq VDD$ ,                                          |  |  |  |

|              |                                                                |                                                                                                           |                                 |        |                    |        | XT and LP options                                                   |  |  |  |

|              | Output Low Voltage                                             |                                                                                                           |                                 |        |                    |        |                                                                     |  |  |  |

| D080         | I/O ports/CLKOUT                                               | Vol                                                                                                       | -                               | -      | 0.6                | V      | IOL = 8.7 mA, VDD = 4.5V                                            |  |  |  |

|              | Output High Voltage                                            |                                                                                                           |                                 |        |                    |        |                                                                     |  |  |  |

| D090         | I/O ports/CLKOUT (3)                                           | Voh                                                                                                       | Vdd - 0.7                       | -      | -                  | V      | IOH = -5.4 mA, VDD = 4.5V                                           |  |  |  |

|              | Capacitive Loading Specs on                                    |                                                                                                           |                                 |        |                    |        |                                                                     |  |  |  |

|              | Output Pins                                                    |                                                                                                           |                                 |        |                    |        |                                                                     |  |  |  |

| D100         | OSC2 pin                                                       | Cosc2                                                                                                     | -                               | -      | 15                 | pF     | In XT and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101         | All I/O pins                                                   | Cio                                                                                                       | -                               | -      | 50                 | pF     |                                                                     |  |  |  |

|              | Data in "Typ" column is at 51/ 25°C ur                         |                                                                                                           | l                               |        |                    |        | l                                                                   |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C5XX be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

### 11.4 Timing Diagrams and Specifications

| AC Characteristics |            |                                         |     |                    |        |       |                |  |  |

|--------------------|------------|-----------------------------------------|-----|--------------------|--------|-------|----------------|--|--|

| Parameter<br>No.   | Sym        | Characteristic                          |     | Typ <sup>(1)</sup> | Мах    | Units | Conditions     |  |  |

|                    | Fosc       | External CLKIN Frequency <sup>(2)</sup> |     |                    |        |       |                |  |  |

|                    |            |                                         | DC  | —                  | 4      | MHz   | XT osc mode    |  |  |

|                    |            |                                         | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

|                    |            | Oscillator Frequency <sup>(2)</sup>     |     |                    |        |       |                |  |  |

|                    |            |                                         | 0.1 | _                  | 4      | MHz   | XT osc mode    |  |  |

|                    |            |                                         | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

| 1                  | Tosc       | External CLKIN Period <sup>(2)</sup>    | 250 | —                  | _      | ns    | EXTRC osc mode |  |  |

|                    |            |                                         | 250 | _                  | _      | ns    | XT osc mode    |  |  |

|                    |            |                                         | 5   | —                  | —      | ms    | LP osc mode    |  |  |

|                    |            | Oscillator Period <sup>(2)</sup>        | 250 | _                  | _      | ns    | EXTRC osc mode |  |  |

|                    |            |                                         | 250 | _                  | 10,000 | ns    | XT osc mode    |  |  |

|                    |            |                                         | 5   | —                  | —      | ms    | LP osc mode    |  |  |

| 2                  | Тсу        | Instruction Cycle Time <sup>(3)</sup>   | —   | 4/Fosc             | —      |       |                |  |  |

| 3                  | TosL, TosH | Clock in (OSC1) Low or High Time        | 50* | —                  | —      | ns    | XT oscillator  |  |  |

|                    |            |                                         | 2*  | _                  | —      | ms    | LP oscillator  |  |  |

| 4                  | TosR, TosF | Clock in (OSC1) Rise or Fall Time       | —   | -                  | 25*    | ns    | XT oscillator  |  |  |

|                    |            |                                         | —   | —                  | 50*    | ns    | LP oscillator  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

Instruction cycle period (Tcy) equals four times the input oscillator time base period.

### TABLE 11-4: TIMING REQUIREMENTS - PIC12C508/C509

| AC CharacteristicsStandard Operating Conditions (unless otherwise spect<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercia)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ (extended<br>Operating Voltage VDD range is described in Section 11.1 |          |                                                                          |     |                    |      |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|-----|--------------------|------|-------|

| Parameter<br>No.                                                                                                                                                                                                                                                                                                          | Sym      | Characteristic                                                           | Min | Typ <sup>(1)</sup> | Max  | Units |

| 17                                                                                                                                                                                                                                                                                                                        | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(3)</sup>            | _   | -                  | 100* | ns    |

| 18                                                                                                                                                                                                                                                                                                                        | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) | TBD | —                  | _    | ns    |

| 19                                                                                                                                                                                                                                                                                                                        | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)                         | TBD | —                  | _    | ns    |

| 20                                                                                                                                                                                                                                                                                                                        | TioR     | Port output rise time <sup>(2, 3)</sup>                                  | _   | 10                 | 25** | ns    |

| 21                                                                                                                                                                                                                                                                                                                        | TioF     | Port output fall time <sup>(2, 3)</sup>                                  | _   | 10                 | 25** | ns    |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: Measurements are taken in EXTRC mode.

- 3: See Figure 11-1 for loading conditions.

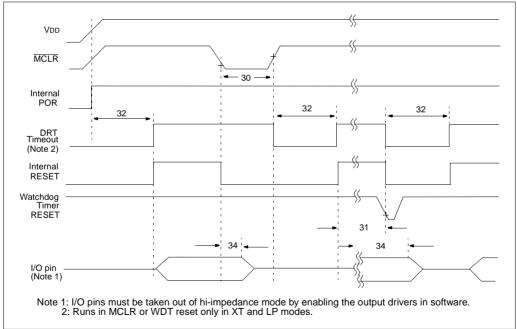

### FIGURE 11-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC12C508/C509

| Oscillator  | Frequency | VDD = 2.5V | VDD = 5.5V |

|-------------|-----------|------------|------------|

| External RC | 4 MHz     | 250 µA*    | 780 µA*    |

| Internal RC | 4 MHz     | 420 µA     | 1.1 mA     |

| XT          | 4 MHz     | 251 µA     | 780 µA     |

| LP          | 32 KHz    | 15 µA      | 37 µA      |

### TABLE 12-1: DYNAMIC IDD (TYPICAL) - WDT ENABLED, 25°C

\*Does not include current through external R&C.

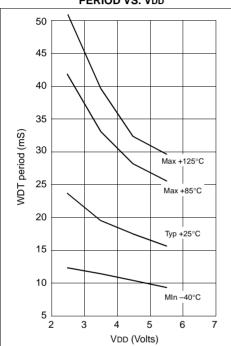

### FIGURE 12-3: WDT TIMER TIME-OUT PERIOD VS. VDD

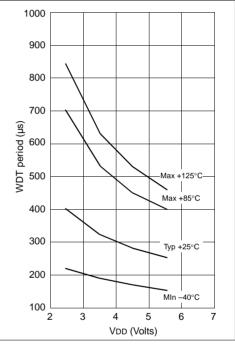

### FIGURE 12-4: SHORT DRT PERIOD VS. VDD

### 13.3 DC CHARACTERISTICS:

### PIC12C508A/509A (Commercial, Industrial, Extended) PIC12C518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

|                |                                    |                                                                                                           | r <b>d Operati</b><br>ng tempera |        | 0°C ≤      | TA ≤ + | s otherwise specified)<br>70°C (commercial)                                                              |  |  |

|----------------|------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|--------|------------|--------|----------------------------------------------------------------------------------------------------------|--|--|

| DC CH          | ARACTERISTICS                      | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |                                  |        |            |        |                                                                                                          |  |  |

|                |                                    | Operatii<br>Section                                                                                       |                                  | VDD ra |            |        | d in DC spec Section 13.1 and                                                                            |  |  |

| Param          | Characteristic                     | Sym                                                                                                       | Min                              | Typ†   | Max        | Units  | Conditions                                                                                               |  |  |

| No.            |                                    |                                                                                                           |                                  |        |            |        |                                                                                                          |  |  |

|                | Input Low Voltage                  |                                                                                                           |                                  |        |            |        |                                                                                                          |  |  |

|                | I/O ports                          | VIL                                                                                                       |                                  |        |            |        |                                                                                                          |  |  |

| D030           | with TTL buffer                    |                                                                                                           | Vss                              | -      | 0.8V       | V      | For $4.5V \le VDD \le 5.5V$                                                                              |  |  |

|                |                                    |                                                                                                           | Vss                              | -      | 0.15Vdd    | V      | otherwise                                                                                                |  |  |

| D031           | with Schmitt Trigger buffer        |                                                                                                           | Vss                              | -      | 0.2VDD     | V      |                                                                                                          |  |  |

| D032           | MCLR, GP2/T0CKI (in EXTRC mode)    |                                                                                                           | Vss                              | -      | 0.2Vdd     | V      |                                                                                                          |  |  |

| D033           | OSC1 (in EXTRC mode)               |                                                                                                           | Vss                              | -      | 0.2VDD     |        | Note 1                                                                                                   |  |  |

| D033           | OSC1 (in XT and LP)                |                                                                                                           | Vss                              | -      | 0.3VDD     | V      | Note 1                                                                                                   |  |  |

|                | Input High Voltage                 | .,                                                                                                        |                                  |        |            |        |                                                                                                          |  |  |