Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | 16 x 8                                                                    |

| RAM Size                   | 25 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce518-04-p |

|                            |                                                                           |

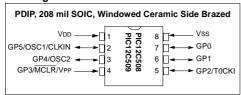

### Pin Diagram - PIC12C508/509

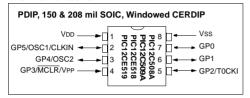

# Pin Diagram - PIC12C508A/509A, PIC12CE518/519

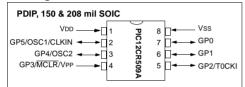

### Pin Diagram - PIC12CR509A

#### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

#### 2.0 PIC12C5XX DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12C5XX Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in ceramic side brazed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

Microchip's PICSTART® PLUS and PRO MATE® programmers all support programming of the PIC12C5XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

# 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> Production (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

#### 2.5 Read Only Memory (ROM) Device

Microchip offers masked ROM to give the customer a low cost option for high volume, mature products.

#### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12C5XX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C5XX uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12-bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (1µs @ 4MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), ROM memory, and non-volatile (EEPROM) for each device.

|             | Memory           |                |             |                |  |  |  |  |  |

|-------------|------------------|----------------|-------------|----------------|--|--|--|--|--|

| Device      | EPROM<br>Program | ROM<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |  |

| PIC12C508   | 512 x 12         |                | 25          |                |  |  |  |  |  |

| PIC12C509   | 1024 x 12        |                | 41          |                |  |  |  |  |  |

| PIC12C508A  | 512 x 12         |                | 25          |                |  |  |  |  |  |

| PIC12C509A  | 1024 x 12        |                | 41          |                |  |  |  |  |  |

| PIC12CR509A |                  | 1024 x 12      | 41          |                |  |  |  |  |  |

| PIC12CE518  | 512 x 12         |                | 25 x 8      | 16 x 8         |  |  |  |  |  |

| PIC12CE519  | 1024 x 12        |                | 41 x 8      | 16 x 8         |  |  |  |  |  |

The PIC12C5XX can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC12C5XX has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C5XX simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC12C5XX device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1.

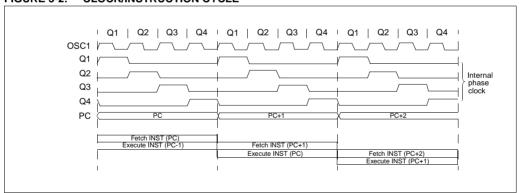

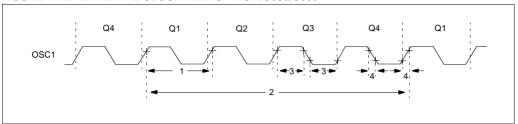

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

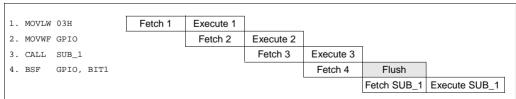

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

### 4.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status, and the page preselect bit for program memories larger than 512 words.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS register because these instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions, which do affect STATUS bits, see Instruction Set Summary.

### FIGURE 4-4: STATUS REGISTER (ADDRESS:03h)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                                                                                                                              | R/W-0        | R-1 | R-1                | R/W-x                                          | R/W-x | R/W-x                  |                                           |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|--------------------|------------------------------------------------|-------|------------------------|-------------------------------------------|--|--|--|--|

| GPWUF  | _                                                                                                                                                                                                                                                                                                                                                                                  | PA0          | TO  | PD                 | Z                                              | DC    | С                      | R = Readable bit                          |  |  |  |  |

| bit7   | 6                                                                                                                                                                                                                                                                                                                                                                                  | 5            | 4   | 3                  | 2                                              | 1     | bit0                   | W = Writable bit - n = Value at POR reset |  |  |  |  |

| bit 7: | GPWUF: GPIO reset bit  1 = Reset due to wake-up from SLEEP on pin change  0 = After power up or other reset                                                                                                                                                                                                                                                                        |              |     |                    |                                                |       |                        |                                           |  |  |  |  |

| bit 6: | Unimplem                                                                                                                                                                                                                                                                                                                                                                           | ented        |     |                    |                                                |       |                        |                                           |  |  |  |  |

| bit 5: | PA0: Program page preselect bits  1 = Page 1 (200h - 3FFh) - PIC12C509, PIC12C509A, PIC12CR509A and PIC12CE519  0 = Page 0 (000h - 1FFh) - PIC12C5XX  Each page is 512 bytes.  Using the PA0 bit as a general purpose read/write bit in devices which do not use it for program page preselect is not recommended since this may affect upward compatibility with future products. |              |     |                    |                                                |       |                        |                                           |  |  |  |  |

| bit 4: | $\overline{TO}$ : Time-of 1 = After point 0 = A WDT                                                                                                                                                                                                                                                                                                                                | ower-up, CL  |     | uction, or S       | LEEP instruc                                   | tion  |                        |                                           |  |  |  |  |

| bit 3: | <b>PD</b> : Power-<br>1 = After po<br>0 = By exec                                                                                                                                                                                                                                                                                                                                  | ower-up or l |     |                    | tion                                           |       |                        |                                           |  |  |  |  |

| bit 2: | <b>Z</b> : Zero bit<br>1 = The res<br>0 = The res                                                                                                                                                                                                                                                                                                                                  |              |     |                    | tion is zero<br>tion is not ze                 | ero   |                        |                                           |  |  |  |  |

| bit 1: |                                                                                                                                                                                                                                                                                                                                                                                    |              |     |                    |                                                |       |                        |                                           |  |  |  |  |

| bit 0: | C: Carry/bo<br>ADDWF<br>1 = A carry<br>0 = A carry                                                                                                                                                                                                                                                                                                                                 | occurred     |     | SUBWF<br>1 = A bor | RF, RLF insti<br>row did not o<br>row occurred | occur | RRF or R<br>Load bit v | LF<br>with LSB or MSB, respectively       |  |  |  |  |

NOTES:

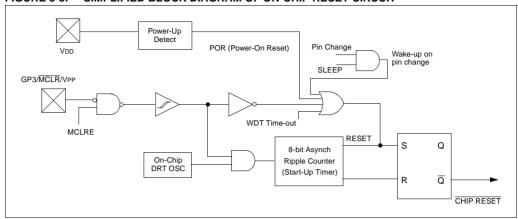

FIGURE 8-8: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

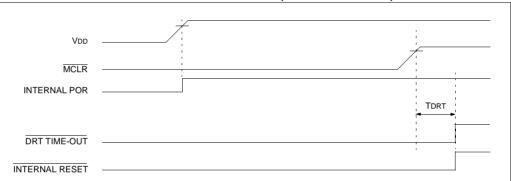

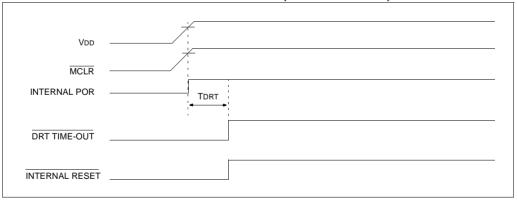

FIGURE 8-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR PULLED LOW)

FIGURE 8-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

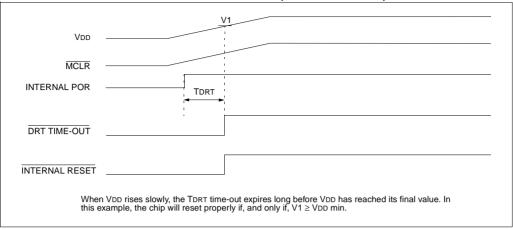

FIGURE 8-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### 8.5 Device Reset Timer (DRT)

In the PIC12C5XX, DRT runs from RESET and varies based on oscillator selection (see Table 8-5.)

The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min., and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after MCLR has reached a logic high (VIHMCLR) level. Thus, programming GP3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the GP3/MCLR/VPP pin as a general purpose input.

The Device Reset time delay will vary from chip to chip due to VDD, temperature, and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake from SLEEP mode automatically.

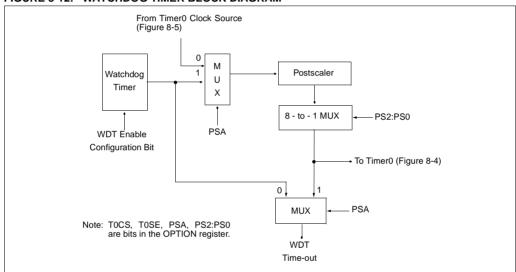

#### 8.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the external RC oscillator of the GP5/OSC1/CLKIN pin and the internal 4 MHz oscillator. That means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT reset or wake-up reset generates a device RESET.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer reset.

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 8.1). Refer to the PIC12C5XX Programming Specifications to determine how to access the configuration word.

TABLE 8-5: DRT (DEVICE RESET TIMER PERIOD)

| Oscillator<br>Configuration | POR Reset       | Subsequent<br>Resets |

|-----------------------------|-----------------|----------------------|

| IntRC &<br>ExtRC            | 18 ms (typical) | 300 μs (typical)     |

| XT & LP                     | 18 ms (typical) | 18 ms (typical)      |

#### 8.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 8.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT wake-up reset.

#### FIGURE 8-12: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 8-6: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

|   | Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| Ī | N/A     | OPTION | GPWU  | GPPU  | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

$\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

#### 9.0 INSTRUCTION SET SUMMARY

Each PIC12C5XX instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC12C5XX instruction set summary in Table 9-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                              |

| x             | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select; d = 0 (store result in W) d = 1 (store result in file register 'f') Default is d = 1                                                           |

| label         | Label name                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                    |

| WDT           | Watchdog Timer Counter                                                                                                                                             |

| TO            | Time-Out bit                                                                                                                                                       |

| PD            | Power-Down bit                                                                                                                                                     |

| dest          | Destination, either the W register or the specified register file location                                                                                         |

| []            | Options                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                        |

| <>            | Register bit field                                                                                                                                                 |

| €             | In the set of                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

# FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

ADDWF Add W and f [ label ] ADDWF Syntax: f,d Operands: 0 < f < 31 $d \in [0,1]$ Operation:  $(W) + (f) \rightarrow (dest)$ Status Affected: C, DC, Z Encodina: 0001 11df ffff Description: Add the contents of the W register and register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. Words: Cycles: Example: ADDWF FSR, 0 Before Instruction

W = 0x17 FSR = 0xC2After Instruction W = 0xD9 FSR = 0xC2

ANDLW And literal with W [label] ANDLW k Syntax: Operands:  $0 \le k \le 255$ Operation: (W).AND. (k)  $\rightarrow$  (W) Status Affected: Ζ Encoding: 1110 kkkk kkkk Description: The contents of the W register are AND'ed with the eight-bit literal 'k'. The result is placed in the W register. Words: 1 Cycles: 1 Example: ANDLW 0x5FBefore Instruction W 0xA3

ANDWF AND W with f [label] ANDWF Syntax: f,d Operands:  $0 \le f \le 31$  $d \in [0,1]$ Operation: (W) .AND. (f)  $\rightarrow$  (dest) Status Affected: Ζ Encodina: 0001 01df ffff Description: The contents of the W register are AND'ed with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. Words: Cycles: Example: ANDWF FSR. 1 Before Instruction W = 0x17FSR = 0xC2 After Instruction W 0x17 0x02 FSR =

**BCF** Bit Clear f Syntax: [label] BCF f,b Operands:  $0 \le f \le 31$  $0 \le b \le 7$ Operation:  $0 \rightarrow (f < b >)$ Status Affected: None Encoding: 0100 bbbf ffff Bit 'b' in register 'f' is cleared. Description: Words: Cycles: Example: BCF FLAG REG, 7 Before Instruction

$FLAG_REG = 0xC7$

$FLAG_REG = 0x47$

After Instruction

After Instruction

0x03

W =

CALL **Subroutine Call** Syntax: [label] CALL k Operands:  $0 \le k \le 255$ Operation: (PC) +  $1 \rightarrow$  Top of Stack;  $k \rightarrow PC < 7:0 > :$  $(STATUS<6:5>) \rightarrow PC<10:9>$ ;  $0 \rightarrow PC < 8 >$ Status Affected: None Encoding: 1001 kkkk kkkk Description: Subroutine call. First, return address (PC+1) is pushed onto the stack. The eight bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STA-TUS<6:5>, PC<8> is cleared. CALL is a two cycle instruction. Words: 1 Cvcles: 2 Example: HERE CALL THERE Before Instruction

After Instruction

PC = address (THERE)

TOS = address (HERE + 1)

address (HERE)

PC =

**CLRF** Clear f [label] CLRF f Syntax: Operands:  $0 \le f \le 31$ Operation:  $00h \rightarrow (f)$ ;  $1 \rightarrow Z$ Status Affected: 7 0000 Encoding: 011f ffff Description: The contents of register 'f' are cleared and the Z bit is set. Words: 1 Cycles: Example: CLRF FLAG\_REG

0x5A

Before Instruction

FLAG\_REG After Instruction

> $FLAG_REG = 0x00$ Z = 1

**CLRW** Clear W [label] CLRW Syntax: Operands: None Operation:  $00h \rightarrow (W);$  $1 \rightarrow Z$ Status Affected: Ζ Encodina: 0000 0100 0000 Description: The W register is cleared. Zero bit (Z) Words: Cycles: Example: CLRW Before Instruction W 0x5A After Instruction W 0x00 7 1

CLRWDT Clear Watchdog Timer

Syntax: [ label ] CLRWDT

Operands: None

Operation:  $00h \rightarrow WDT$ ;

$0 \rightarrow WDT$  prescaler (if assigned);  $1 \rightarrow \overline{TO}$ ;

$1 \rightarrow 10$ ,  $1 \rightarrow PD$

Status Affected:  $\overline{TO}$ ,  $\overline{PD}$

Encoding: 0000 0000 0100

Description: The CLRWDT instruction resets the

WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status hits TO and PD are

not Timer0. Status bits  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  are set.

Words: 1

Cycles: 1

Example: CLRWDT

Before Instruction

WDT counter = 1

After Instruction

## 10.16 <u>KeeLoq® Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

#### 11.4 Timing Diagrams and Specifications

#### FIGURE 11-2: EXTERNAL CLOCK TIMING - PIC12C508/C509

TABLE 11-2: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC12C508/C509

| AC Characteristics | Standard Operating Conditions (unless otherwise specified)                |

|--------------------|---------------------------------------------------------------------------|

|                    | Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial),  |

|                    | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ (industrial), |

|                    | $-40^{\circ}$ C $\leq$ TA $\leq$ +125 $^{\circ}$ C (extended)             |

|                    | Operating Voltage VDD range is described in Section 11.1                  |

| Parameter No. | Sym        | Characteristic                          |     | Тур <sup>(1)</sup> | Max    | Units | Conditions     |

|---------------|------------|-----------------------------------------|-----|--------------------|--------|-------|----------------|

|               | Fosc       | External CLKIN Frequency <sup>(2)</sup> |     |                    |        |       |                |

|               |            | , ,                                     | DC  | _                  | 4      | MHz   | XT osc mode    |

|               |            |                                         | DC  | _                  | 200    | kHz   | LP osc mode    |

|               |            | Oscillator Frequency <sup>(2)</sup>     |     |                    |        |       |                |

|               |            |                                         | 0.1 | _                  | 4      | MHz   | XT osc mode    |

|               |            |                                         | DC  | _                  | 200    | kHz   | LP osc mode    |

| 1             | Tosc       | External CLKIN Period <sup>(2)</sup>    | 250 | _                  | _      | ns    | EXTRC osc mode |

|               |            |                                         | 250 | _                  | _      | ns    | XT osc mode    |

|               |            |                                         | 5   | _                  | _      | ms    | LP osc mode    |

|               |            | Oscillator Period <sup>(2)</sup>        | 250 | _                  | _      | ns    | EXTRC osc mode |

|               |            |                                         | 250 | _                  | 10,000 | ns    | XT osc mode    |

|               |            |                                         | 5   | _                  | _      | ms    | LP osc mode    |

| 2             | Tcy        | Instruction Cycle Time <sup>(3)</sup>   | _   | 4/Fosc             | _      | _     |                |

| 3             | TosL, TosH | Clock in (OSC1) Low or High Time        | 50* | _                  | _      | ns    | XT oscillator  |

|               |            |                                         | 2*  | _                  | _      | ms    | LP oscillator  |

| 4             | TosR, TosF | Clock in (OSC1) Rise or Fall Time       | _   | _                  | 25*    | ns    | XT oscillator  |

|               |            |                                         | _   | _                  | 50*    | ns    | LP oscillator  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

<sup>3:</sup> Instruction cycle period (TcY) equals four times the input oscillator time base period.

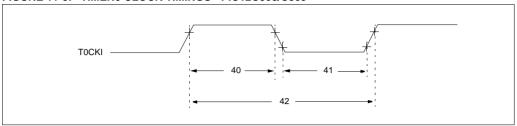

### FIGURE 11-5: TIMERO CLOCK TIMINGS - PIC12C508/C509

TABLE 11-7: TIMERO CLOCK REQUIREMENTS - PIC12C508/C509

| AC Characteristics |                        |                    | Standard Operating Operating Tempera Operating Voltage \ | ture 0°C ≤<br>-40°C ≤<br>-40°C ≤ | ≦ TA ≤ +<br>≦ TA ≤ +<br>≤ TA ≤ + | 70°C (<br>85°C (<br>125°C | comme<br>(industr<br>(exten | rcial)<br>ial)<br>ded)                                    |

|--------------------|------------------------|--------------------|----------------------------------------------------------|----------------------------------|----------------------------------|---------------------------|-----------------------------|-----------------------------------------------------------|

| Parameter No.      | ter Sym Characteristic |                    |                                                          | Min                              | Typ <sup>(1)</sup>               | Max                       | Units                       | Conditions                                                |

| 40                 | Tt0H                   | T0CKI High Pulse V | Vidth - No Prescaler                                     | 0.5 Tcy + 20*                    | _                                | _                         | ns                          |                                                           |

|                    |                        |                    | - With Prescaler                                         | 10*                              | _                                | _                         | ns                          |                                                           |

| 41                 | Tt0L                   | T0CKI Low Pulse W  | Vidth - No Prescaler                                     | 0.5 Tcy + 20*                    | _                                | _                         | ns                          |                                                           |

|                    |                        |                    | 10*                                                      | _                                | _                                | ns                        |                             |                                                           |

| 42                 | Tt0P                   | T0CKI Period       |                                                          | 20 or <u>Tcy + 40</u> *<br>N     | _                                | _                         | ns                          | Whichever is greater.  N = Prescale Value (1, 2, 4,, 256) |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

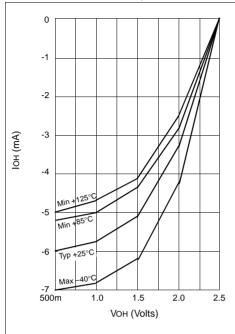

FIGURE 12-5: IOH vs. VOH, VDD = 2.5 V

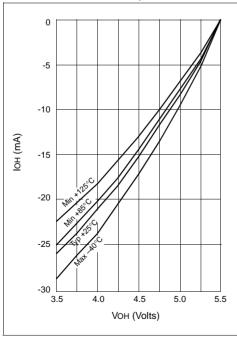

FIGURE 12-6: IOH vs. VOH, VDD = 5.5 V

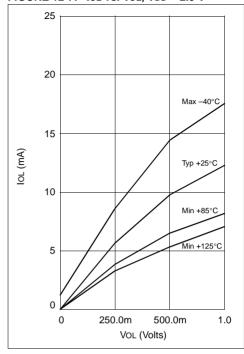

FIGURE 12-7: IOL vs. VOL, VDD = 2.5 V

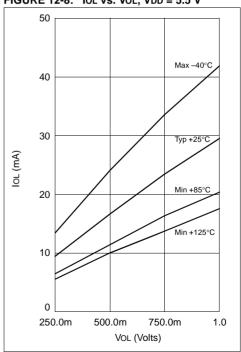

FIGURE 12-8: IOL vs. VOL, VDD = 5.5 V

#### 13.1 DC CHARACTERISTICS:

PIC12C508A/509A (Commercial, Industrial, Extended) PIC12CE518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

DC Characteristics Power Supply Pins Standard Operating Conditions (unless otherwise specified)

Operating Temperature  $0^{\circ}C \le TA \le +70^{\circ}C$  (commercial)

$-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C} \text{ (industrial)}$  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C} \text{ (extended)}$

|               | $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C} \text{ (extended)}$ |                |        |                    |         |          |                                                                            |  |  |

|---------------|---------------------------------------------------------------------------------|----------------|--------|--------------------|---------|----------|----------------------------------------------------------------------------|--|--|

| Parm<br>No.   | Characteristic                                                                  | Sym            | Min    | Тур <sup>(1)</sup> | Max     | Units    | Conditions                                                                 |  |  |

| D001          | Supply Voltage                                                                  | VDD            | 3.0    |                    | 5.5     | V        | Fosc = DC to 4 MHz (Commercial/<br>Industrial, Extended)                   |  |  |

| D002          | RAM Data Retention<br>Voltage <sup>(2)</sup>                                    | Vdr            |        | 1.5*               |         | V        | Device in SLEEP mode                                                       |  |  |

| D003          | VDD Start Voltage to ensure<br>Power-on Reset                                   | VPOR           |        | Vss                |         | V        | See section on Power-on Reset for details                                  |  |  |

| D004          | VDD Rise Rate to ensure<br>Power-on Reset                                       | SVDD           | 0.05*  |                    |         | V/ms     | See section on Power-on Reset for details                                  |  |  |

| D010          | Supply Current <sup>(3)</sup>                                                   | IDD            | _      | 0.8                | 1.4     | mA       | XT and EXTRC options (Note 4) FOSC = 4 MHz, VDD = 5.5V                     |  |  |

| D010C         |                                                                                 |                | _      | 0.8                | 1.4     | mA       | INTRC Option<br>Fosc = 4 MHz, VDD = 5.5V                                   |  |  |

| D010A         |                                                                                 |                | _      | 19                 | 27      | μА       | LP OPTION, Commercial Temperature FOSC = 32 kHz, VDD = 3.0V, WDT disabled  |  |  |

|               |                                                                                 |                | _      | 19                 | 35      | μΑ       | LP OPTION, Industrial Temperature FOSC = 32 kHz, VDD = 3.0V, WDT disabled  |  |  |

|               |                                                                                 |                | _      | 30                 | 55      | μA       | LP OPTION, Extended Temperature<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled |  |  |

| D020          | Power-Down Current (5)                                                          | IPD            | _      | 0.25               | 4       | μΑ       | VDD = 3.0V, Commercial WDT disabled                                        |  |  |

| D021<br>D021B |                                                                                 |                | _      | 0.25<br>2          | 5<br>12 | μA<br>μA | VDD = 3.0V, Industrial WDT disabled<br>VDD = 3.0V, Extended WDT disabled   |  |  |

| D022          | Power-Down Current                                                              | $\Delta l$ WDT | _      | 2.2                | 5       | μΑ       | VDD = 3.0V, Commercial                                                     |  |  |

|               |                                                                                 |                | _<br>_ | 2.2<br>4           | 6<br>11 | μA<br>μA | VDD = 3.0V, Industrial<br>VDD = 3.0V, Extended                             |  |  |

|               | Supply Current <sup>(3)</sup> During read/write to EEPROM peripheral            | Δlee           | _      | 0.1                | 0.2     | mA       | FOSC = 4 MHz, Vdd = 5.5V,<br>SCL = 400kHz                                  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

- Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to

Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: Does not include current through Rext. The current through the resistor can be estimated by the formula: IR = VDD/2Rext (mA) with Rext in kOhm.

- 5: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSs.

TABLE 13-1: PULL-UP RESISTOR RANGES\* - PIC12C508A, PIC12C509A, PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Max  | Units |

|-------------|------------------|------|------|------|-------|

|             |                  | GP0  | /GP1 |      |       |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |

|             | 25               | 42K  | 48K  | 63K  | Ω     |

|             | 85               | 42K  | 49K  | 63K  | Ω     |

|             | 125              | 50K  | 55K  | 63K  | Ω     |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |

|             | 25               | 18K  | 20K  | 23K  | Ω     |

|             | 85               | 19K  | 22K  | 25K  | Ω     |

|             | 125              | 22K  | 24K  | 28K  | Ω     |

|             |                  | G    | P3   |      |       |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |

|             | 25               | 343K | 414K | 532K | Ω     |

|             | 85               | 368K | 457K | 532K | Ω     |

|             | 125              | 431K | 504K | 593K | Ω     |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |

|             | 25               | 288K | 341K | 437K | Ω     |

|             | 85               | 306K | 371K | 448K | Ω     |

|             | 125              | 351K | 407K | 500K | Ω     |

<sup>\*</sup> These parameters are characterized but not tested.

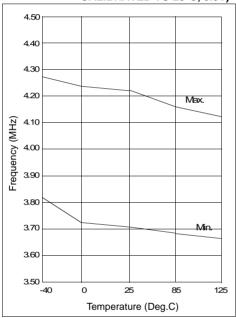

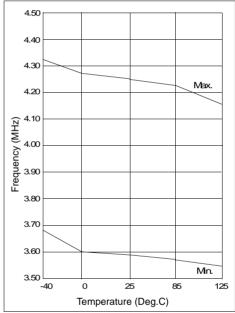

## 14.0 DC AND AC CHARACTERISTICS - PIC12C508A/PIC12C509A/ PIC12LC508A/PIC12LC509A, PIC12CE518/PIC12CE519/PIC12CR509A/ PIC12LCE518/PIC12LCE519/ PIC12LCR509A

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables the data presented are outside specified operating range (e.g., outside specified VDD range). This is for information only and devices will operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean –  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

FIGURE 14-1: CALIBRATED INTERNAL RC FREQUENCY RANGE VS. TEMPERATURE (VDD = 5.0V) (INTERNAL RC IS CALIBRATED TO 25°C, 5.0V)

FIGURE 14-2: CALIBRATED INTERNAL RC FREQUENCY RANGE VS. TEMPERATURE (VDD = 2.5V) (INTERNAL RC IS CALIBRATED TO 25°C, 5.0V)

NOTES: