Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 768B (512 x 12)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | 16 x 8                                                                     |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce518-04-sm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.4 OPTION Register

The OPTION register is a 8-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A RESET sets the OPTION<7:0> bits.

### FIGURE 4-5: OPTION REGISTER

Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin; i.e., note that TRIS overrides OPTION control of GPPU and GPWU.

**Note:** If the TOCS bit is set to '1', GP2 is forced to be an input even if TRIS GP2 = '0'.

| W-1      | W-1                                                  | W-1           | W-1         | W-1          | W-1         | W-1 | W-1  |                                                                                               |

|----------|------------------------------------------------------|---------------|-------------|--------------|-------------|-----|------|-----------------------------------------------------------------------------------------------|

| GPWU     | GPPU                                                 | TOCS          | T0SE        | PSA          | PS2         | PS1 | PS0  | W = Writable bit                                                                              |

| oit7     | 6                                                    | 5             | 4           | 3            | 2           | 1   | bit0 | U = Unimplemented bit<br>- n = Value at POR reset<br>Reference Table 4-1 for<br>other resets. |

| bit 7:   | <b>GPWU</b> : Ena<br>1 = Disable<br>0 = Enable       | d             | p on pin cl | hange (GP    | 0, GP1, GP3 | )   |      |                                                                                               |

| bit 6:   | <b>GPPU</b> : Ena<br>1 = Disable<br>0 = Enablec      | d .           | III-ups (GF | 90, GP1, G   | P3)         |     |      |                                                                                               |

| bit 5:   | <b>TOCS</b> : Time<br>1 = Transitio<br>0 = Transitio | on on TOCK    | l pin       |              | ock, Fosc/4 |     |      |                                                                                               |

| bit 4:   | TOSE: Time<br>1 = Increme<br>0 = Increme             | ent on high t | o low trans | sition on th |             |     |      |                                                                                               |

| bit 3:   | <b>PSA</b> : Presc<br>1 = Prescale<br>0 = Prescale   | er assigned   | to the WD   |              |             |     |      |                                                                                               |

| bit 2-0: | PS2:PS0: P                                           | Prescaler rat | e select bi | its          |             |     |      |                                                                                               |

|          | Bit Value                                            | Timer0 R      | ate WDT     | Rate         |             |     |      |                                                                                               |

|          | 000                                                  | 1:2<br>1:4    | 1:          | 2            |             |     |      |                                                                                               |

|          | 010<br>011                                           | 1:8           | 1:          |              |             |     |      |                                                                                               |

|          | 100                                                  | 1:32          |             | 0<br>16      |             |     |      |                                                                                               |

|          | 101                                                  | 1:64          |             | 32           |             |     |      |                                                                                               |

|          | 110                                                  | 1:128         |             | 64           |             |     |      |                                                                                               |

|          | 111                                                  | 1:256         | : 1.        | 128          |             |     |      |                                                                                               |

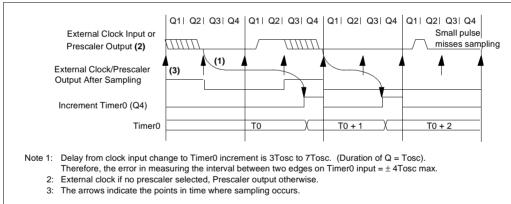

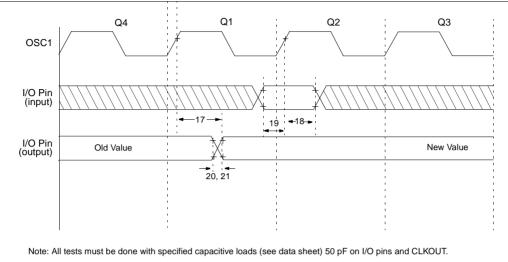

### 6.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

#### 6.1.3 OPTION REGISTER EFFECT ON GP2 TRIS

If the option register is set to read TIMER0 from the pin, the port is forced to an input regardless of the TRIS register setting.

### FIGURE 6-4: TIMER0 TIMING WITH EXTERNAL CLOCK

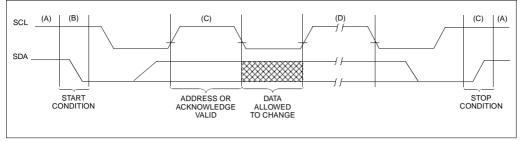

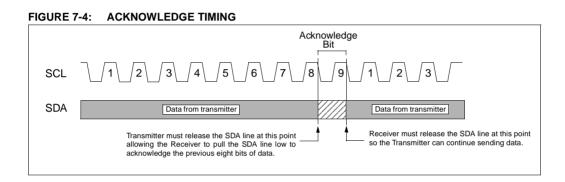

### FIGURE 7-3: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

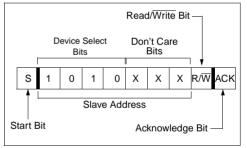

### 7.2 Device Addressing

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed. The slave address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

### FIGURE 7-5: CONTROL BYTE FORMAT

## 7.5 READ OPERATIONS

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

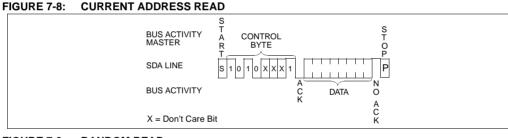

### 7.5.1 CURRENT ADDRESS READ

It contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous read access was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with the R/W bit set to one, the device issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-8).

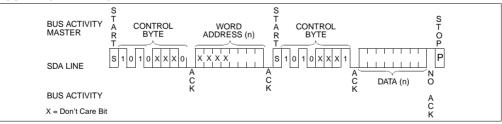

### 7.5.2 RANDOM READ

Random read operations allow the master to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the device as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the  $R/\overline{W}$  bit set to a one. It will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-9). After this command, the internal address counter will point to the address location following the one that was just read.

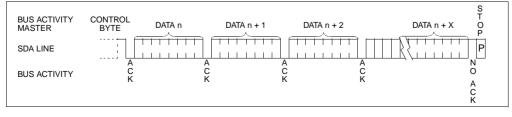

### 7.5.3 SEQUENTIAL READ

Sequential reads are initiated in the same way as a random read except that after the device transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the device to transmit the next sequentially addressed 8-bit word (Figure 7-10).

To provide sequential reads, it contains an internal address pointer which is incremented by one at the completion of each read operation. This address pointer allows the entire memory contents to be serially read during one operation.

#### FIGURE 7-9: RANDOM READ

### FIGURE 7-10: SEQUENTIAL READ

### 8.2 Oscillator Configurations

### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

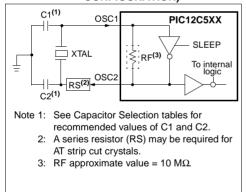

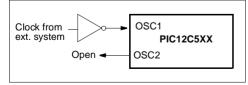

# 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

| BSF              | Bit Set f                                                                                                                    | BTFSS            | Bit Test f, Skip if Set                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------|

| Syntax:          | [label] BSF f,b                                                                                                              | Syntax:          | [label] BTFSS f,b                                                                   |

| Operands:        | $0 \le f \le 31$ $0 \le b \le 7$                                                                                             | Operands:        | $0 \le f \le 31$<br>$0 \le b < 7$                                                   |

| Operation:       | $1 \rightarrow (f < b >)$                                                                                                    | Operation:       | skip if (f <b>) = 1</b>                                                             |

| Status Affected: | None                                                                                                                         | Status Affected: | None                                                                                |

| Encoding:        | 0101 bbbf ffff                                                                                                               | Encoding:        | 0111 bbbf ffff                                                                      |

| Description:     | Bit 'b' in register 'f' is set.                                                                                              | Description:     | If bit 'b' in register 'f' is '1' then the next                                     |

| Words:           | 1                                                                                                                            |                  | instruction is skipped.                                                             |

| Cycles:          | 1                                                                                                                            |                  | If bit 'b' is '1', then the next instruction fetched during the current instruction |

| Example:         | BSF FLAG_REG, 7                                                                                                              |                  | execution, is discarded and an NOP is                                               |

| Before Instru    | uction                                                                                                                       |                  | executed instead, making this a 2 cycle instruction.                                |

| _                | EG = 0x0A                                                                                                                    | Words:           | 1                                                                                   |

| After Instruc    | tion<br>EG = 0x8A                                                                                                            | Cycles:          | 1(2)                                                                                |

| FLAG_K           |                                                                                                                              | Example:         | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CODE                                        |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                    |                  | TRUE •                                                                              |

| Syntax:          | [ label ] BTFSC f,b                                                                                                          |                  | •                                                                                   |

| Operands:        | $0 \le f \le 31$                                                                                                             | Before Instr     | uction                                                                              |

|                  | $0 \le b \le 7$                                                                                                              | PC               | = address (HERE)                                                                    |

| Operation:       | skip if $(f < b >) = 0$                                                                                                      | After Instruc    |                                                                                     |

| Status Affected: | None                                                                                                                         | If FLAG<br>PC    | <1> = 0,<br>= address (FALSE);                                                      |

| Encoding:        | 0110 bbbf ffff                                                                                                               | if FLAG<         | <1> = 1,                                                                            |

| Description:     | If bit 'b' in register 'f' is 0 then the next instruction is skipped.                                                        | PC               | = address (TRUE)                                                                    |

|                  | If bit 'b' is 0 then the next instruction<br>fetched during the current instruction<br>execution is discarded, and an NOP is |                  |                                                                                     |

executed instead, making this a 2 cycle

BTFSC FLAG,1

address (HERE)

address (TRUE);

address(FALSE)

PROCESS\_CODE

GOTO

٠ •

0, =

1, =

instruction.

1

1(2)

HERE

TRUE

Before Instruction PC

After Instruction if FLAG<1>

if FLAG<1>

PC

PC

FALSE

=

=

=

Words:

Cycles:

Example:

| MOVF                 | Move f                                                                                                                                                                                                                               |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:              | [label] MOVF f,d                                                                                                                                                                                                                     |

| Operands:            | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                            |

| Operation:           | $(f) \rightarrow (dest)$                                                                                                                                                                                                             |

| Status Affected:     | Z                                                                                                                                                                                                                                    |

| Encoding:            | 0010 00df ffff                                                                                                                                                                                                                       |

| Description:         | The contents of register 'f' is moved to destination 'd'. If 'd' is 0, destination is the W register. If 'd' is 1, the destination is file register 'f'. 'd' is 1 is useful to test a file register since status flag Z is affected. |

| Words:               | 1                                                                                                                                                                                                                                    |

| Cycles:              | 1                                                                                                                                                                                                                                    |

| Example:             | MOVF FSR, 0                                                                                                                                                                                                                          |

| After Instruc<br>W = | tion<br>value in FSR register                                                                                                                                                                                                        |

| MOVLW                | Move Lit        | eral to W                     | I    |  |

|----------------------|-----------------|-------------------------------|------|--|

| Syntax:              | [ label ]       | MOVLW                         | k    |  |

| Operands:            | $0 \le k \le 2$ | 55                            |      |  |

| Operation:           | $k \to (W)$     |                               |      |  |

| Status Affected:     | None            |                               |      |  |

| Encoding:            | 1100            | kkkk                          | kkkk |  |

| Description:         | 0               | bit literal 'k<br>r. The don' |      |  |

| Words:               | 1               |                               |      |  |

| Cycles:              | 1               |                               |      |  |

| Example:             | MOVLW           | 0x5A                          |      |  |

| After Instruc<br>W = | tion<br>0x5A    |                               |      |  |

| MOVWF                         | Move W                | to f         |            |           |

|-------------------------------|-----------------------|--------------|------------|-----------|

| Syntax:                       | [ label ]             | MOVWF        | f          |           |

| Operands:                     | $0 \le f \le 3^{-1}$  | 1            |            |           |

| Operation:                    | $(W) \to (f$          | )            |            |           |

| Status Affected:              | None                  |              |            |           |

| Encoding:                     | 0000                  | 001f         | ffff       |           |

| Description:                  | Move data<br>ter 'f'. | a from the V | W register | to regis- |

| Words:                        | 1                     |              |            |           |

| Cycles:                       | 1                     |              |            |           |

| Example:                      | MOVWF                 | TEMP_REC     | 3          |           |

| Before Instru<br>TEMP_R<br>W  |                       | 0xFF<br>0x4F |            |           |

| After Instruct<br>TEMP_R<br>W |                       | 0x4F<br>0x4F |            |           |

| NOP              | No Oper   | ration |      |

|------------------|-----------|--------|------|

| Syntax:          | [ label ] | NOP    |      |

| Operands:        | None      |        |      |

| Operation:       | No opera  | ation  |      |

| Status Affected: | None      |        |      |

| Encoding:        | 0000      | 0000   | 0000 |

| Description:     | No opera  | ation. |      |

| Words:           | 1         |        |      |

| Cycles:          | 1         |        |      |

| Example:         | NOP       |        |      |

| OPTION                   | Load OP                 | TION Re | gister |          |

|--------------------------|-------------------------|---------|--------|----------|

| Syntax:                  | [ label ]               | OPTION  | l      |          |

| Operands:                | None                    |         |        |          |

| Operation:               | $(W)\toO$               | PTION   |        |          |

| Status Affected:         | None                    |         |        |          |

| Encoding:                | 0000                    | 0000    | 0010   |          |

| Description:             | The conte<br>into the O |         | 0      | s loaded |

| Words:                   | 1                       |         |        |          |

| Cycles:                  | 1                       |         |        |          |

| Example                  | OPTION                  |         |        |          |

| Before Instru<br>W       | ction<br>= 0x07         |         |        |          |

| After Instruct<br>OPTION |                         |         |        |          |

| RETLW                 | Return with                                                             | Liter            | al in W                                                                         |

|-----------------------|-------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|

| Syntax:               | [label] RE                                                              | TLW              | k                                                                               |

| Operands:             | $0 \le k \le 255$                                                       |                  |                                                                                 |

| Operation:            | $\begin{array}{l} k \rightarrow (W); \\ TOS \rightarrow PC \end{array}$ |                  |                                                                                 |

| Status Affected:      | None                                                                    |                  |                                                                                 |

| Encoding:             | 1000 kł                                                                 | kk               | kkkk                                                                            |

| Description:          | bit literal 'k'. T<br>loaded from th                                    | he pro<br>ne top | aded with the eight<br>gram counter is<br>of the stack (the<br>s is a two cycle |

| Words:                | 1                                                                       |                  |                                                                                 |

| Cycles:               | 2                                                                       |                  |                                                                                 |

| Example:              | CALL TABLE                                                              | ;tab<br>;val     | le offset<br>ue.<br>ow has table                                                |

| TABLE                 | ADDWF PC<br>RETLW k1<br>RETLW k2                                        | ; Beg            | offset<br>in table<br>d of table                                                |

| Before Instru<br>W =  | ox07                                                                    |                  |                                                                                 |

| After Instruct<br>W = | tion<br>value of k8                                                     |                  |                                                                                 |

| RLF                                                                                                                                                | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                            | [label] RLF f,d                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                                                                          | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                               |

| Operation:                                                                                                                                         | See description below                                                                                                                                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                                                                                   | С                                                                                                                                                                                                                                                                                                                                                                                                          |

| Encoding:                                                                                                                                          | 0011 01df ffff                                                                                                                                                                                                                                                                                                                                                                                             |

| Description:                                                                                                                                       | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is stored<br>back in register 'f'.                                                                                                                                                                                                |

| Words:                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                          |

| Cycles:                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                          |

| Example:                                                                                                                                           | RLF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                 |

| Before Instru                                                                                                                                      | iction                                                                                                                                                                                                                                                                                                                                                                                                     |

| REG1<br>C                                                                                                                                          | = 1110 0110<br>= 0                                                                                                                                                                                                                                                                                                                                                                                         |

| After Instruct                                                                                                                                     | tion                                                                                                                                                                                                                                                                                                                                                                                                       |

| REG1<br>W                                                                                                                                          | = 1110 0110<br>= 1100 1100                                                                                                                                                                                                                                                                                                                                                                                 |

| C                                                                                                                                                  | = 1                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRF                                                                                                                                                | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                               |

| RRF<br>Syntax:                                                                                                                                     | Rotate Right f through Carry<br>[ label ] RRF f,d                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |

| Syntax:                                                                                                                                            | [ <i>label</i> ] RRF f,d<br>0 ≤ f ≤ 31                                                                                                                                                                                                                                                                                                                                                                     |

| Syntax:<br>Operands:                                                                                                                               | $\begin{bmatrix} label \end{bmatrix} RRF f,d$<br>$0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                         |

| Syntax:<br>Operands:<br>Operation:                                                                                                                 | $ \begin{bmatrix} label \end{bmatrix} RRF f,d \\ 0 \le f \le 31 \\ d \in [0,1] \\ See description below $                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                                             | $ [label] RRF f,d  0 \le f \le 31  d \in [0,1]  See description below  C  0011 00df ffff  The contents of register 'f' are rotated  one bit to the right through the Carry  Flag. If 'd' is 0 the result is placed in the  W register. If 'd' is 1 the result is placed  back in register 'f'.$                                                                                                            |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                                | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                    |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                      | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>T                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                           | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011  00df  ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>$c \rightarrow register 'f' \rightarrow 1$<br>1                         |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                      | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>T                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                           | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1,0                                                       |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instru-<br>REG1     | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>C register 'f'<br>1<br>1<br>RRF REG1,0<br>interimed<br>= 1110 0110<br>= 0 |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instru<br>REG1<br>C | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1,0<br>interimed<br>= 1110 0110<br>= 0                    |

| SWAPF                       | Swap Nibbles in f                                                                                                                                                     |  |  |  |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                     | [label] SWAPF f,d                                                                                                                                                     |  |  |  |  |  |  |

| Operands:                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                      |  |  |  |  |  |  |

| Operation:                  | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                             |  |  |  |  |  |  |

| Status Affected:            | None                                                                                                                                                                  |  |  |  |  |  |  |

| Encoding:                   | 0011 10df ffff                                                                                                                                                        |  |  |  |  |  |  |

| Description:                | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |  |  |  |  |  |  |

| Words:                      | 1                                                                                                                                                                     |  |  |  |  |  |  |

| Cycles:                     | 1                                                                                                                                                                     |  |  |  |  |  |  |

| Example                     | SWAPF REG1, 0                                                                                                                                                         |  |  |  |  |  |  |

| Before Instru<br>REG1       | iction<br>= 0xA5                                                                                                                                                      |  |  |  |  |  |  |

| After Instruct<br>REG1<br>W |                                                                                                                                                                       |  |  |  |  |  |  |

| TRIS                             | Load TRIS Register                                                          |  |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                          | [label] TRIS f                                                              |  |  |  |  |  |

| Operands:                        | f = 6                                                                       |  |  |  |  |  |

| Operation:                       | $(W) \to TRIS \text{ register f}$                                           |  |  |  |  |  |

| Status Affected:                 | None                                                                        |  |  |  |  |  |

| Encoding:                        | 0000 0000 0fff                                                              |  |  |  |  |  |

| Description:                     | TRIS register 'f' ( $f = 6$ ) is loaded with the contents of the W register |  |  |  |  |  |

| Words:                           | 1                                                                           |  |  |  |  |  |

| Cycles:                          | 1                                                                           |  |  |  |  |  |

| Example                          | TRIS GPIO                                                                   |  |  |  |  |  |

| Before Instruction<br>W = 0XA5   |                                                                             |  |  |  |  |  |

| After Instruction<br>TRIS = 0XA5 |                                                                             |  |  |  |  |  |

| <b>Note:</b> f = 6 f             | or PIC12C5XX only.                                                          |  |  |  |  |  |

| XORLW                | RLW Exclusive OR literal with W                                                                                         |                   |      |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------|------|--|--|--|--|--|--|

| Syntax:              | [ <i>label</i> ]                                                                                                        | XORLW             | k    |  |  |  |  |  |  |

| Operands:            | $0 \le k \le 2$                                                                                                         | $0 \le k \le 255$ |      |  |  |  |  |  |  |

| Operation:           | (W) .XO                                                                                                                 | $R. k \to (W$     | /)   |  |  |  |  |  |  |

| Status Affected:     | Z                                                                                                                       |                   |      |  |  |  |  |  |  |

| Encoding:            | 1111                                                                                                                    | kkkk              | kkkk |  |  |  |  |  |  |

| Description:         | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                   |      |  |  |  |  |  |  |

| Words:               | 1                                                                                                                       |                   |      |  |  |  |  |  |  |

| Cycles:              | 1                                                                                                                       |                   |      |  |  |  |  |  |  |

| Example:             | XORLW                                                                                                                   | 0xAF              |      |  |  |  |  |  |  |

| Before Instru<br>W = | uction<br>0xB5                                                                                                          |                   |      |  |  |  |  |  |  |

| After Instruc<br>W = | tion<br>0x1A                                                                                                            |                   |      |  |  |  |  |  |  |

| XORWF                                              | Exclusive OR W with f                                                                                                                                                              |  |  |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                            | [label] XORWF f,d                                                                                                                                                                  |  |  |  |  |  |  |

| Operands:                                          | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                   |  |  |  |  |  |  |

| Operation:                                         | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected:                                   | Z                                                                                                                                                                                  |  |  |  |  |  |  |

| Encoding:                                          | 0001 10df ffff                                                                                                                                                                     |  |  |  |  |  |  |

| Description:                                       | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |  |  |  |  |  |  |

| Words:                                             | 1                                                                                                                                                                                  |  |  |  |  |  |  |

| Cycles:                                            | 1                                                                                                                                                                                  |  |  |  |  |  |  |

| Example                                            | XORWF REG,1                                                                                                                                                                        |  |  |  |  |  |  |

| Before Instru<br>REG<br>W<br>After Instruct<br>REG | = 0xAF<br>= 0xB5<br>ion<br>= 0x1A                                                                                                                                                  |  |  |  |  |  |  |

| W                                                  | = 0xB5                                                                                                                                                                             |  |  |  |  |  |  |

# 11.0 ELECTRICAL CHARACTERISTICS - PIC12C508/PIC12C509

## Absolute Maximum Ratings†

| Ambient Temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40°C to +125°C                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65°C to +150°C                     |

| Voltage on VDD with respect to VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 to +7.5 V                        |

| Voltage on MCLR with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 to +14 V                         |

| Voltage on all other pins with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | –0.6 V to (VDD + 0.6 V)            |