Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 768B (512 x 12)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 16 x 8                                                                      |

| RAM Size                   | 25 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 8-SOIJ                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce518-04i-sm |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

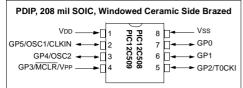

### Pin Diagram - PIC12C508/509

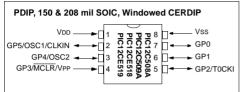

### Pin Diagram - PIC12C508A/509A, PIC12CE518/519

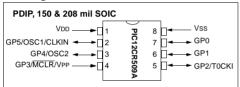

### Pin Diagram - PIC12CR509A

### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

|             |                                               | PIC12C508(A)           | PIC12C509(A)           | PIC12CR509A        | PIC12CE518             | PIC12CE519             | PIC12C671              | PIC12C672              | PIC12CE673       | PIC12CE674       |

|-------------|-----------------------------------------------|------------------------|------------------------|--------------------|------------------------|------------------------|------------------------|------------------------|------------------|------------------|

| Clock       | Maximum<br>Frequency<br>of Operation<br>(MHz) | 4                      | 4                      | 4                  | 4                      | 4                      | 10                     | 10                     | 10               | 10               |

| Memory      | EPROM<br>Program<br>Memory                    | 512 x 12               | 1024 x 12              | 1024 x 12<br>(ROM) | 512 x 12               | 1024 x 12              | 1024 x 14              | 2048 x 14              | 1024 x 14        | 2048 x 14        |

| wemory      | RAM Data<br>Memory<br>(bytes)                 | 25                     | 41                     | 41                 | 25                     | 41                     | 128                    | 128                    | 128              | 128              |

|             | EEPROM<br>Data Memory<br>(bytes)              | —                      | -                      | —                  | 16                     | 16                     | —                      | —                      | 16               | 16               |

| Peripherals | Timer<br>Module(s)                            | TMR0                   | TMR0                   | TMR0               | TMR0                   | TMR0                   | TMR0                   | TMR0                   | TMR0             | TMR0             |

|             | A/D Con-<br>verter (8-bit)<br>Channels        | —                      | _                      | —                  | —                      | —                      | 4                      | 4                      | 4                | 4                |

|             | Wake-up<br>from SLEEP<br>on pin<br>change     | Yes                    | Yes                    | Yes                | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | Interrupt<br>Sources                          | —                      | -                      | _                  |                        |                        | 4                      | 4                      | 4                | 4                |

| Features    | I/O Pins                                      | 5                      | 5                      | 5                  | 5                      | 5                      | 5                      | 5                      | 5                | 5                |

|             | Input Pins                                    | 1                      | 1                      | 1                  | 1                      | 1                      | 1                      | 1                      | 1                | 1                |

|             | Internal<br>Pull-ups                          | Yes                    | Yes                    | Yes                | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | In-Circuit<br>Serial<br>Programming           | Yes                    | Yes                    | —                  | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | Number of<br>Instructions                     | 33                     | 33                     | 33                 | 33                     | 33                     | 35                     | 35                     | 35               | 35               |

|             | Packages                                      | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW | 8-pin DIP,<br>JW |

### TABLE 1-1: PIC12CXXX & PIC12CEXXX FAMILY OF DEVICES

All PIC12CXXX & PIC12CEXXX devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability.

All PIC12CXXX & PIC12CEXXX devices use serial programming with data pin GP0 and clock pin GP1.

NOTES:

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12C5XX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C5XX uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12-bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (1µs @ 4MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), ROM memory, and non-volatile (EEPROM) for each device.

|             | Memory           |                |             |                |  |

|-------------|------------------|----------------|-------------|----------------|--|

| Device      | EPROM<br>Program | ROM<br>Program | RAM<br>Data | EEPROM<br>Data |  |

| PIC12C508   | 512 x 12         |                | 25          |                |  |

| PIC12C509   | 1024 x 12        |                | 41          |                |  |

| PIC12C508A  | 512 x 12         |                | 25          |                |  |

| PIC12C509A  | 1024 x 12        |                | 41          |                |  |

| PIC12CR509A |                  | 1024 x 12      | 41          |                |  |

| PIC12CE518  | 512 x 12         |                | 25 x 8      | 16 x 8         |  |

| PIC12CE519  | 1024 x 12        |                | 41 x 8      | 16 x 8         |  |

The PIC12C5XX can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC12C5XX has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C5XX simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC12C5XX device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1.

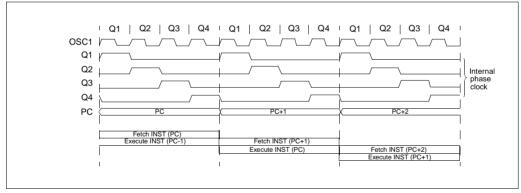

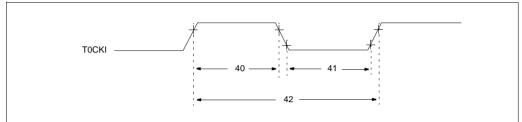

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

### 3.2 Instruction Flow/Pipelining

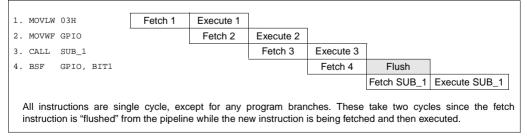

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.2 Data Memory Organization

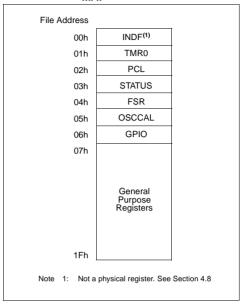

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: special function registers and general purpose registers.

The special function registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports), and the File Select Register (FSR). In addition, special purpose registers are used to control the I/O port configuration and prescaler options.

The general purpose registers are used for data and control information under command of the instructions.

For the PIC12C508, PIC12C508A and PIC12CE518, the register file is composed of 7 special function registers and 25 general purpose registers (Figure 4-2).

For the PIC12C509, PIC12C509A, PIC12CR509A, and PIC12CE519 the register file is composed of 7 special function registers, 25 general purpose registers, and 16 general purpose registers that may be addressed using a banking scheme (Figure 4-3).

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The general purpose register file is accessed either directly or indirectly through the file select register FSR (Section 4.8).

#### FIGURE 4-2: PIC12C508, PIC12C508A AND PIC12CE518 REGISTER FILE MAP

| FSR<6:5>-    | •    | 00                  | 01                       |

|--------------|------|---------------------|--------------------------|

| File Address | · ·  |                     | 1                        |

| 00h          |      | INDF <sup>(1)</sup> | 20h                      |

| <b>∲</b> 01h |      | TMR0                |                          |

| 02h          |      | PCL                 | _                        |

| 03h          |      | STATUS              | Addresses map<br>back to |

| 04h          |      | FSR                 | addresses                |

| 05h          |      | OSCCAL              | in Bank 0.               |

| 06h          |      | GPIO                |                          |

| 07h          |      |                     | 1                        |

|              |      | General<br>Purpose  |                          |

|              |      | Registers           |                          |

| 0Fh          |      | 0                   | 2Fh                      |

|              | 10h  |                     | 30h                      |

|              |      | General             | General                  |

|              |      | Purpose             | Purpose                  |

|              |      | Registers           | Registers                |

|              | 1Fh  |                     | 3Fh                      |

|              |      | Bank 0              | Bank 1                   |

| Note 1       | : No | t a physical regi   | ster. See Section 4.8    |

|              |      |                     |                          |

### FIGURE 4-3: PIC12C509, PIC12C509A, PIC12CR509A AND PIC12CE519 REGISTER FILE MAP

### 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

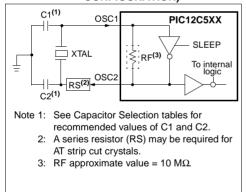

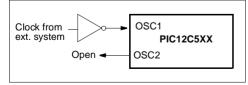

### 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

#### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

| ADDWF                                                           | Add W and f                                                                                                                                                       |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                         | [label] ADDWF f,d                                                                                                                                                 |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                       |

| Operation:                                                      | (W) + (f) $\rightarrow$ (dest)                                                                                                                                    |

| Status Affected:                                                | C, DC, Z                                                                                                                                                          |

| Encoding:                                                       | 0001 11df ffff                                                                                                                                                    |

| Description:                                                    | Add the contents of the W register and register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. |

| Words:                                                          | 1                                                                                                                                                                 |

| Cycles:                                                         | 1                                                                                                                                                                 |

| Example:                                                        | ADDWF FSR, 0                                                                                                                                                      |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>tion<br>0xD9                                                                                                                                      |

| ANDWF                          | AND W with f                                                                                                                                                                       |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] ANDWF f,d                                                                                                                                                                  |

| Operands:                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                                        |

| Operation:                     | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                 |

| Status Affected:               | Z                                                                                                                                                                                  |

| Encoding:                      | 0001 01df ffff                                                                                                                                                                     |

| Description:                   | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>'1' the result is stored back in register 'f'. |

| Words:                         | 1                                                                                                                                                                                  |

| Cycles:                        | 1                                                                                                                                                                                  |

| Example:                       | ANDWF FSR, 1                                                                                                                                                                       |

| Before Instru<br>W =<br>FSR =  | 0x17                                                                                                                                                                               |

| After Instruct<br>W =<br>FSR = | 0x17                                                                                                                                                                               |

| ANDLW                 | And literal with W                                                                                                      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:               | [label] ANDLW k                                                                                                         |

| Operands:             | $0 \le k \le 255$                                                                                                       |

| Operation:            | (W).AND. (k) $\rightarrow$ (W)                                                                                          |

| Status Affected:      | Z                                                                                                                       |

| Encoding:             | 1110 kkkk kkkk                                                                                                          |

| Description:          | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'. The<br>result is placed in the W register. |

| Words:                | 1                                                                                                                       |

| Cycles:               | 1                                                                                                                       |

| Example:              | ANDLW 0x5F                                                                                                              |

| Before Instru<br>W =  | iction<br>0xA3                                                                                                          |

| After Instruct<br>W = | tion<br>0x03                                                                                                            |

| BCF                                   | Bit Clear                                                          | f        |      |  |

|---------------------------------------|--------------------------------------------------------------------|----------|------|--|

| Syntax:                               | [ <i>label</i> ] E                                                 | BCF f,b  | )    |  |

| Operands:                             | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |          |      |  |

| Operation:                            | $0 \rightarrow (f < b;$                                            | >)       |      |  |

| Status Affected:                      | None                                                               |          |      |  |

| Encoding:                             | 0100                                                               | bbbf     | ffff |  |

| Description:                          | Bit 'b' in register 'f' is cleared.                                |          |      |  |

| Words:                                | 1                                                                  |          |      |  |

| Cycles:                               | 1                                                                  |          |      |  |

| Example:                              | BCF                                                                | FLAG_REC | 3, 7 |  |

| Before Instruction<br>FLAG_REG = 0xC7 |                                                                    |          |      |  |

| After Instruction<br>FLAG_REG = 0x47  |                                                                    |          |      |  |

| CALL                  | Subroutine Call                                                                                                                                                                                                                                |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:               | [ <i>label</i> ] CALL k                                                                                                                                                                                                                        |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                                                                              |  |  |

| Operation:            | $\begin{array}{l} (\text{PC}) + 1 \rightarrow \text{Top of Stack}; \\ k \rightarrow \text{PC<7:0>}; \\ (\text{STATUS<6:5>}) \rightarrow \text{PC<10:9>}; \\ 0 \rightarrow \text{PC<8>} \end{array}$                                            |  |  |

| Status Affected:      | None                                                                                                                                                                                                                                           |  |  |

| Encoding:             | 1001 kkkk kkkk                                                                                                                                                                                                                                 |  |  |

| Description:          | Subroutine call. First, return address (PC+1) is pushed onto the stack. The eight bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STA-TUS<6:5>, PC<8> is cleared. CALL is a two cycle instruction. |  |  |

| Words:                | 1                                                                                                                                                                                                                                              |  |  |

| Cycles:               | 2                                                                                                                                                                                                                                              |  |  |

| Example:              | HERE CALL THERE                                                                                                                                                                                                                                |  |  |

| Before Instru<br>PC = |                                                                                                                                                                                                                                                |  |  |

|                       | tion<br>address (THERE)<br>address (HERE + 1)                                                                                                                                                                                                  |  |  |

### CLRF

| Syntax:                        | [label] CLRF f                                                         |           |   |  |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------|-----------|---|--|--|--|--|--|

| Operands:                      | $0 \le f \le 31$                                                       |           |   |  |  |  |  |  |

| Operation:                     | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |           |   |  |  |  |  |  |

| Status Affected: Z             |                                                                        |           |   |  |  |  |  |  |

| Encoding: 0000 011f ffff       |                                                                        |           |   |  |  |  |  |  |

| Description:                   | The contents of register 'f' are cleared and the Z bit is set.         |           |   |  |  |  |  |  |

| Words:                         | 1                                                                      |           |   |  |  |  |  |  |

| Cycles:                        | 1                                                                      |           |   |  |  |  |  |  |

| Example:                       | CLRF                                                                   | FLAG_REC  | 3 |  |  |  |  |  |

| Before Instru<br>FLAG_RE       |                                                                        | 0x5A      |   |  |  |  |  |  |

| After Instruct<br>FLAG_RE<br>Z |                                                                        | 0x00<br>1 |   |  |  |  |  |  |

Clear f

| CLRW                                                                                                     | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                                  | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operation:                                                                                               | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:                                                                                                | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:                                                                                             | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Example:                                                                                                 | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Before Instru<br>W =                                                                                     | uction<br>0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| After Instruct<br>W =<br>Z =                                                                             | tion<br>0x00<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| CLRWDT<br>Syntax:                                                                                        | Clear Watchdog Timer<br>[label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| -                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Syntax:                                                                                                  | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                     | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |