Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 5                                                                            |

| Program Memory Size        | 768B (512 x 12)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | 16 × 8                                                                       |

| RAM Size                   | 25 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                                |

| Supplier Device Package    | 8-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce518t-04i-sn |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

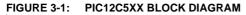

## 2.0 PIC12C5XX DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12C5XX Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in ceramic side brazed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

Microchip's PICSTART<sup>®</sup> PLUS and PRO MATE<sup>®</sup> programmers all support programming of the PIC12C5XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

## 2.5 Read Only Memory (ROM) Device

Microchip offers masked ROM to give the customer a low cost option for high volume, mature products.

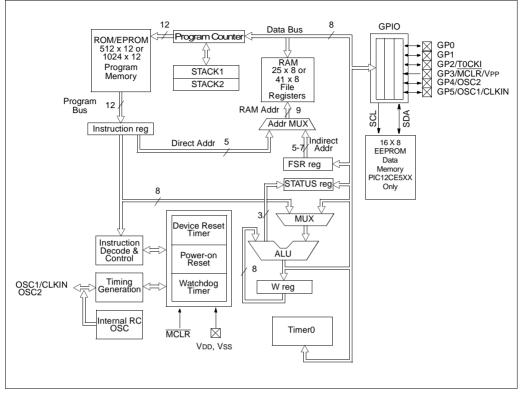

## 5.0 I/O PORT

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

## 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the output data latches. That is, if an output      |

|-------|---------------------------------------------------------------------------------------------|

|       | driver on a pin is enabled and driven high,                                                 |

|       | but the external system is holding it low, a read of the port will indicate that the pin is |

|       | low.                                                                                        |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

## 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

### FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

## FIGURE 5-2: SUCCESSIVE I/O OPERATION

| PC         | Y PC + 1                         | X PC + 2                                                                         | X PC + 3                                                                                | This example shows a write to GPIO follower                                                                 |

|------------|----------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| MOVWF GPIO | MOVF GPIO,W                      | NOP                                                                              | NOP                                                                                     | by a read from GPIO.<br>Data setup time = (0.25 Tcy – TpD)                                                  |

|            | 1<br>1<br>1                      | X                                                                                | 1                                                                                       | where: TCY = instruction cycle.<br>TPD = propagation delay                                                  |

|            | Port pin<br>written here         | Port pin<br>sampled here                                                         | ,<br>,<br>,<br>,                                                                        | Therefore, at higher clock frequencies, a write followed by a read may be problematic                       |

|            | MOVWF GPIO<br>(Write to<br>GPIO) | MOVF GPIO,W<br>(Read<br>GPIO)                                                    | NOP                                                                                     |                                                                                                             |

|            |                                  | MOVWF GPIO<br>MOVF GPIO,W<br>Port pin<br>written here<br>MOVWF GPIO<br>(Write to | MOVWF GPIO MOVF GPIO,W NOP Port pin written here MOVWF GPIO MOVF GPIO,W (Write to (Read | MOVWF GPIO MOVF GPIO,W NOP NOP<br>Port pin<br>written here<br>MOVWF GPIO MOVF GPIO,W NOP<br>(Write to (Read |

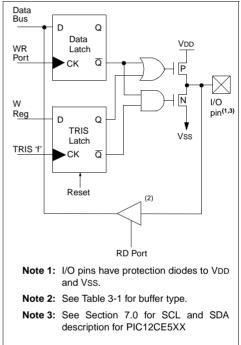

## 7.0 EEPROM PERIPHERAL OPERATION

## This section applies to PIC12CE518 and PIC12CE519 only.

The PIC12CE518 and PIC12CE519 each have 16 bytes of EEPROM data memory. The EEPROM memory has an endurance of 1,000,000 erase/write cycles and a data retention of greater than 40 years. The EEPROM data memory supports a bi-directional 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), that are mapped to bit6 and bit7, respectively, of the GPIO register (SFR 06h). Unlike the GP0-GP5 that are connected to the internal EEPROM peripheral. For most applications, all that is required is calls to the following functions:

; Byte\_Write: Byte write routine Inputs: EEPROM Address EEADDR : ; EEPROM Data EEDATA Outputs: Return 01 in W if OK, else ; return 00 in W ; ; Read\_Current: Read EEPROM at address currently held by EE device. Inputs: NONE ; Outputs: EEPROM Data EEDATA ; Return 01 in W if OK, else ; return 00 in W ; ; Read\_Random: Read EEPROM byte at supplied address Inputs: EEPROM Address : FFADDR ; Outputs: EEPROM Data EEDATA Return 01 in W if OK, ; else return 00 in W

The code for these functions is available on our website www.microchip.com. The code will be accessed by either including the source code FL51XINC.ASM or by linking FLASH5IX.ASM.

It is very important to check the return codes when using these calls, and retry the operation if unsuccessful. Unsuccessful return codes occur when the EE data memory is busy with the previous write, which can take up to 4 mS.

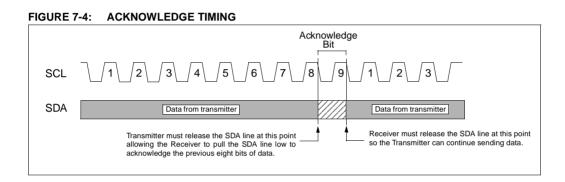

#### 7.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the device.

For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

The EEPROM interface is a 2-wire bus protocol consisting of data (SDA) and a clock (SCL). Although these lines are mapped into the GPIO register, they are not accessible as external pins; only to the internal EEPROM peripheral. SDA and SCL operation is also slightly different than GPO-GP5 as listed below. Namely, to avoid code overhead in modifying the TRIS register, both SDA and SCL are always outputs. To read data from the EEPROM peripheral requires outputting a '1' on SDA placing it in high-Z state, where only the internal 100K pull-up is active on the SDA line.

SDA:

Built-in 100K (typical) pull-up to VDD Open-drain (pull-down only) Always an output Outputs a '1' on reset

SCL: Full CMOS output Always an output Outputs a '1' on reset

The following example requires:

- · Code Space: 77 words

- RAM Space: 5 bytes (4 are overlayable)

- Stack Levels:1 (The call to the function itself. The functions do not call any lower level functions.)

- Timing:

- WRITE\_BYTE takes 328 cycles

- READ\_CURRENT takes 212 cycles

- READ\_RANDOM takes 416 cycles.

- IO Pins: 0 (No external IO pins are used)

This code must reside in the lower half of a page. The code achieves it's small size without additional calls through the use of a sequencing table. The table is a list of procedures that must be called in order. The table uses an ADDWF PCL,F instruction, effectively a computed goto, to sequence to the next procedure. However the ADDWF PCL,F instruction yields an 8 bit address, forcing the code to reside in the first 256 addresses of a page.

<sup>© 1999</sup> Microchip Technology Inc.

## FIGURE 7-3: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

## 7.2 Device Addressing

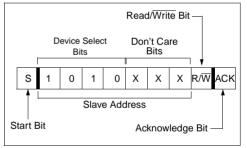

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed. The slave address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

#### FIGURE 7-5: CONTROL BYTE FORMAT

#### 7.3 WRITE OPERATIONS

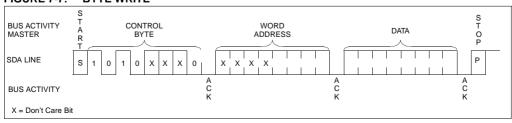

#### 7.3.1 BYTE WRITE

Following the start signal from the master, the device code (4 bits), the don't care bits (3 bits), and the R/Wbit (which is a logic low) are placed onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the master is the word address and will be written into the address pointer. Only the lower four address bits are used by the device, and the upper four bits are don't cares. The address byte is acknowledgeable and the master device will then transmit the data word to be written into the addressed memory location. The memorv acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time will not generate acknowledge signals (Figure 7-7). After a byte write command, the internal address counter will not be incremented and will point to the same address location that was just written. If a stop bit is transmitted to the device at any point in the write command sequence before the entire sequence is complete, then the command will abort and no data will be written. If more than 8 data bits are transmitted before the stop bit is sent, then the device will clear the previously loaded byte and begin loading the data buffer again. If more than one data byte is transmitted to the device and a stop bit is sent before a full eight data bits have been transmitted, then the write command will abort and no data will be written. The EEPROM memory employs a Vcc threshold detector circuit which disables the internal erase/write logic if the Vcc is below minimum VDD.

Byte write operations must be preceded and immediately followed by a bus not busy bus cycle where both SDA and SCL are held high.

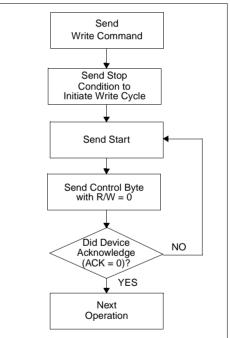

#### 7.4 ACKNOWLEDGE POLLING

Since the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the master, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master sending a start condition followed by the control byte for a write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-6 for flow diagram.

#### FIGURE 7-6: ACKNOWLEDGE POLLING FLOW

FIGURE 7-7: BYTE WRITE

## 7.5 READ OPERATIONS

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

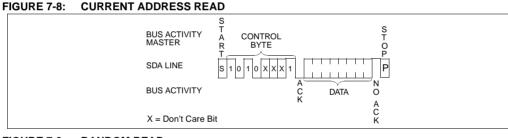

#### 7.5.1 CURRENT ADDRESS READ

It contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous read access was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with the R/W bit set to one, the device issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-8).

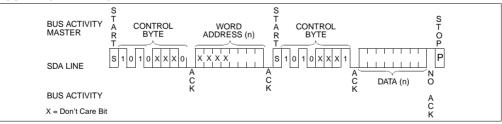

#### 7.5.2 RANDOM READ

Random read operations allow the master to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the device as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the  $R/\overline{W}$  bit set to a one. It will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission (Figure 7-9). After this command, the internal address counter will point to the address location following the one that was just read.

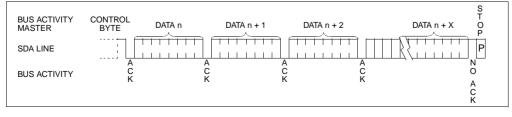

#### 7.5.3 SEQUENTIAL READ

Sequential reads are initiated in the same way as a random read except that after the device transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the device to transmit the next sequentially addressed 8-bit word (Figure 7-10).

To provide sequential reads, it contains an internal address pointer which is incremented by one at the completion of each read operation. This address pointer allows the entire memory contents to be serially read during one operation.

#### FIGURE 7-9: RANDOM READ

#### FIGURE 7-10: SEQUENTIAL READ

#### 8.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and 25°C, see "Electrical Specifications" section for information on variation over voltage and temperature.

In addition, a calibration instruction is programmed into the top of memory which contains the calibration value for the internal RC oscillator. This location is never code protected regardless of the code protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the reset vector. This will load the W register with the calibration value upon reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part. so it can be reprogrammed correctly later.

For the PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, and PIC12CR509A, bits <7:2>, CAL5-CAL0 are used for calibration. Adjusting CAL5-0 from 000000 to 111111 yields a higher clock speed. Note that bits 1 and 0 of OSCCAL are unimplemented and should be written as 0 when modifying OSCCAL for compatibility with future devices.

For the PIC12C508 and PIC12C509, the upper 4 bits of the register are used. Writing a larger value in this location yields a higher clock speed.

#### 8.3 <u>RESET</u>

The device differentiates between various kinds of reset:

- a) Power on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT time-out reset during normal operation

- e) WDT time-out reset during SLEEP

- f) Wake-up from SLEEP on pin change

Some registers are not reset in any way; they are unknown on POR and unchanged in any other reset. Most other registers are reset to "reset state" on poweron reset (POR),  $\overline{MCLR}$ , WDT or wake-up on pin change reset during normal operation. They are not affected by a WDT reset during SLEEP or  $\overline{MCLR}$  reset during SLEEP, since these resets are viewed as resumption of normal operation. The exceptions to this are  $\overline{TO}$ ,  $\overline{PD}$ , and GPWUF bits. They are set or cleared differently in different reset situations. These bits are used in software to determine the nature of reset. See Table 8-3 for a full description of reset states of all registers.

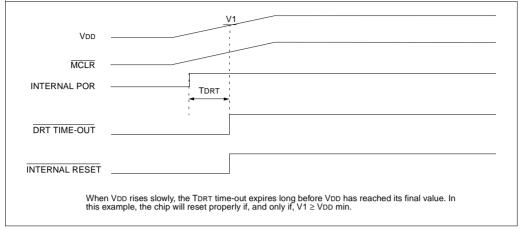

#### FIGURE 8-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### 8.5 Device Reset Timer (DRT)

In the PIC12C5XX, DRT runs from RESET and varies based on oscillator selection (see Table 8-5.)

The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min., and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after MCLR has reached a logic high (VIHMCLR) level. Thus, programming GP3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the GP3/MCLR/VPP pin as a general purpose input.

The Device Reset time delay will vary from chip to chip due to VDD, temperature, and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake from SLEEP mode automatically.

#### 8.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the external RC oscillator of the GP5/OSC1/CLKIN pin and the internal 4 MHz oscillator. That means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT reset or wake-up reset generates a device RESET.

The  $\overline{TO}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer reset.

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 8.1). Refer to the PIC12C5XX Programming Specifications to determine how to access the configuration word.

TABLE 8-5: DRT (DEVICE RESET TIMER PERIOD)

| Oscillator<br>Configuration | POR Reset       | Subsequent<br>Resets |

|-----------------------------|-----------------|----------------------|

| IntRC &<br>ExtRC            | 18 ms (typical) | 300 µs (typical)     |

| XT & LP                     | 18 ms (typical) | 18 ms (typical)      |

| COMF                       | Complement f                                                                                                                                                         |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                    | [ label ] COMF f,d                                                                                                                                                   |  |  |  |

| Operands:                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                            |  |  |  |

| Operation:                 | $(\overline{f}) \rightarrow (dest)$                                                                                                                                  |  |  |  |

| Status Affected:           | Z                                                                                                                                                                    |  |  |  |

| Encoding:                  | 0010 01df ffff                                                                                                                                                       |  |  |  |

| Description:               | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |  |  |  |

| Words:                     | 1                                                                                                                                                                    |  |  |  |

| Cycles:                    | 1                                                                                                                                                                    |  |  |  |

| Example:                   | COMF REG1,0                                                                                                                                                          |  |  |  |

| Before Instru<br>REG1      | uction<br>= 0x13                                                                                                                                                     |  |  |  |

| After Instruc<br>REG1<br>W | xtion<br>= 0x13<br>= 0xEC                                                                                                                                            |  |  |  |

| DECF                                                   | Decrement f                                                                                                                              |  |  |  |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                | [label] DECF f,d                                                                                                                         |  |  |  |

| Operands:                                              | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                |  |  |  |

| Operation:                                             | $(f) - 1 \rightarrow (dest)$                                                                                                             |  |  |  |

| Status Affected:                                       | Z                                                                                                                                        |  |  |  |

| Encoding:                                              | 0000 11df ffff                                                                                                                           |  |  |  |

| Description:                                           | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |  |  |  |

| Words:                                                 | 1                                                                                                                                        |  |  |  |

| Cycles:                                                | 1                                                                                                                                        |  |  |  |

| Example:                                               | DECF CNT, 1                                                                                                                              |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruc<br>CNT<br>Z | = 0x01<br>= 0                                                                                                                            |  |  |  |

| DECFSZ                                               | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                              | [label] DECFSZ f.d                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Operands:                                            | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                    |  |  |  |

| Operation:                                           | (f) $-1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                                          |  |  |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Encoding:                                            | 0010 11df ffff                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Description:                                         | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded<br>and an NOP is executed instead mak-<br>ing it a two cycle instruction. |  |  |  |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Cycles:                                              | 1(2)                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Example:                                             | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •                                                                                                                                                                                                                                                                                        |  |  |  |

| Before Instru                                        | iction                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PC                                                   | = address (HERE)                                                                                                                                                                                                                                                                                                                     |  |  |  |

| After Instruc<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                                                                                                                                                                    |  |  |  |

| GOTO                                                 | Unconditional Branch                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Syntax:                                              | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                              |  |  |  |

| -                                                    | · · · · · ·                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Syntax:                | [ <i>label</i> ] GOTO k                                                                                                                                                                 |         |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|

| Operands:              | $0 \le k \le 511$                                                                                                                                                                       |         |  |  |  |

| Operation:             | $k \rightarrow PC < 8:0>;$<br>STATUS<6:5> $\rightarrow PC < 10:9>$                                                                                                                      |         |  |  |  |

| Status Affected:       | None                                                                                                                                                                                    |         |  |  |  |

| Encoding:              | 101k kkkk kkkk                                                                                                                                                                          |         |  |  |  |

| Description:           | GOTO is an unconditional branch. The<br>9-bit immediate value is loaded into PC<br>bits <8:0>. The upper bits of PC are<br>loaded from STATUS<6:5>. GOTO is a<br>two cycle instruction. |         |  |  |  |

| Words:                 | 1                                                                                                                                                                                       |         |  |  |  |

| Cycles:                | 2                                                                                                                                                                                       |         |  |  |  |

| Example:               | GOTO THERE                                                                                                                                                                              |         |  |  |  |

| After Instruct<br>PC = | ion<br>address                                                                                                                                                                          | (THERE) |  |  |  |

| OPTION                   | Load OP                                                           | TION Re                  | gister |  |  |

|--------------------------|-------------------------------------------------------------------|--------------------------|--------|--|--|

| Syntax:                  | [ label ]                                                         | OPTION                   | l      |  |  |

| Operands:                | None                                                              |                          |        |  |  |

| Operation:               | $(W)\toO$                                                         | $(W) \rightarrow OPTION$ |        |  |  |

| Status Affected:         | None                                                              |                          |        |  |  |

| Encoding:                | 0000                                                              | 0000                     | 0010   |  |  |

| Description:             | The content of the W register is loaded into the OPTION register. |                          |        |  |  |

| Words:                   | 1                                                                 |                          |        |  |  |

| Cycles:                  | 1                                                                 |                          |        |  |  |

| Example OPTION           |                                                                   |                          |        |  |  |

| Before Instru<br>W       | ction<br>= 0x07                                                   |                          |        |  |  |

| After Instruct<br>OPTION |                                                                   |                          |        |  |  |

| RETLW                 | Return with                                                             | Liter            | al in W                                                                         |  |

|-----------------------|-------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|--|

| Syntax:               | [ <i>label</i> ] RETLW k                                                |                  |                                                                                 |  |

| Operands:             | 0 ≤ k ≤ 255                                                             |                  |                                                                                 |  |

| Operation:            | $\begin{array}{l} k \rightarrow (W); \\ TOS \rightarrow PC \end{array}$ |                  |                                                                                 |  |

| Status Affected:      | None                                                                    |                  |                                                                                 |  |

| Encoding:             | 1000 kł                                                                 | kk               | kkkk                                                                            |  |

| Description:          | bit literal 'k'. T<br>loaded from th                                    | he pro<br>ne top | aded with the eight<br>gram counter is<br>of the stack (the<br>s is a two cycle |  |

| Words:                | 1                                                                       |                  |                                                                                 |  |

| Cycles:               | 2                                                                       |                  |                                                                                 |  |

| Example:              | CALL TABLE                                                              | ;tab<br>;val     | le offset<br>ue.<br>ow has table                                                |  |

| TABLE                 | ADDWF PC<br>RETLW k1<br>RETLW k2                                        | ; Beg            | offset<br>in table<br>d of table                                                |  |

| Before Instru<br>W =  | ox07                                                                    |                  |                                                                                 |  |

| After Instruct<br>W = | tion<br>value of k8                                                     |                  |                                                                                 |  |

| RLF                                                                                                                                                | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                                                                                                            | [label] RLF f,d                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Operands:                                                                                                                                          | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Operation:                                                                                                                                         | See description below                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Status Affected:                                                                                                                                   | С                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Encoding:                                                                                                                                          | 0011 01df ffff                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Description:                                                                                                                                       | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is stored<br>back in register 'f'.                                                                                                                                                                                                |  |  |  |  |

| Words:                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Cycles:                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Example:                                                                                                                                           | RLF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Before Instru                                                                                                                                      | iction                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| REG1<br>C                                                                                                                                          | = 1110 0110<br>= 0                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| After Instruct                                                                                                                                     | tion                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| REG1<br>W                                                                                                                                          | = 1110 0110<br>= 1100 1100                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| C                                                                                                                                                  | = 1                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RRF                                                                                                                                                | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| RRF<br>Syntax:                                                                                                                                     | Rotate Right f through Carry<br>[ label ] RRF f,d                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Syntax:                                                                                                                                            | [ <i>label</i> ] RRF f,d<br>0 ≤ f ≤ 31                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Syntax:<br>Operands:                                                                                                                               | $\begin{bmatrix} label \end{bmatrix} RRF f,d$<br>$0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                                                                                 | $ \begin{bmatrix} label \end{bmatrix} RRF f,d \\ 0 \le f \le 31 \\ d \in [0,1] \\ See description below $                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                                             | $ [label] RRF f,d  0 \le f \le 31  d \in [0,1]  See description below  C  0011 00df ffff  The contents of register 'f' are rotated  one bit to the right through the Carry  Flag. If 'd' is 0 the result is placed in the  W register. If 'd' is 1 the result is placed  back in register 'f'.$                                                                                                            |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                                | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                      | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>T                                                                          |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                           | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011  00df  ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>$c \rightarrow register 'f' \rightarrow 1$<br>1                         |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                      | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>T                                                                          |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                           | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1,0                                                       |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instru-<br>REG1     | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>C register 'f'<br>1<br>1<br>RRF REG1,0<br>interimed<br>= 1110 0110<br>= 0 |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instru<br>REG1<br>C | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1,0<br>interimed<br>= 1110 0110<br>= 0                    |  |  |  |  |

#### 10.16 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

## 11.3 Timing Parameter Symbology and Load Conditions - PIC12C508/C509

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

| 2. 1990                               |                                         |     |                |

|---------------------------------------|-----------------------------------------|-----|----------------|

| т                                     |                                         |     |                |

| F                                     | Frequency                               | т   | Time           |

| Lowerc                                | ase subscripts (pp) and their meanings: |     |                |

| рр                                    |                                         |     |                |

| 2                                     | to                                      | mc  | MCLR           |

| ck                                    | CLKOUT                                  | osc | oscillator     |

| су                                    | cycle time                              | os  | OSC1           |

| drt                                   | device reset timer                      | tO  | TOCKI          |

| io                                    | I/O port                                | wdt | watchdog timer |

| Uppercase letters and their meanings: |                                         |     |                |

| S                                     |                                         |     |                |

| F                                     | Fall                                    | Р   | Period         |

| н                                     | High                                    | R   | Rise           |

| I                                     | Invalid (Hi-impedance)                  | V   | Valid          |

| L                                     | Low                                     | Z   | Hi-impedance   |

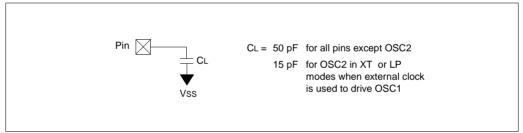

## FIGURE 11-1: LOAD CONDITIONS - PIC12C508/C509

## 12.0 DC AND AC CHARACTERISTICS - PIC12C508/PIC12C509

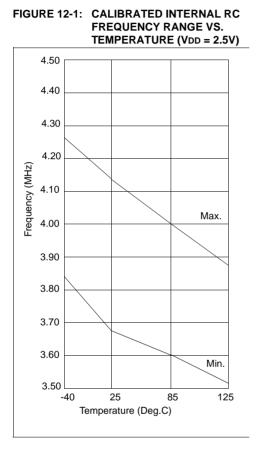

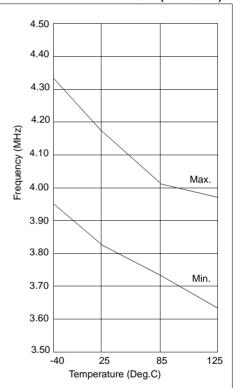

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables the data presented are outside specified operating range (e.g., outside specified VDD range). This is for information only and devices will operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

NOTES:

#### 13.2 DC CHARACTERISTICS:

#### PIC12LC508A/509A (Commercial, Industrial) PIC12LCE518/519 (Commercial, Industrial) PIC12LCR509A (Commercial, Industrial)

|               | DC Characteristics<br>Power Supply Pins       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \end{array}$ |       |                    |        |          |                                                                              |  |  |  |  |

|---------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|--------|----------|------------------------------------------------------------------------------|--|--|--|--|

| Parm<br>No.   | Characteristic                                | Sym                                                                                                                                                                                                                                                          | Min   | Typ <sup>(1)</sup> | Мах    | Units    | Conditions                                                                   |  |  |  |  |

| D001          | Supply Voltage                                | Vdd                                                                                                                                                                                                                                                          | 2.5   |                    | 5.5    | V        | Fosc = DC to 4 MHz (Commercial/<br>Industrial)                               |  |  |  |  |

| D002          | RAM Data Retention<br>Voltage <sup>(2)</sup>  | Vdr                                                                                                                                                                                                                                                          |       | 1.5*               |        | V        | Device in SLEEP mode                                                         |  |  |  |  |

| D003          | VDD Start Voltage to ensure<br>Power-on Reset | VPOR                                                                                                                                                                                                                                                         |       | Vss                |        | V        | See section on Power-on Reset for details                                    |  |  |  |  |

| D004          | VDD Rise Rate to ensure<br>Power-on Reset     | SVDD                                                                                                                                                                                                                                                         | 0.05* |                    |        | V/ms     | See section on Power-on Reset for details                                    |  |  |  |  |

| D010          | Supply Current <sup>(3)</sup>                 | IDD                                                                                                                                                                                                                                                          | —     | 0.4                | 0.8    | mA       | XT and EXTRC options (Note 4)<br>Fosc = 4 MHz, VDD = 2.5V                    |  |  |  |  |

| D010C         |                                               |                                                                                                                                                                                                                                                              | —     | 0.4                | 0.8    | mA       | INTRC Option<br>Fosc = 4 MHz, VDD = 2.5V                                     |  |  |  |  |

| D010A         |                                               |                                                                                                                                                                                                                                                              | —     | 15                 | 23     | μA       | LP OPTION, Commercial Temperature<br>Fosc = 32 kHz, VDD = 2.5V, WDT disabled |  |  |  |  |

|               |                                               |                                                                                                                                                                                                                                                              | _     | 15                 | 31     | μA       | LP OPTION, Industrial Temperature<br>FOSC = 32 kHz, VDD = 2.5V, WDT disabled |  |  |  |  |

| D020          | Power-Down Current (5)                        | IPD                                                                                                                                                                                                                                                          |       |                    |        |          |                                                                              |  |  |  |  |

| D021<br>D021B |                                               |                                                                                                                                                                                                                                                              |       | 0.2<br>0.2         | 3<br>4 | μΑ<br>μΑ | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                             |  |  |  |  |

|               |                                               | ΔIWDT                                                                                                                                                                                                                                                        | -     | 2.0<br>2.0         | 4<br>5 | mA<br>mA | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                             |  |  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: Does not include current through Rext. The current through the resistor can be estimated by the formula: IR = VDD/2Rext (mA) with Rext in kOhm.

- 5: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

#### TABLE 13-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| AC Chara         | cteristics | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ (commercial)}, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)}, \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 10.1} \\ \end{array} $ |      |                    |      |       |            |  |

|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|-------|------------|--|

| Parameter<br>No. | Sym        | Characteristic                                                                                                                                                                                                                                                                                                                                                                                       | Min* | Typ <sup>(1)</sup> | Max* | Units | Conditions |  |

|                  |            | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                                                                                                     | 3.65 | 4.00               | 4.28 | MHz   | VDD = 5.0V |  |

|                  |            | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                                                                                                     | 3.55 | —                  | 4.31 | MHz   | VDD = 2.5V |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 13-6: DRT (DEVICE RESET TIMER PERIOD) - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| Oscillator Configuration | POR Reset                      | Subsequent Resets               |  |  |  |

|--------------------------|--------------------------------|---------------------------------|--|--|--|

| IntRC & ExtRC            | 18 ms (typical) <sup>(1)</sup> | 300 µs (typical) <sup>(1)</sup> |  |  |  |

| XT & LP                  | 18 ms (typical) <sup>(1)</sup> | 18 ms (typical) <sup>(1)</sup>  |  |  |  |

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

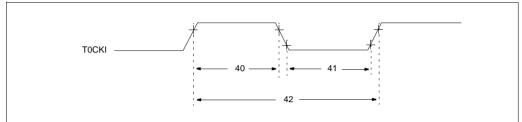

#### FIGURE 13-5: TIMER0 CLOCK TIMINGS - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

#### TABLE 13-7: TIMER0 CLOCK REQUIREMENTS - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| AC Characteristics |      |                                       |                  |                              |     |       |            |                                                                |  |

|--------------------|------|---------------------------------------|------------------|------------------------------|-----|-------|------------|----------------------------------------------------------------|--|

| Parameter<br>No.   | Sym  | Characteristic                        | Min              | Тур <sup>(1)</sup>           | Max | Units | Conditions |                                                                |  |

| 40                 | Tt0H | T0CKI High Pulse Width - No Prescaler |                  | 0.5 TCY + 20*                | —   | —     | ns         |                                                                |  |

|                    |      |                                       | - With Prescaler | 10*                          | -   | —     | ns         |                                                                |  |