Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.5KB (1K x 12)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | 16 × 8                                                                      |

| RAM Size                   | 41 × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 8-SOIJ                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce519-04e-sm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

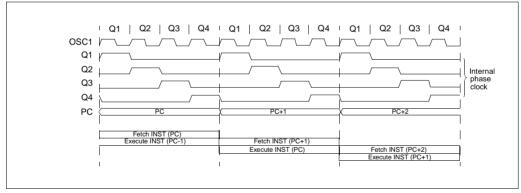

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

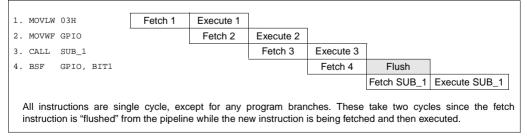

### 3.2 Instruction Flow/Pipelining

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.4 OPTION Register

The OPTION register is a 8-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A RESET sets the OPTION<7:0> bits.

### FIGURE 4-5: OPTION REGISTER

Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin; i.e., note that TRIS overrides OPTION control of GPPU and GPWU.

**Note:** If the TOCS bit is set to '1', GP2 is forced to be an input even if TRIS GP2 = '0'.

| W-1      | W-1                                                                                                                                                                 | W-1           | W-1         | W-1        | W-1         | W-1 | W-1  |                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|------------|-------------|-----|------|-----------------------------------------------------------------------------------------------|

| GPWU     | GPPU                                                                                                                                                                | TOCS          | T0SE        | PSA        | PS2         | PS1 | PS0  | W = Writable bit                                                                              |

| oit7     | 6                                                                                                                                                                   | 5             | 4           | 3          | 2           | 1   | bit0 | U = Unimplemented bit<br>- n = Value at POR reset<br>Reference Table 4-1 for<br>other resets. |

| bit 7:   | <b>GPWU</b> : Ena<br>1 = Disable<br>0 = Enable                                                                                                                      | d             | p on pin cl | hange (GP  | 0, GP1, GP3 | )   |      |                                                                                               |

| bit 6:   | <b>GPPU</b> : Ena<br>1 = Disable<br>0 = Enablec                                                                                                                     | d .           | III-ups (GF | 90, GP1, G | P3)         |     |      |                                                                                               |

| bit 5:   | <b>TOCS</b> : Time<br>1 = Transitio<br>0 = Transitio                                                                                                                | on on TOCK    | l pin       |            | ock, Fosc/4 |     |      |                                                                                               |

| bit 4:   | <b>TOSE</b> : Timer0 source edge select bit<br>1 = Increment on high to low transition on the T0CKI pin<br>0 = Increment on low to high transition on the T0CKI pin |               |             |            |             |     |      |                                                                                               |

| bit 3:   | PSA: Prescaler assignment bit<br>1 = Prescaler assigned to the WDT<br>0 = Prescaler assigned to Timer0                                                              |               |             |            |             |     |      |                                                                                               |

| bit 2-0: | PS2:PS0: P                                                                                                                                                          | Prescaler rat | e select bi | its        |             |     |      |                                                                                               |

|          | Bit Value                                                                                                                                                           | Timer0 R      | ate WDT     | Rate       |             |     |      |                                                                                               |

|          | 000                                                                                                                                                                 | 1:2<br>1:4    | 1:          | 2          |             |     |      |                                                                                               |

|          | 010<br>011                                                                                                                                                          | 1:8           | 1:          |            |             |     |      |                                                                                               |

|          | 100                                                                                                                                                                 | 1:32          |             | 0<br>16    |             |     |      |                                                                                               |

|          | 101                                                                                                                                                                 | 1:64          |             | 32         |             |     |      |                                                                                               |

|          | 110                                                                                                                                                                 | 1:128         |             | 64         |             |     |      |                                                                                               |

|          | 111                                                                                                                                                                 | 1:256         | : 1.        | 128        |             |     |      |                                                                                               |

NOTES:

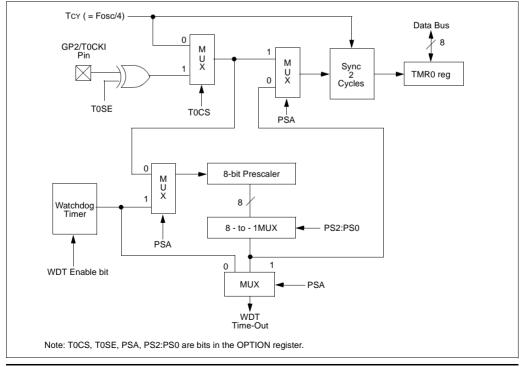

### 6.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 8.6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

| 1.CLRWDT            | ;Clear WDT               |

|---------------------|--------------------------|

| 2.CLRF TMR0         | ;Clear TMR0 & Prescaler  |

| 3.MOVLW '00xx1111'b | ;These 3 lines (5, 6, 7) |

| 4.OPTION            | ; are required only if   |

|                     | ; desired                |

| 5.CLRWDT            | ;PS<2:0> are 000 or 001  |

| 6.MOVLW '00xx1xxx'b | ;Set Postscaler to       |

| 7.OPTION            | ; desired WDT rate       |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT | •          | Clear WDT and       |

|--------|------------|---------------------|

|        |            | ;prescaler          |

| MOVLW  | 'xxxx0xxx' | ;Select TMR0, new   |

|        |            | ;prescale value and |

|        |            | ;clock source       |

| OPTION |            |                     |

### FIGURE 6-5: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

### 8.2 Oscillator Configurations

### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

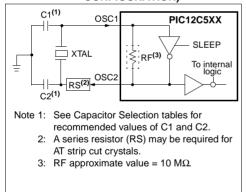

### 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

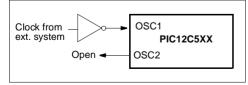

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

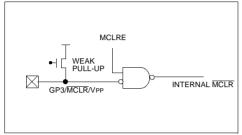

### 8.3.1 MCLR ENABLE

This configuration bit when unprogrammed (left in the '1' state) enables the external  $\overline{MCLR}$  function. When programmed, the  $\overline{MCLR}$  function is tied to the internal VDD, and the pin is assigned to be a GPIO. See Figure 8-7. When pin GP3/ $\overline{MCLR}$ /VPP is configured as  $\overline{MCLR}$ , the internal pull-up is always on.

### FIGURE 8-7: MCLR SELECT

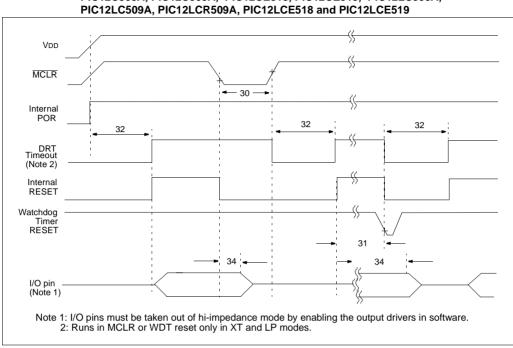

### 8.4 Power-On Reset (POR)

The PIC12C5XX family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip reset for most power-up situations.

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD or program the pin as GP3. An internal weak pull-up resistor is implemented using a transistor. Refer to Table 11-1 for the pull-up resistor ranges. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 8-8.

The Power-On Reset circuit and the Device Reset Timer (Section 8.5) circuit are closely related. On power-up, the reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will reset the reset latch and thus end the onchip reset signal.

A power-up example where  $\overline{\text{MCLR}}$  is held low is shown in Figure 8-9. VDD is allowed to rise and stabilize before bringing  $\overline{\text{MCLR}}$  high. The chip will actually come out of reset TDRT msec after  $\overline{\text{MCLR}}$  goes high.

In Figure 8-10, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3.). The VDD is stable before the start-up timer times out and there is no problem in getting a proper reset. However, Figure 8-11 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 8-10).

| Note: | When the device starts normal operation (exits the reset condition), device operating |

|-------|---------------------------------------------------------------------------------------|

|       | parameters (voltage, frequency, tempera-                                              |

|       | ture, etc.) must be meet to ensure opera-                                             |

|       | tion. If these conditions are not met, the                                            |

|       | device must be held in reset until the oper-                                          |

|       | ating conditions are met.                                                             |

For additional information refer to Application Notes "Power-Up Considerations" - AN522 and "Power-up Trouble Shooting" - AN607.

### 9.0 INSTRUCTION SET SUMMARY

Each PIC12C5XX instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC12C5XX instruction set summary in Table 9-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

### TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is<br>the recommended form of use for compatibility<br>with all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| WDT           | Watchdog Timer Counter                                                                                                                                                         |

| TO            | Time-Out bit                                                                                                                                                                   |

| PD            | Power-Down bit                                                                                                                                                                 |

| dest          | Destination, either the W register or the specified register file location                                                                                                     |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1 µs. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2 µs.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

### FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                                   |                                                                                       |      |        |        |             |   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|--------|--------|-------------|---|

|                                                                                                          | 11                                                                                    | 6    | 5      | 4      |             | 0 |

|                                                                                                          | OPCODE                                                                                |      | d      |        | f (FILE #)  |   |

|                                                                                                          | d = 0 for destination W<br>d = 1 for destination f<br>f = 5-bit file register address |      |        |        |             |   |

| Bi                                                                                                       | t-oriented file regi                                                                  | iste | er ope | eratio | ins         |   |

|                                                                                                          | 11                                                                                    | 8    | 7      | 5      | 4           | 0 |

|                                                                                                          | OPCODE                                                                                |      | b (B   | IT #)  | f (FILE #)  |   |

| b = 3-bit bit address<br>f = 5-bit file register address<br>Literal and control operations (except GOTO) |                                                                                       |      |        |        |             |   |

|                                                                                                          | 11                                                                                    |      | 8      | 7      |             | 0 |

|                                                                                                          | OPCODE                                                                                |      |        |        | k (literal) |   |

| k = 8-bit immediate value                                                                                |                                                                                       |      |        |        |             |   |

| Literal and control operations - GOTO instruction                                                        |                                                                                       |      |        |        |             |   |

| r                                                                                                        | 11                                                                                    |      | 9      | 8      |             | 0 |

|                                                                                                          | OPCODE                                                                                |      |        |        | k (literal) |   |

|                                                                                                          |                                                                                       |      |        |        |             |   |

k = 9-bit immediate value

| ADDWF                                                           | Add W and f                                                                                                                                                       |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                         | [label] ADDWF f,d                                                                                                                                                 |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                       |

| Operation:                                                      | (W) + (f) $\rightarrow$ (dest)                                                                                                                                    |

| Status Affected:                                                | C, DC, Z                                                                                                                                                          |

| Encoding:                                                       | 0001 11df ffff                                                                                                                                                    |

| Description:                                                    | Add the contents of the W register and register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. |

| Words:                                                          | 1                                                                                                                                                                 |

| Cycles:                                                         | 1                                                                                                                                                                 |

| Example:                                                        | ADDWF FSR, 0                                                                                                                                                      |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>tion<br>0xD9                                                                                                                                      |

| ANDWF                          | AND W with f                                                                                                                                                                       |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] ANDWF f,d                                                                                                                                                                  |

| Operands:                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                                        |

| Operation:                     | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                 |

| Status Affected:               | Z                                                                                                                                                                                  |

| Encoding:                      | 0001 01df ffff                                                                                                                                                                     |

| Description:                   | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>'1' the result is stored back in register 'f'. |

| Words:                         | 1                                                                                                                                                                                  |

| Cycles:                        | 1                                                                                                                                                                                  |

| Example:                       | ANDWF FSR, 1                                                                                                                                                                       |

| Before Instru<br>W =<br>FSR =  | 0x17                                                                                                                                                                               |

| After Instruct<br>W =<br>FSR = | 0x17                                                                                                                                                                               |

| ANDLW                 | And literal with W                                                                                                      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:               | [label] ANDLW k                                                                                                         |

| Operands:             | $0 \le k \le 255$                                                                                                       |

| Operation:            | (W).AND. (k) $\rightarrow$ (W)                                                                                          |

| Status Affected:      | Z                                                                                                                       |

| Encoding:             | 1110 kkkk kkkk                                                                                                          |

| Description:          | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'. The<br>result is placed in the W register. |

| Words:                | 1                                                                                                                       |

| Cycles:               | 1                                                                                                                       |

| Example:              | ANDLW 0x5F                                                                                                              |

| Before Instru<br>W =  | iction<br>0xA3                                                                                                          |

| After Instruct<br>W = | tion<br>0x03                                                                                                            |

| BCF                                   | Bit Clear f                                                        | f            |          |  |  |

|---------------------------------------|--------------------------------------------------------------------|--------------|----------|--|--|

| Syntax:                               | [label] B                                                          | CF f,b       | )        |  |  |

| Operands:                             | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |              |          |  |  |

| Operation:                            | $0 \rightarrow (f < b >)$                                          |              |          |  |  |

| Status Affected:                      | None                                                               |              |          |  |  |

| Encoding:                             | 0100                                                               | bbbf         | ffff     |  |  |

| Description:                          | Bit 'b' in reg                                                     | ister 'f' is | cleared. |  |  |

| Words:                                | 1                                                                  |              |          |  |  |

| Cycles:                               | 1                                                                  |              |          |  |  |

| Example:                              | BCF F                                                              | LAG_REG      | s, 7     |  |  |

| Before Instruction<br>FLAG_REG = 0xC7 |                                                                    |              |          |  |  |

| After Instruc<br>FLAG_R               | tion<br>EG = 0x47                                                  |              |          |  |  |

| SWAPF                                        | Swap Nibbles in f                                                                                                                                                     |  |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                      | [label] SWAPF f,d                                                                                                                                                     |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                             |  |  |  |  |

| Operation:                                   | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                             |  |  |  |  |

| Status Affected:                             | None                                                                                                                                                                  |  |  |  |  |

| Encoding:                                    | 0011 10df ffff                                                                                                                                                        |  |  |  |  |

| Description:                                 | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                     |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                     |  |  |  |  |

| Example                                      | SWAPF REG1, 0                                                                                                                                                         |  |  |  |  |

| Before Instru<br>REG1                        | iction<br>= 0xA5                                                                                                                                                      |  |  |  |  |

| After Instruction<br>REG1 = 0xA5<br>W = 0X5A |                                                                                                                                                                       |  |  |  |  |

| TRIS                                                                                   | Load TRIS Register                |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

| Syntax:                                                                                | [label] TRIS f                    |  |  |  |  |

| Operands: f = 6                                                                        |                                   |  |  |  |  |

| Operation:                                                                             | (W) $\rightarrow$ TRIS register f |  |  |  |  |

| Status Affected:                                                                       | None                              |  |  |  |  |

| Encoding:                                                                              | 0000 0000 0fff                    |  |  |  |  |

| Description: TRIS register 'f' (f = 6) is loaded with th<br>contents of the W register |                                   |  |  |  |  |

| Words:                                                                                 | 1                                 |  |  |  |  |

| Cycles:                                                                                | 1                                 |  |  |  |  |

| Example                                                                                | TRIS GPIO                         |  |  |  |  |

| Before Instruction<br>W = 0XA5                                                         |                                   |  |  |  |  |

| After Instruction<br>TRIS = 0XA5                                                       |                                   |  |  |  |  |

| <b>Note:</b> f = 6 f                                                                   | or PIC12C5XX only.                |  |  |  |  |

| XORLW                         | Exclusiv                                                                                                                           | ve OR lite    | ral with | w |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------|----------|---|--|--|

| Syntax:                       | [ <i>label</i> ]                                                                                                                   | XORLW         | k        |   |  |  |

| Operands:                     | $0 \le k \le 2$                                                                                                                    | 55            |          |   |  |  |

| Operation:                    | (W) .XO                                                                                                                            | $R. k \to (W$ | /)       |   |  |  |

| Status Affected:              | Z                                                                                                                                  |               |          |   |  |  |

| Encoding:                     | 1111                                                                                                                               | kkkk          | kkkk     |   |  |  |

| Description:                  | Description: The contents of the W register are<br>XOR'ed with the eight bit literal 'k'. T<br>result is placed in the W register. |               |          |   |  |  |

| Words:                        | 1                                                                                                                                  |               |          |   |  |  |

| Cycles:                       | 1                                                                                                                                  |               |          |   |  |  |

| Example:                      | XORLW                                                                                                                              | 0xAF          |          |   |  |  |

| Before Instru<br>W =          | uction<br>0xB5                                                                                                                     |               |          |   |  |  |

| After Instruction<br>W = 0x1A |                                                                                                                                    |               |          |   |  |  |

| XORWF                                              | Exclusive OR W with f                                                                                                                                                              |  |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                            | [label] XORWF f,d                                                                                                                                                                  |  |  |  |  |  |

| Operands:                                          | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                   |  |  |  |  |  |

| Operation:                                         | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                 |  |  |  |  |  |

| Status Affected:                                   | Z                                                                                                                                                                                  |  |  |  |  |  |

| Encoding:                                          | 0001 10df ffff                                                                                                                                                                     |  |  |  |  |  |

| Description:                                       | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |  |  |  |  |  |

| Words:                                             | 1                                                                                                                                                                                  |  |  |  |  |  |

| Cycles:                                            | 1                                                                                                                                                                                  |  |  |  |  |  |

| Example                                            | XORWF REG,1                                                                                                                                                                        |  |  |  |  |  |

| Before Instru<br>REG<br>W<br>After Instruct<br>REG | = 0xAF<br>= 0xB5<br>ion<br>= 0x1A                                                                                                                                                  |  |  |  |  |  |

| W                                                  | = 0xB5                                                                                                                                                                             |  |  |  |  |  |

### **10.0 DEVELOPMENT SUPPORT**

### 10.1 <u>Development Tools</u>

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- MPLAB<sup>™</sup>-ICE Real-Time In-Circuit Emulator

- ICEPIC<sup>™</sup> Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- SIMICE

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

- KEELOQ<sup>®</sup> Evaluation Kits and Programmer

### 10.2 MPLAB-ICE: High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro<sup>®</sup> microcontrollers (MCUs). MPLAB-ICE is supplied with the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support all new Microchip microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x or Windows 95 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE is available in two versions. MPLAB-ICE 1000 is a basic, low-cost emulator system with simple trace capabilities. It shares processor modules with the MPLAB-ICE 2000. This is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems will operate across the entire operating speed range of the PICmicro<sup>®</sup> MCU.

### 10.3 ICEPIC: Low-Cost PICmicro<sup>®</sup> In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 386 through Pentium<sup>™</sup> based machines under Windows 3.x, Windows 95, or Windows NT environment. ICEPIC features real time, non-intrusive emulation.

### 10.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

### 10.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

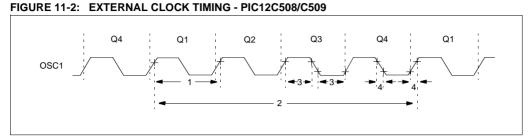

### 11.4 Timing Diagrams and Specifications

| AC CharacteristicsStandard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial),<br>$-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial),<br>$-40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended)<br>Operating Voltage VDD range is described in Section 11.1 |            |                                         |     |        |        |     |                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------|-----|--------|--------|-----|----------------|

| Parameter<br>No.         Sym         Characteristic         Min         Typ <sup>(1)</sup> Max         Units                                                                                                                                                                                                                             |            |                                         |     |        |        |     |                |

|                                                                                                                                                                                                                                                                                                                                          | Fosc       | External CLKIN Frequency <sup>(2)</sup> |     |        |        |     |                |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | DC  | —      | 4      | MHz | XT osc mode    |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | DC  | —      | 200    | kHz | LP osc mode    |

|                                                                                                                                                                                                                                                                                                                                          |            | Oscillator Frequency <sup>(2)</sup>     |     |        |        |     |                |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | 0.1 | —      | 4      | MHz | XT osc mode    |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | DC  | —      | 200    | kHz | LP osc mode    |

| 1                                                                                                                                                                                                                                                                                                                                        | Tosc       | External CLKIN Period <sup>(2)</sup>    | 250 | —      | _      | ns  | EXTRC osc mode |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | 250 | —      | —      | ns  | XT osc mode    |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | 5   | —      | —      | ms  | LP osc mode    |

|                                                                                                                                                                                                                                                                                                                                          |            | Oscillator Period <sup>(2)</sup>        | 250 | _      | _      | ns  | EXTRC osc mode |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | 250 | —      | 10,000 | ns  | XT osc mode    |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | 5   | —      | —      | ms  | LP osc mode    |

| 2                                                                                                                                                                                                                                                                                                                                        | Тсу        | Instruction Cycle Time <sup>(3)</sup>   | —   | 4/Fosc | —      |     |                |

| 3                                                                                                                                                                                                                                                                                                                                        | TosL, TosH | Clock in (OSC1) Low or High Time        | 50* | —      | —      | ns  | XT oscillator  |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | 2*  | —      | —      | ms  | LP oscillator  |

| 4                                                                                                                                                                                                                                                                                                                                        | TosR, TosF | Clock in (OSC1) Rise or Fall Time       | —   | —      | 25*    | ns  | XT oscillator  |

|                                                                                                                                                                                                                                                                                                                                          |            |                                         | -   | _      | 50*    | ns  | LP oscillator  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

3: Instruction cycle period (TCY) equals four times the input oscillator time base period.

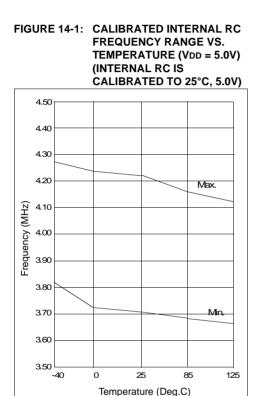

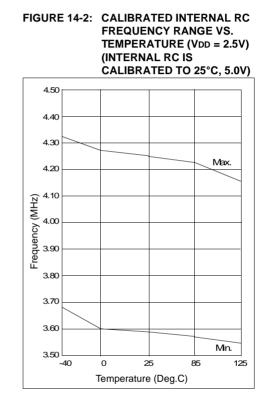

### TABLE 11-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC12C508/C509

| AC Characteristics       Standard Operating Conditions (unless otherwise specified)         Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial), $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial), $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)         Operating Voltage VDD range is described in Section 10.1 |     |                                  |      |                    |      |       |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|------|--------------------|------|-------|------------|

| Parameter<br>No.                                                                                                                                                                                                                                                                                                                              | Sym | Characteristic                   | Min* | Typ <sup>(1)</sup> | Max* | Units | Conditions |

|                                                                                                                                                                                                                                                                                                                                               |     | Internal Calibrated RC Frequency | 3.58 | 4.00               | 4.32 | MHz   | VDD = 5.0V |

|                                                                                                                                                                                                                                                                                                                                               |     | Internal Calibrated RC Frequency | 3.50 | —                  | 4.26 | MHz   | VDD = 2.5V |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

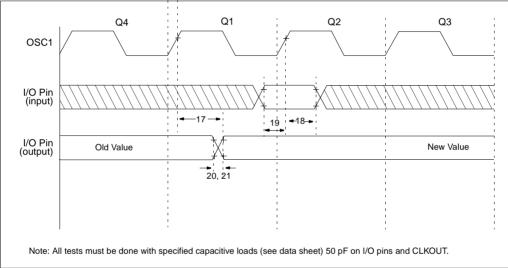

### FIGURE 11-3: I/O TIMING - PIC12C508/C509

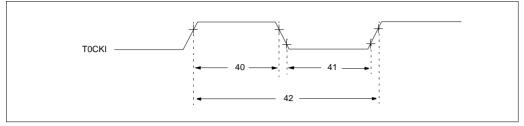

### FIGURE 11-5: TIMER0 CLOCK TIMINGS - PIC12C508/C509

### TABLE 11-7: TIMER0 CLOCK REQUIREMENTS - PIC12C508/C509

| AC               | Charao | cteristics         | Standard Operating Conditions (unless otherwise specified)         Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)         Operating Voltage VDD range is described in Section 11.1. |                              |   |   |    | ercial)<br>ial)<br>ded)                                        |

|------------------|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---|---|----|----------------------------------------------------------------|

| Parameter<br>No. | Sym    | Characteristic     | Min Typ <sup>(1)</sup> Max Units Conditions                                                                                                                                                                                                                                                                         |                              |   |   |    | Conditions                                                     |

| 40               | Tt0H   | T0CKI High Pulse V | Vidth - No Prescaler                                                                                                                                                                                                                                                                                                | 0.5 TCY + 20*                | — |   | ns |                                                                |

|                  |        |                    | - With Prescaler                                                                                                                                                                                                                                                                                                    |                              |   |   | ns |                                                                |

| 41               | Tt0L   | T0CKI Low Pulse W  | /idth - No Prescaler                                                                                                                                                                                                                                                                                                | 0.5 TCY + 20*                | — |   | ns |                                                                |

|                  |        |                    | - With Prescaler                                                                                                                                                                                                                                                                                                    | 10*                          | _ |   | ns |                                                                |

| 42               | Tt0P   | T0CKI Period       |                                                                                                                                                                                                                                                                                                                     | 20 or <u>Tcy + 40</u> *<br>N | _ | - | ns | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 13.3 DC CHARACTERISTICS:

### PIC12C508A/509A (Commercial, Industrial, Extended) PIC12C518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

| -40°C $\leq TA \leq +125°C$ (extended)<br>Operating voltage Vbb range as described in DC spec Sec<br>Section 13.2.Param<br>No.CharacteristicSymMinTyp†MaxUnitsConditInput Low Voltage<br>I/O portsVILVILVSS-0.8VVFor 4.5V $\leq$ VDD $\leq$ 5D030with TTL bufferVILVSS-0.15VDDVotherwiseD031with Schmitt Trigger bufferVSS-0.2VDDVotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)VSS-0.2VDDVNote 1D033OSC1 (in EXTRC mode)VSS-0.3VDDVNote 1D040with TTL bufferVIHD040with Schmitt Trigger buffer0.8VD-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD0404with Schmitt Trigger buffer0.8VD-VDDVFor entire VDD ranD0404with Schmitt Trigger buffer0.8VD-VDDVFor entire VDD ranD041with Schmitt Trigger buffer0.8VDD-VDDVVD042AOSC1 (in EXTRC mode)0.9VDD-VDDVVDVD042MCLR, gP2/T0CKI0.8VDD300 $\muA$ VDD $=$ 5V, VPIN $\leq$ VDD043OSC1 (in EXTRC mode)0.9VDD-VDDVVDVD044MCLR, gP2/T0CKI0.8VDD300 $\muA$ VDD $=$ 5V, VPIN $\leq$ <t< th=""><th>)</th></t<>         | )                                                           |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|--|

| Operating voltage VDD range as described in DC spec Sector 13.2.Param<br>No.CharacteristicSymMinTyp†MaxUnitsConditNo.Input Low Voltage<br>I/O portsViLViLVss-0.8VVFor 4.5V $\leq$ VDD $\leq$ 5D030with TTL bufferViLVss-0.15VDDVVD031with Schmitt Trigger bufferVss-0.2VDDVVD032MCLR, GP2/T0CKI (in EXTRC mode)Vss-0.2VDDVNote 1D033OSC1 (in TA rad LP)Vss-0.3VDDVNote 1D040Input High Voltage<br>with TTL bufferVIHD0404with Schmitt Trigger buffer0.8VDD-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD0404with Schmitt Trigger buffer0.8VDD-VDDV4.5V $\leq$ VDD $\leq$ 5.5VD0404with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD0404MCLR, GP2/T0CKI0.8VDD-VDDVVDD042OSC1 (in EXTRC mode)0.9VDD-VDDVVDVD042OSC1 (in EXTRC mode)0.9VDD-VDDVVDVD043OSC1 (in EXTRC mode)0.9VDD-VDDVVDVD044MCLR, GP2/T0CKI0.9VDD-VDDVVDVD045OSC1 (in EXTRC mode)0.9VDD-<                                                                                             | $-40^{\circ}C \le TA \le +85^{\circ}C \text{ (industrial)}$ |  |  |  |  |  |  |  |

| No.Input Low Voltage<br>I/O portsVILVILVILVILD030with TTL bufferVILVSS-0.8VVFor 4.5V $\leq$ VDD $\leq$ 5D031with Schmitt Trigger bufferVSS-0.15VDDVotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)VSS-0.2VDDVD033OSC1 (in EXTRC mode)VSS-0.2VDDVD033OSC1 (in XT and LP)VSS-0.2VDDVD040with TTL bufferVIHD040with Schmitt Trigger buffer0.8VD-VDDVD040with Schmitt Trigger buffer0.8VDD-VDDVD041with Schmitt Trigger buffer0.8VDD-VDDVD042AMCLR, GP2/T0CKI0.7VDD-VDDVD043OSC1 (XT and LP)0.7VDD-VDDVD043OSC1 (in EXTRC mode)IPUR30250400 $\mu$ AD043OSC1 (in EXTRC mode)IPUR30250400 $\mu$ AD043OSC1 (in EXTRC mode)IPUR30250400 $\mu$ AD044OportsIIL30 $\mu$ AD050I/O portsIIL+1 $\mu$ AVSS $\leq$ VPIN $\leq$ VDDD060I/O portsIIL+5 $\mu$ AVSS $\leq$ VPIN $\leq$ VDDD063OSC1+5 $\mu$ A <td< th=""><th>ion 13.1 and</th></td<>                                                                                                                  | ion 13.1 and                                                |  |  |  |  |  |  |  |

| Input Low Voltage<br>I/O portsVILVILVILVILVILVILVILD030with TTL bufferVILVSS- $0.8V$ VFor $4.5V \le VDD \le 5$ D031with Schmitt Trigger bufferVSS- $0.2VDD$ VotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)VSS- $0.2VDD$ VNote 1D033OSC1 (in XT and LP)VSS- $0.2VDD$ VNote 1D040with TTL bufferVIH0.3VDDVNote 1D040with TTL buffer0.25VDD +-VDDV $4.5V \le VDD \le 5.5V$ D040with TTL buffer0.8VDD-VDDVFor entire VDD ranD041with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD042MCLR, GP2/T0CKI0.8VDD-VDDVNote 1D043OSC1 (In EXTRC mode)0.9VDD-VDDVNote 1D043OSC1 (In EXTRC mode)0.9VDD-VDDVNote 1D043OSC1 (In EXTRC mode)IPUR30250400 $\mu A$ VDD = 5V, VPIN = VD070GPIO weak pull-up current (Notes 2, 3)IIL $\pm 1$ $\mu A$ VSS $\le VPIN \le VDD,$ D060I/O portsIIL $\pm 5$ $\mu A$ VSS $\le VPIN \le VDD,$ configurationD061TOCKI $\pm 5$ $\mu A$ VSS $\le VPIN \le VDD,$ configuration<                                          | ons                                                         |  |  |  |  |  |  |  |

| I/O portsVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVILVIL <th></th>                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |  |  |  |  |  |  |  |

| D030with TTL bufferVss- $0.8V$ VFor $4.5V \le Vbo \le 5$ D031with Schmitt Trigger bufferVss- $0.15Vbd$ VotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)Vss- $0.2Vbd$ VD033OSC1 (in EXTRC mode)Vss- $0.2Vbd$ VD033OSC1 (in XT and LP)Vss- $0.2Vbd$ Note 1D040Input High VoltageVIHVN0404 $0.25Vbd + 1$ VDDV $V$ $4.5V \le Vbd \le 5.5V$ D0404with Schmitt Trigger buffer $0.8Vbd + 2.0V$ VDDV $V$ D0404With Schmitt Trigger buffer $0.8Vbd + 2.0V$ VDDVFor entire VbD ranD0405With Schmitt Trigger buffer $0.8Vbd + 2.0V$ VDDVFor entire VbD ranD042MCLR, GP2/T0CKI $0.8Vbd + 2.0V$ VDDVFor entire VbD ranD043OSC1 (XT and LP) $0.7Vbd + 2.0V$ VDDVVD043OSC1 (in EXTRC mode) $0.9Vbd + 2.0V$ VDDVD070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu A$ VDD = 5V, VPIN = VD060I/O portsIIL30 $\mu A$ VDD = 5V, VPIN = VD060I/O portsIIL+5 $\mu A$ Vss $\leq VPIN \leq Vdd$ D061TOCKI+5 $\mu A$ Vss $\leq VPIN \leq Vdd$ D063OSC1Low Voltage-< |                                                             |  |  |  |  |  |  |  |

| D031with Schmitt Trigger bufferVSS-0.15VDDVotherwiseD032MCLR, GP2/T0CKI (in EXTRC mode)VSS-0.2VDDVVD033OSC1 (in EXTRC mode)VSS-0.2VDDVNote 1D033OSC1 (in XT and LP)VSS-0.3VDDVNote 1D040with TTL bufferVIHD040with TTL buffer0.25VDD +-VDDV4.5V ≤ VDD ≤ 5.5VD040AWith Schmitt Trigger buffer0.8VDD-VDDV4.5V ≤ VDD ≤ 5.5VD041with Schmitt Trigger buffer0.8VDD-VDDVFor entire VDD ranD042MCLR, GP2/T0CKI0.8VDD-VDDVNote 1D043OSC1 (in EXTRC mode)0.7VDD-VDDVNote 1D043OSC1 (in EXTRC mode)0.9VDD-VDDVNote 1D070GPIO weak pull-up current (Note 4)IPUR30250400 $\mu$ AVDD = 5V, VPIN = ND060I/O portsIIL30 $\mu$ AVDS ≤ VPIN ≤ VDD, configurationD061T0CKI+5 $\mu$ AVSS ≤ VPIN ≤ VDD, configurationD060I/O portsVOL0.6VIoL = 8.5 mA, VDD                                                                                                                                                                                                        |                                                             |  |  |  |  |  |  |  |