Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.5KB (1K x 12)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | 16 × 8                                                                     |

| RAM Size                   | 41 × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 8-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce519-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

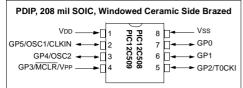

#### Pin Diagram - PIC12C508/509

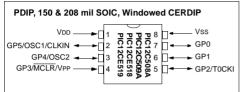

# Pin Diagram - PIC12C508A/509A, PIC12CE518/519

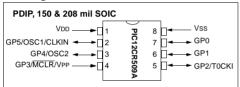

#### Pin Diagram - PIC12CR509A

#### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

# 2.0 PIC12C5XX DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12C5XX Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in ceramic side brazed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

Microchip's PICSTART<sup>®</sup> PLUS and PRO MATE<sup>®</sup> programmers all support programming of the PIC12C5XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

## 2.5 Read Only Memory (ROM) Device

Microchip offers masked ROM to give the customer a low cost option for high volume, mature products.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12C5XX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C5XX uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12-bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (1µs @ 4MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), ROM memory, and non-volatile (EEPROM) for each device.

|             | Memory           |                |             |                |  |  |  |  |

|-------------|------------------|----------------|-------------|----------------|--|--|--|--|

| Device      | EPROM<br>Program | ROM<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |

| PIC12C508   | 512 x 12         |                | 25          |                |  |  |  |  |

| PIC12C509   | 1024 x 12        |                | 41          |                |  |  |  |  |

| PIC12C508A  | 512 x 12         |                | 25          |                |  |  |  |  |

| PIC12C509A  | 1024 x 12        |                | 41          |                |  |  |  |  |

| PIC12CR509A |                  | 1024 x 12      | 41          |                |  |  |  |  |

| PIC12CE518  | 512 x 12         |                | 25 x 8      | 16 x 8         |  |  |  |  |

| PIC12CE519  | 1024 x 12        |                | 41 x 8      | 16 x 8         |  |  |  |  |

The PIC12C5XX can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC12C5XX has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C5XX simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC12C5XX device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The special registers can be classified into two sets. The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

#### TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

|                    |                                                                                     |                             |                                      |             |           |                        |              |         |       | Value on<br>Power-On | Value on<br>All Other    |

|--------------------|-------------------------------------------------------------------------------------|-----------------------------|--------------------------------------|-------------|-----------|------------------------|--------------|---------|-------|----------------------|--------------------------|

| Address            | Name                                                                                | Bit 7                       | Bit 6                                | Bit 5       | Bit 4     | Bit 3                  | Bit 2        | Bit 1   | Bit 0 | Reset                | Resets <sup>(2)</sup>    |

| N/A                | TRIS                                                                                | —                           | I                                    |             |           |                        |              |         |       | 11 1111              | 11 1111                  |

| N/A                | OPTION                                                                              | Contains co<br>prescaler, v |                                      |             |           | Timer0/WD1<br>pull-ups | Г            |         |       | 1111 1111            | 1111 1111                |

| 00h                | INDF                                                                                | Uses conte                  | ents of FSR                          | R to addres | s data me | mory (not a            | physical reg | jister) |       | xxxx xxxx            | uuuu uuuu                |

| 01h                | TMR0                                                                                | 8-bit real-ti               | me clock/c                           | ounter      |           |                        |              |         |       | xxxx xxxx            | uuuu uuuu                |

| 02h <sup>(1)</sup> | PCL                                                                                 | Low order                   | B bits of PC                         | c           |           |                        |              |         |       | 1111 1111            | 1111 1111                |

| 03h                | STATUS                                                                              | GPWUF                       | -                                    | PA0         | TO        | PD                     | Z            | DC      | С     | 0001 1xxx            | q00q quuu <sup>(3)</sup> |

| 04h                | FSR<br>(PIC12C508/<br>PIC12C508A/<br>PIC12C518)                                     | Indirect dat                | ndirect data memory address pointer  |             |           |                        |              |         | 1     | 111x xxxx            | 111u uuuu                |

| 04h                | FSR<br>(PIC12C509/<br>PIC12C509A/<br>PIC12CR509A/<br>PIC12CE519)                    | Indirect dat                | Indirect data memory address pointer |             |           |                        |              |         |       | 110x xxxx            | 11uu uuuu                |

| 05h                | OSCCAL<br>(PIC12C508/<br>PIC12C509)                                                 | CAL3                        | CAL2                                 | CAL1        | CAL0      | _                      | _            | _       | _     | 0111                 | uuuu                     |

| 05h                | OSCCAL<br>(PIC12C508A/<br>PIC12C509A/<br>PIC12CE518/<br>PIC12CE519/<br>PIC12CR509A) | CAL5                        | CAL4                                 | CAL3        | CAL2      | CAL1                   | CAL0         |         | _     | 1000 00              | uuuu uu                  |

| 06h                | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CC509A)     | _                           | _                                    | GP5         | GP4       | GP3                    | GP2          | GP1     | GP0   | xx xxxx              | uu uuuu                  |

| 06h                | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                                 | SCL                         | SDA                                  | GP5         | GP4       | GP3                    | GP2          | GP1     | GP0   | 11xx xxxx            | 11uu uuuu                |

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as '0' (if applicable)

x = unknown, u = unchanged, q = see the tables in Section 8.7 for possible values.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 for an explanation of how to access these bits.

2: Other (non power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

3: If reset was due to wake-up on pin change then bit 7 = 1. All other resets will cause bit 7 = 0.

# FIGURE 5-2: SUCCESSIVE I/O OPERATION

| PC         | Y PC + 1                         | X PC + 2                                                                         | X PC + 3                                                                                | This example shows a write to GPIO follower                                                                 |

|------------|----------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| MOVWF GPIO | MOVF GPIO,W                      | NOP                                                                              | NOP                                                                                     | by a read from GPIO.<br>Data setup time = (0.25 Tcy – TpD)                                                  |

|            | 1<br>1<br>1                      | X                                                                                | 1                                                                                       | where: TCY = instruction cycle.<br>TPD = propagation delay                                                  |

|            | Port pin<br>written here         | Port pin<br>sampled here                                                         | ,<br>,<br>,<br>,                                                                        | Therefore, at higher clock frequencies, a write followed by a read may be problematic                       |

|            | MOVWF GPIO<br>(Write to<br>GPIO) | MOVF GPIO,W<br>(Read<br>GPIO)                                                    | NOP                                                                                     |                                                                                                             |

|            |                                  | MOVWF GPIO<br>MOVF GPIO,W<br>Port pin<br>written here<br>MOVWF GPIO<br>(Write to | MOVWF GPIO MOVF GPIO,W NOP Port pin written here MOVWF GPIO MOVF GPIO,W (Write to (Read | MOVWF GPIO MOVF GPIO,W NOP NOP<br>Port pin<br>written here<br>MOVWF GPIO MOVF GPIO,W NOP<br>(Write to (Read |

# PIC12C5XX

NOTES:

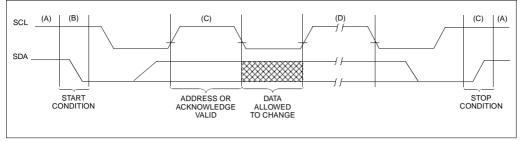

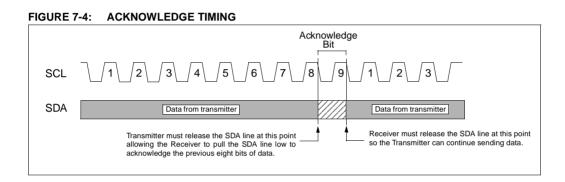

### FIGURE 7-3: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

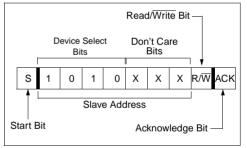

### 7.2 Device Addressing

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed. The slave address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

#### FIGURE 7-5: CONTROL BYTE FORMAT

# 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC12C5XX family of microcontrollers has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- · Oscillator selection

- Reset

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from SLEEP on pin change

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- · ID locations

- · In-circuit Serial Programming

The PIC12C5XX has a Watchdog Timer which can be shut off only through configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in reset until the crystal oscillator is stable. If using INTRC or EXTRC there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 8.1 Configuration Bits

The PIC12C5XX configuration word consists of 12 bits. Configuration bits can be programmed to select various device configurations. Two bits are for the selection of the oscillator type, one bit is the Watchdog Timer enable bit, and one bit is the MCLR enable bit.

#### FIGURE 8-1: CONFIGURATION WORD FOR PIC12C5XX

| _         | —                                                                                                                                                                                                            | —       | —  | — | — | — | MCLRE                       | CP | WDTE | FOSC1 | FOSC0 | Register:                | CONFIG |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----|---|---|---|-----------------------------|----|------|-------|-------|--------------------------|--------|

| bit11     | 10                                                                                                                                                                                                           | 9       | 8  | 7 | 6 | 5 | 4                           | 3  | 2    | 1     | bit0  | Address <sup>(1)</sup> : | FFFh   |

| bit 11-5: | Unim                                                                                                                                                                                                         | olement | ed |   |   |   |                             |    |      |       |       |                          |        |

| bit 4:    | t 4: MCLRE: MCLR enable bit.<br>1 = MCLR pin enabled<br>0 = MCLR tied to VDD, (Internally)                                                                                                                   |         |    |   |   |   |                             |    |      |       |       |                          |        |

| bit 3:    | <b>CP:</b> Code protection bit.<br>1 = Code protection off<br>0 = Code protection on                                                                                                                         |         |    |   |   |   |                             |    |      |       |       |                          |        |

| bit 2:    | WDTE: Watchdog timer enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                       |         |    |   |   |   |                             |    |      |       |       |                          |        |

| bit 1-0:  | <ul> <li>FOSC1:FOSC0: Oscillator selection bits</li> <li>11 = EXTRC - external RC oscillator</li> <li>10 = INTRC - internal RC oscillator</li> <li>01 = XT oscillator</li> <li>00 = LP oscillator</li> </ul> |         |    |   |   |   |                             |    |      |       |       |                          |        |

| Note 1:   |                                                                                                                                                                                                              |         |    | • | • |   | ations to de<br>Iressable d |    |      |       | he    |                          |        |

#### 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

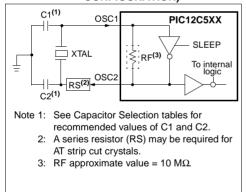

# 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

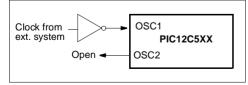

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

#### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

#### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

#### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 8-4 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

#### FIGURE 8-4: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

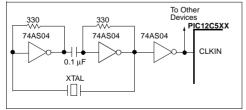

Figure 8-5 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 8-5: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

#### 8.2.4 EXTERNAL RC OSCILLATOR

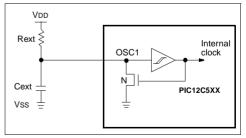

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 8-6 shows how the R/C combination is connected to the PIC12C5XX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

# FIGURE 8-6: EXTERNAL RC OSCILLATOR MODE

#### 8.7 <u>Time-Out Sequence, Power Down,</u> and Wake-up from SLEEP Status Bits (TO/PD/GPWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits in the STATUS register can be tested to determine if a RESET condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) reset.

| TABLE 8-7: | TO/PD/GPWUF STATUS |

|------------|--------------------|

|            | AFTER RESET        |

| GPWUF | то | PD | RESET caused by                     |

|-------|----|----|-------------------------------------|

| 0     | 0  | 0  | WDT wake-up from<br>SLEEP           |

| 0     | 0  | u  | WDT time-out (not from<br>SLEEP)    |

| 0     | 1  | 0  | MCLR wake-up from<br>SLEEP          |

| 0     | 1  | 1  | Power-up                            |

| 0     | u  | u  | MCLR not during SLEEP               |

| 1     | 1  | 0  | Wake-up from SLEEP on<br>pin change |

Legend: u = unchanged

Note 1: The TO, PD, and GPWUF bits maintain their status (u) until a reset occurs. A lowpulse on the MCLR input does not change the TO, PD, and GPWUF status bits.

#### 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

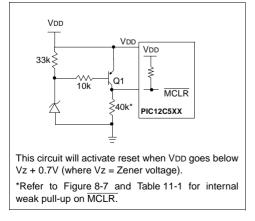

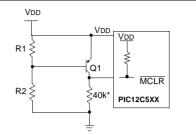

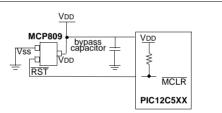

To reset PIC12C5XX devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-13 , Figure 8-14 and Figure 8-15

#### FIGURE 8-13: BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

\*Refer to Figure 8-7 and Table 11-1 for internal weak pull-up on MCLR.

#### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX family of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accomodate 5V and 3V systems.

# PIC12C5XX

| COMF                       | Complement f                                                                                                                                                         |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                    | [ label ] COMF f,d                                                                                                                                                   |

| Operands:                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                            |

| Operation:                 | $(\overline{f}) \rightarrow (dest)$                                                                                                                                  |

| Status Affected:           | Z                                                                                                                                                                    |

| Encoding:                  | 0010 01df ffff                                                                                                                                                       |

| Description:               | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |

| Words:                     | 1                                                                                                                                                                    |

| Cycles:                    | 1                                                                                                                                                                    |

| Example:                   | COMF REG1,0                                                                                                                                                          |

| Before Instru<br>REG1      | uction<br>= 0x13                                                                                                                                                     |

| After Instruc<br>REG1<br>W | tion<br>= 0x13<br>= 0xEC                                                                                                                                             |

| DECF                                                    | Decrement f                                                                                                                              |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                 | [label] DECF f,d                                                                                                                         |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                |

| Operation:                                              | $(f) - 1 \rightarrow (dest)$                                                                                                             |

| Status Affected:                                        | Z                                                                                                                                        |

| Encoding:                                               | 0000 11df ffff                                                                                                                           |

| Description:                                            | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |

| Words:                                                  | 1                                                                                                                                        |

| Cycles:                                                 | 1                                                                                                                                        |

| Example:                                                | decf cnt, 1                                                                                                                              |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0x01 $= 0$                                                                                                                             |

| DECFSZ                                               | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                              | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Operation:                                           | (f) $- 1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Encoding:                                            | 0010 11df ffff                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Description:                                         | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded<br>and an NOP is executed instead mak-<br>ing it a two cycle instruction. |  |  |  |  |  |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:                                              | 1(2)                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Example:                                             | HERE DECFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                                                      | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Before Instru                                        | uction                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| PC                                                   | = address (HERE)                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| After Instruc<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | <pre>tion = CNT - 1; = 0, = address (CONTINUE); ≠ 0, = address (HERE+1)</pre>                                                                                                                                                                                                                                                        |  |  |  |  |  |

| GOTO                                                 | Unconditional Branch                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| GOTO                                      | Unconditional Branch                                                                                                                                                                    |  |  |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                   | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |  |  |  |

| Operands:                                 | $0 \le k \le 511$                                                                                                                                                                       |  |  |  |  |  |  |

| Operation:                                | $k \rightarrow PC<8:0>;$<br>STATUS<6:5> $\rightarrow PC<10:9>$                                                                                                                          |  |  |  |  |  |  |

| Status Affected:                          | None                                                                                                                                                                                    |  |  |  |  |  |  |

| Encoding:                                 | 101k kkkk kkkk                                                                                                                                                                          |  |  |  |  |  |  |

| Description:                              | GOTO is an unconditional branch. The<br>9-bit immediate value is loaded into PC<br>bits <8:0>. The upper bits of PC are<br>loaded from STATUS<6:5>. GOTO is a<br>two cycle instruction. |  |  |  |  |  |  |

| Words:                                    | 1                                                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:                                   | 2                                                                                                                                                                                       |  |  |  |  |  |  |

| Example:                                  | GOTO THERE                                                                                                                                                                              |  |  |  |  |  |  |

| After Instruction<br>PC = address (THERE) |                                                                                                                                                                                         |  |  |  |  |  |  |

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Max  | Units |  |  |  |  |

|-------------|------------------|------|------|------|-------|--|--|--|--|

| GP0/GP1     |                  |      |      |      |       |  |  |  |  |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |  |  |  |  |

|             | 25               | 42K  | 48K  | 63K  | Ω     |  |  |  |  |

|             | 85               | 42K  | 49K  | 63K  | Ω     |  |  |  |  |

|             | 125              | 50K  | 55K  | 63K  | Ω     |  |  |  |  |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |  |  |  |  |

|             | 25               | 18K  | 20K  | 23K  | Ω     |  |  |  |  |

|             | 85               | 19K  | 22K  | 25K  | Ω     |  |  |  |  |

|             | 125              | 22K  | 24K  | 28K  | Ω     |  |  |  |  |

|             |                  | G    | P3   |      |       |  |  |  |  |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |  |  |  |  |

|             | 25               | 343K | 414K | 532K | Ω     |  |  |  |  |

|             | 85               | 368K | 457K | 532K | Ω     |  |  |  |  |

|             | 125              | 431K | 504K | 593K | Ω     |  |  |  |  |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |  |  |  |  |

|             | 25               | 288K | 341K | 437K | Ω     |  |  |  |  |

|             | 85               | 306K | 371K | 448K | Ω     |  |  |  |  |

|             | 125              | 351K | 407K | 500K | Ω     |  |  |  |  |

# TABLE 11-1: PULL-UP RESISTOR RANGES - PIC12C508/C509

\* These parameters are characterized but not tested.

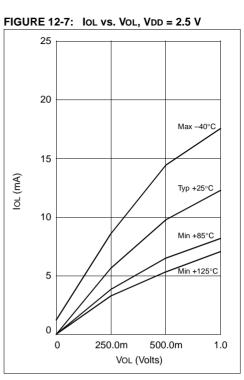

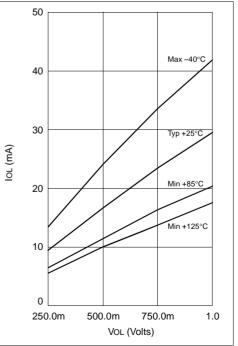

FIGURE 12-8: IOL vs. VOL, VDD = 5.5 V

#### TABLE 13-8: EEPROM MEMORY BUS TIMING REQUIREMENTS - PIC12CE5XX ONLY.

| AC Characteristics                                                                   | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ , Vcc = 3.0V to 5.5V (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ , Vcc = 3.0V to 5.5V (industrial) $-40^{\circ}C \leq TA \leq +125^{\circ}C$ , Vcc = 4.5V to 5.5V (extended)Operating Voltage VDD range is described in Section 13.1 |                      |                     |        |                                                                                                                                     |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                            | Symbol                                                                                                                                                                                                                                                                                                                                                                | Min                  | Max                 | Units  | Conditions                                                                                                                          |

| Clock frequency                                                                      | FCLK                                                                                                                                                                                                                                                                                                                                                                  |                      | 100<br>100<br>400   | kHz    | 4.5V ≤ Vcc ≤ 5.5V (E Temp range)<br>3.0V ≤ Vcc ≤ 4.5V<br>4.5V ≤ Vcc ≤ 5.5V                                                          |

| Clock high time                                                                      | Тнідн                                                                                                                                                                                                                                                                                                                                                                 | 4000<br>4000<br>600  |                     | ns     |                                                                                                                                     |

| Clock low time                                                                       | TLOW                                                                                                                                                                                                                                                                                                                                                                  | 4700<br>4700<br>1300 |                     | ns     |                                                                                                                                     |

| SDA and SCL rise time<br>(Note 1)                                                    | TR                                                                                                                                                                                                                                                                                                                                                                    |                      | 1000<br>1000<br>300 | ns     |                                                                                                                                     |

| SDA and SCL fall time                                                                | TF                                                                                                                                                                                                                                                                                                                                                                    | _                    | 300                 | ns     | (Note 1)                                                                                                                            |

| START condition hold time                                                            | THD:STA                                                                                                                                                                                                                                                                                                                                                               | 4000<br>4000<br>600  |                     | ns     |                                                                                                                                     |

| START condition setup time                                                           | TSU:STA                                                                                                                                                                                                                                                                                                                                                               | 4700<br>4700<br>600  |                     | ns     |                                                                                                                                     |

| Data input hold time                                                                 | THD:DAT                                                                                                                                                                                                                                                                                                                                                               | 0                    |                     | ns     | (Note 2)                                                                                                                            |

| Data input setup time                                                                | TSU:DAT                                                                                                                                                                                                                                                                                                                                                               | 250<br>250<br>100    |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \mbox{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$ |

| STOP condition setup time                                                            | Tsu:sto                                                                                                                                                                                                                                                                                                                                                               | 4000<br>4000<br>600  |                     | ns     | 4.5V ≤ Vcc ≤ 5.5V (E Temp range)<br>3.0V ≤ Vcc ≤ 4.5V<br>4.5V ≤ Vcc ≤ 5.5V                                                          |

| Output valid from clock<br>(Note 2)                                                  | ΤΑΑ                                                                                                                                                                                                                                                                                                                                                                   |                      | 3500<br>3500<br>900 | ns     | 4.5V ≤ Vcc ≤ 5.5V (E Temp range)<br>3.0V ≤ Vcc ≤ 4.5V<br>4.5V ≤ Vcc ≤ 5.5V                                                          |

| Bus free time: Time the bus must<br>be free before a new transmis-<br>sion can start | TBUF                                                                                                                                                                                                                                                                                                                                                                  | 4700<br>4700<br>1300 |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \mbox{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$ |

| Output fall time from VIH<br>minimum to VIL maximum                                  | TOF                                                                                                                                                                                                                                                                                                                                                                   | 20+0.1<br>CB         | 250                 | ns     | (Note 1), CB ≤ 100 pF                                                                                                               |

| Input filter spike suppression (SDA and SCL pins)                                    | TSP                                                                                                                                                                                                                                                                                                                                                                   |                      | 50                  | ns     | (Notes 1, 3)                                                                                                                        |

| Write cycle time                                                                     | Twc                                                                                                                                                                                                                                                                                                                                                                   | —                    | 4                   | ms     |                                                                                                                                     |

| Endurance                                                                            |                                                                                                                                                                                                                                                                                                                                                                       | 1M                   | _                   | cycles | 25°C, Vcc = 5.0V, Block Mode (Note 4)                                                                                               |

Note 1: Not 100% tested. CB = total capacitance of one bus line in pF.

2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

**3:** The combined TSP and VHYS specifications are due to new Schmitt trigger inputs which provide improved noise spike suppression. This eliminates the need for a TI specification for standard operation.

4: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be obtained on Microchip's website.

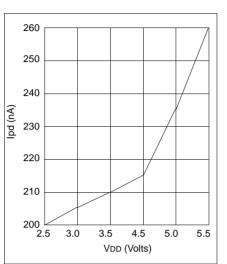

FIGURE 14-13: TYPICAL IPD VS. VDD, WATCHDOG DISABLED (25°C)

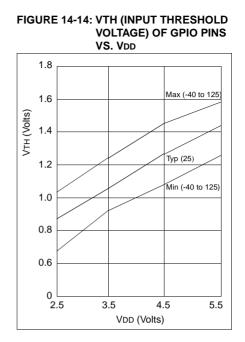

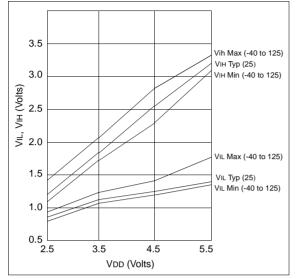

# FIGURE 14-15: VIL, VIH OF NMCLR, AND TOCKI VS. VDD

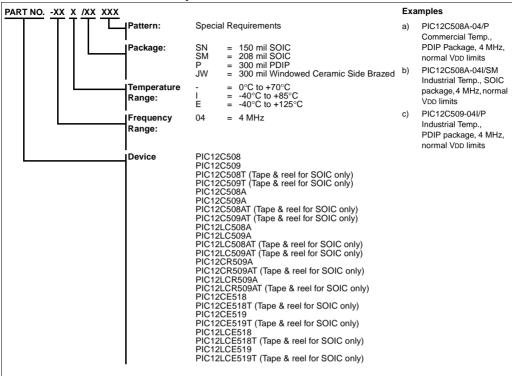

#### PIC12C5XX Product Identification System

Please contact your local sales office for exact ordering procedures.

#### Sales and Support:

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoq® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.