Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 768B (512 x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Through Hole                                                               |

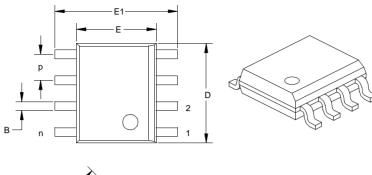

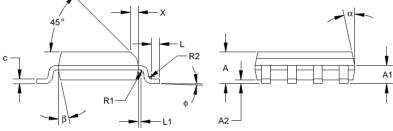

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 8-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc508a-04-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

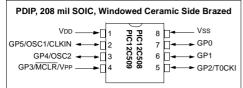

#### Pin Diagram - PIC12C508/509

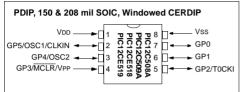

# Pin Diagram - PIC12C508A/509A, PIC12CE518/519

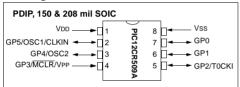

#### Pin Diagram - PIC12CR509A

#### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

# 1.0 GENERAL DESCRIPTION

The PIC12C5XX from Microchip Technology is a family of low-cost, high performance, 8-bit, fully static, EEPROM/EPROM/ROM-based CMOS microcontrollers. It employs a RISC architecture with only 33 single word/single cycle instructions. All instructions are single cycle (1  $\mu$ s) except for program branches which take two cycles. The PIC12C5XX delivers performance an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

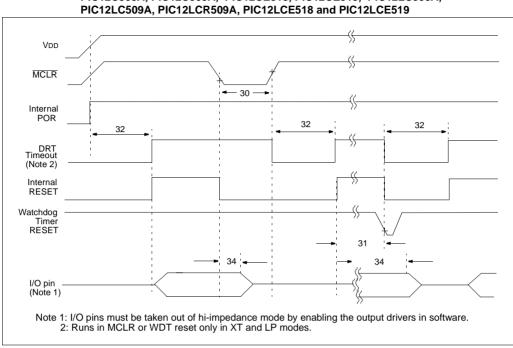

The PIC12C5XX products are equipped with special features that reduce system cost and power requirements. The Power-On Reset (POR) and Device Reset Timer (DRT) eliminate the need for external reset circuitry. There are four oscillator configurations to choose from, including INTRC internal oscillator mode and the power-saving LP (Low Power) oscillator mode. Power saving SLEEP mode, Watchdog Timer and code protection features also improve system cost, power and reliability.

The PIC12C5XX are available in the cost-effective One-Time-Programmable (OTP) versions which are suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers while benefiting from the OTP's flexibility.

The PIC12C5XX products are supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a 'C' compiler, fuzzy logic support tools, a low-cost development programmer, and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

### 1.1 Applications

The PIC12C5XX series fits perfectly in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The EPROM technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies. etc.) extremely fast and convenient, while the EEPROM data memory technology allows for the changing of calibration factors and security codes. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC12C5XX series very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic and PLD's in larger systems, coprocessor applications).

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The special registers can be classified into two sets. The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

### TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

|                    |                                                                                     |               |                                                                                                         |             |           |             |              |         |       | Value on<br>Power-On | Value on<br>All Other    |

|--------------------|-------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------|-------------|-----------|-------------|--------------|---------|-------|----------------------|--------------------------|

| Address            | Name                                                                                | Bit 7         | Bit 6                                                                                                   | Bit 5       | Bit 4     | Bit 3       | Bit 2        | Bit 1   | Bit 0 | Reset                | Resets <sup>(2)</sup>    |

| N/A                | TRIS                                                                                | —             | I                                                                                                       |             |           |             |              |         |       | 11 1111              | 11 1111                  |

| N/A                | OPTION                                                                              |               | Contains control bits to configure Timer0, Timer0/WDT<br>rescaler, wake-up on change, and weak pull-ups |             |           |             |              |         |       |                      | 1111 1111                |

| 00h                | INDF                                                                                | Uses conte    | ents of FSR                                                                                             | R to addres | s data me | mory (not a | physical reg | jister) |       | xxxx xxxx            | uuuu uuuu                |

| 01h                | TMR0                                                                                | 8-bit real-ti | me clock/c                                                                                              | ounter      |           |             |              |         |       | xxxx xxxx            | uuuu uuuu                |

| 02h <sup>(1)</sup> | PCL                                                                                 | Low order     | B bits of PC                                                                                            | c           |           |             |              |         |       | 1111 1111            | 1111 1111                |

| 03h                | STATUS                                                                              | GPWUF         | -                                                                                                       | PA0         | TO        | PD          | Z            | DC      | С     | 0001 1xxx            | q00q quuu <sup>(3)</sup> |

| 04h                | FSR<br>(PIC12C508/<br>PIC12C508A/<br>PIC12C518)                                     | Indirect dat  | ndirect data memory address pointer                                                                     |             |           |             |              |         | 1     | 111x xxxx            | 111u uuuu                |

| 04h                | FSR<br>(PIC12C509/<br>PIC12C509A/<br>PIC12CR509A/<br>PIC12CE519)                    | Indirect dat  | Indirect data memory address pointer                                                                    |             |           |             |              |         |       | 110x xxxx            | 11uu uuuu                |

| 05h                | OSCCAL<br>(PIC12C508/<br>PIC12C509)                                                 | CAL3          | CAL2                                                                                                    | CAL1        | CAL0      | _           | _            | _       | _     | 0111                 | uuuu                     |

| 05h                | OSCCAL<br>(PIC12C508A/<br>PIC12C509A/<br>PIC12CE518/<br>PIC12CE519/<br>PIC12CR509A) | CAL5          | CAL4                                                                                                    | CAL3        | CAL2      | CAL1        | CAL0         |         | _     | 1000 00              | uuuu uu                  |

| 06h                | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12C509A)      | _             | _                                                                                                       | GP5         | GP4       | GP3         | GP2          | GP1     | GP0   | xx xxxx              | uu uuuu                  |

| 06h                | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                                 | SCL           | SDA                                                                                                     | GP5         | GP4       | GP3         | GP2          | GP1     | GP0   | 11xx xxxx            | 11uu uuuu                |

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as '0' (if applicable)

x = unknown, u = unchanged, q = see the tables in Section 8.7 for possible values.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 for an explanation of how to access these bits.

2: Other (non power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

3: If reset was due to wake-up on pin change then bit 7 = 1. All other resets will cause bit 7 = 0.

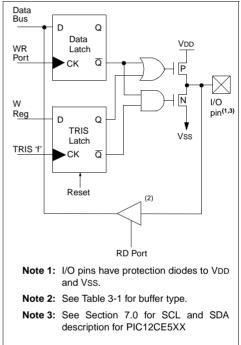

# 5.0 I/O PORT

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

# 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the output data latches. That is, if an output      |

|-------|---------------------------------------------------------------------------------------------|

|       | driver on a pin is enabled and driven high,                                                 |

|       | but the external system is holding it low, a read of the port will indicate that the pin is |

|       | low.                                                                                        |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

# 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

## FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

| TABLE 5-1: S | UMMARY OF PORT | <b>REGISTERS</b> |

|--------------|----------------|------------------|

|--------------|----------------|------------------|

| Address | Name                                                                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|---------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------|

| N/A     | TRIS                                                                            | —     | -     |       |       |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | OPTION                                                                          | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                    |

| 03H     | STATUS                                                                          | GPWUF | -     | PAO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>     |

| 06h     | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CR509A) |       | _     | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                      |

| 06h     | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                             | SCL   | SDA   | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 11xx xxxx                     | 11uu uuuu                    |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, g = see tables in Section 8.7 for possible values.

Note 1: If reset was due to wake-up on change, then bit 7 = 1. All other resets will cause bit 7 = 0.

#### 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of GPIO will cause all eight bits of GPIO to be read into the CPU, bit5 to be set and the GPIO value to be written to the output latches. If another bit of GPIO is used as a bidirectional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}$  ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wiredand"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ; | Initia              | L GPIO  | Sett | ings |         |     |        |

|---|---------------------|---------|------|------|---------|-----|--------|

| ; | GPIO<5              | 5:3> In | puts | 3    |         |     |        |

| ; | ; GPIO<2:0> Outputs |         |      |      |         |     |        |

| ; |                     |         |      |      |         |     |        |

| ; |                     |         |      | GPIC | ) latch | GPI | ) pins |

| ; |                     |         |      |      |         |     |        |

|   | BCF                 | GPIO,   | 5    | ;01  | -ppp    | 11  | pppp   |

|   | BCF                 | GPIO,   | 4    | ;10  | -ppp    | 11  | pppp   |

|   | MOVLW               | 007h    |      | ;    |         |     |        |

|   | TRIS                | GPIO    |      | ;10  | -ppp    | 11  | pppp   |

|   |                     |         |      |      |         |     |        |

;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;GP5 to be latched as the pin value (High).

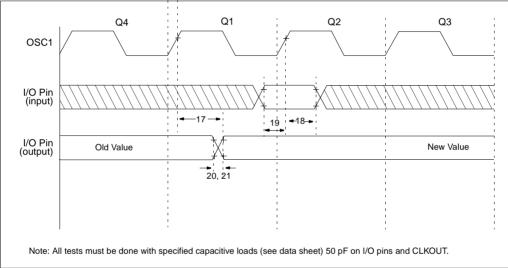

# 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

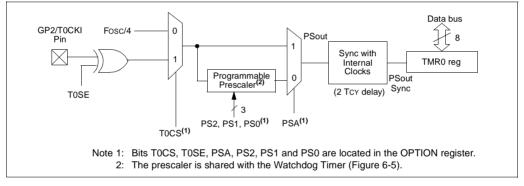

# 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 6.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

#### FIGURE 6-1: TIMER0 BLOCK DIAGRAM

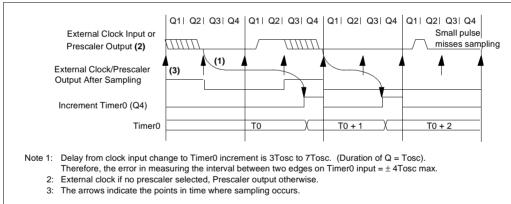

#### 6.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4ToSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

#### 6.1.3 OPTION REGISTER EFFECT ON GP2 TRIS

If the option register is set to read TIMER0 from the pin, the port is forced to an input regardless of the TRIS register setting.

#### FIGURE 6-4: TIMER0 TIMING WITH EXTERNAL CLOCK

# 7.0 EEPROM PERIPHERAL OPERATION

# This section applies to PIC12CE518 and PIC12CE519 only.

The PIC12CE518 and PIC12CE519 each have 16 bytes of EEPROM data memory. The EEPROM memory has an endurance of 1,000,000 erase/write cycles and a data retention of greater than 40 years. The EEPROM data memory supports a bi-directional 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), that are mapped to bit6 and bit7, respectively, of the GPIO register (SFR 06h). Unlike the GP0-GP5 that are connected to the internal EEPROM peripheral. For most applications, all that is required is calls to the following functions:

; Byte\_Write: Byte write routine Inputs: EEPROM Address EEADDR : ; EEPROM Data EEDATA Outputs: Return 01 in W if OK, else ; return 00 in W ; ; Read\_Current: Read EEPROM at address currently held by EE device. Inputs: NONE ; Outputs: EEPROM Data EEDATA ; Return 01 in W if OK, else ; return 00 in W ; ; Read\_Random: Read EEPROM byte at supplied address Inputs: EEPROM Address : FFADDR ; Outputs: EEPROM Data EEDATA Return 01 in W if OK, ; else return 00 in W

The code for these functions is available on our website www.microchip.com. The code will be accessed by either including the source code FL51XINC.ASM or by linking FLASH5IX.ASM.

It is very important to check the return codes when using these calls, and retry the operation if unsuccessful. Unsuccessful return codes occur when the EE data memory is busy with the previous write, which can take up to 4 mS.

#### 7.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the device.

For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

The EEPROM interface is a 2-wire bus protocol consisting of data (SDA) and a clock (SCL). Although these lines are mapped into the GPIO register, they are not accessible as external pins; only to the internal EEPROM peripheral. SDA and SCL operation is also slightly different than GPO-GP5 as listed below. Namely, to avoid code overhead in modifying the TRIS register, both SDA and SCL are always outputs. To read data from the EEPROM peripheral requires outputting a '1' on SDA placing it in high-Z state, where only the internal 100K pull-up is active on the SDA line.

SDA:

Built-in 100K (typical) pull-up to VDD Open-drain (pull-down only) Always an output Outputs a '1' on reset

SCL: Full CMOS output Always an output Outputs a '1' on reset

The following example requires:

- · Code Space: 77 words

- RAM Space: 5 bytes (4 are overlayable)

- Stack Levels:1 (The call to the function itself. The functions do not call any lower level functions.)

- Timing:

- WRITE\_BYTE takes 328 cycles

- READ\_CURRENT takes 212 cycles

- READ\_RANDOM takes 416 cycles.

- IO Pins: 0 (No external IO pins are used)

This code must reside in the lower half of a page. The code achieves it's small size without additional calls through the use of a sequencing table. The table is a list of procedures that must be called in order. The table uses an ADDWF PCL,F instruction, effectively a computed goto, to sequence to the next procedure. However the ADDWF PCL,F instruction yields an 8 bit address, forcing the code to reside in the first 256 addresses of a page.

<sup>© 1999</sup> Microchip Technology Inc.

| BSF              | Bit Set f                                                                                                                    | BTFSS                                       | Bit Test f, Skip if Set                                                                                                         |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] BSF f,b                                                                                                              | Syntax:                                     | [label] BTFSS f,b                                                                                                               |  |  |  |

| Operands:        | $0 \le f \le 31$ $0 \le b \le 7$                                                                                             | Operands: $0 \le f \le 31$<br>$0 \le b < 7$ |                                                                                                                                 |  |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                                                                                    | Operation:                                  | skip if (f <b>) = 1</b>                                                                                                         |  |  |  |

| Status Affected: | None                                                                                                                         | Status Affected:                            | None                                                                                                                            |  |  |  |

| Encoding:        | 0101 bbbf ffff                                                                                                               | Encoding:                                   | 0111 bbbf ffff                                                                                                                  |  |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                                                                              | Description:                                | If bit 'b' in register 'f' is '1' then the next                                                                                 |  |  |  |

| Words:           | 1                                                                                                                            |                                             | instruction is skipped.                                                                                                         |  |  |  |

| Cycles:          | 1                                                                                                                            |                                             | If bit 'b' is '1', then the next instruction<br>fetched during the current instruction<br>execution, is discarded and an NOP is |  |  |  |

| Example:         | BSF FLAG_REG, 7                                                                                                              |                                             |                                                                                                                                 |  |  |  |

| Before Instru    | uction                                                                                                                       |                                             | executed instead, making this a 2 cycle instruction.                                                                            |  |  |  |

| _                | EG = 0x0A                                                                                                                    | Words:                                      | 1                                                                                                                               |  |  |  |

| After Instruc    | tion<br>EG = 0x8A                                                                                                            | Cycles:                                     | 1(2)                                                                                                                            |  |  |  |

| FLAG_K           |                                                                                                                              | Example:                                    | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CODE                                                                                    |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                    |                                             | TRUE •                                                                                                                          |  |  |  |

| Syntax:          | [ label ] BTFSC f,b                                                                                                          |                                             | •                                                                                                                               |  |  |  |

| Operands:        | $0 \le f \le 31$                                                                                                             | Before Instr                                | uction                                                                                                                          |  |  |  |

|                  | $0 \le b \le 7$                                                                                                              | PC                                          | = address (HERE)                                                                                                                |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                      | After Instruc                               |                                                                                                                                 |  |  |  |

| Status Affected: | None                                                                                                                         | If FLAG<br>PC                               | <1> = 0,<br>= address (FALSE);                                                                                                  |  |  |  |

| Encoding:        | 0110 bbbf ffff                                                                                                               | if FLAG<                                    | <1> = 1,                                                                                                                        |  |  |  |

| Description:     | If bit 'b' in register 'f' is 0 then the next instruction is skipped.                                                        | PC                                          | = address (TRUE)                                                                                                                |  |  |  |

|                  | If bit 'b' is 0 then the next instruction<br>fetched during the current instruction<br>execution is discarded, and an NOP is |                                             |                                                                                                                                 |  |  |  |

executed instead, making this a 2 cycle

BTFSC FLAG,1

address (HERE)

address (TRUE);

address(FALSE)

PROCESS\_CODE

GOTO

٠ •

0, =

1, =

instruction.

1

1(2)

HERE

TRUE

Before Instruction PC

After Instruction if FLAG<1>

if FLAG<1>

PC

PC

FALSE

=

=

=

Words:

Cycles:

Example:

| CALL                  | Subroutine Call                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:               | [ <i>label</i> ] CALL k                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Operation:            | $\begin{array}{l} (PC) + 1 \rightarrow \text{Top of Stack;} \\ k \rightarrow PC < 7:0 >; \\ (STATUS < 6:5 >) \rightarrow PC < 10:9 >; \\ 0 \rightarrow PC < 8 > \end{array}$                                                                   |  |  |  |  |  |  |

| Status Affected:      | None                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Encoding:             | 1001 kkkk kkkk                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Description:          | Subroutine call. First, return address (PC+1) is pushed onto the stack. The eight bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STA-TUS<6:5>, PC<8> is cleared. CALL is a two cycle instruction. |  |  |  |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Cycles:               | 2                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Example:              | HERE CALL THERE                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Before Instru<br>PC = |                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                       | tion<br>address (THERE)<br>address (HERE + 1)                                                                                                                                                                                                  |  |  |  |  |  |  |

### CLRF

| Syntax:                        | [label] CLRF f                                                         |           |   |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------|-----------|---|--|--|--|--|

| Operands:                      | $0 \le f \le 31$                                                       |           |   |  |  |  |  |

| Operation:                     | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |           |   |  |  |  |  |

| Status Affected: Z             |                                                                        |           |   |  |  |  |  |

| Encoding:                      | 0000 011f ffff                                                         |           |   |  |  |  |  |

| Description:                   | The contents of register 'f' are cleared and the Z bit is set.         |           |   |  |  |  |  |

| Words:                         | 1                                                                      |           |   |  |  |  |  |

| Cycles:                        | 1                                                                      |           |   |  |  |  |  |

| Example:                       | CLRF                                                                   | FLAG_REC  | 3 |  |  |  |  |

| Before Instru<br>FLAG_RE       |                                                                        | 0x5A      |   |  |  |  |  |

| After Instruct<br>FLAG_RE<br>Z |                                                                        | 0x00<br>1 |   |  |  |  |  |

Clear f

| CLRW                                                                                                     | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation:                                                                                               | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}); \\ 1 \rightarrow \text{Z} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                                                                                             | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                                 | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Before Instru<br>W =                                                                                     | uction<br>0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| After Instruct<br>W =<br>Z =                                                                             | tion<br>0x00<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |