Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 5                                                                            |

| Program Memory Size        | 768B (512 x 12)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                |                                                                              |

| RAM Size                   | 25 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 8-SOIJ                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc508a-04i-sm |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

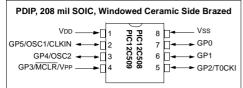

#### Pin Diagram - PIC12C508/509

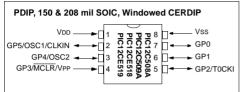

### Pin Diagram - PIC12C508A/509A, PIC12CE518/519

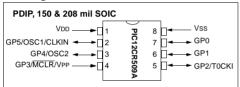

#### Pin Diagram - PIC12CR509A

#### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

#### TABLE OF CONTENTS

| 1.0   | General Description                                                                   | 4   |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | PIC12C5XX Device Varieties                                                            |     |

| 3.0   | Architectural Overview                                                                |     |

| 4.0   | Memory Organization                                                                   | 13  |

| 5.0   | I/O Port                                                                              |     |

| 6.0   | Timer0 Module and TMR0 Register                                                       | 25  |

| 7.0   | EEPROM Peripheral Operation                                                           | 29  |

| 8.0   | Special Features of the CPU                                                           | 35  |

| 9.0   | Instruction Set Summary                                                               | 47  |

| 10.0  | Development Support                                                                   |     |

| 11.0  | Electrical Characteristics - PIC12C508/PIC12C509                                      | 65  |

| 12.0  | DC and AC Characteristics - PIC12C508/PIC12C509                                       | 75  |

| 13.0  | Electrical Characteristics PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CR509A/ |     |

|       | PIC12CE518/PIC12CE519/                                                                |     |

|       | PIC12LCE518/PIC12LCE519/PIC12LCR509A                                                  | 79  |

| 14.0  | DC and AC Characteristics                                                             |     |

|       | PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CE518/PIC12CE519/PIC12CR509A/      |     |

|       | PIC12LCE518/PIC12LCE519/ PIC12LCR509A                                                 | 93  |

| 15.0  | Packaging Information                                                                 | 99  |

| Index | ۲                                                                                     | 105 |

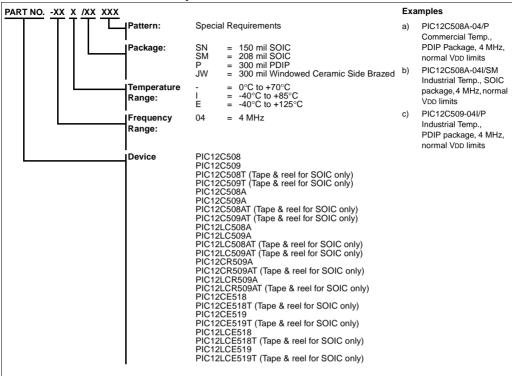

|       | 2C5XX Product Identification System                                                   |     |

| Sales | and Support:                                                                          | 109 |

#### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

NOTES:

#### 4.4 OPTION Register

The OPTION register is a 8-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A RESET sets the OPTION<7:0> bits.

#### FIGURE 4-5: OPTION REGISTER

Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin; i.e., note that TRIS overrides OPTION control of GPPU and GPWU.

**Note:** If the TOCS bit is set to '1', GP2 is forced to be an input even if TRIS GP2 = '0'.

| W-1      | W-1                                                  | W-1           | W-1         | W-1          | W-1         | W-1 | W-1  |                                                                                               |

|----------|------------------------------------------------------|---------------|-------------|--------------|-------------|-----|------|-----------------------------------------------------------------------------------------------|

| GPWU     | GPPU                                                 | TOCS          | T0SE        | PSA          | PS2         | PS1 | PS0  | W = Writable bit                                                                              |

| oit7     | 6                                                    | 5             | 4           | 3            | 2           | 1   | bit0 | U = Unimplemented bit<br>- n = Value at POR reset<br>Reference Table 4-1 for<br>other resets. |

| bit 7:   | <b>GPWU</b> : Ena<br>1 = Disable<br>0 = Enable       | d             | p on pin cl | hange (GP    | 0, GP1, GP3 | )   |      |                                                                                               |

| bit 6:   | <b>GPPU</b> : Ena<br>1 = Disable<br>0 = Enablec      | d .           | III-ups (GF | 90, GP1, G   | P3)         |     |      |                                                                                               |

| bit 5:   | <b>TOCS</b> : Time<br>1 = Transitio<br>0 = Transitio | on on TOCK    | l pin       |              | ock, Fosc/4 |     |      |                                                                                               |

| bit 4:   | TOSE: Time<br>1 = Increme<br>0 = Increme             | ent on high t | o low trans | sition on th |             |     |      |                                                                                               |

| bit 3:   | <b>PSA</b> : Presc<br>1 = Prescale<br>0 = Prescale   | er assigned   | to the WD   |              |             |     |      |                                                                                               |

| bit 2-0: | PS2:PS0: P                                           | Prescaler rat | e select bi | its          |             |     |      |                                                                                               |

|          | Bit Value                                            | Timer0 R      | ate WDT     | Rate         |             |     |      |                                                                                               |

|          | 000                                                  | 1:2<br>1:4    | 1:          | 2            |             |     |      |                                                                                               |

|          | 010<br>011                                           | 1:8           | 1:          |              |             |     |      |                                                                                               |

|          | 100                                                  | 1:32          |             | 0<br>16      |             |     |      |                                                                                               |

|          | 101                                                  | 1:64          |             | 32           |             |     |      |                                                                                               |

|          | 110                                                  | 1:128         |             | 64           |             |     |      |                                                                                               |

|          | 111                                                  | 1:256         | : 1.        | 128          |             |     |      |                                                                                               |

NOTES:

#### 7.0 EEPROM PERIPHERAL OPERATION

### This section applies to PIC12CE518 and PIC12CE519 only.

The PIC12CE518 and PIC12CE519 each have 16 bytes of EEPROM data memory. The EEPROM memory has an endurance of 1,000,000 erase/write cycles and a data retention of greater than 40 years. The EEPROM data memory supports a bi-directional 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), that are mapped to bit6 and bit7, respectively, of the GPIO register (SFR 06h). Unlike the GP0-GP5 that are connected to the internal EEPROM peripheral. For most applications, all that is required is calls to the following functions:

; Byte\_Write: Byte write routine Inputs: EEPROM Address EEADDR : ; EEPROM Data EEDATA Outputs: Return 01 in W if OK, else ; return 00 in W ; ; Read\_Current: Read EEPROM at address currently held by EE device. Inputs: NONE ; Outputs: EEPROM Data EEDATA ; Return 01 in W if OK, else ; return 00 in W ; ; Read\_Random: Read EEPROM byte at supplied address Inputs: EEPROM Address : FFADDR ; Outputs: EEPROM Data EEDATA Return 01 in W if OK, ; else return 00 in W

The code for these functions is available on our website www.microchip.com. The code will be accessed by either including the source code FL51XINC.ASM or by linking FLASH5IX.ASM.

It is very important to check the return codes when using these calls, and retry the operation if unsuccessful. Unsuccessful return codes occur when the EE data memory is busy with the previous write, which can take up to 4 mS.

#### 7.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the device.

For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

The EEPROM interface is a 2-wire bus protocol consisting of data (SDA) and a clock (SCL). Although these lines are mapped into the GPIO register, they are not accessible as external pins; only to the internal EEPROM peripheral. SDA and SCL operation is also slightly different than GPO-GP5 as listed below. Namely, to avoid code overhead in modifying the TRIS register, both SDA and SCL are always outputs. To read data from the EEPROM peripheral requires outputting a '1' on SDA placing it in high-Z state, where only the internal 100K pull-up is active on the SDA line.

SDA:

Built-in 100K (typical) pull-up to VDD Open-drain (pull-down only) Always an output Outputs a '1' on reset

SCL: Full CMOS output Always an output Outputs a '1' on reset

The following example requires:

- · Code Space: 77 words

- RAM Space: 5 bytes (4 are overlayable)

- Stack Levels:1 (The call to the function itself. The functions do not call any lower level functions.)

- Timing:

- WRITE\_BYTE takes 328 cycles

- READ\_CURRENT takes 212 cycles

- READ\_RANDOM takes 416 cycles.

- IO Pins: 0 (No external IO pins are used)

This code must reside in the lower half of a page. The code achieves it's small size without additional calls through the use of a sequencing table. The table is a list of procedures that must be called in order. The table uses an ADDWF PCL,F instruction, effectively a computed goto, to sequence to the next procedure. However the ADDWF PCL,F instruction yields an 8 bit address, forcing the code to reside in the first 256 addresses of a page.

<sup>© 1999</sup> Microchip Technology Inc.

#### 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

### 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

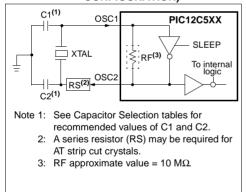

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

#### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

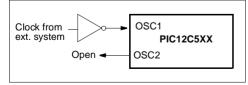

#### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

#### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 8-4 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

#### FIGURE 8-4: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

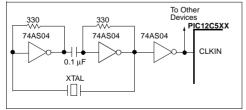

Figure 8-5 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 8-5: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

#### 8.2.4 EXTERNAL RC OSCILLATOR

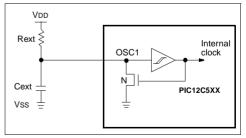

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 8-6 shows how the R/C combination is connected to the PIC12C5XX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

### FIGURE 8-6: EXTERNAL RC OSCILLATOR MODE

#### 8.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and 25°C, see "Electrical Specifications" section for information on variation over voltage and temperature.

In addition, a calibration instruction is programmed into the top of memory which contains the calibration value for the internal RC oscillator. This location is never code protected regardless of the code protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the reset vector. This will load the W register with the calibration value upon reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part. so it can be reprogrammed correctly later.

For the PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, and PIC12CR509A, bits <7:2>, CAL5-CAL0 are used for calibration. Adjusting CAL5-0 from 000000 to 111111 yields a higher clock speed. Note that bits 1 and 0 of OSCCAL are unimplemented and should be written as 0 when modifying OSCCAL for compatibility with future devices.

For the PIC12C508 and PIC12C509, the upper 4 bits of the register are used. Writing a larger value in this location yields a higher clock speed.

#### 8.3 <u>RESET</u>

The device differentiates between various kinds of reset:

- a) Power on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT time-out reset during normal operation

- e) WDT time-out reset during SLEEP

- f) Wake-up from SLEEP on pin change

Some registers are not reset in any way; they are unknown on POR and unchanged in any other reset. Most other registers are reset to "reset state" on poweron reset (POR),  $\overline{MCLR}$ , WDT or wake-up on pin change reset during normal operation. They are not affected by a WDT reset during SLEEP or  $\overline{MCLR}$  reset during SLEEP, since these resets are viewed as resumption of normal operation. The exceptions to this are  $\overline{TO}$ ,  $\overline{PD}$ , and GPWUF bits. They are set or cleared differently in different reset situations. These bits are used in software to determine the nature of reset. See Table 8-3 for a full description of reset states of all registers.

#### 8.7 <u>Time-Out Sequence, Power Down,</u> and Wake-up from SLEEP Status Bits (TO/PD/GPWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits in the STATUS register can be tested to determine if a RESET condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) reset.

| TABLE 8-7: | TO/PD/GPWUF STATUS |

|------------|--------------------|

|            | AFTER RESET        |

| GPWUF | то | PD | RESET caused by                     |

|-------|----|----|-------------------------------------|

| 0     | 0  | 0  | WDT wake-up from<br>SLEEP           |

| 0     | 0  | u  | WDT time-out (not from<br>SLEEP)    |

| 0     | 1  | 0  | MCLR wake-up from<br>SLEEP          |

| 0     | 1  | 1  | Power-up                            |

| 0     | u  | u  | MCLR not during SLEEP               |

| 1     | 1  | 0  | Wake-up from SLEEP on<br>pin change |

Legend: u = unchanged

Note 1: The TO, PD, and GPWUF bits maintain their status (u) until a reset occurs. A lowpulse on the MCLR input does not change the TO, PD, and GPWUF status bits.

#### 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

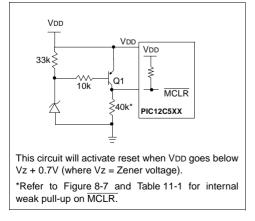

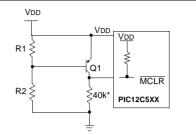

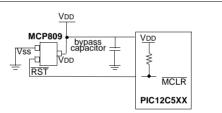

To reset PIC12C5XX devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-13 , Figure 8-14 and Figure 8-15

#### FIGURE 8-13: BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

\*Refer to Figure 8-7 and Table 11-1 for internal weak pull-up on MCLR.

#### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX family of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accomodate 5V and 3V systems.

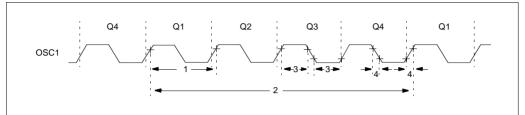

#### 11.4 Timing Diagrams and Specifications

| AC Chara         | cteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq Ta \leq +70^{\circ}C \mbox{ (commercial)}, \\ -40^{\circ}C \leq Ta \leq +85^{\circ}C \mbox{ (industrial)}, \\ -40^{\circ}C \leq Ta \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 11.1} \end{array}$ |     |                    |        |       |                |  |  |

|------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|--------|-------|----------------|--|--|

| Parameter<br>No. | Sym        | Characteristic                                                                                                                                                                                                                                                                                                                                                                                  | Min | Typ <sup>(1)</sup> | Мах    | Units | Conditions     |  |  |

|                  | Fosc       | External CLKIN Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                         |     |                    |        |       |                |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | DC  | —                  | 4      | MHz   | XT osc mode    |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

|                  |            | Oscillator Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                             |     |                    |        |       |                |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | 0.1 | _                  | 4      | MHz   | XT osc mode    |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

| 1                | Tosc       | External CLKIN Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                            | 250 | —                  | _      | ns    | EXTRC osc mode |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | 250 | _                  | _      | ns    | XT osc mode    |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | 5   | —                  | —      | ms    | LP osc mode    |  |  |

|                  |            | Oscillator Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                | 250 | _                  | _      | ns    | EXTRC osc mode |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | 250 | _                  | 10,000 | ns    | XT osc mode    |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | 5   | —                  | —      | ms    | LP osc mode    |  |  |

| 2                | Тсу        | Instruction Cycle Time <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                           | —   | 4/Fosc             | —      |       |                |  |  |

| 3                | TosL, TosH | Clock in (OSC1) Low or High Time                                                                                                                                                                                                                                                                                                                                                                | 50* | —                  | —      | ns    | XT oscillator  |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | 2*  | _                  | —      | ms    | LP oscillator  |  |  |

| 4                | TosR, TosF | Clock in (OSC1) Rise or Fall Time                                                                                                                                                                                                                                                                                                                                                               | —   | -                  | 25*    | ns    | XT oscillator  |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                 | —   | —                  | 50*    | ns    | LP oscillator  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

3: Instruction cycle period (TCY) equals four times the input oscillator time base period.

#### TABLE 11-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC12C508/C509

|                                  |     | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ (commercial)}, \\ -40^\circ C \leq TA \leq +85^\circ C \mbox{ (industrial)}, \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 10.1} \\ \end{array} $ |      |                    |      |       |            |

|----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|-------|------------|

| Parameter<br>No.                 | Sym | Characteristic                                                                                                                                                                                                                                                                                                                                                                                 | Min* | Typ <sup>(1)</sup> | Max* | Units | Conditions |

| Internal Calibrated RC Frequency |     | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                                                                                               | 3.58 | 4.00               | 4.32 | MHz   | VDD = 5.0V |

| Internal Calibrated RC Frequency |     | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                                                                                               | 3.50 | —                  | 4.26 | MHz   | VDD = 2.5V |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

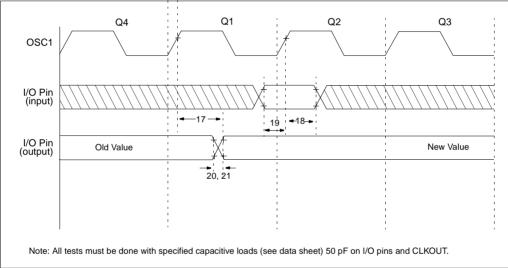

#### FIGURE 11-3: I/O TIMING - PIC12C508/C509

| Oscillator  | Frequency | VDD = 2.5V | VDD = 5.5V |

|-------------|-----------|------------|------------|

| External RC | 4 MHz     | 250 µA*    | 780 µA*    |

| Internal RC | 4 MHz     | 420 µA     | 1.1 mA     |

| XT          | 4 MHz     | 251 µA     | 780 µA     |

| LP          | 32 KHz    | 15 µA      | 37 µA      |

#### TABLE 12-1: DYNAMIC IDD (TYPICAL) - WDT ENABLED, 25°C

\*Does not include current through external R&C.

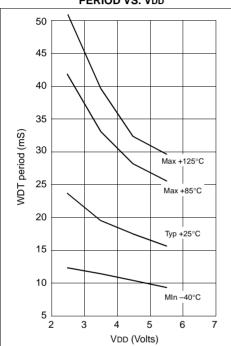

#### FIGURE 12-3: WDT TIMER TIME-OUT PERIOD VS. VDD

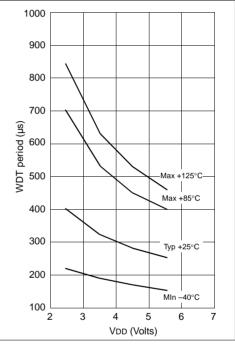

#### FIGURE 12-4: SHORT DRT PERIOD VS. VDD

NOTES:

#### 13.6 Timing Diagrams and Specifications

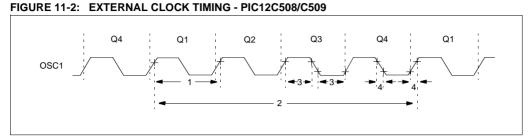

#### FIGURE 13-2: EXTERNAL CLOCK TIMING - PIC12C508A, PIC12C509A, PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

#### TABLE 13-2: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| AC Chara         | cteristics | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq Ta \leq +70^{\circ}C \mbox{ (commercial)}, \\ -40^{\circ}C \leq Ta \leq +85^{\circ}C \mbox{ (industrial)}, \\ -40^{\circ}C \leq Ta \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 13.1} \end{array}$ |     |                    |        |       |                |  |

|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|--------|-------|----------------|--|

| Parameter<br>No. | Sym        | Characteristic                                                                                                                                                                                                                                                                                                                                                                                 | Min | Typ <sup>(1)</sup> | Max    | Units | Conditions     |  |

|                  | Fosc       | External CLKIN Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                        |     |                    |        |       |                |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | DC  | —                  | 4      | MHz   | XT osc mode    |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | DC  | —                  | 200    | kHz   | LP osc mode    |  |

|                  |            | Oscillator Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                            | DC  | —                  | 4      | MHz   | EXTRC osc mode |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | 0.1 | —                  | 4      | MHz   | XT osc mode    |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | DC  | —                  | 200    | kHz   | LP osc mode    |  |

| 1                | Tosc       | External CLKIN Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                           |     |                    |        |       |                |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | 250 | —                  | —      | ns    | XT osc mode    |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | 5   | —                  | —      | ms    | LP osc mode    |  |

|                  |            | Oscillator Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                               | 250 | —                  | —      | ns    | EXTRC osc mode |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | 250 | —                  | 10,000 | ns    | XT osc mode    |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | 5   | —                  | —      | ms    | LP osc mode    |  |

| 2                | Тсу        | Instruction Cycle Time <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                          | _   | 4/Fosc             | —      | —     |                |  |

| 3                | TosL, TosH | Clock in (OSC1) Low or High Time                                                                                                                                                                                                                                                                                                                                                               | 50* | -                  | —      | ns    | XT oscillator  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | 2*  | _                  | —      | ms    | LP oscillator  |  |

| 4                | TosR, TosF | Clock in (OSC1) Rise or Fall Time                                                                                                                                                                                                                                                                                                                                                              | —   | -                  | 25*    | ns    | XT oscillator  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                | _   | _                  | 50*    | ns    | LP oscillator  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

3: Instruction cycle period (TCY) equals four times the input oscillator time base period.

#### TABLE 13-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| AC Characteristics |     | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ (commercial)}, \\ & -40^\circ C \leq TA \leq +85^\circ C \mbox{ (industrial)}, \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 10.1} \end{array}$ |      |                    |      |       |            |  |  |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|-------|------------|--|--|

| Parameter<br>No.   | Sym | Characteristic                                                                                                                                                                                                                                                                                                                                                                                | Min* | Typ <sup>(1)</sup> | Max* | Units | Conditions |  |  |

|                    |     | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                                                                                              | 3.65 | 4.00               | 4.28 | MHz   | VDD = 5.0V |  |  |

|                    |     | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                                                                                              | 3.55 | —                  | 4.31 | MHz   | VDD = 2.5V |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 13-8: EEPROM MEMORY BUS TIMING REQUIREMENTS - PIC12CE5XX ONLY.

| AC Characteristics                                                                   | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ , Vcc = 3.0V to 5.5V (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ , Vcc = 3.0V to 5.5V (industrial) $-40^{\circ}C \leq TA \leq +125^{\circ}C$ , Vcc = 4.5V to 5.5V (extended)Operating Voltage VDD range is described in Section 13.1 |                      |                     |        |                                                                                                                                              |  |  |  |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                                                            | Symbol Min Max Units Conditions                                                                                                                                                                                                                                                                                                                                       |                      |                     |        |                                                                                                                                              |  |  |  |

| Clock frequency                                                                      | FCLK                                                                                                                                                                                                                                                                                                                                                                  |                      | 100<br>100<br>400   | kHz    | 4.5V ≤ Vcc ≤ 5.5V (E Temp range)<br>3.0V ≤ Vcc ≤ 4.5V<br>4.5V ≤ Vcc ≤ 5.5V                                                                   |  |  |  |

| Clock high time                                                                      | Тнідн                                                                                                                                                                                                                                                                                                                                                                 | 4000<br>4000<br>600  |                     | ns     |                                                                                                                                              |  |  |  |

| Clock low time                                                                       | TLOW                                                                                                                                                                                                                                                                                                                                                                  | 4700<br>4700<br>1300 |                     | ns     |                                                                                                                                              |  |  |  |

| SDA and SCL rise time<br>(Note 1)                                                    | TR                                                                                                                                                                                                                                                                                                                                                                    |                      | 1000<br>1000<br>300 | ns     |                                                                                                                                              |  |  |  |

| SDA and SCL fall time                                                                | TF                                                                                                                                                                                                                                                                                                                                                                    | _                    | 300                 | ns     | (Note 1)                                                                                                                                     |  |  |  |

| START condition hold time                                                            | THD:STA                                                                                                                                                                                                                                                                                                                                                               | 4000<br>4000<br>600  |                     | ns     |                                                                                                                                              |  |  |  |

| START condition setup time                                                           | TSU:STA                                                                                                                                                                                                                                                                                                                                                               | 4700<br>4700<br>600  |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \mbox{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| Data input hold time                                                                 | THD:DAT                                                                                                                                                                                                                                                                                                                                                               | 0                    |                     | ns     | (Note 2)                                                                                                                                     |  |  |  |

| Data input setup time                                                                | TSU:DAT                                                                                                                                                                                                                                                                                                                                                               | 250<br>250<br>100    |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \mbox{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| STOP condition setup time                                                            | Tsu:sto                                                                                                                                                                                                                                                                                                                                                               | 4000<br>4000<br>600  |                     | ns     | 4.5V ≤ Vcc ≤ 5.5V (E Temp range)<br>3.0V ≤ Vcc ≤ 4.5V<br>4.5V ≤ Vcc ≤ 5.5V                                                                   |  |  |  |

| Output valid from clock<br>(Note 2)                                                  | ΤΑΑ                                                                                                                                                                                                                                                                                                                                                                   |                      | 3500<br>3500<br>900 | ns     | 4.5V ≤ Vcc ≤ 5.5V (E Temp range)<br>3.0V ≤ Vcc ≤ 4.5V<br>4.5V ≤ Vcc ≤ 5.5V                                                                   |  |  |  |

| Bus free time: Time the bus must<br>be free before a new transmis-<br>sion can start | TBUF                                                                                                                                                                                                                                                                                                                                                                  | 4700<br>4700<br>1300 |                     | ns     | $\begin{array}{l} 4.5 V \leq V cc \leq 5.5 V \mbox{ (E Temp range)} \\ 3.0 V \leq V cc \leq 4.5 V \\ 4.5 V \leq V cc \leq 5.5 V \end{array}$ |  |  |  |

| Output fall time from VIH<br>minimum to VIL maximum                                  | TOF                                                                                                                                                                                                                                                                                                                                                                   | 20+0.1<br>CB         | 250                 | ns     | (Note 1), CB ≤ 100 pF                                                                                                                        |  |  |  |

| Input filter spike suppression (SDA and SCL pins)                                    | TSP                                                                                                                                                                                                                                                                                                                                                                   |                      | 50                  | ns     | (Notes 1, 3)                                                                                                                                 |  |  |  |

| Write cycle time                                                                     | Twc                                                                                                                                                                                                                                                                                                                                                                   | —                    | 4                   | ms     |                                                                                                                                              |  |  |  |

| Endurance                                                                            |                                                                                                                                                                                                                                                                                                                                                                       | 1M                   | _                   | cycles | 25°C, Vcc = 5.0V, Block Mode (Note 4)                                                                                                        |  |  |  |

Note 1: Not 100% tested. CB = total capacitance of one bus line in pF.

2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

**3:** The combined TSP and VHYS specifications are due to new Schmitt trigger inputs which provide improved noise spike suppression. This eliminates the need for a TI specification for standard operation.

4: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be obtained on Microchip's website.

NOTES:

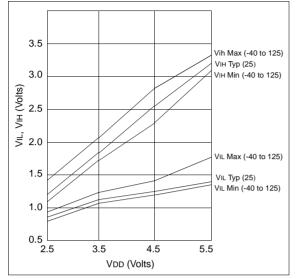

### FIGURE 14-15: VIL, VIH OF NMCLR, AND TOCKI VS. VDD

#### PIC12C5XX Product Identification System

Please contact your local sales office for exact ordering procedures.

#### Sales and Support:

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.