Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

-XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 5                                                                            |

| Program Memory Size        | 768B (512 x 12)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 25 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                                |

| Supplier Device Package    | 8-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc508a-04i-sn |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE OF CONTENTS

| 1.0   | General Description                                                                   | 4   |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | PIC12C5XX Device Varieties                                                            |     |

| 3.0   | Architectural Overview                                                                |     |

| 4.0   | Memory Organization                                                                   | 13  |

| 5.0   | I/O Port                                                                              |     |

| 6.0   | Timer0 Module and TMR0 Register                                                       | 25  |

| 7.0   | EEPROM Peripheral Operation                                                           | 29  |

| 8.0   | Special Features of the CPU                                                           | 35  |

| 9.0   | Instruction Set Summary                                                               | 47  |

| 10.0  | Development Support                                                                   |     |

| 11.0  | Electrical Characteristics - PIC12C508/PIC12C509                                      | 65  |

| 12.0  | DC and AC Characteristics - PIC12C508/PIC12C509                                       | 75  |

| 13.0  | Electrical Characteristics PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CR509A/ |     |

|       | PIC12CE518/PIC12CE519/                                                                |     |

|       | PIC12LCE518/PIC12LCE519/PIC12LCR509A                                                  | 79  |

| 14.0  | DC and AC Characteristics                                                             |     |

|       | PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CE518/PIC12CE519/PIC12CR509A/      |     |

|       | PIC12LCE518/PIC12LCE519/ PIC12LCR509A                                                 | 93  |

| 15.0  | Packaging Information                                                                 | 99  |

| Index | ۲                                                                                     | 105 |

|       | 2C5XX Product Identification System                                                   |     |

| Sales | and Support:                                                                          | 109 |

#### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

# 2.0 PIC12C5XX DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12C5XX Product Identification System at the back of this data sheet to specify the correct part number.

### 2.1 UV Erasable Devices

The UV erasable version, offered in ceramic side brazed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

Microchip's PICSTART<sup>®</sup> PLUS and PRO MATE<sup>®</sup> programmers all support programming of the PIC12C5XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

### 2.5 Read Only Memory (ROM) Device

Microchip offers masked ROM to give the customer a low cost option for high volume, mature products.

NOTES:

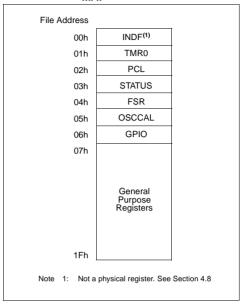

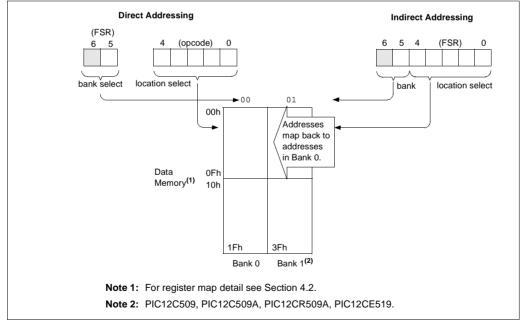

#### 4.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: special function registers and general purpose registers.

The special function registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports), and the File Select Register (FSR). In addition, special purpose registers are used to control the I/O port configuration and prescaler options.

The general purpose registers are used for data and control information under command of the instructions.

For the PIC12C508, PIC12C508A and PIC12CE518, the register file is composed of 7 special function registers and 25 general purpose registers (Figure 4-2).

For the PIC12C509, PIC12C509A, PIC12CR509A, and PIC12CE519 the register file is composed of 7 special function registers, 25 general purpose registers, and 16 general purpose registers that may be addressed using a banking scheme (Figure 4-3).

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The general purpose register file is accessed either directly or indirectly through the file select register FSR (Section 4.8).

#### FIGURE 4-2: PIC12C508, PIC12C508A AND PIC12CE518 REGISTER FILE MAP

| FSR<6:5>-    | •    | 00                  | 01                       |

|--------------|------|---------------------|--------------------------|

| File Address | · ·  |                     | 1                        |

| 00h          |      | INDF <sup>(1)</sup> | 20h                      |

| <b>∲</b> 01h |      | TMR0                |                          |

| 02h          |      | PCL                 | _                        |

| 03h          |      | STATUS              | Addresses map<br>back to |

| 04h          |      | FSR                 | addresses                |

| 05h          |      | OSCCAL              | in Bank 0.               |

| 06h          |      | GPIO                |                          |

| 07h          |      |                     | 1                        |

|              |      | General<br>Purpose  |                          |

|              |      | Registers           |                          |

| 0Fh          |      | 0                   | 2Fh                      |

|              | 10h  |                     | 30h                      |

|              |      | General             | General                  |

|              |      | Purpose             | Purpose                  |

|              |      | Registers           | Registers                |

|              | 1Fh  |                     | 3Fh                      |

|              |      | Bank 0              | Bank 1                   |

| Note 1       | : No | t a physical regi   | ster. See Section 4.8    |

|              |      |                     |                          |

#### FIGURE 4-3: PIC12C509, PIC12C509A, PIC12CR509A AND PIC12CE519 REGISTER FILE MAP

#### 4.8 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 07 contains the value 10h

- · Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-2.

#### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw | 0x10  | ;initialize pointer |

|----------|-------|-------|---------------------|

|          | movwf | FSR   | ; to RAM            |

| NEXT     | clrf  | INDF  | clear INDF register |

|          | incf  | FSR,F | ;inc pointer        |

|          | btfsc | FSR,4 | ;all done?          |

|          | goto  | NEXT  | ;NO, clear next     |

| CONTINUE | 9     |       | -,                  |

|          | :     |       | ;YES, continue      |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC12C508/PIC12C508A/PIC12CE518:** Does not use banking. FSR<7:5> are unimplemented and read as '1's.

#### PIC12C509/PIC12C509A/PIC12CR509A/

**PIC12CE519:** Uses FSR<5>. Selects between bank 0 and bank 1. FSR<7:6> is unimplemented, read as '1'.

#### FIGURE 4-9: DIRECT/INDIRECT ADDRESSING

# 5.0 I/O PORT

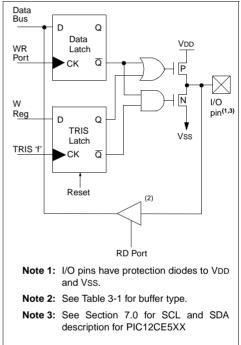

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

### 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the output data latches. That is, if an output      |

|-------|---------------------------------------------------------------------------------------------|

|       | driver on a pin is enabled and driven high,                                                 |

|       | but the external system is holding it low, a read of the port will indicate that the pin is |

|       | low.                                                                                        |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

### FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

| TABLE 5-1: S | UMMARY OF PORT | <b>REGISTERS</b> |

|--------------|----------------|------------------|

|--------------|----------------|------------------|

| Address | Name                                                                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|---------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------|

| N/A     | TRIS                                                                            | —     | -     |       |       |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | OPTION                                                                          | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                    |

| 03H     | STATUS                                                                          | GPWUF | -     | PAO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>     |

| 06h     | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CR509A) |       | _     | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                      |

| 06h     | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                             | SCL   | SDA   | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 11xx xxxx                     | 11uu uuuu                    |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, g = see tables in Section 8.7 for possible values.

Note 1: If reset was due to wake-up on change, then bit 7 = 1. All other resets will cause bit 7 = 0.

#### 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of GPIO will cause all eight bits of GPIO to be read into the CPU, bit5 to be set and the GPIO value to be written to the output latches. If another bit of GPIO is used as a bidirectional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}$  ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wiredand"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ; | ;Initial GPIO Settings |         |       |      |         |     |        |

|---|------------------------|---------|-------|------|---------|-----|--------|

| ; | ; GPIO<5:3> Inputs     |         |       |      |         |     |        |

| ; | GPIO<2                 | 2:0> Ou | itput | s    |         |     |        |

| ; |                        |         |       |      |         |     |        |

| ; |                        |         |       | GPIC | ) latch | GPI | ) pins |

| ; |                        |         |       |      |         |     |        |

|   | BCF                    | GPIO,   | 5     | ;01  | -ppp    | 11  | pppp   |

|   | BCF                    | GPIO,   | 4     | ;10  | -ppp    | 11  | pppp   |

|   | MOVLW                  | 007h    |       | ;    |         |     |        |

|   | TRIS                   | GPIO    |       | ;10  | -ppp    | 11  | pppp   |

|   |                        |         |       |      |         |     |        |

;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;GP5 to be latched as the pin value (High).

# 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

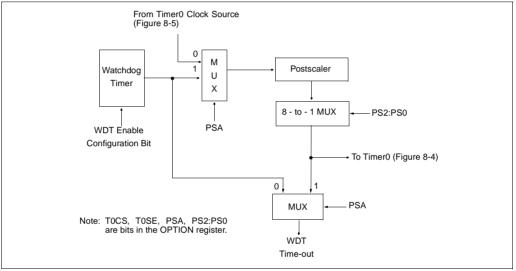

#### 8.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 8.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT wake-up reset.

#### FIGURE 8-12: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 8-6: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer, - = unimplemented, read as '0', u = unchanged

# 9.0 INSTRUCTION SET SUMMARY

Each PIC12C5XX instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC12C5XX instruction set summary in Table 9-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 9-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

#### TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is<br>the recommended form of use for compatibility<br>with all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| WDT           | Watchdog Timer Counter                                                                                                                                                         |

| TO            | Time-Out bit                                                                                                                                                                   |

| PD            | Power-Down bit                                                                                                                                                                 |

| dest          | Destination, either the W register or the specified register file location                                                                                                     |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1 µs. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2 µs.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

# FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                                   |                                                                                       |      |        |        |             |   |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|--------|--------|-------------|---|--|--|

|                                                                                                          | 11                                                                                    | 6    | 5      | 4      |             | 0 |  |  |

|                                                                                                          | OPCODE                                                                                |      | d      |        | f (FILE #)  |   |  |  |

|                                                                                                          | d = 0 for destination W<br>d = 1 for destination f<br>f = 5-bit file register address |      |        |        |             |   |  |  |

| Bi                                                                                                       | t-oriented file regi                                                                  | iste | er ope | eratio | ins         |   |  |  |

|                                                                                                          | 11                                                                                    | 8    | 7      | 5      | 4           | 0 |  |  |

|                                                                                                          | OPCODE                                                                                |      | b (B   | IT #)  | f (FILE #)  |   |  |  |

| b = 3-bit bit address<br>f = 5-bit file register address<br>Literal and control operations (except GOTO) |                                                                                       |      |        |        |             |   |  |  |

|                                                                                                          | 11                                                                                    |      | 8      | 7      |             | 0 |  |  |

|                                                                                                          | OPCODE                                                                                |      |        |        | k (literal) |   |  |  |

| k = 8-bit immediate value                                                                                |                                                                                       |      |        |        |             |   |  |  |

| Literal and control operations - GOTO instruction                                                        |                                                                                       |      |        |        |             |   |  |  |

| r                                                                                                        | 11                                                                                    |      | 9      | 8      |             | 0 |  |  |

|                                                                                                          | OPCODE                                                                                |      |        |        | k (literal) |   |  |  |

|                                                                                                          |                                                                                       |      |        |        |             |   |  |  |

k = 9-bit immediate value

| ADDWF                                                           | Add W and f                                                                                                                                                                |  |  |  |  |  |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                         | [ label ] ADDWF f,d                                                                                                                                                        |  |  |  |  |  |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                                |  |  |  |  |  |

| Operation:                                                      | (W) + (f) $\rightarrow$ (dest)                                                                                                                                             |  |  |  |  |  |

| Status Affected:                                                | C, DC, Z                                                                                                                                                                   |  |  |  |  |  |

| Encoding:                                                       | 0001 11df ffff                                                                                                                                                             |  |  |  |  |  |

| Description:                                                    | Add the contents of the W register and<br>register 'f'. If 'd' is 0 the result is stored<br>in the W register. If 'd' is '1' the result is<br>stored back in register 'f'. |  |  |  |  |  |

| Words:                                                          | 1                                                                                                                                                                          |  |  |  |  |  |

| Cycles:                                                         | 1                                                                                                                                                                          |  |  |  |  |  |

| Example:                                                        | ADDWF FSR, 0                                                                                                                                                               |  |  |  |  |  |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>tion<br>0xD9                                                                                                                                               |  |  |  |  |  |

| ANDWF                          | AND W with f                                                                                                                                                                       |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] ANDWF f,d                                                                                                                                                                  |

| Operands:                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                                        |

| Operation:                     | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                 |

| Status Affected:               | Z                                                                                                                                                                                  |

| Encoding:                      | 0001 01df ffff                                                                                                                                                                     |

| Description:                   | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>'1' the result is stored back in register 'f'. |

| Words:                         | 1                                                                                                                                                                                  |

| Cycles:                        | 1                                                                                                                                                                                  |

| Example:                       | ANDWF FSR, 1                                                                                                                                                                       |

| Before Instru<br>W =<br>FSR =  | 0x17                                                                                                                                                                               |

| After Instruct<br>W =<br>FSR = | 0x17                                                                                                                                                                               |

| ANDLW                 | And literal with W                                                                                                      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:               | [ <i>label</i> ] ANDLW k                                                                                                |

| Operands:             | $0 \le k \le 255$                                                                                                       |

| Operation:            | (W).AND. (k) $\rightarrow$ (W)                                                                                          |

| Status Affected:      | Z                                                                                                                       |

| Encoding:             | 1110 kkkk kkkk                                                                                                          |

| Description:          | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'. The<br>result is placed in the W register. |

| Words:                | 1                                                                                                                       |

| Cycles:               | 1                                                                                                                       |

| Example:              | ANDLW 0x5F                                                                                                              |

| Before Instru<br>W =  | iction<br>0xA3                                                                                                          |

| After Instruct<br>W = | tion<br>0x03                                                                                                            |

| BCF                     | Bit Clear                                                          | f             |          |  |

|-------------------------|--------------------------------------------------------------------|---------------|----------|--|

| Syntax:                 | [ <i>label</i> ] E                                                 | BCF f,b       | )        |  |

| Operands:               | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |               |          |  |

| Operation:              | $0 \rightarrow (f < b;$                                            | >)            |          |  |

| Status Affected:        | None                                                               |               |          |  |

| Encoding:               | 0100                                                               | bbbf          | ffff     |  |

| Description:            | Bit 'b' in re                                                      | gister 'f' is | cleared. |  |

| Words:                  | 1                                                                  |               |          |  |

| Cycles:                 | 1                                                                  |               |          |  |

| Example:                | BCF                                                                | FLAG_REC      | 3, 7     |  |

| Before Instru<br>FLAG_R | iction<br>EG = 0xC7                                                | 7             |          |  |

| After Instruc<br>FLAG_R | tion<br>EG = 0x47                                                  |               |          |  |

| BSF              | Bit Set f                                                                                                                    | BTFSS            | Bit Test f, Skip if Set                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------|

| Syntax:          | [label] BSF f,b                                                                                                              | Syntax:          | [label] BTFSS f,b                                                                   |

| Operands:        | $0 \le f \le 31$ $0 \le b \le 7$                                                                                             | Operands:        | $0 \le f \le 31$<br>$0 \le b < 7$                                                   |

| Operation:       | $1 \rightarrow (f < b >)$                                                                                                    | Operation:       | skip if (f <b>) = 1</b>                                                             |

| Status Affected: | None                                                                                                                         | Status Affected: | None                                                                                |

| Encoding:        | 0101 bbbf ffff                                                                                                               | Encoding:        | 0111 bbbf ffff                                                                      |

| Description:     | Bit 'b' in register 'f' is set.                                                                                              | Description:     | If bit 'b' in register 'f' is '1' then the next                                     |

| Words:           | 1                                                                                                                            |                  | instruction is skipped.                                                             |

| Cycles:          | 1                                                                                                                            |                  | If bit 'b' is '1', then the next instruction fetched during the current instruction |

| Example:         | BSF FLAG_REG, 7                                                                                                              |                  | execution, is discarded and an NOP is                                               |

| Before Instru    | uction                                                                                                                       |                  | executed instead, making this a 2 cycle instruction.                                |

| _                | EG = 0x0A                                                                                                                    | Words:           | 1                                                                                   |

| After Instruc    | tion<br>EG = 0x8A                                                                                                            | Cycles:          | 1(2)                                                                                |

| FLAG_K           |                                                                                                                              | Example:         | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CODE                                        |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                    |                  | TRUE •                                                                              |

| Syntax:          | [ label ] BTFSC f,b                                                                                                          |                  | •                                                                                   |

| Operands:        | $0 \le f \le 31$                                                                                                             | Before Instr     | uction                                                                              |

|                  | $0 \le b \le 7$                                                                                                              | PC               | = address (HERE)                                                                    |

| Operation:       | skip if $(f < b >) = 0$                                                                                                      | After Instruc    |                                                                                     |

| Status Affected: | None                                                                                                                         | If FLAG<br>PC    | <1> = 0,<br>= address (FALSE);                                                      |

| Encoding:        | 0110 bbbf ffff                                                                                                               | if FLAG<         | <1> = 1,                                                                            |

| Description:     | If bit 'b' in register 'f' is 0 then the next instruction is skipped.                                                        | PC               | = address (TRUE)                                                                    |

|                  | If bit 'b' is 0 then the next instruction<br>fetched during the current instruction<br>execution is discarded, and an NOP is |                  |                                                                                     |

executed instead, making this a 2 cycle

BTFSC FLAG,1

address (HERE)

address (TRUE);

address(FALSE)

PROCESS\_CODE

GOTO

٠ •

0, =

1, =

instruction.

1

1(2)

HERE

TRUE

Before Instruction PC

After Instruction if FLAG<1>

if FLAG<1>

PC

PC

FALSE

=

=

=

Words:

Cycles:

Example:

| CALL                  | Subroutine Call                                                                                                                                                                                                                                |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:               | [ <i>label</i> ] CALL k                                                                                                                                                                                                                        |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                                                                              |  |  |  |

| Operation:            | $\begin{array}{l} (PC) + 1 \rightarrow \text{Top of Stack;} \\ k \rightarrow PC < 7:0>; \\ (STATUS < 6:5>) \rightarrow PC < 10:9>; \\ 0 \rightarrow PC < 8> \end{array}$                                                                       |  |  |  |

| Status Affected:      | None                                                                                                                                                                                                                                           |  |  |  |

| Encoding:             | 1001 kkkk kkkk                                                                                                                                                                                                                                 |  |  |  |

| Description:          | Subroutine call. First, return address (PC+1) is pushed onto the stack. The eight bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STA-TUS<6:5>, PC<8> is cleared. CALL is a two cycle instruction. |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                              |  |  |  |

| Cycles:               | 2                                                                                                                                                                                                                                              |  |  |  |

| Example:              | HERE CALL THERE                                                                                                                                                                                                                                |  |  |  |

| Before Instru<br>PC = |                                                                                                                                                                                                                                                |  |  |  |

|                       | tion<br>address (THERE)<br>address (HERE + 1)                                                                                                                                                                                                  |  |  |  |

### CLRF

| Syntax:                               | [label]                                                                | CLRF f    |      |  |

|---------------------------------------|------------------------------------------------------------------------|-----------|------|--|

| Operands:                             | $0 \le f \le 31$                                                       |           |      |  |

| Operation:                            | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |           |      |  |

| Status Affected:                      | Z                                                                      |           |      |  |

| Encoding:                             | 0000                                                                   | 011f      | ffff |  |

| Description:                          | The contents of register 'f' are cleared and the Z bit is set.         |           |      |  |

| Words:                                | 1                                                                      |           |      |  |

| Cycles:                               | 1                                                                      |           |      |  |

| Example:                              | CLRF                                                                   | FLAG_REC  | 3    |  |

| Before Instruction<br>FLAG_REG = 0x5A |                                                                        |           |      |  |

| After Instruct<br>FLAG_RE<br>Z        |                                                                        | 0x00<br>1 |      |  |

Clear f

| CLRW                                                                                                     | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Operation:                                                                                               | $\begin{array}{l} \text{00h} \rightarrow (\text{W}); \\ 1 \rightarrow \text{Z} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Encoding:                                                                                                | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Description:                                                                                             | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Example:                                                                                                 | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Before Instru<br>W =                                                                                     | uction<br>0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| After Instruc<br>W =<br>Z =                                                                              | tion<br>0x00<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLRWDT<br>Syntax:                                                                                        | Clear Watchdog Timer<br>[label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Syntax:                                                                                                  | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Syntax:<br>Operands:                                                                                     | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Syntax:<br>Operands:<br>Operation:                                                                       | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $ \begin{array}{l l} \textit{[label]} & \textit{CLRWDT} \\ \hline None \\ 00h \rightarrow WDT; \\ 0 \rightarrow WDT \ prescaler \ (if \ assigned); \\ 1 \rightarrow \overline{\text{TO}}; \\ 1 \rightarrow \overline{\text{PD}} \\ \hline \overline{\text{TO}}, \overline{\text{PD}} \\ \hline \hline \hline 0000 & 0000 & 0100 \\ \hline \hline \text{The } \ \text{CLRWDT} \ instruction \ resets \ the \\ WDT. \ It \ also \ resets \ the \ prescaler, \ if \ the \\ prescaler \ is \ assigned \ to \ the \ WDT \ and \\ not \ Timer0. \ Status \ bits \ \overline{\text{TO}} \ and \ \overline{\text{PD}} \ are \\ \end{array} $                                                                                                                                                                                                |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $ \begin{array}{l l} \textit{[label]} & \textit{CLRWDT} \\ \hline None \\ 00h \rightarrow \textit{WDT}; \\ 0 \rightarrow \textit{WDT} \textit{ prescaler} (if assigned); \\ 1 \rightarrow \overrightarrow{\textit{TO}}; \\ 1 \rightarrow \overrightarrow{\textit{PD}} \\ \hline \overrightarrow{\textit{TO}}, \overrightarrow{\textit{PD}} \\ \hline \hline \overrightarrow{\textit{TO}}, \overrightarrow{\textit{PD}} \\ \hline \hline \hline \textit{O000} & 0000 & 0100 \\ \hline \hline \hline \textit{The } \textit{CLRWDT} \textit{ instruction resets the} \\ \textit{WDT. It also resets the prescaler, if the} \\ \textit{prescaler is assigned to the WDT and} \\ \textit{not Timer0. Status bits } \overrightarrow{\textit{TO}} \textit{ and } \overrightarrow{\textit{PD}} \textit{ are} \\ \textit{set.} \end{array} $ |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |