Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>Details</b> Product Status | Active                                                                      |

|-------------------------------|-----------------------------------------------------------------------------|

| Core Processor                | PIC                                                                         |

|                               |                                                                             |

| Core Size                     | 8-Bit                                                                       |

| Speed                         | 4MHz                                                                        |

| Connectivity                  | -                                                                           |

| Peripherals                   | POR, WDT                                                                    |

| Number of I/O                 | 5                                                                           |

| Program Memory Size           | 1.5KB (1K x 12)                                                             |

| Program Memory Type           | ОТР                                                                         |

| EEPROM Size                   | -                                                                           |

| RAM Size                      | 41 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd)    | 2.5V ~ 5.5V                                                                 |

| Data Converters               | -                                                                           |

| Oscillator Type               | Internal                                                                    |

| Operating Temperature         | 0°C ~ 70°C (TA)                                                             |

| Mounting Type                 | Surface Mount                                                               |

| Package / Case                | 8-SOIC (0.154", 3.90mm Width)                                               |

| Supplier Device Package       | 8-SOIC                                                                      |

| Purchase URL                  | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc509a-04-sn |

**NOTES:**

**NOTES:**

### 4.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: special function registers and general purpose registers.

The special function registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports), and the File Select Register (FSR). In addition, special purpose registers are used to control the I/O port configuration and prescaler options.

The general purpose registers are used for data and control information under command of the instructions.

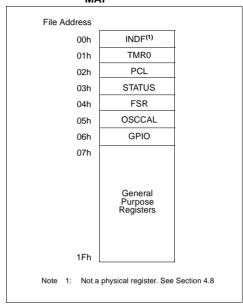

For the PIC12C508, PIC12C508A and PIC12CE518, the register file is composed of 7 special function registers and 25 general purpose registers (Figure 4-2).

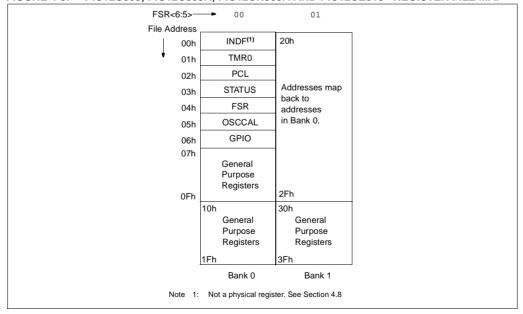

For the PIC12C509, PIC12C509A, PIC12CR509A, and PIC12CE519 the register file is composed of 7 special function registers, 25 general purpose registers, and 16 general purpose registers that may be addressed using a banking scheme (Figure 4-3).

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The general purpose register file is accessed either directly or indirectly through the file select register FSR (Section 4.8).

FIGURE 4-2: PIC12C508, PIC12C508A AND PIC12CE518 REGISTER FILE MAP

FIGURE 4-3: PIC12C509, PIC12C509A, PIC12CR509A AND PIC12CE519 REGISTER FILE MAP

### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The special registers can be classified into two sets. The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

| Address            | Name                                                                                | Bit 7                                | Bit 6        | Bit 5     | Bit 4     | Bit 3                  | Bit 2        | Bit 1     | Bit 0     | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets <sup>(2)</sup> |

|--------------------|-------------------------------------------------------------------------------------|--------------------------------------|--------------|-----------|-----------|------------------------|--------------|-----------|-----------|-------------------------------|------------------------------------------------|

| N/A                | TRIS                                                                                | _                                    | _            |           |           |                        |              |           |           | 11 1111                       | 11 1111                                        |

| N/A                | OPTION                                                                              | Contains of prescaler, v             |              |           |           | Timer0/WD7<br>pull-ups | Г            |           |           | 1111 1111                     | 1111 1111                                      |

| 00h                | INDF                                                                                | Uses conte                           | ents of FSF  | to addres | s data me | mory (not a            | physical reg | gister)   |           | xxxx xxxx                     | uuuu uuuu                                      |

| 01h                | TMR0                                                                                | 8-bit real-ti                        | me clock/c   | ounter    |           |                        |              |           |           | xxxx xxxx                     | uuuu uuuu                                      |

| 02h <sup>(1)</sup> | PCL                                                                                 | Low order                            | 8 bits of PO | 2         |           |                        |              |           |           | 1111 1111                     | 1111 1111                                      |

| 03h                | STATUS                                                                              | GPWUF                                | _            | PA0       | TO        | PD                     | Z            | DC        | С         | 0001 1xxx                     | q00q quuu(3)                                   |

| 04h                | FSR<br>(PIC12C508/<br>PIC12C508A/<br>PIC12C518)                                     | Indirect data memory address pointer |              |           |           |                        |              | 111x xxxx | 111u uuuu |                               |                                                |

| 04h                | FSR<br>(PIC12C509/<br>PIC12C509A/<br>PIC12CR509A/<br>PIC12CE519)                    | Indirect data memory address pointer |              |           |           |                        |              | 110x xxxx | 11uu uuuu |                               |                                                |

| 05h                | OSCCAL<br>(PIC12C508/<br>PIC12C509)                                                 | CAL3                                 | CAL2         | CAL1      | CAL0      | _                      | _            | _         | _         | 0111                          | uuuu                                           |

| 05h                | OSCCAL<br>(PIC12C508A/<br>PIC12C509A/<br>PIC12CE518/<br>PIC12CE519/<br>PIC12CR509A) | CAL5                                 | CAL4         | CAL3      | CAL2      | CAL1                   | CAL0         | _         | _         | 1000 00                       | uuuu uu                                        |

| 06h                | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CR509A)     | _                                    | _            | GP5       | GP4       | GP3                    | GP2          | GP1       | GP0       | xx xxxx                       | uu uuuu                                        |

| 06h                | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                                 | SCL                                  | SDA          | GP5       | GP4       | GP3                    | GP2          | GP1       | GP0       | 11xx xxxx                     | 11uu uuuu                                      |

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as '0' (if applicable)

x = unknown,  $\alpha$  = unchanged, q = see the tables in Section 8.7 for possible values.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6

for an explanation of how to access these bits.

<sup>2:</sup> Other (non power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

<sup>3:</sup> If reset was due to wake-up on pin change then bit 7 = 1. All other resets will cause bit 7 = 0.

## 4.8 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### **EXAMPLE 4-1: INDIRECT ADDRESSING**

- · Register file 07 contains the value 10h

- · Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-2.

# EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | movlw<br>movwf<br>clrf<br>incf<br>btfsc | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | ;initialize pointer; to RAM; clear INDF register; inc pointer; all done?; NO, clear next |

|----------|-----------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------|

| CONTINUE | 5                                       |                                               | .,                                                                                       |

|          | :                                       |                                               | :YES, continue                                                                           |

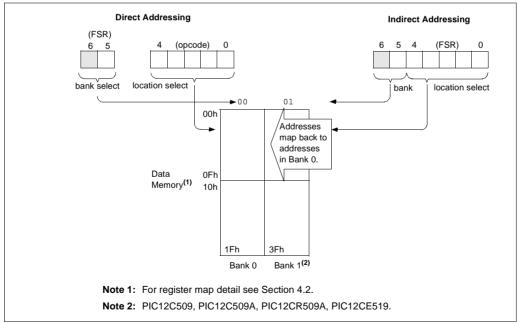

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC12C508/PIC12C508A/PIC12CE518:** Does not use banking. FSR<7:5> are unimplemented and read as '1's.

### PIC12C509/PIC12C509A/PIC12CR509A/

**PIC12CE519:** Uses FSR<5>. Selects between bank 0 and bank 1. FSR<7:6> is unimplemented, read as '1'.

FIGURE 4-9: DIRECT/INDIRECT ADDRESSING

#### 7.0.2 SERIAL CLOCK

This SCL input is used to synchronize the data transfer from and to the device.

#### 7.1 BUS CHARACTERISTICS

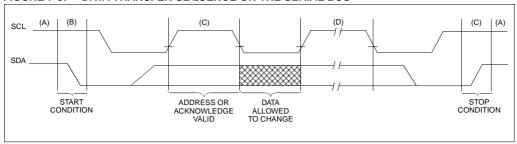

The following **bus protocol** is to be used with the EEPROM data memory.

Data transfer may be initiated only when the bus is not busy.

During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 7-3).

### 7.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

### 7.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

### 7.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### 7.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the master device and is theoretically unlimited.

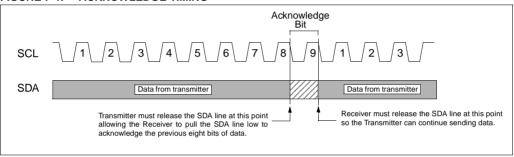

### 7.1.5 ACKNOWLEDGE

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.

**Note:** Acknowledge bits are not generated if an internal programming cycle is in progress.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition (Figure 7-4).

### FIGURE 7-3: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

### FIGURE 7-4: ACKNOWLEDGE TIMING

### 7.2 <u>Device Addressing</u>

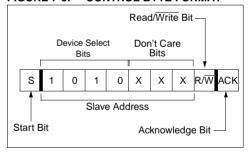

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed. The slave address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

FIGURE 7-5: CONTROL BYTE FORMAT

MOVF Move f Syntax: [ label ] MOVF f,d Operands:  $0 \le f \le 31$  $d \in [0,1]$ Operation:  $(f) \rightarrow (dest)$ Status Affected: Ζ Encoding: 0010 00df ffff Description: The contents of register 'f' is moved to destination 'd'. If 'd' is 0, destination is the W register. If 'd' is 1, the destination is file register 'f'. 'd' is 1 is useful to test a file register since status flag Z is affected. Words: 1 Cycles: 1 Example: MOVF FSR, 0 After Instruction

| MOVLW             | Move Literal to W                                                                             |       |      |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------|-------|------|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                     | MOVLW | k    |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 2$                                                                               | 55    |      |  |  |  |  |  |  |

| Operation:        | $k \rightarrow (W)$                                                                           |       |      |  |  |  |  |  |  |

| Status Affected:  | None                                                                                          |       |      |  |  |  |  |  |  |

| Encoding:         | 1100                                                                                          | kkkk  | kkkk |  |  |  |  |  |  |

| Description:      | The eight bit literal 'k' is loaded into the W register. The don't cares will assemble as 0s. |       |      |  |  |  |  |  |  |

| Words:            | 1                                                                                             |       |      |  |  |  |  |  |  |

| Cycles:           | 1                                                                                             |       |      |  |  |  |  |  |  |

| Example:          | MOVLW                                                                                         | 0x5A  |      |  |  |  |  |  |  |

| After Instruction |                                                                                               |       |      |  |  |  |  |  |  |

value in FSR register

| MOVWF                         | Move W to f                                    |  |  |  |  |  |  |

|-------------------------------|------------------------------------------------|--|--|--|--|--|--|

| Syntax:                       | [label] MOVWF f                                |  |  |  |  |  |  |

| Operands:                     | $0 \le f \le 31$                               |  |  |  |  |  |  |

| Operation:                    | $(W) \rightarrow (f)$                          |  |  |  |  |  |  |

| Status Affected:              | None                                           |  |  |  |  |  |  |

| Encoding:                     | 0000 001f ffff                                 |  |  |  |  |  |  |

| Description:                  | Move data from the W register to register 'f'. |  |  |  |  |  |  |

| Words:                        | 1                                              |  |  |  |  |  |  |

| Cycles:                       | 1                                              |  |  |  |  |  |  |

| Example:                      | MOVWF TEMP_REG                                 |  |  |  |  |  |  |

| Before Instru<br>TEMP_R<br>W  |                                                |  |  |  |  |  |  |

| After Instruct<br>TEMP_R<br>W |                                                |  |  |  |  |  |  |

| NOD              | Na Ones      | -4!    |      |  |  |  |

|------------------|--------------|--------|------|--|--|--|

| NOP              | No Oper      | ation  |      |  |  |  |

| Syntax:          | [ label ]    | NOP    |      |  |  |  |

| Operands:        | None         |        |      |  |  |  |

| Operation:       | No operation |        |      |  |  |  |

| Status Affected: | None         |        |      |  |  |  |

| Encoding:        | 0000         | 0000   | 0000 |  |  |  |

| Description:     | No opera     | ation. |      |  |  |  |

| Words:           | 1            |        |      |  |  |  |

| Cycles:          | 1            |        |      |  |  |  |

| Example:         | NOP          |        |      |  |  |  |

|                  |              |        |      |  |  |  |

W =

0x5A

### 11.4 Timing Diagrams and Specifications

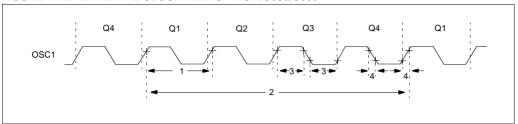

### FIGURE 11-2: EXTERNAL CLOCK TIMING - PIC12C508/C509

TABLE 11-2: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC12C508/C509

| AC Characteristics | Standard Operating Conditions (unless otherwise specified)                |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------|--|--|--|--|--|

|                    | Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial),  |  |  |  |  |  |

|                    | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ (industrial), |  |  |  |  |  |

|                    | $-40^{\circ}$ C $\leq$ TA $\leq$ +125 $^{\circ}$ C (extended)             |  |  |  |  |  |

|                    | Operating Voltage VDD range is described in Section 11.1                  |  |  |  |  |  |

| Parameter No. | Sym        | Characteristic                          | Min | Тур <sup>(1)</sup> | Max    | Units | Conditions     |

|---------------|------------|-----------------------------------------|-----|--------------------|--------|-------|----------------|

|               | Fosc       | External CLKIN Frequency <sup>(2)</sup> |     |                    |        |       |                |

|               |            | , ,                                     | DC  | _                  | 4      | MHz   | XT osc mode    |

|               |            |                                         | DC  | _                  | 200    | kHz   | LP osc mode    |

|               |            | Oscillator Frequency <sup>(2)</sup>     |     |                    |        |       |                |

|               |            |                                         | 0.1 | _                  | 4      | MHz   | XT osc mode    |

|               |            |                                         | DC  | _                  | 200    | kHz   | LP osc mode    |

| 1             | Tosc       | External CLKIN Period <sup>(2)</sup>    | 250 | _                  | _      | ns    | EXTRC osc mode |

|               |            |                                         | 250 | _                  | _      | ns    | XT osc mode    |

|               |            |                                         | 5   | _                  | _      | ms    | LP osc mode    |

|               |            | Oscillator Period <sup>(2)</sup>        | 250 | _                  | _      | ns    | EXTRC osc mode |

|               |            |                                         | 250 | _                  | 10,000 | ns    | XT osc mode    |

|               |            |                                         | 5   | _                  | _      | ms    | LP osc mode    |

| 2             | Tcy        | Instruction Cycle Time <sup>(3)</sup>   | _   | 4/Fosc             | _      | _     |                |

| 3             | TosL, TosH | Clock in (OSC1) Low or High Time        | 50* | _                  | _      | ns    | XT oscillator  |

|               |            |                                         | 2*  | _                  | _      | ms    | LP oscillator  |

| 4             | TosR, TosF | Clock in (OSC1) Rise or Fall Time       | _   | _                  | 25*    | ns    | XT oscillator  |

|               |            |                                         | _   | _                  | 50*    | ns    | LP oscillator  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

<sup>3:</sup> Instruction cycle period (TcY) equals four times the input oscillator time base period.

TABLE 13-1: PULL-UP RESISTOR RANGES\* - PIC12C508A, PIC12C509A, PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| VDD (Volts) | Temperature (°C) | Min  | Max  | Units |   |  |  |  |  |

|-------------|------------------|------|------|-------|---|--|--|--|--|

|             | GP0/GP1          |      |      |       |   |  |  |  |  |

| 2.5         | -40              | 38K  | 42K  | 63K   | Ω |  |  |  |  |

|             | 25               | 42K  | 48K  | 63K   | Ω |  |  |  |  |

|             | 85               | 42K  | 49K  | 63K   | Ω |  |  |  |  |

|             | 125              | 50K  | 55K  | 63K   | Ω |  |  |  |  |

| 5.5         | -40              | 15K  | 17K  | 20K   | Ω |  |  |  |  |

|             | 25               | 18K  | 20K  | 23K   | Ω |  |  |  |  |

|             | 85               | 19K  | 22K  | 25K   | Ω |  |  |  |  |

|             | 125              | 22K  | 24K  | 28K   | Ω |  |  |  |  |

|             |                  | G    | P3   |       |   |  |  |  |  |

| 2.5         | -40              | 285K | 346K | 417K  | Ω |  |  |  |  |

|             | 25               | 343K | 414K | 532K  | Ω |  |  |  |  |

|             | 85               | 368K | 457K | 532K  | Ω |  |  |  |  |

|             | 125              | 431K | 504K | 593K  | Ω |  |  |  |  |

| 5.5         | -40              | 247K | 292K | 360K  | Ω |  |  |  |  |

|             | 25               | 288K | 341K | 437K  | Ω |  |  |  |  |

|             | 85               | 306K | 371K | 448K  | Ω |  |  |  |  |

|             | 125              | 351K | 407K | 500K  | Ω |  |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

# TABLE 13-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCE518 and PIC12LCE519

| AC Charac     | cteristics | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial), $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial), $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)  Operating Voltage VDD range is described in Section 10.1 |      |                    |      |       |            |

|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|-------|------------|

| Parameter No. | Sym        | Characteristic                                                                                                                                                                                                                                                                                         | Min* | Typ <sup>(1)</sup> | Max* | Units | Conditions |

|               |            | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                       | 3.65 | 4.00               | 4.28 | MHz   | VDD = 5.0V |

|               |            | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                       | 3.55 | _                  | 4.31 | MHz   | VDD = 2.5V |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

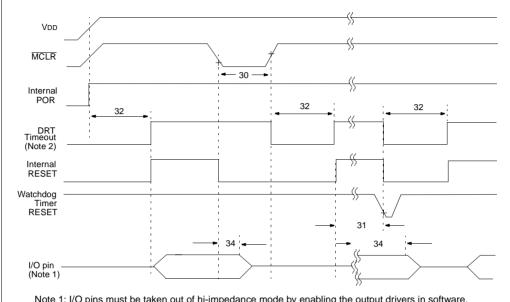

FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCF519 and PIC12LCE519

Note 1: I/O pins must be taken out of hi-impedance mode by enabling the output drivers in software. 2: Runs in MCLR or WDT reset only in XT and LP modes.

TABLE 13-5: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC12C508A, PIC12C509A, PIC12C509A, PIC12C509A, PIC12LC509A, PIC12LC7509A, PIC12LC750A, PIC1

### AC Characteristics Standard Operating Conditions (unless otherwise specified)

Operating Temperature  $0^{\circ}C \le TA \le +70^{\circ}C$  (commercial)

$-40^{\circ}C \le TA \le +85^{\circ}C$  (industrial)

$-40^{\circ}C \leq TA \leq +125^{\circ}C$  (extended)

Operating Voltage VDD range is described in Section 13.1

| Parameter No. | Sym  | Characteristic                                | Min   | Typ <sup>(1)</sup> | Max   | Units | Conditions             |

|---------------|------|-----------------------------------------------|-------|--------------------|-------|-------|------------------------|

| 30            | TmcL | MCLR Pulse Width (low)                        | 2000* | _                  |       | ns    | VDD = 5 V              |

| 31            | Twdt | Watchdog Timer Time-out Period (No Prescaler) | 9*    | 18*                | 30*   | ms    | VDD = 5 V (Commercial) |

| 32            | TDRT | Device Reset Timer Period <sup>(2)</sup>      | 9*    | 18*                | 30*   | ms    | VDD = 5 V (Commercial) |

| 34            | Tioz | I/O Hi-impedance from MCLR Low                | _     | _                  | 2000* | ns    |                        |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 2: See Table 13-6.

TABLE 13-6: DRT (DEVICE RESET TIMER PERIOD) - PIC12C508A, PIC12C509A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCF509A, PIC12LCE518 and PIC12LCE519

| Oscillator Configuration | POR Reset                      | Subsequent Resets               |  |  |

|--------------------------|--------------------------------|---------------------------------|--|--|

| IntRC & ExtRC            | 18 ms (typical) <sup>(1)</sup> | 300 μs (typical) <sup>(1)</sup> |  |  |

| XT & LP                  | 18 ms (typical) <sup>(1)</sup> | 18 ms (typical) <sup>(1)</sup>  |  |  |

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

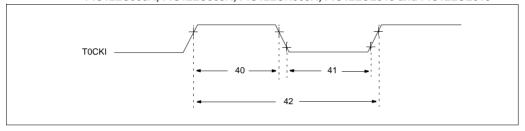

FIGURE 13-5: TIMER0 CLOCK TIMINGS - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCF509A, PIC12LCE518 and PIC12LCE519

TABLE 13-7: TIMERO CLOCK REQUIREMENTS - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCF509A, PIC12LCF518 and PIC12LCE519

| AC Characteristics |      |                                       |                      |                              |                    |     |       |                                                           |  |  |

|--------------------|------|---------------------------------------|----------------------|------------------------------|--------------------|-----|-------|-----------------------------------------------------------|--|--|

| Parameter No.      | Sym  | Characteristic                        |                      | Min                          | Typ <sup>(1)</sup> | Max | Units | Conditions                                                |  |  |

| 40                 | Tt0H | T0CKI High Pulse Width - No Prescaler |                      | 0.5 Tcy + 20*                | _                  | _   | ns    |                                                           |  |  |

|                    |      |                                       | - With Prescaler     | 10*                          | _                  | _   | ns    |                                                           |  |  |

| 41                 | Tt0L | T0CKI Low Pulse V                     | Vidth - No Prescaler | 0.5 Tcy + 20*                | _                  | _   | ns    |                                                           |  |  |

|                    |      |                                       | - With Prescaler     | 10*                          | _                  | _   | ns    |                                                           |  |  |

| 42                 | Tt0P | T0CKI Period                          |                      | 20 or <u>Tcy + 40</u> *<br>N | _                  | _   | ns    | Whichever is greater.  N = Prescale Value (1, 2, 4,, 256) |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

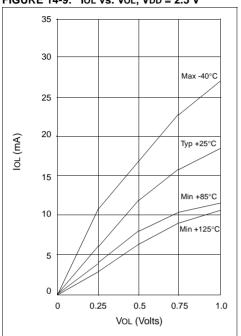

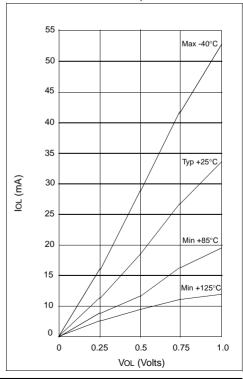

FIGURE 14-9: IOL vs. Vol, VDD = 2.5 V

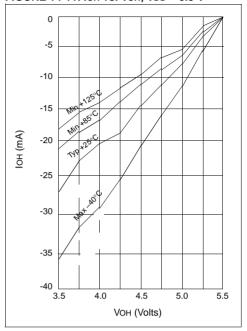

FIGURE 14-11: IOH vs. VOH, VDD = 5.5 V

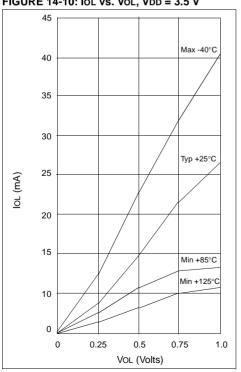

FIGURE 14-10: IOL vs. Vol, VDD = 3.5 V

FIGURE 14-12: IOL vs. Vol, VDD = 5.5 V

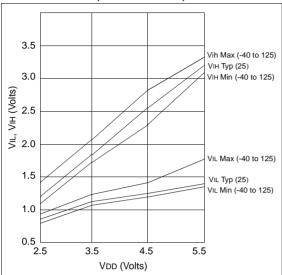

### FIGURE 14-15: VIL, VIH OF NMCLR, AND TOCKI VS. VDD

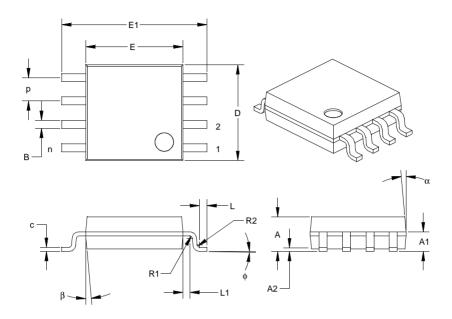

Package Type: K04-056 8-Lead Plastic Small Outline (SM) - Medium, 208 mil

| Units                   |                | INCHES* |       |       | MILLIMETERS |      |      |  |

|-------------------------|----------------|---------|-------|-------|-------------|------|------|--|

| Dimension Limits        |                | MIN     | NOM   | MAX   | MIN         | NOM  | MAX  |  |

| Pitch                   | р              |         | 0.050 |       |             | 1.27 |      |  |

| Number of Pins          | n              |         | 8     |       |             | 8    |      |  |

| Overall Pack. Height    | Α              | 0.070   | 0.074 | 0.079 | 1.78        | 1.89 | 2.00 |  |

| Shoulder Height         | A1             | 0.037   | 0.042 | 0.048 | 0.94        | 1.08 | 1.21 |  |

| Standoff                | A2             | 0.002   | 0.005 | 0.009 | 0.05        | 0.14 | 0.22 |  |

| Molded Package Length   | D <sup>‡</sup> | 0.200   | 0.205 | 0.210 | 5.08        | 5.21 | 5.33 |  |

| Molded Package Width    | E <sup>‡</sup> | 0.203   | 0.208 | 0.213 | 5.16        | 5.28 | 5.41 |  |

| Outside Dimension       | E1             | 0.300   | 0.313 | 0.325 | 7.62        | 7.94 | 8.26 |  |

| Shoulder Radius         | R1             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13 | 0.25 |  |

| Gull Wing Radius        | R2             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13 | 0.25 |  |

| Foot Length             | L              | 0.011   | 0.016 | 0.021 | 0.28        | 0.41 | 0.53 |  |

| Foot Angle              | φ              | 0       | 4     | 8     | 0           | 4    | 8    |  |

| Radius Centerline       | L1             | 0.010   | 0.015 | 0.020 | 0.25        | 0.38 | 0.51 |  |

| Lead Thickness          | С              | 0.008   | 0.009 | 0.010 | 0.19        | 0.22 | 0.25 |  |

| Lower Lead Width        | Β <sup>†</sup> | 0.014   | 0.017 | 0.020 | 0.36        | 0.43 | 0.51 |  |

| Mold Draft Angle Top    | α              | 0       | 12    | 15    | 0           | 12   | 15   |  |

| Mold Draft Angle Bottom | β              | 0       | 12    | 15    | 0           | 12   | 15   |  |

<sup>\*</sup> Controlling Parameter.

<sup>&</sup>lt;sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>&</sup>lt;sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

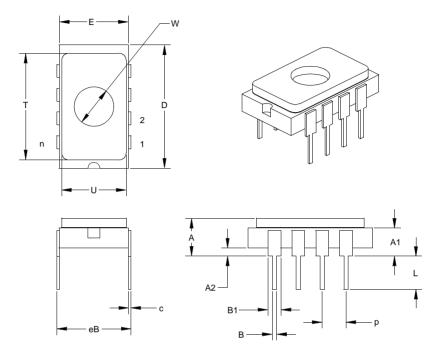

### Package Type: K04-084 8-Lead Ceramic Side Brazed Dual In-line with Window (JW) - 300 mil

| Units                        | INCHES* |       |       | MILLIMETERS |       |       |       |

|------------------------------|---------|-------|-------|-------------|-------|-------|-------|

| Dimension Limits             |         | MIN   | NOM   | MAX         | MIN   | NOM   | MAX   |

| PCB Row Spacing              |         |       | 0.300 |             |       | 7.62  |       |

| Number of Pins               | n       |       | 8     |             |       | 8     |       |

| Pitch                        | р       | 0.098 | 0.100 | 0.102       | 2.49  | 2.54  | 2.59  |

| Lower Lead Width             | В       | 0.016 | 0.018 | 0.020       | 0.41  | 0.46  | 0.51  |

| Upper Lead Width             | B1      | 0.050 | 0.055 | 0.060       | 1.27  | 1.40  | 1.52  |

| Lead Thickness               | С       | 0.008 | 0.010 | 0.012       | 0.20  | 0.25  | 0.30  |

| Top to Seating Plane         | Α       | 0.145 | 0.165 | 0.185       | 3.68  | 4.19  | 4.70  |

| Top of Body to Seating Plane | A1      | 0.103 | 0.123 | 0.143       | 2.62  | 3.12  | 3.63  |

| Base to Seating Plane        | A2      | 0.025 | 0.035 | 0.045       | 0.64  | 0.89  | 1.14  |

| Tip to Seating Plane         | L       | 0.130 | 0.140 | 0.150       | 3.30  | 3.56  | 3.81  |

| Package Length               | D       | 0.510 | 0.520 | 0.530       | 12.95 | 13.21 | 13.46 |

| Package Width                | E       | 0.280 | 0.290 | 0.300       | 7.11  | 7.37  | 7.62  |

| Overall Row Spacing          | eB      | 0.310 | 0.338 | 0.365       | 7.87  | 8.57  | 9.27  |

| Window Diameter              | W       | 0.161 | 0.166 | 0.171       | 4.09  | 4.22  | 4.34  |

| Lid Length                   | T       | 0.440 | 0.450 | 0.460       | 11.18 | 11.43 | 11.68 |

| Lid Width                    | U       | 0.260 | 0.270 | 0.280       | 6.60  | 6.86  | 7.11  |

<sup>\*</sup> Controlling Parameter.

### **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- · Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- · Design Tips

- Device Errata

- Job Postings

- · Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- · Listing of seminars and events

### Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits. The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and 1-602-786-7302 for the rest of the world

981103

**Trademarks:** The Microchip name, logo, PIC, PICmicro, PICSTART, PICMASTER and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. *Flex*ROM, MPLAB and *fuzzy*-LAB are trademarks and SQTP is a service mark of Microchip in the U.S.A.

All other trademarks mentioned herein are the property of their respective companies.

**NOTES:**

### Note the following details of the code protection feature on PICmicro® MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet.

The person doing so may be engaged in theft of intellectual property.

- · Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

### **Trademarks**

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELO© code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.