Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFl

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 5                                                                            |

| Program Memory Size        | 1.5KB (1K x 12)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 41 × 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

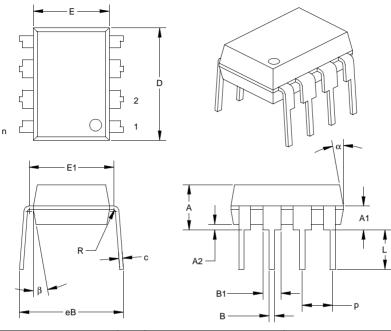

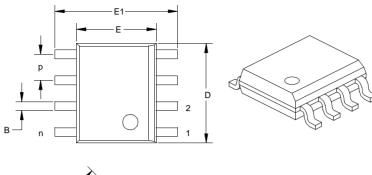

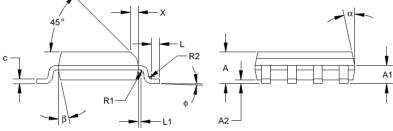

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 8-SOIJ                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc509a-04i-sm |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

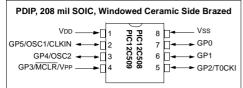

#### Pin Diagram - PIC12C508/509

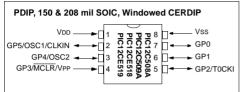

## Pin Diagram - PIC12C508A/509A, PIC12CE518/519

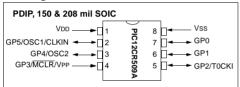

#### Pin Diagram - PIC12CR509A

#### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

NOTES:

# 5.0 I/O PORT

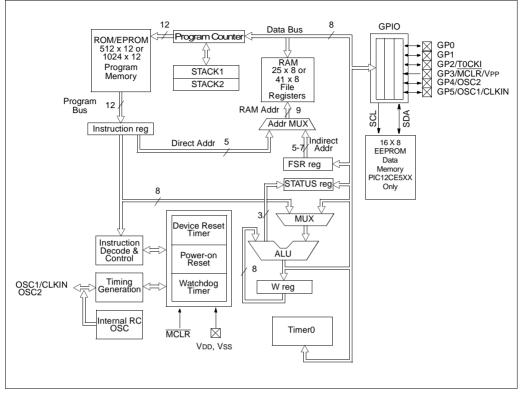

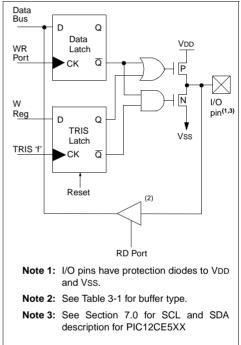

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

## 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the output data latches. That is, if an output      |

|-------|---------------------------------------------------------------------------------------------|

|       | driver on a pin is enabled and driven high,                                                 |

|       | but the external system is holding it low, a read of the port will indicate that the pin is |

|       | low.                                                                                        |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

## 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

### FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

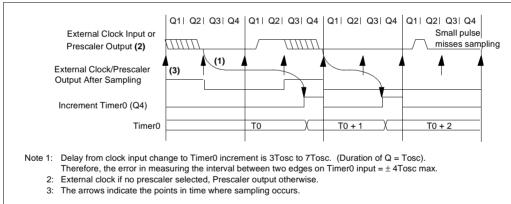

#### 6.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

#### 6.1.3 OPTION REGISTER EFFECT ON GP2 TRIS

If the option register is set to read TIMER0 from the pin, the port is forced to an input regardless of the TRIS register setting.

#### FIGURE 6-4: TIMER0 TIMING WITH EXTERNAL CLOCK

#### 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

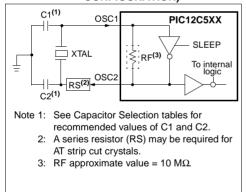

# 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

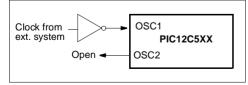

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

#### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

#### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

#### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

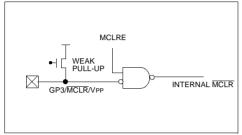

#### 8.3.1 MCLR ENABLE

This configuration bit when unprogrammed (left in the '1' state) enables the external  $\overline{MCLR}$  function. When programmed, the  $\overline{MCLR}$  function is tied to the internal VDD, and the pin is assigned to be a GPIO. See Figure 8-7. When pin GP3/ $\overline{MCLR}$ /VPP is configured as  $\overline{MCLR}$ , the internal pull-up is always on.

#### FIGURE 8-7: MCLR SELECT

#### 8.4 Power-On Reset (POR)

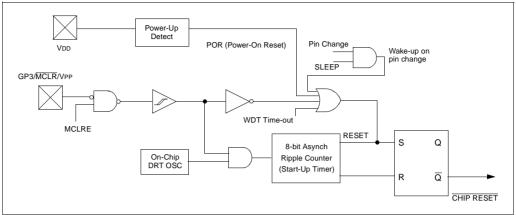

The PIC12C5XX family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip reset for most power-up situations.

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD or program the pin as GP3. An internal weak pull-up resistor is implemented using a transistor. Refer to Table 11-1 for the pull-up resistor ranges. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 8-8.

The Power-On Reset circuit and the Device Reset Timer (Section 8.5) circuit are closely related. On power-up, the reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will reset the reset latch and thus end the onchip reset signal.

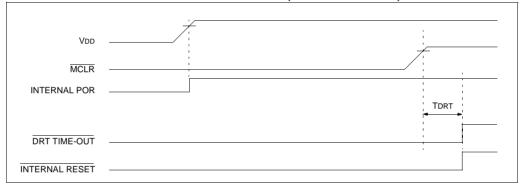

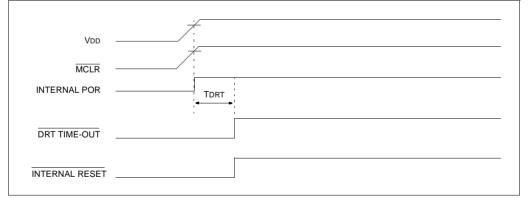

A power-up example where  $\overline{\text{MCLR}}$  is held low is shown in Figure 8-9. VDD is allowed to rise and stabilize before bringing  $\overline{\text{MCLR}}$  high. The chip will actually come out of reset TDRT msec after  $\overline{\text{MCLR}}$  goes high.

In Figure 8-10, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3.). The VDD is stable before the start-up timer times out and there is no problem in getting a proper reset. However, Figure 8-11 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 8-10).

| Note: | When the device starts normal operation (exits the reset condition), device operating |

|-------|---------------------------------------------------------------------------------------|

|       | parameters (voltage, frequency, tempera-                                              |

|       | ture, etc.) must be meet to ensure opera-                                             |

|       | tion. If these conditions are not met, the                                            |

|       | device must be held in reset until the oper-                                          |

|       | ating conditions are met.                                                             |

For additional information refer to Application Notes "Power-Up Considerations" - AN522 and "Power-up Trouble Shooting" - AN607.

#### FIGURE 8-8: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

FIGURE 8-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR PULLED LOW)

#### 8.12 In-Circuit Serial Programming

The PIC12C5XX microcontrollers with EPROM program memory can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the GP1 and GP0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1 becomes the programming clock and GP0 becomes the programming data. Both GP1 and GP0 are Schmitt Trigger inputs in this mode.

After reset, a 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC12C5XX Programming Specifications.

A typical in-circuit serial programming connection is shown in Figure 8-16.

#### FIGURE 8-16: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| BSF              | Bit Set f                                                                                                                    | BTFSS            | Bit Test f, Skip if Set                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------|

| Syntax:          | [label] BSF f,b                                                                                                              | Syntax:          | [label] BTFSS f,b                                                                   |

| Operands:        | $0 \le f \le 31$ $0 \le b \le 7$                                                                                             | Operands:        | $0 \le f \le 31$<br>$0 \le b < 7$                                                   |

| Operation:       | $1 \rightarrow (f < b >)$                                                                                                    | Operation:       | skip if (f <b>) = 1</b>                                                             |

| Status Affected: | None                                                                                                                         | Status Affected: | None                                                                                |

| Encoding:        | 0101 bbbf ffff                                                                                                               | Encoding:        | 0111 bbbf ffff                                                                      |

| Description:     | Bit 'b' in register 'f' is set.                                                                                              | Description:     | If bit 'b' in register 'f' is '1' then the next                                     |

| Words:           | 1                                                                                                                            |                  | instruction is skipped.                                                             |

| Cycles:          | 1                                                                                                                            |                  | If bit 'b' is '1', then the next instruction fetched during the current instruction |

| Example:         | BSF FLAG_REG, 7                                                                                                              |                  | execution, is discarded and an NOP is                                               |

| Before Instru    | uction                                                                                                                       |                  | executed instead, making this a 2 cycle instruction.                                |

| _                | EG = 0x0A                                                                                                                    | Words:           | 1                                                                                   |

| After Instruc    | tion<br>EG = 0x8A                                                                                                            | Cycles:          | 1(2)                                                                                |

| FLAG_K           |                                                                                                                              | Example:         | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CODE                                        |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                    |                  | TRUE •                                                                              |

| Syntax:          | [ label ] BTFSC f,b                                                                                                          |                  | •                                                                                   |

| Operands:        | $0 \le f \le 31$                                                                                                             | Before Instr     | uction                                                                              |

|                  | $0 \le b \le 7$                                                                                                              | PC               | = address (HERE)                                                                    |

| Operation:       | skip if $(f < b >) = 0$                                                                                                      | After Instruc    |                                                                                     |

| Status Affected: | None                                                                                                                         | If FLAG<br>PC    | <1> = 0,<br>= address (FALSE);                                                      |

| Encoding:        | 0110 bbbf ffff                                                                                                               | if FLAG<         | <1> = 1,                                                                            |

| Description:     | If bit 'b' in register 'f' is 0 then the next instruction is skipped.                                                        | PC               | = address (TRUE)                                                                    |

|                  | If bit 'b' is 0 then the next instruction<br>fetched during the current instruction<br>execution is discarded, and an NOP is |                  |                                                                                     |

executed instead, making this a 2 cycle

BTFSC FLAG,1

address (HERE)

address (TRUE);

address(FALSE)

PROCESS\_CODE

GOTO

٠ •

0, =

1, =

instruction.

1

1(2)

HERE

TRUE

Before Instruction PC

After Instruction if FLAG<1>

if FLAG<1>

PC

PC

FALSE

=

=

=

Words:

Cycles:

Example:

| COMF                       | Complement f                                                                                                                                                         |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                    | [ label ] COMF f,d                                                                                                                                                   |  |  |

| Operands:                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                            |  |  |

| Operation:                 | $(\overline{f}) \rightarrow (dest)$                                                                                                                                  |  |  |

| Status Affected:           | Z                                                                                                                                                                    |  |  |

| Encoding:                  | 0010 01df ffff                                                                                                                                                       |  |  |

| Description:               | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |  |  |

| Words:                     | 1                                                                                                                                                                    |  |  |

| Cycles:                    | 1                                                                                                                                                                    |  |  |

| Example:                   | COMF REG1,0                                                                                                                                                          |  |  |

| Before Instru<br>REG1      | uction<br>= 0x13                                                                                                                                                     |  |  |

| After Instruc<br>REG1<br>W | xtion<br>= 0x13<br>= 0xEC                                                                                                                                            |  |  |

| DECF                                                   | Decrement f                                                                                                                              |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                | [label] DECF f,d                                                                                                                         |

| Operands:                                              | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                |

| Operation:                                             | $(f) - 1 \rightarrow (dest)$                                                                                                             |

| Status Affected:                                       | Z                                                                                                                                        |

| Encoding:                                              | 0000 11df ffff                                                                                                                           |

| Description:                                           | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |

| Words:                                                 | 1                                                                                                                                        |

| Cycles:                                                | 1                                                                                                                                        |

| Example:                                               | DECF CNT, 1                                                                                                                              |

| Before Instru<br>CNT<br>Z<br>After Instruc<br>CNT<br>Z | = 0x01<br>= 0                                                                                                                            |

| DECFSZ                                               | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                              | [label] DECFSZ f.d                                                                                                                                                                                                                                                                                                                   |  |

| Operands:                                            | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                    |  |

| Operation:                                           | (f) $- 1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                                         |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                 |  |

| Encoding:                                            | 0010 11df ffff                                                                                                                                                                                                                                                                                                                       |  |

| Description:                                         | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded<br>and an NOP is executed instead mak-<br>ing it a two cycle instruction. |  |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                                                    |  |

| Cycles:                                              | 1(2)                                                                                                                                                                                                                                                                                                                                 |  |

| Example:                                             | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •                                                                                                                                                                                                                                                                                        |  |

| Before Instru                                        | iction                                                                                                                                                                                                                                                                                                                               |  |

| PC                                                   | = address (HERE)                                                                                                                                                                                                                                                                                                                     |  |

| After Instruc<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                                                                                                                                                                    |  |

| GOTO                                                 | Unconditional Branch                                                                                                                                                                                                                                                                                                                 |  |

| Syntax:                                              | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                              |  |

| -                                                    |                                                                                                                                                                                                                                                                                                                                      |  |

| Syntax:                                   | [ label ]                                                                                                                                                                               | GOTO | k    |   |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---|

| Operands:                                 | $0 \le k \le 5^{-1}$                                                                                                                                                                    | 11   |      |   |

| Operation:                                | $k \rightarrow PC < 8:0>;$<br>STATUS<6:5> $\rightarrow PC < 10:9>$                                                                                                                      |      |      |   |

| Status Affected:                          | None                                                                                                                                                                                    |      |      |   |

| Encoding:                                 | 101k                                                                                                                                                                                    | kkkk | kkkk |   |

| Description:                              | GOTO is an unconditional branch. The<br>9-bit immediate value is loaded into PC<br>bits <8:0>. The upper bits of PC are<br>loaded from STATUS<6:5>. GOTO is a<br>two cycle instruction. |      |      | : |

| Words:                                    | 1                                                                                                                                                                                       |      |      |   |

| Cycles:                                   | 2                                                                                                                                                                                       |      |      |   |

| Example:                                  | GOTO THE                                                                                                                                                                                | ERE  |      |   |

| After Instruction<br>PC = address (THERE) |                                                                                                                                                                                         |      |      |   |

#### TABLE 11-4: TIMING REQUIREMENTS - PIC12C508/C509

| AC Chara         | cteristics | standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)Operating Voltage VDD range is described in Section 11.1 |     |    |      |       |

|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|------|-------|

| Parameter<br>No. | Sym        | Characteristic Min Typ <sup>(1)</sup> Max Units                                                                                                                                                                                                                                                  |     |    |      | Units |

| 17               | TosH2ioV   | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(3)</sup>                                                                                                                                                                                                                                    | _   | -  | 100* | ns    |

| 18               | TosH2iol   | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                                                                                                                                                                                         | TBD | —  | _    | ns    |

| 19               | TioV2osH   | Port input valid to OSC1 <sup>↑</sup><br>(I/O in setup time)                                                                                                                                                                                                                                     | TBD | —  | _    | ns    |

| 20               | TioR       | Port output rise time <sup>(2, 3)</sup>                                                                                                                                                                                                                                                          | _   | 10 | 25** | ns    |

| 21               | TioF       | Port output fall time <sup>(2, 3)</sup>                                                                                                                                                                                                                                                          | _   | 10 | 25** | ns    |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: Measurements are taken in EXTRC mode.

- 3: See Figure 11-1 for loading conditions.

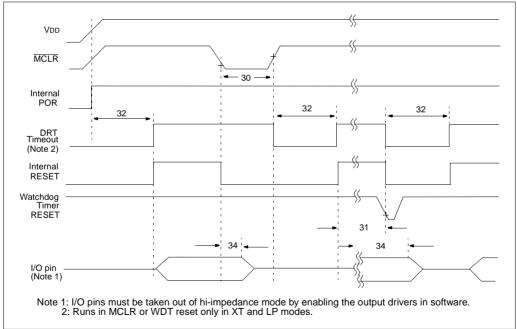

#### FIGURE 11-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC12C508/C509

#### 13.3 DC CHARACTERISTICS:

#### PIC12C508A/509A (Commercial, Industrial, Extended) PIC12C518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

|       |                                    |                                                                   | r <b>d Operati</b><br>ng tempera |        | 0°C ≤      | TA ≤ + | s otherwise specified)<br>70°C (commercial)                        |  |  |  |

|-------|------------------------------------|-------------------------------------------------------------------|----------------------------------|--------|------------|--------|--------------------------------------------------------------------|--|--|--|

| DC CH | ARACTERISTICS                      | –40°C ≤ TA ≤ +85°C (industrial)<br>–40°C ≤ TA ≤ +125°C (extended) |                                  |        |            |        |                                                                    |  |  |  |

|       |                                    | Operatii<br>Section                                               |                                  | Vdd ra |            |        | d in DC spec Section 13.1 and                                      |  |  |  |

| Param | Characteristic                     | Sym                                                               | Min                              | Typ†   | Max        | Units  | Conditions                                                         |  |  |  |

| No.   |                                    |                                                                   |                                  |        |            |        |                                                                    |  |  |  |

|       | Input Low Voltage                  |                                                                   |                                  |        |            |        |                                                                    |  |  |  |

|       | I/O ports                          | VIL                                                               |                                  |        |            |        |                                                                    |  |  |  |

| D030  | with TTL buffer                    |                                                                   | Vss                              | -      | 0.8V       | V      | For $4.5V \le VDD \le 5.5V$                                        |  |  |  |

|       |                                    |                                                                   | Vss                              | -      | 0.15Vdd    | V      | otherwise                                                          |  |  |  |

| D031  | with Schmitt Trigger buffer        |                                                                   | Vss                              | -      | 0.2VDD     | V      |                                                                    |  |  |  |

| D032  | MCLR, GP2/T0CKI (in EXTRC mode)    |                                                                   | Vss                              | -      | 0.2VDD     | V      |                                                                    |  |  |  |

| D033  | OSC1 (in EXTRC mode)               |                                                                   | Vss                              | -      | 0.2VDD     |        | Note 1                                                             |  |  |  |

| D033  | OSC1 (in XT and LP)                |                                                                   | Vss                              | -      | 0.3VDD     | V      | Note 1                                                             |  |  |  |

|       | Input High Voltage                 | N (++ +                                                           |                                  |        |            |        |                                                                    |  |  |  |

| Do 10 | I/O ports                          | Vih                                                               | 0.051/                           | -      | N /        |        |                                                                    |  |  |  |

| D040  | with TTL buffer                    |                                                                   | 0.25VDD +<br>0.8V                | -      | Vdd        | V      | $4.5V \le VDD \le 5.5V$                                            |  |  |  |

| D040A |                                    |                                                                   | 2.0V                             | -      | Vdd        | V      | otherwise                                                          |  |  |  |

| D041  | with Schmitt Trigger buffer        |                                                                   | 0.8Vdd                           | -      | Vdd        | V      | For entire VDD range                                               |  |  |  |

| D042  | MCLR, GP2/T0CKI                    |                                                                   | 0.8Vdd                           | -      | Vdd        | V      |                                                                    |  |  |  |

|       | OSC1 (XT and LP)                   |                                                                   | 0.7Vdd                           | -      | Vdd        | V      | Note 1                                                             |  |  |  |

| D043  | OSC1 (in EXTRC mode)               |                                                                   | 0.9Vdd                           | -      | Vdd        | V      |                                                                    |  |  |  |

| D070  | GPIO weak pull-up current (Note 4) | IPUR                                                              | 30                               | 250    | 400        | μA     | VDD = 5V, VPIN = VSS                                               |  |  |  |

|       | MCLR pull-up current               | -                                                                 | -                                | -      | 30         | μΑ     | VDD = 5V, VPIN = VSS                                               |  |  |  |

|       | Input Leakage Current (Notes 2, 3) |                                                                   |                                  |        |            | _      |                                                                    |  |  |  |

| D060  | I/O ports                          | lı∟                                                               | -                                | -      | <u>+</u> 1 | μA     | Vss ≤ VPIN ≤ VDD, Pin at hi-<br>impedance                          |  |  |  |

| D061  | TOCKI                              |                                                                   | -                                | -      | <u>+</u> 5 | μΑ     | $Vss \le VPIN \le VDD$                                             |  |  |  |

| D063  | OSC1                               |                                                                   | -                                | -      | <u>+</u> 5 | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT and LP osc configuration            |  |  |  |

|       | Output Low Voltage                 |                                                                   |                                  |        |            |        |                                                                    |  |  |  |

| D080  | I/O ports                          | Vol                                                               | -                                | -      | 0.6        | V      | IOL = 8.5 mA, VDD = 4.5V,<br>−40°C to +85°C                        |  |  |  |

| D080A |                                    |                                                                   | -                                | -      | 0.6        | V      | IOL = 7.0 mA, VDD = 4.5V,<br>−40°C to +125°C                       |  |  |  |

|       | Output High Voltage                |                                                                   |                                  |        |            |        |                                                                    |  |  |  |

| D090  | I/O ports (Note 3)                 | Voн                                                               | Vdd - 0.7                        | -      | -          | V      | Юн = -3.0 mA, VDD = 4.5V,<br>−40°C to +85°C                        |  |  |  |

| D090A |                                    |                                                                   | Vdd - 0.7                        | -      | -          | V      | ІОН = -2.5 mA, VDD = 4.5V,<br>−40°C to +125°C                      |  |  |  |

|       | Capacitive Loading Specs on        |                                                                   |                                  |        |            |        |                                                                    |  |  |  |

|       | Output Pins                        |                                                                   |                                  |        |            | _      |                                                                    |  |  |  |

| D100  | OSC2 pin                           | COSC2                                                             | -                                | -      | 15         | pF     | In XT and LP modes when exter-<br>nal clock is used to drive OSC1. |  |  |  |

| D101  | All I/O pins                       | Сю                                                                | -                                | -      | 50         | pF     |                                                                    |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C5XX be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: This spec. applies when GP3/MCLR is configured as MCLR. The leakage current of the MCLR circuit is higher than the standard I/O logic.

# 13.4 DC CHARACTERISTICS:

#### PIC12LC508A/509A (Commercial, Industrial) PIC12LC518/519 (Commercial, Industrial) PIC12LCR509A (Commercial, Industrial)

| DC CHARACTERISTICS |                                            |           | Standard Operating Conditions (unless otherwise specified)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) |                               |            |           |                                                                    |  |  |

|--------------------|--------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|-----------|--------------------------------------------------------------------|--|--|

|                    |                                            |           | ing voltage                                                                                                                                                                           | d in DC spec Section 13.1 and |            |           |                                                                    |  |  |

| Param<br>No.       | Characteristic                             | Sym       | Min                                                                                                                                                                                   | Тур†                          | Max        | Units     | Conditions                                                         |  |  |

|                    | Input Low Voltage                          |           |                                                                                                                                                                                       |                               |            |           |                                                                    |  |  |

|                    | I/O ports                                  | VIL       |                                                                                                                                                                                       |                               |            |           |                                                                    |  |  |

| D030               | with TTL buffer                            |           | Vss                                                                                                                                                                                   | -                             | 0.8V       | V         | For $4.5V \le VDD \le 5.5V$                                        |  |  |

|                    |                                            |           | Vss                                                                                                                                                                                   | -                             | 0.15Vdd    | V         | otherwise                                                          |  |  |

| D031               | with Schmitt Trigger buffer                |           | Vss                                                                                                                                                                                   | -                             | 0.2Vdd     | V         |                                                                    |  |  |

| D032               | MCLR, GP2/T0CKI (in EXTRC mode)            |           | Vss                                                                                                                                                                                   | -                             | 0.2Vdd     | V         |                                                                    |  |  |

| D033               | OSC1 (in EXTRC mode)                       |           | Vss                                                                                                                                                                                   | -                             | 0.2Vdd     | V         | Note 1                                                             |  |  |

| D033               | OSC1 (in XT and LP)                        |           | Vss                                                                                                                                                                                   | -                             | 0.3Vdd     | V         | Note 1                                                             |  |  |

|                    | Input High Voltage                         | 1         |                                                                                                                                                                                       |                               |            |           |                                                                    |  |  |

|                    | I/O ports                                  | VIH       |                                                                                                                                                                                       | -                             |            |           |                                                                    |  |  |

| D040               | with TTL buffer                            |           | 0.25Vdd +                                                                                                                                                                             | -                             | Vdd        | V         | $4.5V \le VDD \le 5.5V$                                            |  |  |

|                    |                                            |           | 0.8V                                                                                                                                                                                  |                               |            |           |                                                                    |  |  |

| D040A              |                                            |           | 2.0V                                                                                                                                                                                  | -                             | Vdd        | V         | otherwise                                                          |  |  |

| D041               | with Schmitt Trigger buffer                |           | 0.8Vdd                                                                                                                                                                                | -                             | Vdd        | V         | For entire VDD range                                               |  |  |

| D042               | MCLR, GP2/T0CKI                            |           | 0.8Vdd                                                                                                                                                                                | -                             | Vdd        | V         |                                                                    |  |  |

| D042A              | OSC1 (XT and LP)                           |           | 0.7Vdd                                                                                                                                                                                | -                             | Vdd        | V         | Note 1                                                             |  |  |

| D043               | OSC1 (in EXTRC mode)                       |           | 0.9Vdd                                                                                                                                                                                | -                             | Vdd        | V         |                                                                    |  |  |

| D070               | GPIO weak pull-up current (Note 4)         | IPUR      | 30                                                                                                                                                                                    | 250                           | 400        | μA        | VDD = 5V, VPIN = VSS                                               |  |  |

|                    | MCLR pull-up current                       | -         | -                                                                                                                                                                                     | -                             | 30         | μA        | VDD = 5V, VPIN = VSS                                               |  |  |

|                    | Input Leakage Current (Notes 2, 3)         |           |                                                                                                                                                                                       |                               |            | -         |                                                                    |  |  |

| D060               | I/O ports                                  | lι∟       | -                                                                                                                                                                                     | -                             | <u>+</u> 1 | μΑ        | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-imped ance                   |  |  |

| D061               | тоскі                                      |           | -                                                                                                                                                                                     | -                             | <u>+</u> 5 | μA        | $Vss \leq VPIN \leq VDD$                                           |  |  |

| D063               | OSC1                                       |           | -                                                                                                                                                                                     | -                             | <u>+</u> 5 | μA        | Vss $\leq$ VPIN $\leq$ VDD, XT and LP osc configuration            |  |  |

|                    | Output Low Voltage                         |           |                                                                                                                                                                                       |                               |            |           |                                                                    |  |  |

| D080               | I/O ports                                  | Vol       | -                                                                                                                                                                                     | -                             | 0.6        | V         | IOL = 8.5 mA, VDD = 4.5V,<br>−40°C to +85°C                        |  |  |

| D080A              |                                            |           | -                                                                                                                                                                                     | -                             | 0.6        | V         | IOL = 7.0 mA, VDD = 4.5V,<br>−40°C to +125°C                       |  |  |

|                    | Output High Voltage                        |           |                                                                                                                                                                                       |                               |            |           |                                                                    |  |  |

| D090               | I/O ports (Note 3)                         | Vон       | Vdd - 0.7                                                                                                                                                                             | -                             | -          | V         | IOH = -3.0 mA, VDD = 4.5V,<br>−40°C to +85°C                       |  |  |

| D090A              |                                            |           | Vdd - 0.7                                                                                                                                                                             | -                             | -          | V         | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                      |  |  |

|                    | Capacitive Loading Specs on<br>Output Pins |           |                                                                                                                                                                                       |                               |            |           |                                                                    |  |  |

| D100               | OSC2 pin                                   | COSC<br>2 | -                                                                                                                                                                                     | -                             | 15         | pF        | In XT and LP modes when exter-<br>nal clock is used to drive OSC1. |  |  |

| D101               | All I/O pins                               | Сю        | -                                                                                                                                                                                     | -                             | 50         | pF        |                                                                    |  |  |

| †                  | Data in "Typ" column is at 5V, 25°C unles  | e othory  | vice stated                                                                                                                                                                           | Those                         | paramoto   | ro oro fo | r dealar auidenee entrend ere net                                  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C5XX be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: This spec. applies when GP3/MCLR is configured as MCLR. The leakage current of the MCLR circuit is higher than the standard I/O logic.

# TABLE 13-1: PULL-UP RESISTOR RANGES\* - PIC12C508A, PIC12C509A, PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Max  | Units |  |  |  |

|-------------|------------------|------|------|------|-------|--|--|--|

| GP0/GP1     |                  |      |      |      |       |  |  |  |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |  |  |  |

|             | 25               | 42K  | 48K  | 63K  | Ω     |  |  |  |

|             | 85               | 42K  | 49K  | 63K  | Ω     |  |  |  |

|             | 125              | 50K  | 55K  | 63K  | Ω     |  |  |  |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |  |  |  |

|             | 25               | 18K  | 20K  | 23K  | Ω     |  |  |  |

|             | 85               | 19K  | 22K  | 25K  | Ω     |  |  |  |

|             | 125              | 22K  | 24K  | 28K  | Ω     |  |  |  |

|             |                  | G    | P3   |      |       |  |  |  |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |  |  |  |

|             | 25               | 343K | 414K | 532K | Ω     |  |  |  |

|             | 85               | 368K | 457K | 532K | Ω     |  |  |  |

|             | 125              | 431K | 504K | 593K | Ω     |  |  |  |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |  |  |  |

|             | 25               | 288K | 341K | 437K | Ω     |  |  |  |

|             | 85               | 306K | 371K | 448K | Ω     |  |  |  |

|             | 125              | 351K | 407K | 500K | Ω     |  |  |  |

\* These parameters are characterized but not tested.

#### 13.6 Timing Diagrams and Specifications

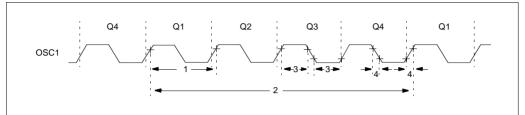

#### FIGURE 13-2: EXTERNAL CLOCK TIMING - PIC12C508A, PIC12C509A, PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

#### TABLE 13-2: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC12C508A, PIC12C509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| AC Characteristics |            | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ (commercial)}, \\ -40^\circ C \leq TA \leq +85^\circ C \mbox{ (industrial)}, \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 13.1} \end{array}$ |     |                    |        |       |                |  |  |

|--------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|--------|-------|----------------|--|--|

| Parameter<br>No.   | Sym        | Characteristic                                                                                                                                                                                                                                                                                                                                                                            | Min | Typ <sup>(1)</sup> | Мах    | Units | Conditions     |  |  |

|                    | Fosc       | External CLKIN Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                   |     |                    |        |       |                |  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                           | DC  | —                  | 4      | MHz   | XT osc mode    |  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                           | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

|                    |            | Oscillator Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                       | DC  | —                  | 4      | MHz   | EXTRC osc mode |  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                           | 0.1 | —                  | 4      | MHz   | XT osc mode    |  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                           | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

| 1                  | Tosc       | External CLKIN Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                      |     |                    |        |       |                |  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                           | 250 | —                  | —      | ns    | XT osc mode    |  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                           | 5   | _                  | —      | ms    | LP osc mode    |  |  |

|                    |            | Oscillator Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                          | 250 | _                  | —      | ns    | EXTRC osc mode |  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                           | 250 | —                  | 10,000 | ns    | XT osc mode    |  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                           | 5   | -                  | —      | ms    | LP osc mode    |  |  |

| 2 Tcy              |            | Instruction Cycle Time <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |     | 4/Fosc             | —      | —     |                |  |  |