Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 4MHz                                                                          |

| Connectivity               | -                                                                             |

| Peripherals                | POR, WDT                                                                      |

| Number of I/O              | 5                                                                             |

| Program Memory Size        | 1.5KB (1K x 12)                                                               |

| Program Memory Type        | OTP                                                                           |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 41 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | -                                                                             |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

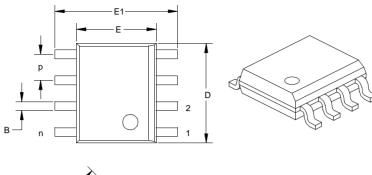

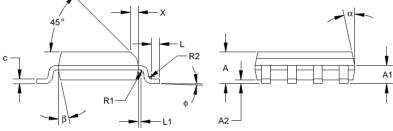

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 8-VDFN Exposed Pad                                                            |

| Supplier Device Package    | 8-DFN (3x3)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc509at-04i-mf |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC12C5XX from Microchip Technology is a family of low-cost, high performance, 8-bit, fully static, EEPROM/EPROM/ROM-based CMOS microcontrollers. It employs a RISC architecture with only 33 single word/single cycle instructions. All instructions are single cycle (1  $\mu$ s) except for program branches which take two cycles. The PIC12C5XX delivers performance an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

The PIC12C5XX products are equipped with special features that reduce system cost and power requirements. The Power-On Reset (POR) and Device Reset Timer (DRT) eliminate the need for external reset circuitry. There are four oscillator configurations to choose from, including INTRC internal oscillator mode and the power-saving LP (Low Power) oscillator mode. Power saving SLEEP mode, Watchdog Timer and code protection features also improve system cost, power and reliability.

The PIC12C5XX are available in the cost-effective One-Time-Programmable (OTP) versions which are suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers while benefiting from the OTP's flexibility.

The PIC12C5XX products are supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a 'C' compiler, fuzzy logic support tools, a low-cost development programmer, and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

## 1.1 Applications

The PIC12C5XX series fits perfectly in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The EPROM technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies. etc.) extremely fast and convenient, while the EEPROM data memory technology allows for the changing of calibration factors and security codes. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC12C5XX series very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic and PLD's in larger systems, coprocessor applications).

NOTES:

## 4.5 <u>OSCCAL Register</u>

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal 4 MHz oscillator. It contains four to six bits for calibration. Increasing the cal value increases the frequency. See Section 7.2.5 for more information on the internal oscillator.

## FIGURE 4-6: OSCCAL REGISTER (ADDRESS 05h) FOR PIC12C508 AND PIC12C509

| R/W-0                               | R/W-1                          | R/W-1 | R/W-1 | R/W-0 | R/W-0 | U-0 | U-0  |                                                                                                                      |

|-------------------------------------|--------------------------------|-------|-------|-------|-------|-----|------|----------------------------------------------------------------------------------------------------------------------|

| CAL3                                | CAL2                           | CAL1  | CAL0  | -     |       | —   | —    | R = Readable bit                                                                                                     |

| bit7                                |                                |       |       |       |       |     | bit0 | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7-4:                            | bit 7-4: CAL<3:0>: Calibration |       |       |       |       |     |      |                                                                                                                      |

| bit 3-0: Unimplemented: Read as '0' |                                |       |       |       |       |     |      |                                                                                                                      |

|                                     |                                |       |       |       |       |     |      |                                                                                                                      |

|                                     |                                |       |       |       |       |     |      |                                                                                                                      |

## FIGURE 4-7: OSCCAL REGISTER (ADDRESS 05h) FOR PIC12C508A/C509A/CR509A/12CE518/ 12CE519

| CAL5     CAL4     CAL3     CAL2     CAL1     CAL0     —     —     R     = Readable bit       bit7     bit0     bit0     U     = Writable bit     U     = Unimplemented bit, read en (10) | bit0 W = Writable bit |                  | CAL0 | CAL1 | 041.0 |      |      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|------|------|-------|------|------|------|

| U = Unimplemented bit,                                                                                                                                                                   | Dito                  | bit0 W = Writ    |      |      | CALZ  | CAL3 | CAL4 | CAL5 |

| - n = Value at POR reset                                                                                                                                                                 | read as '0'           | U = Unir<br>read |      |      |       | •    |      | bit7 |

| bit 7-2: CAL<5:0>: Calibration                                                                                                                                                           |                       | bit 7-2:         |      |      |       |      |      |      |

| bit 1-0: <b>Unimplemented:</b> Read as '0'                                                                                                                                               |                       | bit 1-0:         |      |      |       |      |      |      |

|                                                                                                                                                                                          |                       |                  |      |      |       |      |      |      |

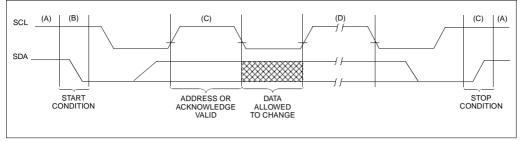

## FIGURE 7-3: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

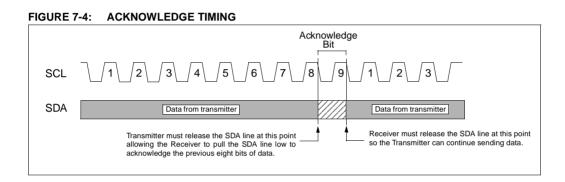

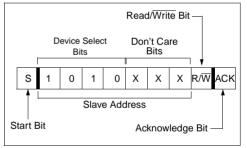

## 7.2 Device Addressing

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed. The slave address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

### FIGURE 7-5: CONTROL BYTE FORMAT

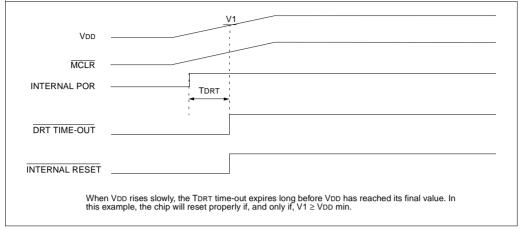

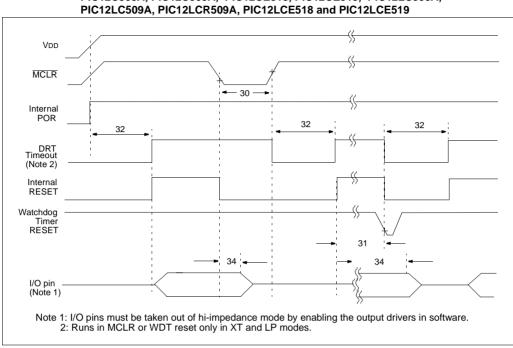

## FIGURE 8-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

### 8.5 Device Reset Timer (DRT)

In the PIC12C5XX, DRT runs from RESET and varies based on oscillator selection (see Table 8-5.)

The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min., and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after MCLR has reached a logic high (VIHMCLR) level. Thus, programming GP3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the GP3/MCLR/VPP pin as a general purpose input.

The Device Reset time delay will vary from chip to chip due to VDD, temperature, and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake from SLEEP mode automatically.

## 8.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the external RC oscillator of the GP5/OSC1/CLKIN pin and the internal 4 MHz oscillator. That means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT reset or wake-up reset generates a device RESET.

The  $\overline{TO}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer reset.

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 8.1). Refer to the PIC12C5XX Programming Specifications to determine how to access the configuration word.

TABLE 8-5: DRT (DEVICE RESET TIMER PERIOD)

| Oscillator<br>Configuration | POR Reset       | Subsequent<br>Resets |

|-----------------------------|-----------------|----------------------|

| IntRC &<br>ExtRC            | 18 ms (typical) | 300 µs (typical)     |

| XT & LP                     | 18 ms (typical) | 18 ms (typical)      |

| ADDWF                                                           | Add W and f                                                                                                                                                       |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                         | [ label ] ADDWF f,d                                                                                                                                               |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                       |

| Operation:                                                      | (W) + (f) $\rightarrow$ (dest)                                                                                                                                    |

| Status Affected:                                                | C, DC, Z                                                                                                                                                          |

| Encoding:                                                       | 0001 11df ffff                                                                                                                                                    |

| Description:                                                    | Add the contents of the W register and register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. |

| Words:                                                          | 1                                                                                                                                                                 |

| Cycles:                                                         | 1                                                                                                                                                                 |

| Example:                                                        | ADDWF FSR, 0                                                                                                                                                      |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>tion<br>0xD9                                                                                                                                      |

| ANDWF                          | AND W with f                                                                                                                                                                       |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] ANDWF f,d                                                                                                                                                                  |

| Operands:                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                                        |

| Operation:                     | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                 |

| Status Affected:               | Z                                                                                                                                                                                  |

| Encoding:                      | 0001 01df ffff                                                                                                                                                                     |

| Description:                   | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>'1' the result is stored back in register 'f'. |

| Words:                         | 1                                                                                                                                                                                  |

| Cycles:                        | 1                                                                                                                                                                                  |

| Example:                       | ANDWF FSR, 1                                                                                                                                                                       |

| Before Instru<br>W =<br>FSR =  | 0x17                                                                                                                                                                               |

| After Instruct<br>W =<br>FSR = | 0x17                                                                                                                                                                               |

| ANDLW                 | And literal with W                                                                                                      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:               | [ <i>label</i> ] ANDLW k                                                                                                |

| Operands:             | $0 \le k \le 255$                                                                                                       |

| Operation:            | (W).AND. (k) $\rightarrow$ (W)                                                                                          |

| Status Affected:      | Z                                                                                                                       |

| Encoding:             | 1110 kkkk kkkk                                                                                                          |

| Description:          | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'. The<br>result is placed in the W register. |

| Words:                | 1                                                                                                                       |

| Cycles:               | 1                                                                                                                       |

| Example:              | ANDLW 0x5F                                                                                                              |

| Before Instru<br>W =  | iction<br>0xA3                                                                                                          |

| After Instruct<br>W = | tion<br>0x03                                                                                                            |

| BCF                                   | Bit Clear                                                          | f             |          |  |

|---------------------------------------|--------------------------------------------------------------------|---------------|----------|--|

| Syntax:                               | [label] E                                                          | BCF f,b       | )        |  |

| Operands:                             | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |               |          |  |

| Operation:                            | $0 \rightarrow (f < b;$                                            | >)            |          |  |

| Status Affected:                      | None                                                               |               |          |  |

| Encoding:                             | 0100                                                               | bbbf          | ffff     |  |

| Description:                          | Bit 'b' in re                                                      | gister 'f' is | cleared. |  |

| Words:                                | 1                                                                  |               |          |  |

| Cycles:                               | 1                                                                  |               |          |  |

| Example:                              | BCF                                                                | FLAG_REC      | 3, 7     |  |

| Before Instruction<br>FLAG_REG = 0xC7 |                                                                    |               |          |  |

| After Instruction<br>FLAG_REG = 0x47  |                                                                    |               |          |  |

| BSF                                  | Bit Set f                                                                                                                    | BTFSS            | Bit Test f, Skip if Set                                                                |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------|--|--|

| Syntax:                              | [label] BSF f,b                                                                                                              | Syntax:          | [label] BTFSS f,b                                                                      |  |  |

| Operands:                            | $0 \le f \le 31$ $0 \le b \le 7$                                                                                             | Operands:        | $0 \le f \le 31$<br>$0 \le b < 7$                                                      |  |  |

| Operation:                           | $1 \rightarrow (f < b >)$                                                                                                    | Operation:       | skip if (f <b>) = 1</b>                                                                |  |  |

| Status Affected:                     | None                                                                                                                         | Status Affected: | None                                                                                   |  |  |

| Encoding:                            | 0101 bbbf ffff                                                                                                               | Encoding:        | 0111 bbbf ffff                                                                         |  |  |

| Description:                         | Bit 'b' in register 'f' is set.                                                                                              | Description:     | If bit 'b' in register 'f' is '1' then the next                                        |  |  |

| Words:                               | 1                                                                                                                            |                  | instruction is skipped.                                                                |  |  |

| Cycles:                              | 1                                                                                                                            |                  | If bit 'b' is '1', then the next instruction<br>fetched during the current instruction |  |  |

| Example:                             | BSF FLAG_REG, 7                                                                                                              |                  | execution, is discarded and an NOP is                                                  |  |  |

| Before Instru                        | uction                                                                                                                       |                  | executed instead, making this a 2 cycle instruction.                                   |  |  |

| _                                    | EG = 0x0A                                                                                                                    | Words:           | 1                                                                                      |  |  |

| After Instruction<br>FLAG REG = 0x8A |                                                                                                                              | Cycles:          | 1(2)                                                                                   |  |  |

| FLAG_K                               |                                                                                                                              | Example:         | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CODE                                           |  |  |

| BTFSC                                | Bit Test f, Skip if Clear                                                                                                    |                  | TRUE •                                                                                 |  |  |

| Syntax:                              | [ label ] BTFSC f,b                                                                                                          |                  | •                                                                                      |  |  |

| Operands:                            | $0 \le f \le 31$                                                                                                             | Before Instr     | uction                                                                                 |  |  |

|                                      | $0 \le b \le 7$                                                                                                              | PC               | = address (HERE)                                                                       |  |  |

| Operation:                           | skip if $(f < b >) = 0$                                                                                                      | After Instruc    |                                                                                        |  |  |

| Status Affected:                     | None                                                                                                                         | If FLAG<br>PC    | <1> = 0,<br>= address (FALSE);                                                         |  |  |

| Encoding:                            | 0110 bbbf ffff                                                                                                               | if FLAG<         | <1> = 1,                                                                               |  |  |

| Description:                         | If bit 'b' in register 'f' is 0 then the next instruction is skipped.                                                        | PC               | = address (TRUE)                                                                       |  |  |

|                                      | If bit 'b' is 0 then the next instruction<br>fetched during the current instruction<br>execution is discarded, and an NOP is |                  |                                                                                        |  |  |

executed instead, making this a 2 cycle

BTFSC FLAG,1

address (HERE)

address (TRUE);

address(FALSE)

PROCESS\_CODE

GOTO

٠ •

0, =

1, =

instruction.

1

1(2)

HERE

TRUE

Before Instruction PC

After Instruction if FLAG<1>

if FLAG<1>

PC

PC

FALSE

=

=

=

Words:

Cycles:

Example:

| INCF                      | Increment f                                                                                                                                                         |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                   | [label] INCF f,d                                                                                                                                                    |

| Operands:                 | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                           |

| Operation:                | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected:          | Z                                                                                                                                                                   |

| Encoding:                 | 0010 10df ffff                                                                                                                                                      |

| Description:              | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |

| Words:                    | 1                                                                                                                                                                   |

| Cycles:                   | 1                                                                                                                                                                   |

| Example:                  | INCF CNT, 1                                                                                                                                                         |

| Before Instru<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                       |

| After Instruct            |                                                                                                                                                                     |

| CNT<br>Z                  | = 0x00<br>= 1                                                                                                                                                       |

|                           |                                                                                                                                                                     |

| INCFSZ                    | Increment f, Skip if 0                                                                                                                                              |

| Syntax:                   | [label] INCFSZ f,d                                                                                                                                                  |

| Operands:                 | $0 \le f \le 31$                                                                                                                                                    |

| Syntax:                                             | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:                                           | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                 |

| Operation:                                          | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                                 |

| Status Affected:                                    | None                                                                                                                                                                                                                                                                                                                                             |

| Encoding:                                           | 0011 11df ffff                                                                                                                                                                                                                                                                                                                                   |

| Description:                                        | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, then the next instruc-<br>tion, which is already fetched, is dis-<br>carded and an NOP is executed<br>instead making it a two cycle instruc-<br>tion. |

| Words:                                              | 1                                                                                                                                                                                                                                                                                                                                                |

| Cycles:                                             | 1(2)                                                                                                                                                                                                                                                                                                                                             |

| Example:                                            | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                                  |

|                                                     | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                                  |

| Before Inst<br>PC                                   | ruction<br>= address (HERE)                                                                                                                                                                                                                                                                                                                      |

| After Instru<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | = CNT + 1;                                                                                                                                                                                                                                                                                                                                       |

| IORLW                       | Inclusive OR literal with W                                                                                            |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | [ <i>label</i> ] IORLW k                                                                                               |

| Operands:                   | $0 \le k \le 255$                                                                                                      |

| Operation:                  | (W) .OR. (k) $\rightarrow$ (W)                                                                                         |

| Status Affected:            | Z                                                                                                                      |

| Encoding:                   | 1101 kkkk kkkk                                                                                                         |

| Description:                | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:                      | 1                                                                                                                      |

| Cycles:                     | 1                                                                                                                      |

| Example:                    | IORLW 0x35                                                                                                             |

| Before Instru<br>W =        | uction<br>0x9A                                                                                                         |

| After Instruc<br>W =<br>Z = | tion<br>0xBF<br>0                                                                                                      |

| IORWF                                     | Inclusive OR W with f                                                                                                                                                |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                   | [ label ] IORWF f,d                                                                                                                                                  |

| Operands:                                 | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                         |

| Operation:                                | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                     |

| Status Affected                           | I: Z                                                                                                                                                                 |

| Encoding:                                 | 0001 00df ffff                                                                                                                                                       |

| Description:                              | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |

| Words:                                    | 1                                                                                                                                                                    |

| Cycles:                                   | 1                                                                                                                                                                    |

| Example:                                  | IORWF RESULT, 0                                                                                                                                                      |

| Before Inst<br>RESUL<br>W<br>After Instru | LT = 0x13<br>= 0x91                                                                                                                                                  |

| RESUL<br>W<br>Z                           |                                                                                                                                                                      |

| SWAPF                       | Swap Nibbles in f                                                                                                                                                     |  |  |  |  |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                     | [label] SWAPF f,d                                                                                                                                                     |  |  |  |  |  |  |  |

| Operands:                   | $\begin{array}{l} 0\leq f\leq 31\\ d\in \left[0,1\right] \end{array}$                                                                                                 |  |  |  |  |  |  |  |

| Operation:                  | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                             |  |  |  |  |  |  |  |

| Status Affected:            | None                                                                                                                                                                  |  |  |  |  |  |  |  |

| Encoding:                   | 0011 10df ffff                                                                                                                                                        |  |  |  |  |  |  |  |

| Description:                | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |  |  |  |  |  |  |  |

| Words:                      | 1                                                                                                                                                                     |  |  |  |  |  |  |  |

| Cycles:                     | 1                                                                                                                                                                     |  |  |  |  |  |  |  |

| Example                     | SWAPF REG1, 0                                                                                                                                                         |  |  |  |  |  |  |  |

| Before Instru<br>REG1       | iction<br>= 0xA5                                                                                                                                                      |  |  |  |  |  |  |  |

| After Instruct<br>REG1<br>W | tion<br>= 0xA5<br>= 0X5A                                                                                                                                              |  |  |  |  |  |  |  |

| TRIS                   | Load TRIS Register                                                          |  |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                | [label] TRIS f                                                              |  |  |  |  |  |

| Operands:              | f = 6                                                                       |  |  |  |  |  |

| Operation:             | (W) $\rightarrow$ TRIS register f                                           |  |  |  |  |  |

| Status Affected:       | None                                                                        |  |  |  |  |  |

| Encoding:              | 0000 0000 0fff                                                              |  |  |  |  |  |

| Description:           | TRIS register 'f' ( $f = 6$ ) is loaded with the contents of the W register |  |  |  |  |  |

| Words:                 | 1                                                                           |  |  |  |  |  |

| Cycles:                | 1                                                                           |  |  |  |  |  |

| Example                | TRIS GPIO                                                                   |  |  |  |  |  |

| Before Instru<br>W     | iction<br>= 0XA5                                                            |  |  |  |  |  |

| After Instruct<br>TRIS |                                                                             |  |  |  |  |  |

| <b>Note:</b> f = 6 f   | or PIC12C5XX only.                                                          |  |  |  |  |  |

| XORLW                | Exclusiv                                                                                                                | ve OR lite    | ral with | w |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|---------------|----------|---|--|--|--|

| Syntax:              | [ <i>label</i> ]                                                                                                        | XORLW         | k        |   |  |  |  |

| Operands:            | $0 \le k \le 2$                                                                                                         | 55            |          |   |  |  |  |

| Operation:           | (W) .XO                                                                                                                 | $R. k \to (W$ | /)       |   |  |  |  |

| Status Affected:     | Affected: Z                                                                                                             |               |          |   |  |  |  |

| Encoding:            | 1111                                                                                                                    | kkkk          | kkkk     |   |  |  |  |

| Description:         | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |               |          |   |  |  |  |

| Words:               | 1                                                                                                                       |               |          |   |  |  |  |

| Cycles:              | 1                                                                                                                       |               |          |   |  |  |  |

| Example:             | XORLW                                                                                                                   | 0xAF          |          |   |  |  |  |

| Before Instru<br>W = | uction<br>0xB5                                                                                                          |               |          |   |  |  |  |

| After Instruc<br>W = | tion<br>0x1A                                                                                                            |               |          |   |  |  |  |

| XORWF                                              | Exclusive OR W with f                                                                                                                                                     |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                            | [label] XORWF f,d                                                                                                                                                         |

| Operands:                                          | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                          |

| Operation:                                         | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected:                                   | Z                                                                                                                                                                         |

| Encoding:                                          | 0001 10df ffff                                                                                                                                                            |

| Description:                                       | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |

| Words:                                             | 1                                                                                                                                                                         |

| Cycles:                                            | 1                                                                                                                                                                         |

| Example                                            | XORWF REG,1                                                                                                                                                               |

| Before Instru<br>REG<br>W<br>After Instruct<br>REG | = 0xAF<br>= 0xB5<br>ion<br>= 0x1A                                                                                                                                         |

| W                                                  | = 0xB5                                                                                                                                                                    |

## 11.2 DC CHARACTERISTICS:

## PIC12C508/509 (Commercial, Industrial, Extended)

|              |                                                                |                                                                                    | <b>rd Operati</b><br>ng tempera | -    | 0°C ≤              | TA ≤ + | s otherwise specified)<br>70°C (commercial)                         |  |  |  |

|--------------|----------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------|------|--------------------|--------|---------------------------------------------------------------------|--|--|--|

| DC CHA       | ARACTERISTICS                                                  | –40°C ≤ TA ≤ +85°C (industrial)<br>–40°C ≤ TA ≤ +125°C (extended)                  |                                 |      |                    |        |                                                                     |  |  |  |

|              |                                                                | Operating voltage VDD range as described in DC spec Section 11.1 and Section 11.2. |                                 |      |                    |        |                                                                     |  |  |  |

| Param<br>No. | Characteristic                                                 | Sym                                                                                | Min                             | Тур† | Max                | Units  | Conditions                                                          |  |  |  |

| NO.          |                                                                |                                                                                    |                                 |      |                    |        |                                                                     |  |  |  |

|              | Input Low Voltage                                              | VIL                                                                                |                                 |      |                    |        |                                                                     |  |  |  |

| <b>D</b> 000 | •                                                              | VIL                                                                                | Vee                             | -    | 0.01/              | V      |                                                                     |  |  |  |

| D030         | with TTL buffer                                                |                                                                                    | Vss                             | -    | 0.8V               | V      | 4.5 < VDD ≤ 5.5V                                                    |  |  |  |

| D031         | with Coheritt Trigger huffer                                   |                                                                                    | Vee                             | -    | 0.15VDD<br>0.15VDD | V<br>V | otherwise                                                           |  |  |  |

| D031<br>D032 | with Schmitt Trigger buffer<br>MCLR, GP2/T0CKI (in EXTRC mode) |                                                                                    | Vss<br>Vss                      | -    | 0.15VDD<br>0.15VDD | V      |                                                                     |  |  |  |

|              |                                                                |                                                                                    | VSS<br>VSS                      | -    | 0.15VDD            | v      |                                                                     |  |  |  |

| D033         | OSC1 (EXTRC) <sup>(1)</sup>                                    |                                                                                    |                                 | -    |                    |        |                                                                     |  |  |  |

| D033         | OSC1 (in XT and LP)                                            |                                                                                    | Vss                             | -    | 0.3Vdd             | V      | Note1                                                               |  |  |  |

|              | Input High Voltage                                             |                                                                                    |                                 |      |                    |        |                                                                     |  |  |  |

|              | I/O ports                                                      | VIH                                                                                |                                 | -    |                    |        |                                                                     |  |  |  |

| D040         | with TTL buffer                                                | Vss                                                                                | 2.0V                            | -    | Vdd                | V      | $4.5 \leq VDD \leq 5.5V$                                            |  |  |  |

| D040A        |                                                                |                                                                                    | 0.25VDD+<br>0.8V                | -    | Vdd                | V      | otherwise                                                           |  |  |  |

| D041         | with Schmitt Trigger buffer                                    |                                                                                    | 0.85VDD                         | -    | VDD                | v      | For entire VDD range                                                |  |  |  |

| D042         | MCLR/GP2/T0CKI                                                 |                                                                                    | 0.85VDD                         | -    | VDD                | v      |                                                                     |  |  |  |

| -            |                                                                |                                                                                    | 0.7VDD                          | -    | VDD                | V      | Note1                                                               |  |  |  |

| D043         | OSC1 (in EXTRC mode)                                           |                                                                                    | 0.85VDD                         | -    | VDD                | V      |                                                                     |  |  |  |

| D070         | GPIO weak pull-up current                                      | IPUR                                                                               | 50                              | 250  | 400                | μA     | VDD = 5V, VPIN = VSS                                                |  |  |  |

|              | Input Leakage Current <sup>(2, 3)</sup>                        |                                                                                    |                                 |      |                    | 1.     | For VDD ≤5.5V                                                       |  |  |  |

| D060         | I/O ports                                                      | ١L                                                                                 | -1                              | 0.5  | <u>+</u> 1         | μΑ     | Vss ≤ VPIN ≤ VDD,<br>Pin at hi-impedance                            |  |  |  |

| D061         | MCLR, GP2/T0CKI                                                |                                                                                    | 20                              | 130  | 250                | μA     | $V_{PIN} = V_{SS} + 0.25 V^{(2)}$                                   |  |  |  |

| 2001         |                                                                |                                                                                    |                                 | 0.5  | +5                 | μΑ     | VPIN = VDD                                                          |  |  |  |

| D063         | OSC1                                                           |                                                                                    | -3                              | 0.5  | +3                 | μΑ     | $Vss \le VPIN \le VDD$ ,                                            |  |  |  |

|              |                                                                |                                                                                    |                                 |      |                    |        | XT and LP options                                                   |  |  |  |

|              | Output Low Voltage                                             |                                                                                    |                                 |      |                    |        |                                                                     |  |  |  |

| D080         | I/O ports/CLKOUT                                               | Vol                                                                                | -                               | -    | 0.6                | V      | IOL = 8.7 mA, VDD = 4.5V                                            |  |  |  |

|              | Output High Voltage                                            |                                                                                    |                                 |      |                    |        |                                                                     |  |  |  |

| D090         | I/O ports/CLKOUT (3)                                           | Voh                                                                                | Vdd - 0.7                       | -    | -                  | V      | IOH = -5.4 mA, VDD = 4.5V                                           |  |  |  |

|              | Capacitive Loading Specs on                                    |                                                                                    |                                 |      |                    |        |                                                                     |  |  |  |

|              | Output Pins                                                    |                                                                                    |                                 |      |                    |        |                                                                     |  |  |  |

| D100         | OSC2 pin                                                       | Cosc2                                                                              | -                               | -    | 15                 | pF     | In XT and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101         | All I/O pins                                                   | Cio                                                                                | -                               | -    | 50                 | pF     |                                                                     |  |  |  |

|              | Data in "Typ" column is at 51/ 25°C ur                         |                                                                                    |                                 |      |                    |        | l                                                                   |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C5XX be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

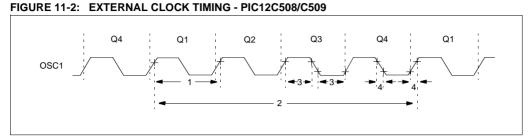

## 11.4 Timing Diagrams and Specifications

| AC Chara         | cteristics | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq Ta \leq +70^{\circ}C \mbox{ (commercial)}, \\ -40^{\circ}C \leq Ta \leq +85^{\circ}C \mbox{ (industrial)}, \\ -40^{\circ}C \leq Ta \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 11.1} \end{array} $ |     |                    |        |       |                |  |  |

|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|--------|-------|----------------|--|--|

| Parameter<br>No. | Sym        | Characteristic                                                                                                                                                                                                                                                                                                                                                                                    | Min | Typ <sup>(1)</sup> | Мах    | Units | Conditions     |  |  |

|                  | Fosc       | External CLKIN Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                           |     |                    |        |       |                |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | DC  | —                  | 4      | MHz   | XT osc mode    |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

|                  |            | Oscillator Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                               |     |                    |        |       |                |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | 0.1 | _                  | 4      | MHz   | XT osc mode    |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | DC  | —                  | 200    | kHz   | LP osc mode    |  |  |

| 1                | Tosc       | External CLKIN Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                              | 250 | —                  | _      | ns    | EXTRC osc mode |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | 250 | _                  | _      | ns    | XT osc mode    |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | 5   | —                  | —      | ms    | LP osc mode    |  |  |

|                  |            | Oscillator Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                  | 250 | _                  | _      | ns    | EXTRC osc mode |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | 250 | _                  | 10,000 | ns    | XT osc mode    |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | 5   | —                  | —      | ms    | LP osc mode    |  |  |

| 2                | Тсу        | Instruction Cycle Time <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                             | —   | 4/Fosc             | —      |       |                |  |  |

| 3                | TosL, TosH | Clock in (OSC1) Low or High Time                                                                                                                                                                                                                                                                                                                                                                  | 50* | —                  | —      | ns    | XT oscillator  |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | 2*  | _                  | —      | ms    | LP oscillator  |  |  |

| 4                | TosR, TosF | Clock in (OSC1) Rise or Fall Time                                                                                                                                                                                                                                                                                                                                                                 | —   | -                  | 25*    | ns    | XT oscillator  |  |  |

|                  |            |                                                                                                                                                                                                                                                                                                                                                                                                   | —   | —                  | 50*    | ns    | LP oscillator  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

3: Instruction cycle period (TCY) equals four times the input oscillator time base period.

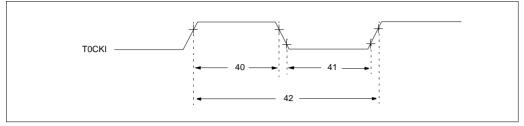

## FIGURE 11-5: TIMER0 CLOCK TIMINGS - PIC12C508/C509

## TABLE 11-7: TIMER0 CLOCK REQUIREMENTS - PIC12C508/C509

| AC               | Charao |                                       |                      |                              |                    |     |       |                                                                |

|------------------|--------|---------------------------------------|----------------------|------------------------------|--------------------|-----|-------|----------------------------------------------------------------|

| Parameter<br>No. | Sym    | Characteristic                        | •                    | Min                          | Тур <sup>(1)</sup> | Max | Units | Conditions                                                     |

| 40               | Tt0H   | T0CKI High Pulse Width - No Prescaler |                      | 0.5 TCY + 20*                | -                  | _   | ns    |                                                                |

|                  |        |                                       | - With Prescaler     | 10*                          | —                  | —   | ns    |                                                                |

| 41               | Tt0L   | T0CKI Low Pulse W                     | /idth - No Prescaler | 0.5 TCY + 20*                | —                  | —   | ns    |                                                                |

|                  |        |                                       | - With Prescaler     | 10*                          | _                  | —   | ns    |                                                                |