Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 4MHz                                                                          |

| Connectivity               | -                                                                             |

| Peripherals                | POR, WDT                                                                      |

| Number of I/O              | 5                                                                             |

| Program Memory Size        | 1.5KB (1K x 12)                                                               |

| Program Memory Type        | OTP                                                                           |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 41 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | -                                                                             |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 8-SOIJ                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc509at-04i-sm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |                                               | PIC12C508(A)           | PIC12C509(A)           | PIC12CR509A        | PIC12CE518             | PIC12CE519             | PIC12C671              | PIC12C672              | PIC12CE673       | PIC12CE674       |

|-------------|-----------------------------------------------|------------------------|------------------------|--------------------|------------------------|------------------------|------------------------|------------------------|------------------|------------------|

| Clock       | Maximum<br>Frequency<br>of Operation<br>(MHz) | 4                      | 4                      | 4                  | 4                      | 4                      | 10                     | 10                     | 10               | 10               |

| Memory      | EPROM<br>Program<br>Memory                    | 512 x 12               | 1024 x 12              | 1024 x 12<br>(ROM) | 512 x 12               | 1024 x 12              | 1024 x 14              | 2048 x 14              | 1024 x 14        | 2048 x 14        |

| wemory      | RAM Data<br>Memory<br>(bytes)                 | 25                     | 41                     | 41                 | 25                     | 41                     | 128                    | 128                    | 128              | 128              |

|             | EEPROM<br>Data Memory<br>(bytes)              | —                      | -                      | —                  | 16                     | 16                     | —                      | —                      | 16               | 16               |

| Peripherals | Timer<br>Module(s)                            | TMR0                   | TMR0                   | TMR0               | TMR0                   | TMR0                   | TMR0                   | TMR0                   | TMR0             | TMR0             |

|             | A/D Con-<br>verter (8-bit)<br>Channels        | —                      | _                      | —                  | —                      | —                      | 4                      | 4                      | 4                | 4                |

|             | Wake-up<br>from SLEEP<br>on pin<br>change     | Yes                    | Yes                    | Yes                | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | Interrupt<br>Sources                          | —                      | -                      | _                  |                        |                        | 4                      | 4                      | 4                | 4                |

| Features    | I/O Pins                                      | 5                      | 5                      | 5                  | 5                      | 5                      | 5                      | 5                      | 5                | 5                |

|             | Input Pins                                    | 1                      | 1                      | 1                  | 1                      | 1                      | 1                      | 1                      | 1                | 1                |

|             | Internal<br>Pull-ups                          | Yes                    | Yes                    | Yes                | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | In-Circuit<br>Serial<br>Programming           | Yes                    | Yes                    | —                  | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes              |

|             | Number of<br>Instructions                     | 33                     | 33                     | 33                 | 33                     | 33                     | 35                     | 35                     | 35               | 35               |

|             | Packages                                      | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW | 8-pin DIP,<br>JW |

#### TABLE 1-1: PIC12CXXX & PIC12CEXXX FAMILY OF DEVICES

All PIC12CXXX & PIC12CEXXX devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability.

All PIC12CXXX & PIC12CEXXX devices use serial programming with data pin GP0 and clock pin GP1.

PIC12C5XX

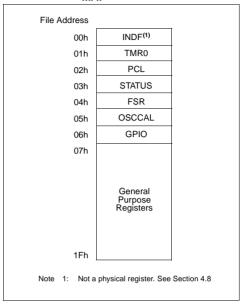

#### 4.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: special function registers and general purpose registers.

The special function registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports), and the File Select Register (FSR). In addition, special purpose registers are used to control the I/O port configuration and prescaler options.

The general purpose registers are used for data and control information under command of the instructions.

For the PIC12C508, PIC12C508A and PIC12CE518, the register file is composed of 7 special function registers and 25 general purpose registers (Figure 4-2).

For the PIC12C509, PIC12C509A, PIC12CR509A, and PIC12CE519 the register file is composed of 7 special function registers, 25 general purpose registers, and 16 general purpose registers that may be addressed using a banking scheme (Figure 4-3).

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The general purpose register file is accessed either directly or indirectly through the file select register FSR (Section 4.8).

#### FIGURE 4-2: PIC12C508, PIC12C508A AND PIC12CE518 REGISTER FILE MAP

| FSR<6:5>-    | •    | 00                  | 01                       |

|--------------|------|---------------------|--------------------------|

| File Address | · ·  |                     | 1                        |

| 00h          |      | INDF <sup>(1)</sup> | 20h                      |

| <b>∲</b> 01h |      | TMR0                |                          |

| 02h          |      | PCL                 | _                        |

| 03h          |      | STATUS              | Addresses map<br>back to |

| 04h          |      | FSR                 | addresses                |

| 05h          |      | OSCCAL              | in Bank 0.               |

| 06h          |      | GPIO                |                          |

| 07h          |      |                     | 1                        |

|              |      | General<br>Purpose  |                          |

|              |      | Registers           |                          |

| 0Fh          |      | 0                   | 2Fh                      |

|              | 10h  |                     | 30h                      |

|              |      | General             | General                  |

|              |      | Purpose             | Purpose                  |

|              |      | Registers           | Registers                |

|              | 1Fh  |                     | 3Fh                      |

|              |      | Bank 0              | Bank 1                   |

| Note 1       | : No | t a physical regi   | ster. See Section 4.8    |

|              |      |                     |                          |

#### FIGURE 4-3: PIC12C509, PIC12C509A, PIC12CR509A AND PIC12CE519 REGISTER FILE MAP

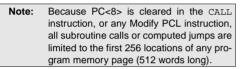

#### 4.6 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4-8).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-8).

Instructions where the PCL is the destination, or Modify PCL instructions, include <code>MOVWF PC</code>, <code>ADDWF PC</code>, and <code>BSF PC</code>, <code>5</code>.

#### FIGURE 4-8: LOADING OF PC BRANCH INSTRUCTIONS -PIC12C5XX

#### 4.6.1 EFFECTS OF RESET

The Program Counter is set upon a RESET, which means that the PC addresses the last location in the last page i.e., the oscillator calibration instruction. After executing MOVLW XX, the PC will roll over to location 00h, and begin executing user code.

The STATUS register page preselect bits are cleared upon a RESET, which means that page 0 is pre-selected.

Therefore, upon a RESET, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

#### 4.7 Stack

PIC12C5XX devices have a 12-bit wide L.I.F.O. hardware push/pop stack.

A CALL instruction will *push* the current value of stack 1 into stack 2 and then push the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will *pop* the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

Upon any reset, the contents of the stack remain unchanged, however the program counter (PCL) will also be reset to 0.

- Note 1: There are no STATUS bits to indicate stack overflows or stack underflow conditions.

- Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL and RETLW instructions.

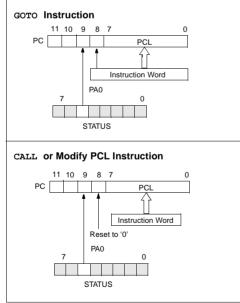

#### 7.3 WRITE OPERATIONS

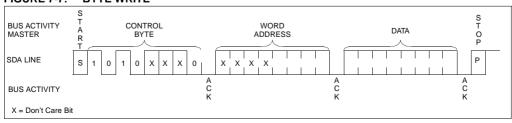

#### 7.3.1 BYTE WRITE

Following the start signal from the master, the device code (4 bits), the don't care bits (3 bits), and the R/Wbit (which is a logic low) are placed onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the master is the word address and will be written into the address pointer. Only the lower four address bits are used by the device, and the upper four bits are don't cares. The address byte is acknowledgeable and the master device will then transmit the data word to be written into the addressed memory location. The memorv acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time will not generate acknowledge signals (Figure 7-7). After a byte write command, the internal address counter will not be incremented and will point to the same address location that was just written. If a stop bit is transmitted to the device at any point in the write command sequence before the entire sequence is complete, then the command will abort and no data will be written. If more than 8 data bits are transmitted before the stop bit is sent, then the device will clear the previously loaded byte and begin loading the data buffer again. If more than one data byte is transmitted to the device and a stop bit is sent before a full eight data bits have been transmitted, then the write command will abort and no data will be written. The EEPROM memory employs a Vcc threshold detector circuit which disables the internal erase/write logic if the Vcc is below minimum VDD.

Byte write operations must be preceded and immediately followed by a bus not busy bus cycle where both SDA and SCL are held high.

#### 7.4 ACKNOWLEDGE POLLING

Since the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the master, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master sending a start condition followed by the control byte for a write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-6 for flow diagram.

#### FIGURE 7-6: ACKNOWLEDGE POLLING FLOW

FIGURE 7-7: BYTE WRITE

#### 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC12C5XX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- LP: Low Power Crystal

- XT: Crystal/Resonator

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

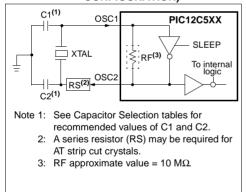

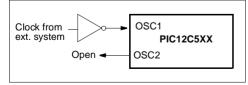

## 8.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC12C5XX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/ OSC1/CLKIN pin (Figure 8-3).

#### FIGURE 8-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT OR LP OSC CONFIGURATION)

#### FIGURE 8-3: EXTERNAL CLOCK INPUT OPERATION (XT OR LP OSC CONFIGURATION)

#### TABLE 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C5XX

| Osc  | Resonator | Cap. Range | Cap. Range |

|------|-----------|------------|------------|

| Type | Freq      | C1         | C2         |

| XT   | 4.0 MHz   | 30 pF      | 30 pF      |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC12C5XX

| Osc<br>Type | Resonator<br>Freq     | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 200 kHz               | 47-68 pF        | 47-68 pF         |

|             | 1 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

TABLE 8-3: RESET CONDITIONS FOR REGISTERS

| Register                                                                    | Address | Power-on Reset | MCLR Reset<br>WDT time-out<br>Wake-up on Pin Change |

|-----------------------------------------------------------------------------|---------|----------------|-----------------------------------------------------|

| W (PIC12C508/509)                                                           | _       | qqqq xxxx (1)  | qqqq uuuu (1)                                       |

| W (PIC12C508A/509A/<br>PIC12CE518/519/<br>PIC12CE509A)                      | _       | qqqq qqxx (1)  | qqqq qquu (1)                                       |

| INDF                                                                        | 00h     | xxxx xxxx      | uuuu uuuu                                           |

| TMR0                                                                        | 01h     | xxxx xxxx      | uuuu uuuu                                           |

| PC                                                                          | 02h     | 1111 1111      | 1111 1111                                           |

| STATUS                                                                      | 03h     | 0001 1xxx      | q00q quuu (2,3)                                     |

| FSR (PIC12C508/<br>PIC12C508A/<br>PIC12CE518)                               | 04h     | 111x xxxx      | 111u uuuu                                           |

| FSR (PIC12C509/<br>PIC12C509A/<br>PIC12CE519/<br>PIC12CR509A)               | 04h     | 110x xxxx      | 11uu uuuu                                           |

| OSCCAL<br>(PIC12C508/509)                                                   | 05h     | 0111           | uuuu                                                |

| OSCCAL<br>(PIC12C508A/509A/<br>PIC12CE518/512/<br>PIC12CR509A)              | 05h     | 1000 00        | uuuu uu                                             |

| GPIO<br>(PIC12C508/PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CR509A) | 06h     | xx xxxx        | uu uuuu                                             |

| GPIO<br>(PIC12CE518/                                                        | 06h     | 11             | 11                                                  |

| PIC12CE519)<br>OPTION                                                       |         | 11xx xxxx      | 11uu uuuu                                           |

| TRIS                                                                        | —       | 1111 1111      | 1111 1111                                           |

| IKIS                                                                        |         | 11 1111        | 11 1111                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

Note 2: See Table 8-7 for reset value for specific conditions

**Note 3:** If reset was due to wake-up on pin change, then bit 7 = 1. All other resets will cause bit 7 = 0.

#### TABLE 8-4: RESET CONDITION FOR SPECIAL REGISTERS

|                                    | STATUS Addr: 03h | PCL Addr: 02h |  |  |

|------------------------------------|------------------|---------------|--|--|

| Power on reset                     | 0001 1xxx        | 1111 1111     |  |  |

| MCLR reset during normal operation | 000u uuuu        | 1111 1111     |  |  |

| MCLR reset during SLEEP            | 0001 0uuu        | 1111 1111     |  |  |

| WDT reset during SLEEP             | 0000 Ouuu        | 1111 1111     |  |  |

| WDT reset normal operation         | 0000 uuuu        | 1111 1111     |  |  |

| Wake-up from SLEEP on pin change   | 1001 Ouuu        | 1111 1111     |  |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

## PIC12C5XX

| MOVF                                           | Move f                                                                                                                                                                                                                               |  |  |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                        | [label] MOVF f,d                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Operands:                                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                            |  |  |  |  |  |  |

| Operation:                                     | $(f) \rightarrow (dest)$                                                                                                                                                                                                             |  |  |  |  |  |  |

| Status Affected:                               | Z                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Encoding:                                      | 0010 00df ffff                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:                                   | The contents of register 'f' is moved to destination 'd'. If 'd' is 0, destination is the W register. If 'd' is 1, the destination is file register 'f'. 'd' is 1 is useful to test a file register since status flag Z is affected. |  |  |  |  |  |  |

| Words:                                         | 1                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:                                        | 1                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Example:                                       | MOVF FSR, 0                                                                                                                                                                                                                          |  |  |  |  |  |  |

| After Instruction<br>W = value in FSR register |                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| MOVLW                | Move Lit        | eral to W                     | I    |  |  |  |

|----------------------|-----------------|-------------------------------|------|--|--|--|

| Syntax:              | [ label ]       | MOVLW                         | k    |  |  |  |

| Operands:            | $0 \le k \le 2$ | 55                            |      |  |  |  |

| Operation:           | $k \to (W)$     |                               |      |  |  |  |

| Status Affected:     | None            |                               |      |  |  |  |

| Encoding:            | 1100            | kkkk                          | kkkk |  |  |  |

| Description:         | 0               | bit literal 'k<br>r. The don' |      |  |  |  |

| Words:               | 1               |                               |      |  |  |  |

| Cycles:              | 1               |                               |      |  |  |  |

| Example:             | MOVLW           | 0x5A                          |      |  |  |  |

| After Instruc<br>W = | tion<br>0x5A    |                               |      |  |  |  |

| MOVWF                         | Move W to f                                                |              |      |  |  |  |  |

|-------------------------------|------------------------------------------------------------|--------------|------|--|--|--|--|

| Syntax:                       | [ <i>label</i> ] MOVWF f                                   |              |      |  |  |  |  |

| Operands:                     | $0 \le f \le 31$                                           |              |      |  |  |  |  |

| Operation:                    | $(W) \to (f$                                               | )            |      |  |  |  |  |

| Status Affected:              | None                                                       |              |      |  |  |  |  |

| Encoding:                     | 0000                                                       | 001f         | ffff |  |  |  |  |

| Description:                  | Move data from the W register to register to register 'f'. |              |      |  |  |  |  |

| Words:                        | 1                                                          |              |      |  |  |  |  |

| Cycles:                       | 1                                                          |              |      |  |  |  |  |

| Example:                      | MOVWF                                                      | TEMP_REC     | 3    |  |  |  |  |

| Before Instru<br>TEMP_R<br>W  |                                                            | 0xFF<br>0x4F |      |  |  |  |  |

| After Instruct<br>TEMP_R<br>W |                                                            | 0x4F<br>0x4F |      |  |  |  |  |

| NOP              | No Operation |             |      |  |  |  |  |  |

|------------------|--------------|-------------|------|--|--|--|--|--|

| Syntax:          | [ label ]    | [label] NOP |      |  |  |  |  |  |

| Operands:        | None         |             |      |  |  |  |  |  |

| Operation:       | No operation |             |      |  |  |  |  |  |

| Status Affected: | None         |             |      |  |  |  |  |  |

| Encoding:        | 0000         | 0000        | 0000 |  |  |  |  |  |

| Description:     | No opera     | ation.      |      |  |  |  |  |  |

| Words:           | 1            |             |      |  |  |  |  |  |

| Cycles:          | 1            |             |      |  |  |  |  |  |

| Example:         | NOP          |             |      |  |  |  |  |  |

#### **10.0 DEVELOPMENT SUPPORT**

#### 10.1 <u>Development Tools</u>

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- MPLAB<sup>™</sup>-ICE Real-Time In-Circuit Emulator

- ICEPIC<sup>™</sup> Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- SIMICE

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

- KEELOQ<sup>®</sup> Evaluation Kits and Programmer

#### 10.2 MPLAB-ICE: High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro<sup>®</sup> microcontrollers (MCUs). MPLAB-ICE is supplied with the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support all new Microchip microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x or Windows 95 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE is available in two versions. MPLAB-ICE 1000 is a basic, low-cost emulator system with simple trace capabilities. It shares processor modules with the MPLAB-ICE 2000. This is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems will operate across the entire operating speed range of the PICmicro<sup>®</sup> MCU.

#### 10.3 ICEPIC: Low-Cost PICmicro<sup>®</sup> In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 386 through Pentium<sup>™</sup> based machines under Windows 3.x, Windows 95, or Windows NT environment. ICEPIC features real time, non-intrusive emulation.

#### 10.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

#### 10.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

#### 10.10 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- A full featured editor

- Three operating modes

- editor

- emulator

- simulator

- A project manager

- Customizable tool bar and key mapping

- A status bar with project information

- · Extensive on-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PICmicro<sup>®</sup> tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 10.11 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PChosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from MPLAB-ICE, Microchip's Universal Emulator System.

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PICmicro<sup>®</sup>. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

#### 10.12 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PICmicro<sup>®</sup> series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 10.13 MPLAB-C17 Compiler

The MPLAB-C17 Code Development System is a complete ANSI 'C' compiler and integrated development environment for Microchip's PIC17CXXX family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

#### 10.14 <u>Fuzzy Logic Development System</u> (fuzzyTECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, Edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 10.15 <u>SEEVAL® Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 11.2 DC CHARACTERISTICS:

#### PIC12C508/509 (Commercial, Industrial, Extended)

|              |                                                                | Standard Operating Conditions (unless otherwise specified)         Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial) |                  |      |                    |        |                                                                     |  |  |  |

|--------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|--------------------|--------|---------------------------------------------------------------------|--|--|--|

| DC CHA       | ARACTERISTICS                                                  | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)<br>-40^{\circ}C \le TA \le +125^{\circ}C (extended)                                                                                            |                  |      |                    |        |                                                                     |  |  |  |

|              |                                                                | Operating voltage VDD range as described in DC spec Section 11.1 and Section 11.2.                                                                                                                 |                  |      |                    |        |                                                                     |  |  |  |

| Param<br>No. | Characteristic                                                 | Sym                                                                                                                                                                                                | Min              | Тур† | Max                | Units  | Conditions                                                          |  |  |  |

| NO.          |                                                                |                                                                                                                                                                                                    |                  |      |                    |        |                                                                     |  |  |  |

|              | Input Low Voltage                                              | VIL                                                                                                                                                                                                |                  |      |                    |        |                                                                     |  |  |  |

| <b>D</b> 000 | •                                                              | VIL                                                                                                                                                                                                | Vee              | -    | 0.01/              | V      |                                                                     |  |  |  |

| D030         | with TTL buffer                                                |                                                                                                                                                                                                    | Vss              | -    | 0.8V               | V      | 4.5 < VDD ≤ 5.5V                                                    |  |  |  |

| D031         | with Coheritt Trigger huffer                                   |                                                                                                                                                                                                    | Vee              | -    | 0.15VDD<br>0.15VDD | V<br>V | otherwise                                                           |  |  |  |

| D031<br>D032 | with Schmitt Trigger buffer<br>MCLR, GP2/T0CKI (in EXTRC mode) |                                                                                                                                                                                                    | Vss<br>Vss       | -    | 0.15VDD<br>0.15VDD | V      |                                                                     |  |  |  |

|              |                                                                |                                                                                                                                                                                                    | VSS<br>VSS       | -    | 0.15VDD            | v      |                                                                     |  |  |  |

| D033         | OSC1 (EXTRC) <sup>(1)</sup>                                    |                                                                                                                                                                                                    |                  | -    |                    |        |                                                                     |  |  |  |

| D033         | OSC1 (in XT and LP)                                            |                                                                                                                                                                                                    | Vss              | -    | 0.3Vdd             | V      | Note1                                                               |  |  |  |

|              | Input High Voltage                                             |                                                                                                                                                                                                    |                  |      |                    |        |                                                                     |  |  |  |

|              | I/O ports                                                      | VIH                                                                                                                                                                                                |                  | -    |                    |        |                                                                     |  |  |  |

| D040         | with TTL buffer                                                | Vss                                                                                                                                                                                                | 2.0V             | -    | Vdd                | V      | $4.5 \leq VDD \leq 5.5V$                                            |  |  |  |

| D040A        |                                                                |                                                                                                                                                                                                    | 0.25VDD+<br>0.8V | -    | Vdd                | V      | otherwise                                                           |  |  |  |

| D041         | with Schmitt Trigger buffer                                    |                                                                                                                                                                                                    | 0.85VDD          | -    | VDD                | v      | For entire VDD range                                                |  |  |  |

| D042         | MCLR/GP2/T0CKI                                                 |                                                                                                                                                                                                    | 0.85VDD          | -    | VDD                | v      |                                                                     |  |  |  |

| -            |                                                                |                                                                                                                                                                                                    | 0.7VDD           | -    | VDD                | V      | Note1                                                               |  |  |  |

| D043         | OSC1 (in EXTRC mode)                                           |                                                                                                                                                                                                    | 0.85VDD          | -    | VDD                | V      |                                                                     |  |  |  |

| D070         | GPIO weak pull-up current                                      | IPUR                                                                                                                                                                                               | 50               | 250  | 400                | μA     | VDD = 5V, VPIN = VSS                                                |  |  |  |

|              | Input Leakage Current <sup>(2, 3)</sup>                        |                                                                                                                                                                                                    |                  |      |                    | 1.     | For VDD ≤5.5V                                                       |  |  |  |

| D060         | I/O ports                                                      | ١L                                                                                                                                                                                                 | -1               | 0.5  | <u>+</u> 1         | μΑ     | Vss ≤ VPIN ≤ VDD,<br>Pin at hi-impedance                            |  |  |  |

| D061         | MCLR, GP2/T0CKI                                                |                                                                                                                                                                                                    | 20               | 130  | 250                | μA     | $V_{PIN} = V_{SS} + 0.25 V^{(2)}$                                   |  |  |  |

| 2001         |                                                                |                                                                                                                                                                                                    |                  | 0.5  | +5                 | μΑ     | VPIN = VDD                                                          |  |  |  |

| D063         | OSC1                                                           |                                                                                                                                                                                                    | -3               | 0.5  | +3                 | μΑ     | $Vss \leq VPIN \leq VDD$ ,                                          |  |  |  |

|              |                                                                |                                                                                                                                                                                                    |                  |      |                    |        | XT and LP options                                                   |  |  |  |

|              | Output Low Voltage                                             |                                                                                                                                                                                                    |                  |      |                    |        |                                                                     |  |  |  |

| D080         | I/O ports/CLKOUT                                               | Vol                                                                                                                                                                                                | -                | -    | 0.6                | V      | IOL = 8.7 mA, VDD = 4.5V                                            |  |  |  |

|              | Output High Voltage                                            |                                                                                                                                                                                                    |                  |      |                    |        |                                                                     |  |  |  |

| D090         | I/O ports/CLKOUT <sup>(3)</sup>                                | Voh                                                                                                                                                                                                | Vdd - 0.7        | -    | -                  | V      | IOH = -5.4 mA, VDD = 4.5V                                           |  |  |  |

|              | Capacitive Loading Specs on                                    |                                                                                                                                                                                                    |                  |      |                    |        |                                                                     |  |  |  |

|              | Output Pins                                                    |                                                                                                                                                                                                    |                  |      |                    |        |                                                                     |  |  |  |

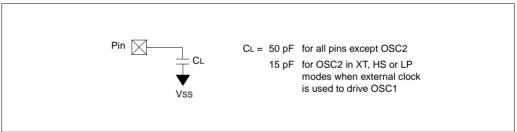

| D100         | OSC2 pin                                                       | Cosc2                                                                                                                                                                                              | -                | -    | 15                 | pF     | In XT and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101         | All I/O pins                                                   | Cio                                                                                                                                                                                                | -                | -    | 50                 | pF     |                                                                     |  |  |  |

|              | Data in "Typ" column is at 51/ 25°C ur                         |                                                                                                                                                                                                    |                  |      |                    |        | l                                                                   |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C5XX be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

## PIC12C5XX

#### 11.4 Timing Diagrams and Specifications

| AC Characteristics |            | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq Ta \leq +70^{\circ}C \mbox{ (commercial)}, \\ & -40^{\circ}C \leq Ta \leq +85^{\circ}C \mbox{ (industrial)}, \\ & -40^{\circ}C \leq Ta \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 11.1} \end{array} $ |     |                              |        |       |                |  |

|--------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------|--------|-------|----------------|--|

| Parameter<br>No.   | Sym        | Characteristic                                                                                                                                                                                                                                                                                                                                                                                        |     | Min Typ <sup>(1)</sup> Max U |        | Units | Conditions     |  |

|                    | Fosc       | External CLKIN Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                               |     |                              |        |       |                |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | DC  | —                            | 4      | MHz   | XT osc mode    |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | DC  | —                            | 200    | kHz   | LP osc mode    |  |

|                    |            | Oscillator Frequency <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                   |     |                              |        |       |                |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | 0.1 | —                            | 4      | MHz   | XT osc mode    |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | DC  | —                            | 200    | kHz   | LP osc mode    |  |

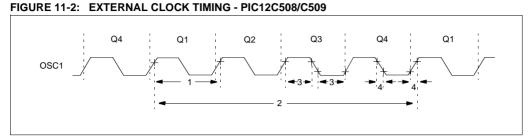

| 1                  | Tosc       | External CLKIN Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                  | 250 | —                            | _      | ns    | EXTRC osc mode |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | 250 | —                            | —      | ns    | XT osc mode    |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | 5   | —                            | —      | ms    | LP osc mode    |  |

|                    |            | Oscillator Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      | 250 | _                            | _      | ns    | EXTRC osc mode |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | 250 | —                            | 10,000 | ns    | XT osc mode    |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | 5   | —                            | —      | ms    | LP osc mode    |  |

| 2                  | Тсу        | Instruction Cycle Time <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                 | —   | 4/Fosc                       | —      |       |                |  |

| 3                  | TosL, TosH | Clock in (OSC1) Low or High Time                                                                                                                                                                                                                                                                                                                                                                      | 50* | —                            | —      | ns    | XT oscillator  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | 2*  | —                            | —      | ms    | LP oscillator  |  |

| 4                  | TosR, TosF | Clock in (OSC1) Rise or Fall Time                                                                                                                                                                                                                                                                                                                                                                     | —   | —                            | 25*    | ns    | XT oscillator  |  |

|                    |            |                                                                                                                                                                                                                                                                                                                                                                                                       | -   | _                            | 50*    | ns    | LP oscillator  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

3: Instruction cycle period (TCY) equals four times the input oscillator time base period.

#### TABLE 11-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC12C508/C509

| AC Characteristics             |                                  | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ (commercial),} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial),} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 10.1} \end{array} $ |      |                    |      |       |            |

|--------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|-------|------------|

| Parameter<br>No.               | Sym                              | Characteristic                                                                                                                                                                                                                                                                                                                                                                                        | Min* | Typ <sup>(1)</sup> | Max* | Units | Conditions |

|                                | Internal Calibrated RC Frequency |                                                                                                                                                                                                                                                                                                                                                                                                       | 3.58 | 4.00               | 4.32 | MHz   | VDD = 5.0V |

| Internal Calibrated RC Frequen |                                  | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                                                                                                      | 3.50 | —                  | 4.26 | MHz   | VDD = 2.5V |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

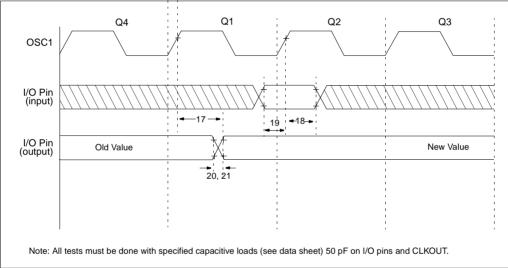

#### FIGURE 11-3: I/O TIMING - PIC12C508/C509

## PIC12C5XX

NOTES:

#### 13.1 DC CHARACTERISTICS:

#### PIC12C508A/509A (Commercial, Industrial, Extended) PIC12CE518/519 (Commercial, Industrial, Extended) PIC12CR509A (Commercial, Industrial, Extended)

|             | DC Characteristics<br>Power Supply Pins                                    |                |       | ard Oper<br>ting Temp |     | 0°<br>-40° | s (unless otherwise specified)<br>$C \le TA \le +70^{\circ}C$ (commercial)<br>$C \le TA \le +85^{\circ}C$ (industrial)<br>$C \le TA \le +125^{\circ}C$ (extended) |

|-------------|----------------------------------------------------------------------------|----------------|-------|-----------------------|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parm<br>No. | Characteristic                                                             | Sym            | Min   | Typ <sup>(1)</sup>    | Max | Units      | Conditions                                                                                                                                                        |

| D001        | Supply Voltage                                                             | Vdd            | 3.0   |                       | 5.5 | V          | Fosc = DC to 4 MHz (Commercial/<br>Industrial, Extended)                                                                                                          |

| D002        | RAM Data Retention<br>Voltage <sup>(2)</sup>                               | Vdr            |       | 1.5*                  |     | V          | Device in SLEEP mode                                                                                                                                              |

| D003        | VDD Start Voltage to ensure<br>Power-on Reset                              | VPOR           |       | Vss                   |     | V          | See section on Power-on Reset for details                                                                                                                         |

| D004        | VDD Rise Rate to ensure<br>Power-on Reset                                  | SVDD           | 0.05* |                       |     | V/ms       | See section on Power-on Reset for details                                                                                                                         |

| D010        | Supply Current <sup>(3)</sup>                                              | IDD            | —     | 0.8                   | 1.4 | mA         | XT and EXTRC options (Note 4)<br>Fosc = 4 MHz, VDD = 5.5V                                                                                                         |

| D010C       |                                                                            |                | _     | 0.8                   | 1.4 | mA         | INTRC Option<br>Fosc = 4 MHz, VDD = 5.5V                                                                                                                          |

| D010A       |                                                                            |                | -     | 19                    | 27  | μA         | LP OPTION, Commercial Temperature<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                      |

|             |                                                                            |                | _     | 19                    | 35  | μA         | LP OPTION, Industrial Temperature<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                                                      |

|             |                                                                            |                | _     | 30                    | 55  | μA         | LP OPTION, Extended Temperature<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                                                        |

| D020        | Power-Down Current <sup>(5)</sup>                                          | IPD            | —     | 0.25                  | 4   | μA         | VDD = 3.0V, Commercial WDT disabled                                                                                                                               |

| D021        |                                                                            |                | —     | 0.25                  | 5   | μA         | VDD = 3.0V, Industrial WDT disabled                                                                                                                               |

| D021B       |                                                                            |                | -     | 2                     | 12  | μA         | VDD = 3.0V, Extended WDT disabled                                                                                                                                 |

| D022        | Power-Down Current                                                         | $\Delta I$ WDT | —     | 2.2                   | 5   | μA         | VDD = 3.0V, Commercial                                                                                                                                            |

|             |                                                                            |                | -     | 2.2                   | 6   | μA         | VDD = 3.0V, Industrial                                                                                                                                            |

|             |                                                                            |                | -     | 4                     | 11  | μA         | VDD = 3.0V, Extended                                                                                                                                              |

|             | Supply Current <sup>(3)</sup><br>During read/write to<br>EEPROM peripheral | ΔIEE           | -     | 0.1                   | 0.2 | mA         | FOSC = 4 MHz, Vdd = 5.5V,<br>SCL = 400kHz                                                                                                                         |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to

- Vss, T0CKI = VDD,  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: Does not include current through Rext. The current through the resistor can be estimated by the formula: IR = VDD/2Rext (mA) with Rext in kOhm.

- 5: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

# TABLE 13-1: PULL-UP RESISTOR RANGES\* - PIC12C508A, PIC12C509A, PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Max  | Units |

|-------------|------------------|------|------|------|-------|

|             |                  | GP0  | /GP1 |      |       |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |

|             | 25               | 42K  | 48K  | 63K  | Ω     |

|             | 85               | 42K  | 49K  | 63K  | Ω     |

|             | 125              | 50K  | 55K  | 63K  | Ω     |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |

|             | 25               | 18K  | 20K  | 23K  | Ω     |

|             | 85               | 19K  | 22K  | 25K  | Ω     |

|             | 125              | 22K  | 24K  | 28K  | Ω     |

|             |                  | G    | P3   |      |       |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |

|             | 25               | 343K | 414K | 532K | Ω     |

|             | 85               | 368K | 457K | 532K | Ω     |

|             | 125              | 431K | 504K | 593K | Ω     |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |

|             | 25               | 288K | 341K | 437K | Ω     |

|             | 85               | 306K | 371K | 448K | Ω     |

|             | 125              | 351K | 407K | 500K | Ω     |

\* These parameters are characterized but not tested.

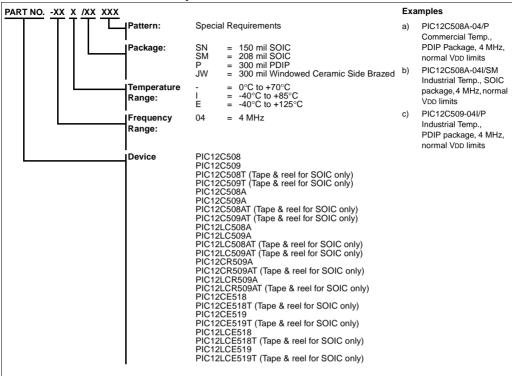

#### 13.5 <u>Timing Parameter Symbology and Load Conditions - PIC12C508A, PIC12C509A,</u> PIC12CR509A, PIC12CE518, PIC12CE519, PIC12LC508A, PIC12LC509A, PIC12LCR509A, PIC12LCE518 and PIC12LCE519

The timing parameter symbols have been created following one of the following formats:

| 1. Tp | oS2ppS |

|-------|--------|

|-------|--------|

2. TppS

| 2. TppS |                                       |     |                |  |