Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2 0 0 0 0 0 0              |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 5                                                                            |

| Program Memory Size        | 768B (512 x 12)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | 16 x 8                                                                       |

| RAM Size                   | 25 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

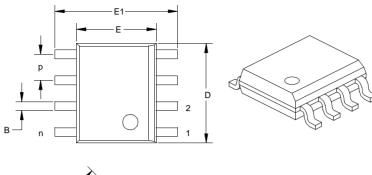

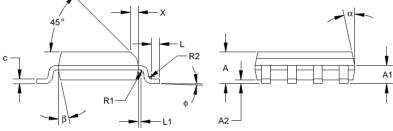

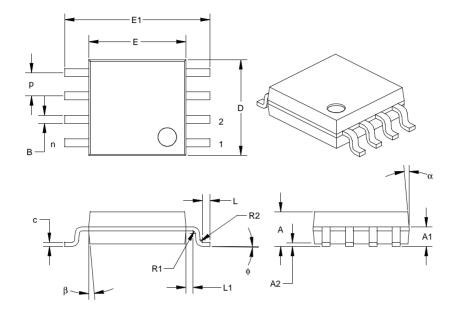

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                                |

| Supplier Device Package    | 8-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lce518-04i-sn |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 PIC12C5XX DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12C5XX Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in ceramic side brazed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

Microchip's PICSTART<sup>®</sup> PLUS and PRO MATE<sup>®</sup> programmers all support programming of the PIC12C5XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

### 2.5 Read Only Memory (ROM) Device

Microchip offers masked ROM to give the customer a low cost option for high volume, mature products.

NOTES:

| Name           | DIP<br>Pin # | SOIC<br>Pin # | l/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|--------------|---------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0            | 7            | 7             | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming data. Can<br>be software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming<br>mode.                                                                                                                                                                                                               |

| GP1            | 6            | 6             | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming clock. Can<br>be software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming<br>mode.                                                                                                                                                                                                              |

| GP2/T0CKI      | 5            | 5             | I/O           | ST             | Bi-directional I/O port. Can be configured as T0CKI.                                                                                                                                                                                                                                                                                                                                                                                                |

| GP3/MCLR/Vpp   | 4            | 4             | Ι             | TTL/ST         | Input port/master clear (reset) input/programming volt-<br>age input. When configured as MCLR, this pin is an<br>active low reset to the device. Voltage on MCLR/VPP<br>must not exceed VDD during normal device operation<br>or the device will enter programming mode. Can be<br>software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. Weak pull-up<br>always on if configured as MCLR. ST when in MCLR<br>mode. |

| GP4/OSC2       | 3            | 3             | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output. Con-<br>nections to crystal or resonator in crystal oscillator<br>mode (XT and LP modes only, GPIO in other modes).                                                                                                                                                                                                                                                                              |

| GP5/OSC1/CLKIN | 2            | 2             | I/O           | TTL/ST         | Bidirectional IO port/oscillator crystal input/external<br>clock source input (GPIO in Internal RC mode only,<br>OSC1 in all other oscillator modes). TTL input when<br>GPIO, ST input in external RC oscillator mode.                                                                                                                                                                                                                              |

| Vdd            | 1            | 1             | Р             | _              | Positive supply for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vss            | 8            | 8             | Р             | _              | Ground reference for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                                             |

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input

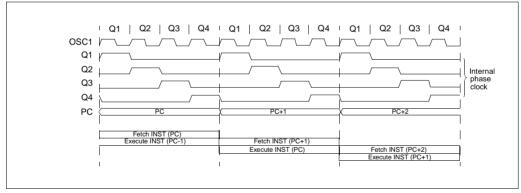

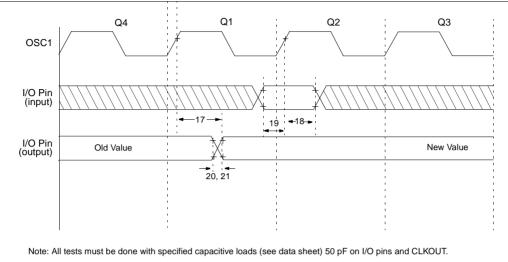

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.0 MEMORY ORGANIZATION

PIC12C5XX memory is organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one STA-TUS register bit. For the PIC12C509, PIC12C509A, PICCR509A and PIC12CE519 with a data memory register file of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Select Register (FSR).

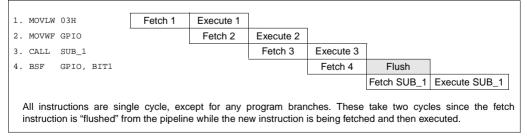

#### 4.1 Program Memory Organization

The PIC12C5XX devices have a 12-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space.

Only the first 512 x 12 (0000h-01FFh) for the PIC12C508. PIC12C508A and PIC12CE518 and 1K x 12 (0000h-03FFh) for the PIC12C509, PIC12C509A. PIC12CR509A, and PIC12CE519 are physically implemented. Refer to Figure 4-1. Accessing a location above these boundaries will cause a wraparound within the first 512 x 12 space (PIC12C508, PIC12C508A and PIC12CE518) or 1K x 12 space (PIC12C509, PIC12C509A, PIC12CR509A and PIC12CE519). The effective reset vector is at 000h, (see Figure 4-1). Location 01FFh (PIC12C508, PIC12C508A and PIC12CE518) or location 03FFh (PIC12C509, PIC12C509A, PIC12CR509A and PIC12CE519) contains the internal clock oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK

#### 4.4 OPTION Register

The OPTION register is a 8-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A RESET sets the OPTION<7:0> bits.

#### FIGURE 4-5: OPTION REGISTER

Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin; i.e., note that TRIS overrides OPTION control of GPPU and GPWU.

**Note:** If the TOCS bit is set to '1', GP2 is forced to be an input even if TRIS GP2 = '0'.

| W-1      | W-1                                                  | W-1           | W-1         | W-1          | W-1         | W-1 | W-1  |                                                                                               |

|----------|------------------------------------------------------|---------------|-------------|--------------|-------------|-----|------|-----------------------------------------------------------------------------------------------|

| GPWU     | GPPU                                                 | TOCS          | T0SE        | PSA          | PS2         | PS1 | PS0  | W = Writable bit                                                                              |

| oit7     | 6                                                    | 5             | 4           | 3            | 2           | 1   | bit0 | U = Unimplemented bit<br>- n = Value at POR reset<br>Reference Table 4-1 for<br>other resets. |

| bit 7:   | <b>GPWU</b> : Ena<br>1 = Disable<br>0 = Enable       | d             | p on pin cl | hange (GP    | 0, GP1, GP3 | )   |      |                                                                                               |

| bit 6:   | <b>GPPU</b> : Ena<br>1 = Disable<br>0 = Enablec      | d .           | III-ups (GF | 90, GP1, G   | P3)         |     |      |                                                                                               |

| bit 5:   | <b>TOCS</b> : Time<br>1 = Transitio<br>0 = Transitio | on on TOCK    | l pin       |              | ock, Fosc/4 |     |      |                                                                                               |

| bit 4:   | TOSE: Time<br>1 = Increme<br>0 = Increme             | ent on high t | o low trans | sition on th |             |     |      |                                                                                               |

| bit 3:   | <b>PSA</b> : Presc<br>1 = Prescale<br>0 = Prescale   | er assigned   | to the WD   |              |             |     |      |                                                                                               |

| bit 2-0: | PS2:PS0: P                                           | Prescaler rat | e select bi | its          |             |     |      |                                                                                               |

|          | Bit Value                                            | Timer0 R      | ate WDT     | Rate         |             |     |      |                                                                                               |

|          | 000                                                  | 1:2<br>1:4    | 1:          | 2            |             |     |      |                                                                                               |

|          | 010<br>011                                           | 1:8           | 1:          |              |             |     |      |                                                                                               |

|          | 100                                                  | 1:32          |             | 0<br>16      |             |     |      |                                                                                               |

|          | 101                                                  | 1:64          |             | 32           |             |     |      |                                                                                               |

|          | 110                                                  | 1:128         |             | 64           |             |     |      |                                                                                               |

|          | 111                                                  | 1:256         | : 1.        | 128          |             |     |      |                                                                                               |

#### 8.7 <u>Time-Out Sequence, Power Down,</u> and Wake-up from SLEEP Status Bits (TO/PD/GPWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and GPWUF bits in the STATUS register can be tested to determine if a RESET condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) reset.

| TABLE 8-7: | TO/PD/GPWUF STATUS |

|------------|--------------------|

|            | AFTER RESET        |

| GPWUF | то | PD | RESET caused by                     |  |  |

|-------|----|----|-------------------------------------|--|--|

| 0     | 0  | 0  | WDT wake-up from<br>SLEEP           |  |  |

| 0     | 0  | u  | WDT time-out (not from<br>SLEEP)    |  |  |

| 0     | 1  | 0  | MCLR wake-up from<br>SLEEP          |  |  |

| 0     | 1  | 1  | Power-up                            |  |  |

| 0     | u  | u  | MCLR not during SLEEP               |  |  |

| 1     | 1  | 0  | Wake-up from SLEEP on<br>pin change |  |  |

Legend: u = unchanged

Note 1: The TO, PD, and GPWUF bits maintain their status (u) until a reset occurs. A lowpulse on the MCLR input does not change the TO, PD, and GPWUF status bits.

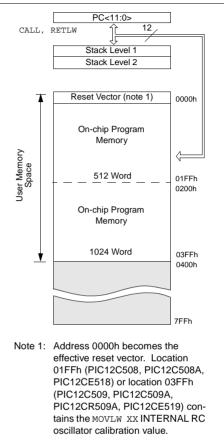

#### 8.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset PIC12C5XX devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 8-13 , Figure 8-14 and Figure 8-15

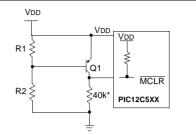

#### FIGURE 8-13: BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 8-14: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

\*Refer to Figure 8-7 and Table 11-1 for internal weak pull-up on MCLR.

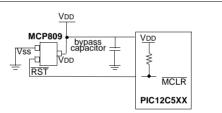

#### FIGURE 8-15: BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX family of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accomodate 5V and 3V systems.

| CALL                  | Subroutine Call                                                                                                                                                                                                                                |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:               | [ <i>label</i> ] CALL k                                                                                                                                                                                                                        |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                                                                                                                                              |  |  |  |  |

| Operation:            | $\begin{array}{l} (PC) + 1 \rightarrow \text{Top of Stack;} \\ k \rightarrow PC < 7:0 >; \\ (STATUS < 6:5 >) \rightarrow PC < 10:9 >; \\ 0 \rightarrow PC < 8 > \end{array}$                                                                   |  |  |  |  |

| Status Affected:      | None                                                                                                                                                                                                                                           |  |  |  |  |

| Encoding:             | 1001 kkkk kkkk                                                                                                                                                                                                                                 |  |  |  |  |

| Description:          | Subroutine call. First, return address (PC+1) is pushed onto the stack. The eight bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STA-TUS<6:5>, PC<8> is cleared. CALL is a two cycle instruction. |  |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                              |  |  |  |  |

| Cycles:               | 2                                                                                                                                                                                                                                              |  |  |  |  |

| Example:              | HERE CALL THERE                                                                                                                                                                                                                                |  |  |  |  |

| Before Instru<br>PC = |                                                                                                                                                                                                                                                |  |  |  |  |

|                       | tion<br>address (THERE)<br>address (HERE + 1)                                                                                                                                                                                                  |  |  |  |  |

#### CLRF

| Syntax:                        | [label]                                                                | CLRF f    |      |  |  |

|--------------------------------|------------------------------------------------------------------------|-----------|------|--|--|

| Operands:                      | $0 \le f \le 31$                                                       |           |      |  |  |

| Operation:                     | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |           |      |  |  |

| Status Affected:               | Z                                                                      |           |      |  |  |

| Encoding:                      | 0000                                                                   | 011f      | ffff |  |  |

| Description:                   | The contents of register 'f' are cleared and the Z bit is set.         |           |      |  |  |

| Words:                         | 1                                                                      |           |      |  |  |

| Cycles:                        | 1                                                                      |           |      |  |  |

| Example:                       | CLRF                                                                   | FLAG_REC  | 3    |  |  |

| Before Instru<br>FLAG_RE       |                                                                        | 0x5A      |      |  |  |

| After Instruct<br>FLAG_RE<br>Z |                                                                        | 0x00<br>1 |      |  |  |

Clear f

| CLRW                                                                                                     | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation:                                                                                               | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}); \\ 1 \rightarrow \text{Z} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                                                                                             | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                                 | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Before Instru<br>W =                                                                                     | uction<br>0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| After Instruct<br>W =<br>Z =                                                                             | tion<br>0x00<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLRWDT<br>Syntax:                                                                                        | Clear Watchdog Timer<br>[label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Syntax:                                                                                                  | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Syntax:<br>Operands:                                                                                     | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Syntax:<br>Operands:<br>Operation:                                                                       | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |